ADC for EMC PANDA EMC Readout System A

- Slides: 27

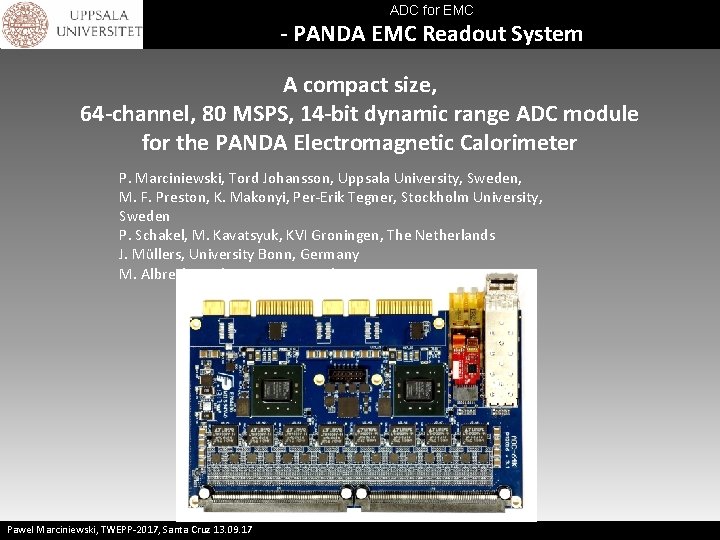

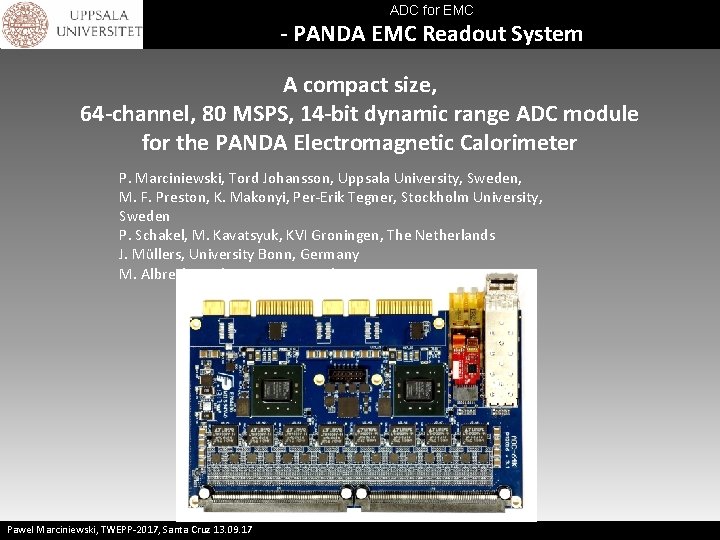

ADC for EMC - PANDA EMC Readout System A compact size, 64 -channel, 80 MSPS, 14 -bit dynamic range ADC module for the PANDA Electromagnetic Calorimeter P. Marciniewski, Tord Johansson, Uppsala University, Sweden, M. F. Preston, K. Makonyi, Per-Erik Tegner, Stockholm University, Sweden P. Schakel, M. Kavatsyuk, KVI Groningen, The Netherlands J. Müllers, University Bonn, Germany M. Albrecht, Ruhr University Bochum, Germany Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

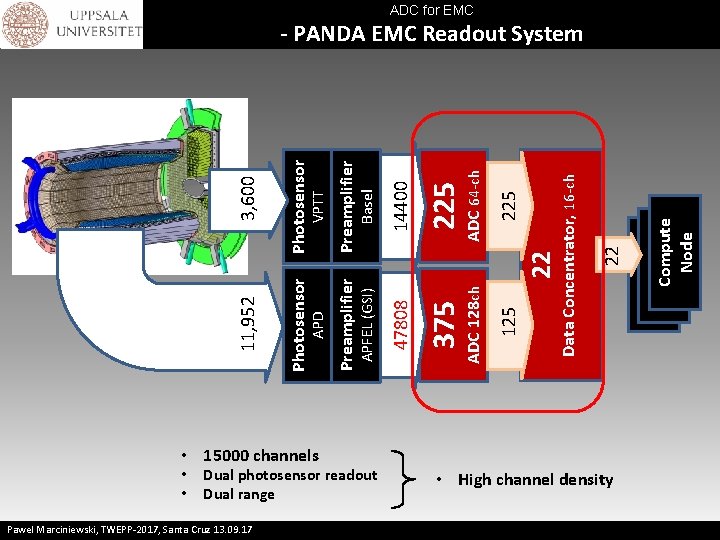

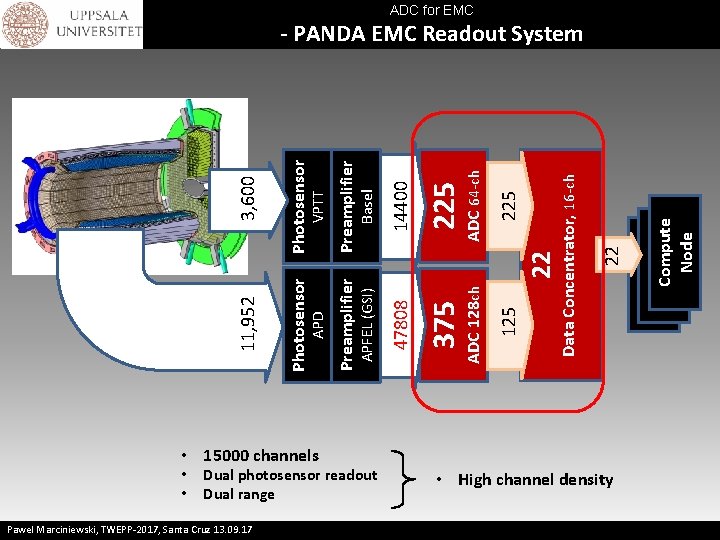

• • Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 • 15000 channels Dual photosensor readout Dual range 14400 225 47808 375 225 125 • High channel density Compute Node 22 Data Concentrator, 16 -ch ADC 64 -ch Basel ADC 128 ch APFEL (GSI) 22 Preamplifier VPTT Photosensor APD 3, 600 11, 952 ADC for EMC - PANDA EMC Readout System

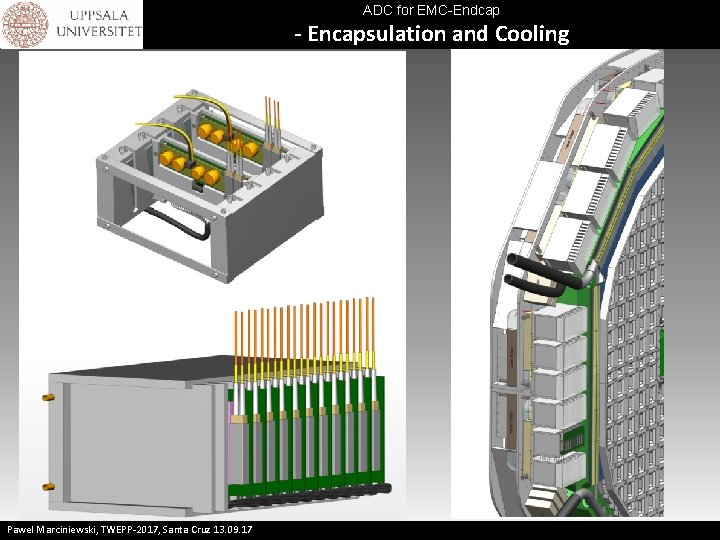

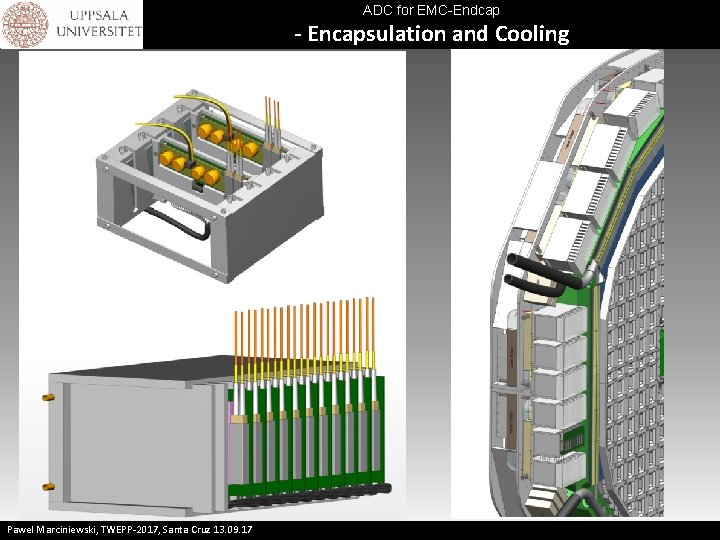

ADC for EMC-Endcap - Encapsulation and Cooling Courtesy KVI Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

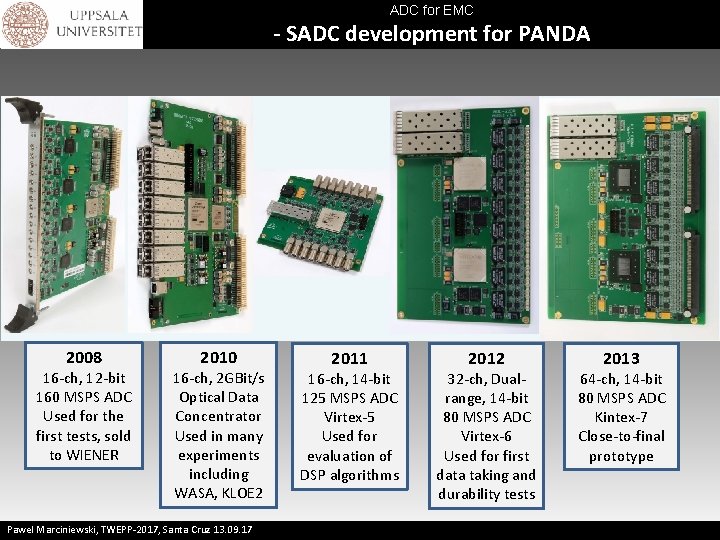

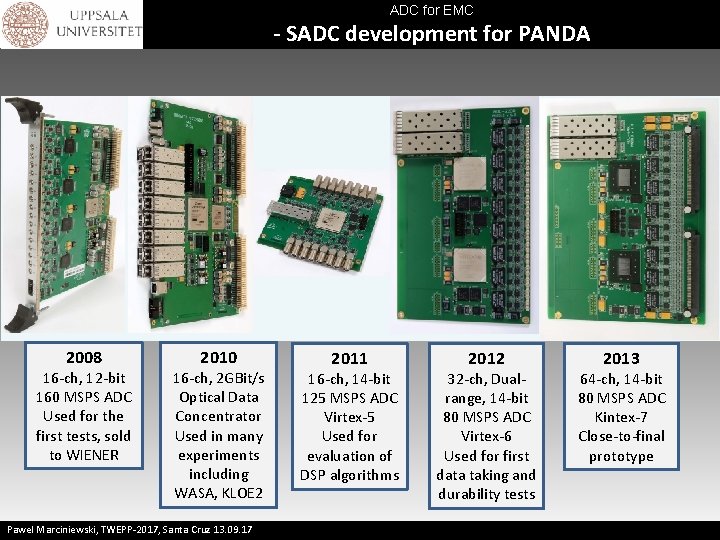

ADC for EMC - SADC development for PANDA 2008 16 -ch, 12 -bit 160 MSPS ADC Used for the first tests, sold to WIENER 2010 16 -ch, 2 GBit/s Optical Data Concentrator Used in many experiments including WASA, KLOE 2 Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 2011 16 -ch, 14 -bit 125 MSPS ADC Virtex-5 Used for evaluation of DSP algorithms 2012 32 -ch, Dualrange, 14 -bit 80 MSPS ADC Virtex-6 Used for first data taking and durability tests 2013 64 -ch, 14 -bit 80 MSPS ADC Kintex-7 Close-to-final prototype

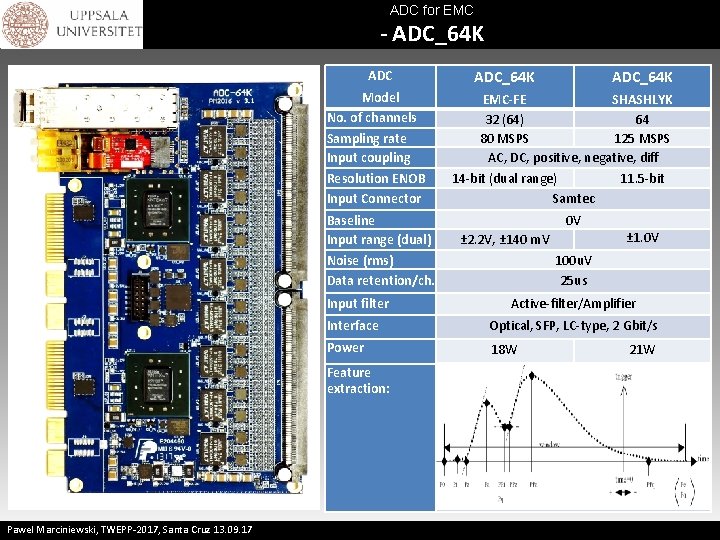

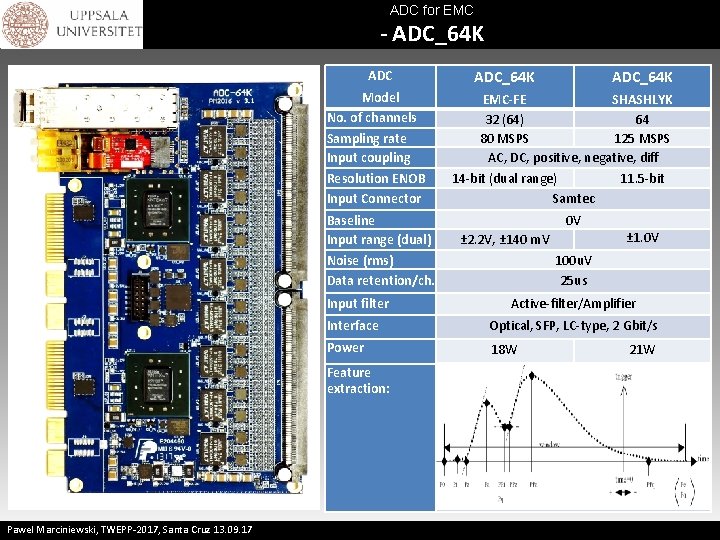

ADC for EMC - ADC_64 K ADC Model No. of channels Sampling rate Input coupling Resolution ENOB Input Connector Baseline Input range (dual) ADC_64 K EMC-FE SHASHLYK 32 (64) 64 80 MSPS 125 MSPS AC, DC, positive, negative, diff 14 -bit (dual range) Samtec ± 1. 0 V ± 2. 2 V, ± 140 m. V 100 u. V 25 us Active-filter/Amplifier Interface Optical, SFP, LC-type, 2 Gbit/s Power 18 W Feature extraction: Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 11. 5 -bit 0 V Noise (rms) Data retention/ch. Input filter ADC_64 K 21 W

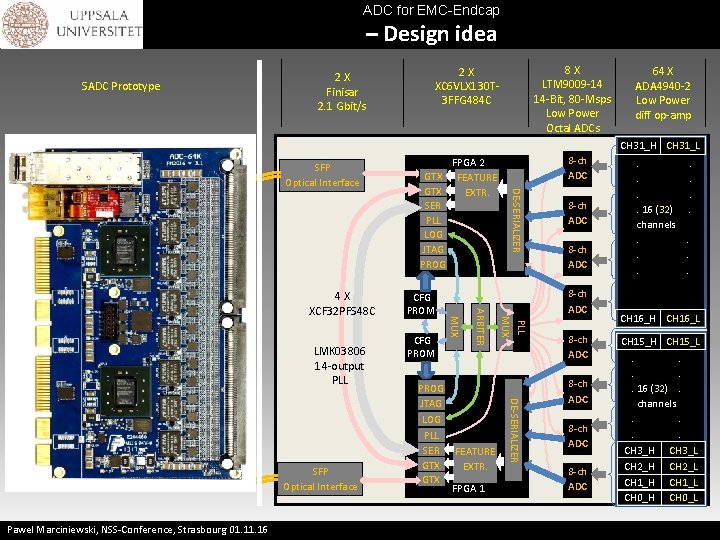

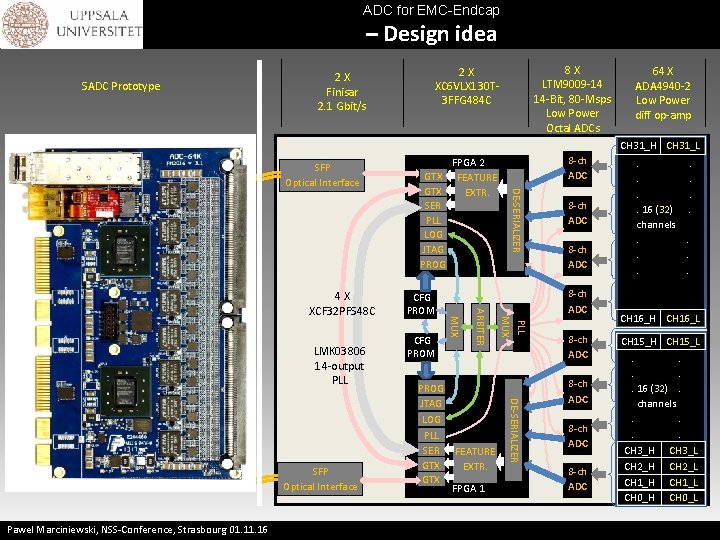

ADC for EMC-Endcap – Design idea SADC Prototype 2 X Finisar 2. 1 Gbit/s 8 X LTM 9009 -14 14 -Bit, 80 -Msps Low Power Octal ADCs 2 X XC 6 VLX 130 T 3 FFG 484 C 64 X ADA 4940 -2 Low Power diff op-amp CH 31_H CH 31_L DE-SERIALIZER Pawel Marciniewski, NSS-Conference, Strasbourg 01. 16 PROG JTAG LOG PLL SER FEATURE GTX EXTR. GTX FPGA 1 8 -ch ADC PLL MUX SFP Optical Interface CFG PROM ARBITER LMK 03806 14 -output PLL CFG PROM MUX 4 X XCF 32 PFS 48 C FPGA 2 GTX FEATURE GTX EXTR. SER PLL LOG JTAG PROG DE-SERIALIZER SFP Optical Interface 8 -ch ADC 8 -ch ADC . . . . 16 (32). channels. . . CH 16_H CH 16_L CH 15_H CH 15_L. . . 16 (32). channels. . CH 3_H CH 3_L CH 2_H CH 2_L CH 1_H CH 1_L CH 0_H CH 0_L

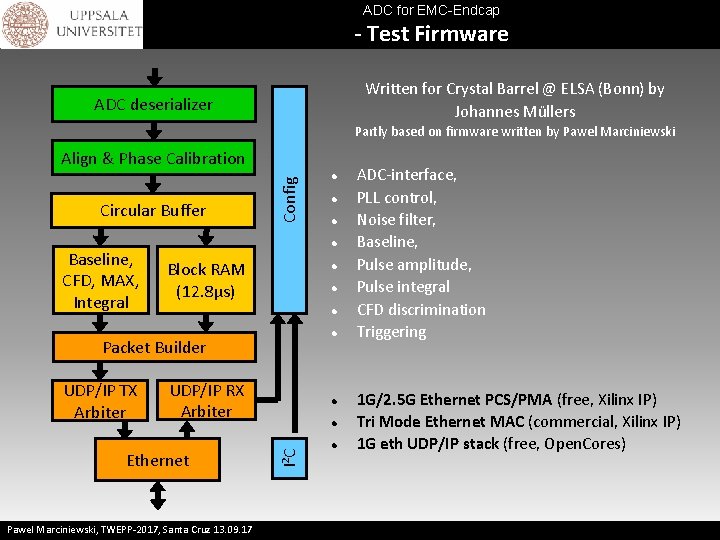

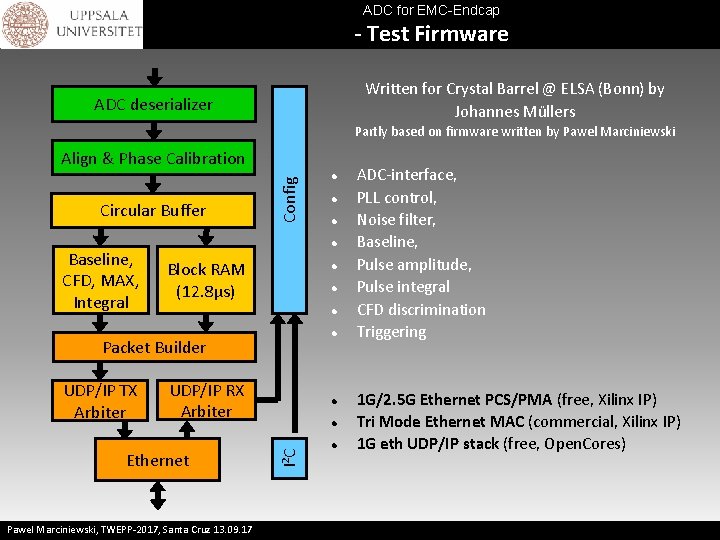

ADC for EMC-Endcap - Test Firmware Written for Crystal Barrel @ ELSA (Bonn) by Johannes Müllers ADC deserializer Partly based on firmware written by Pawel Marciniewski Circular Buffer Baseline, CFD, MAX, Integral Config Align & Phase Calibration Block RAM (12. 8µs) Packet Builder UDP/IP RX Arbiter Ethernet Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 I²C UDP/IP TX Arbiter ADC-interface, PLL control, Noise filter, Baseline, Pulse amplitude, Pulse integral CFD discrimination Triggering 1 G/2. 5 G Ethernet PCS/PMA (free, Xilinx IP) Tri Mode Ethernet MAC (commercial, Xilinx IP) 1 G eth UDP/IP stack (free, Open. Cores)

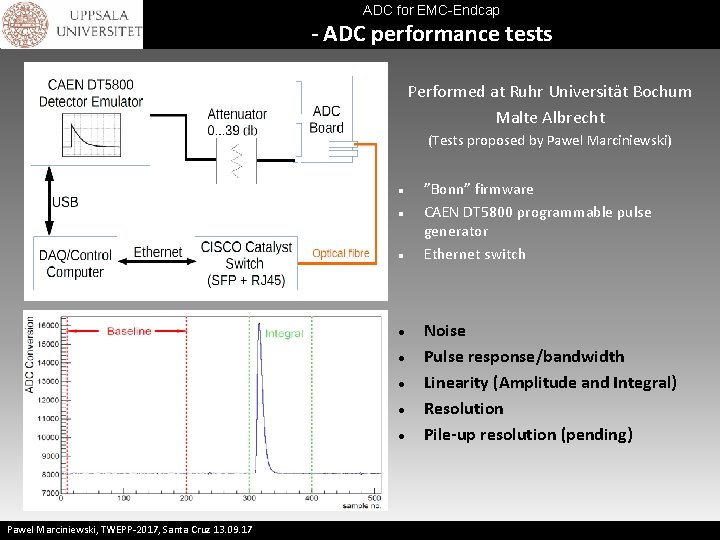

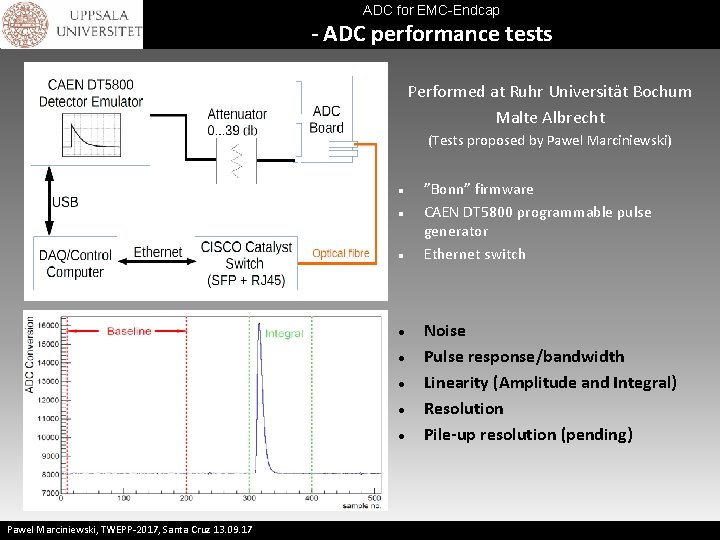

ADC for EMC-Endcap - ADC performance tests Performed at Ruhr Universität Bochum Malte Albrecht (Tests proposed by Pawel Marciniewski) Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 ”Bonn” firmware CAEN DT 5800 programmable pulse generator Ethernet switch Noise Pulse response/bandwidth Linearity (Amplitude and Integral) Resolution Pile-up resolution (pending)

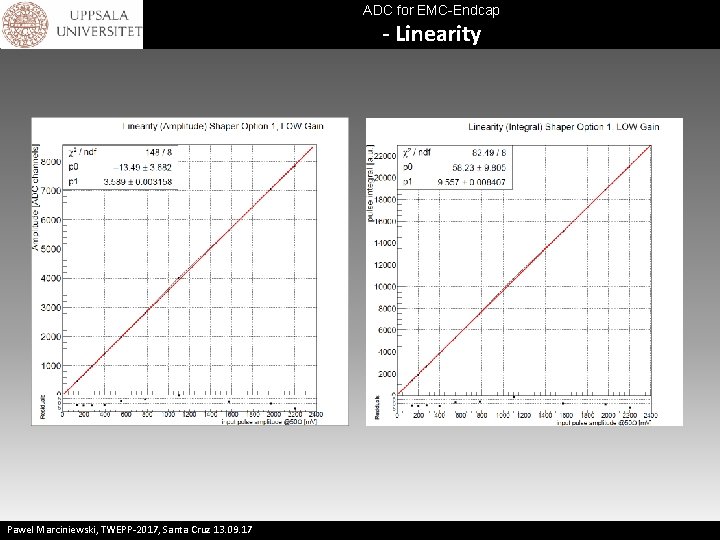

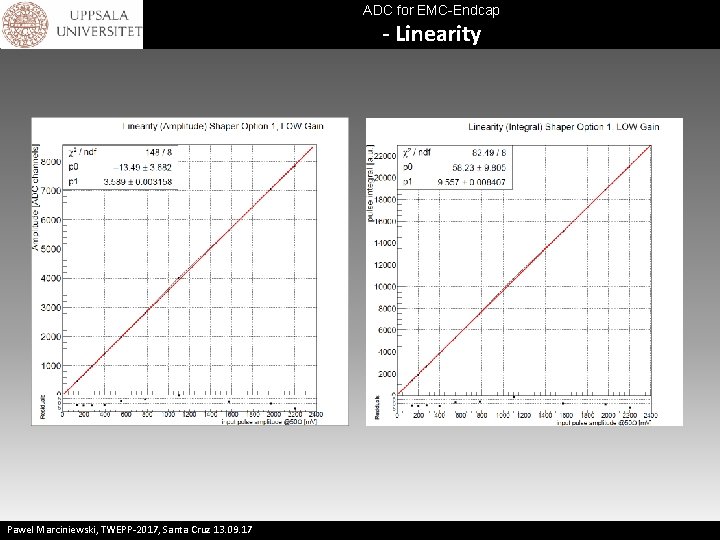

ADC for EMC-Endcap - Linearity Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

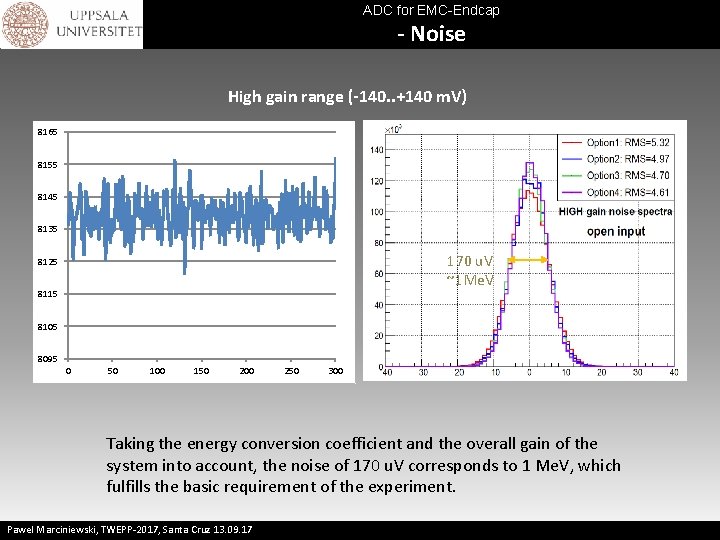

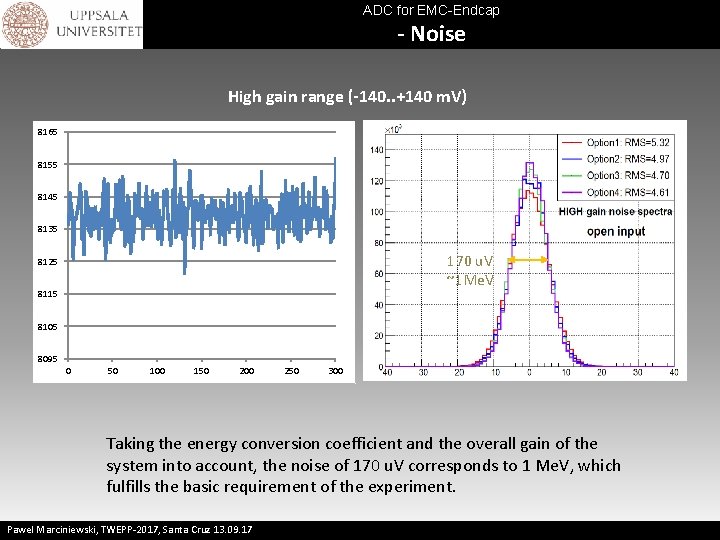

ADC for EMC-Endcap - Noise High gain range (-140. . +140 m. V) 8165 8155 8145 8135 170 u. V ~1 Me. V 8125 8115 8105 8095 0 50 100 150 200 250 300 Taking the energy conversion coefficient and the overall gain of the system into account, the noise of 170 u. V corresponds to 1 Me. V, which fulfills the basic requirement of the experiment. Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

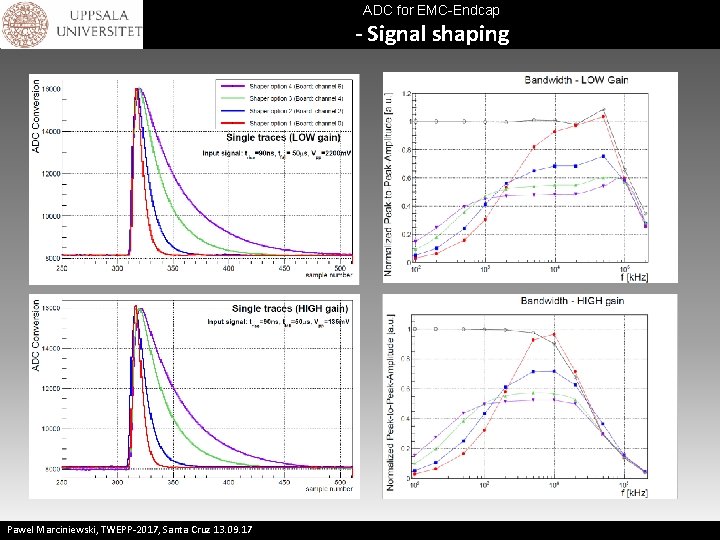

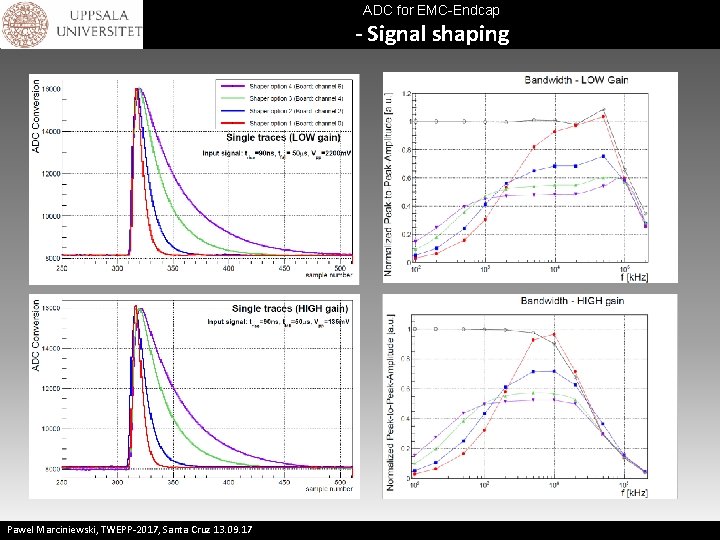

ADC for EMC-Endcap - Signal shaping Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

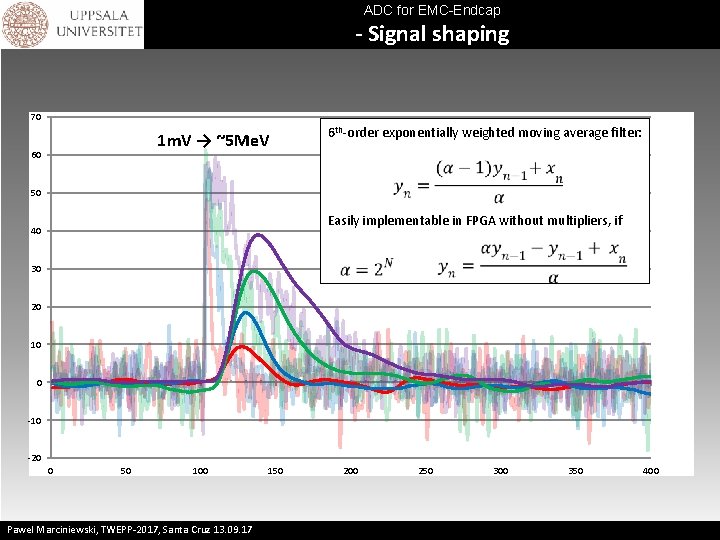

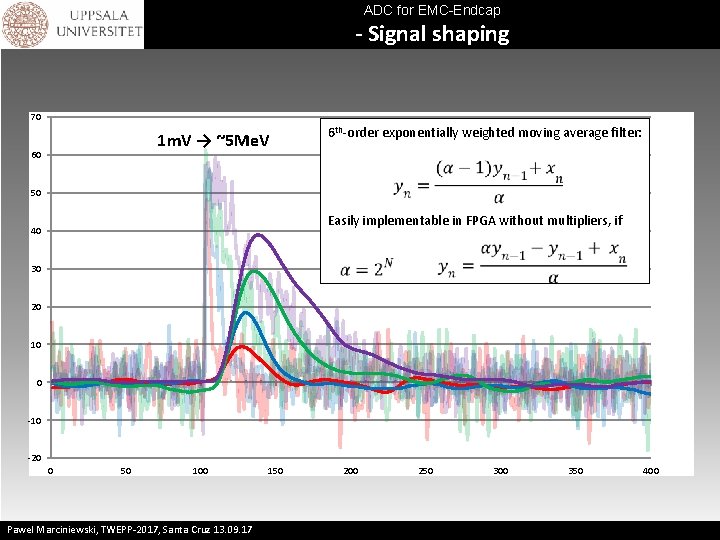

ADC for EMC-Endcap - Signal shaping 70 1 m. V → ~5 Me. V 60 6 th-order exponentially weighted moving average filter: 50 Easily implementable in FPGA without multipliers, if 40 30 20 10 0 -10 -20 0 50 100 Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 150 200 250 300 350 400

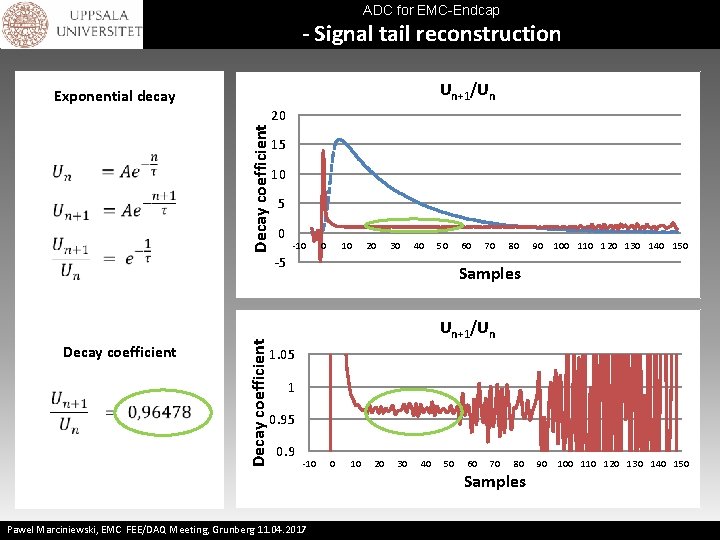

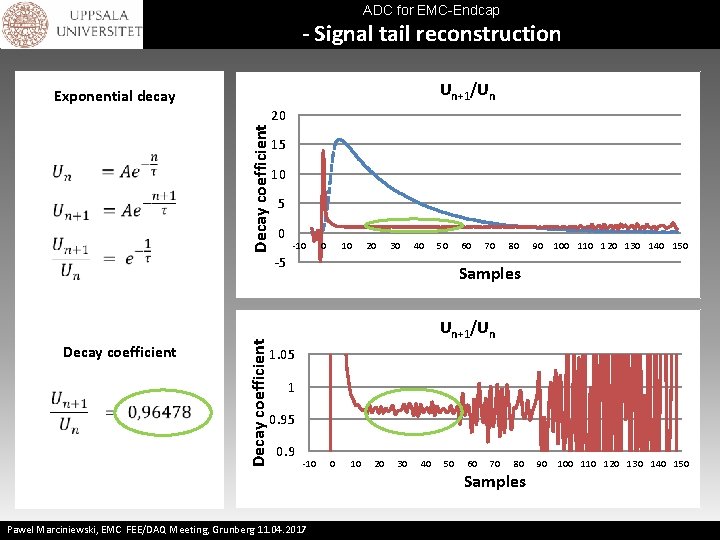

ADC for EMC-Endcap - Signal tail reconstruction Un+1/Un Exponential decay Decay coefficient 20 15 10 5 0 -10 0 10 20 30 40 50 Decay coefficient -5 60 70 80 90 100 110 120 130 140 150 Samples Un+1/Un 1. 05 1 0. 95 0. 9 -10 Pawel Marciniewski, EMC FEE/DAQ Meeting, Grunberg 11. 04. 2017 0 10 20 30 40 50 60 70 80 Samples 90 100 110 120 130 140 150

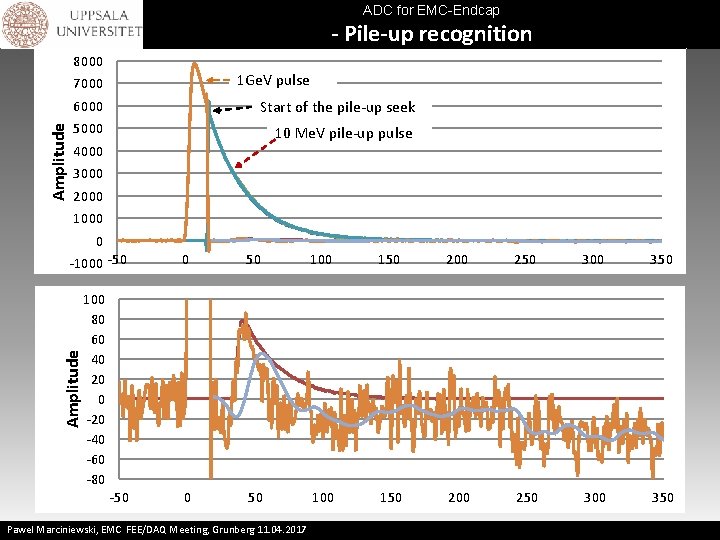

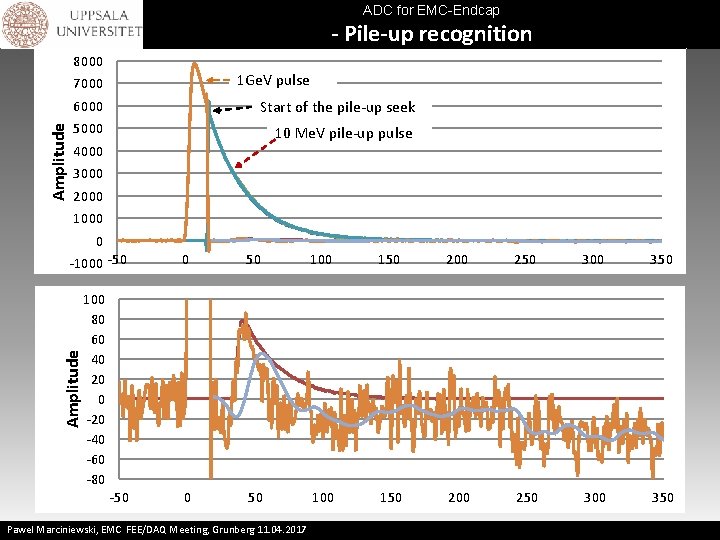

ADC for EMC-Endcap 8000 7000 6000 5000 4000 3000 2000 1000 0 -1000 -50 Amplitude - Pile-up recognition 1 Ge. V pulse Start of the pile-up seek 10 Me. V pile-up pulse 0 50 100 150 200 250 300 350 100 80 60 40 20 0 -20 -40 -60 -80 -50 Pawel Marciniewski, EMC FEE/DAQ Meeting, Grunberg 11. 04. 2017

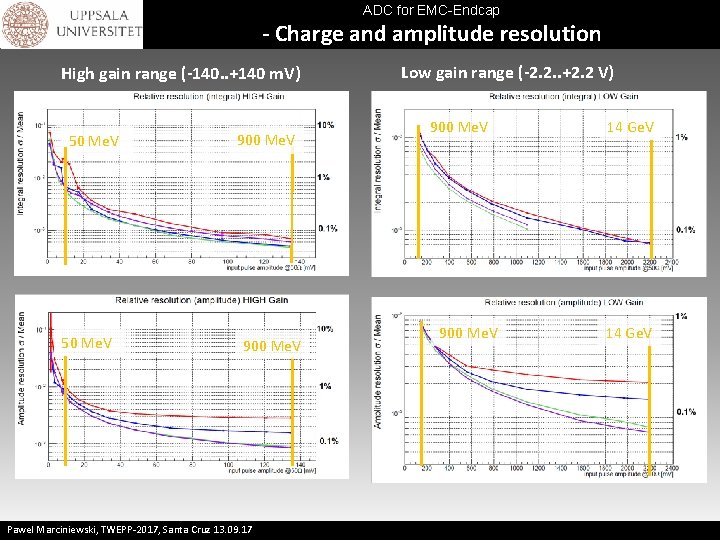

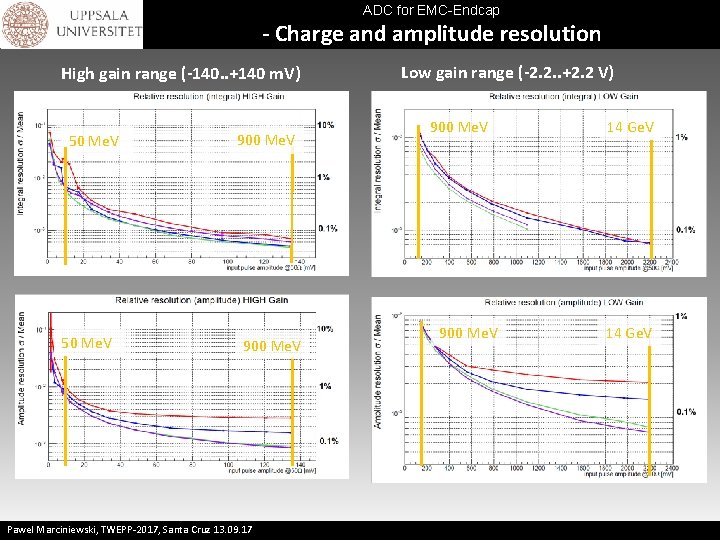

ADC for EMC-Endcap - Charge and amplitude resolution High gain range (-140. . +140 m. V) 50 Me. V 900 Me. V Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 Low gain range (-2. 2. . +2. 2 V) 900 Me. V 14 Ge. V

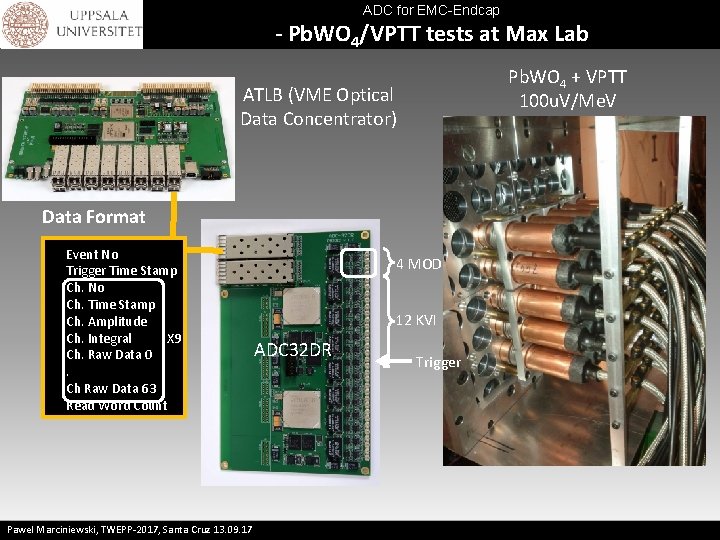

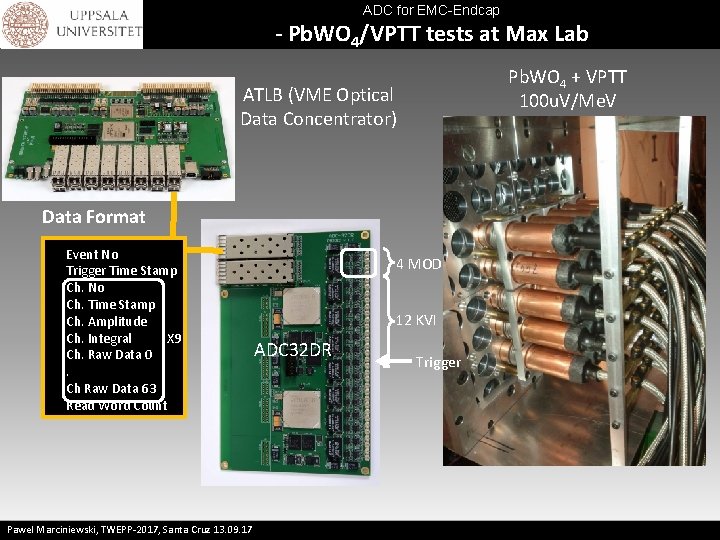

ADC for EMC-Endcap - Pb. WO 4/VPTT tests at Max Lab Pb. WO 4 + VPTT 100 u. V/Me. V ATLB (VME Optical Data Concentrator) Data Format Event No Trigger Time Stamp Ch. No Ch. Time Stamp Ch. Amplitude Ch. Integral X 9 Ch. Raw Data 0. Ch Raw Data 63 Read Word Count Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 4 MOD 12 KVI ADC 32 DR Trigger

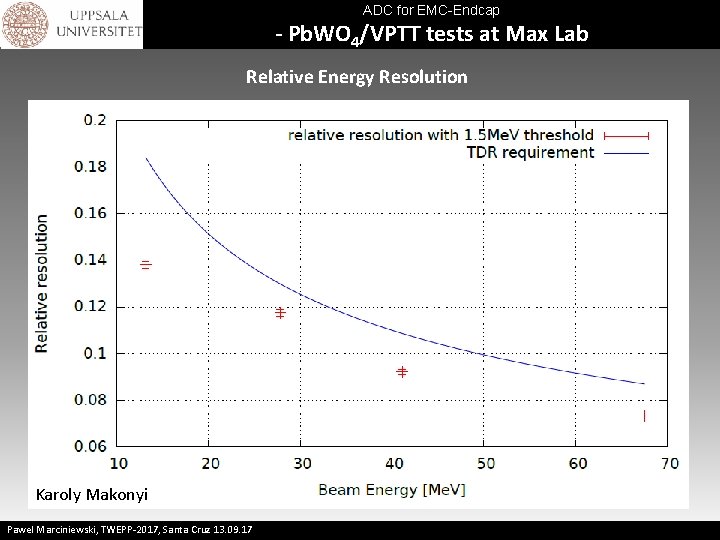

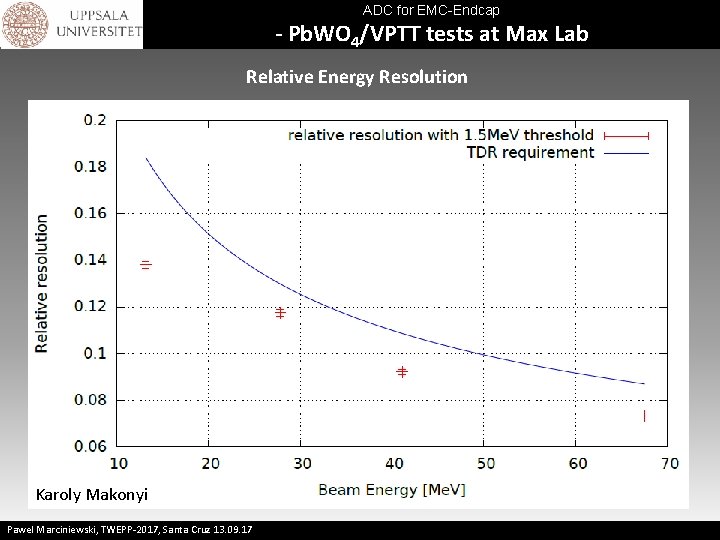

ADC for EMC-Endcap - Pb. WO 4/VPTT tests at Max Lab Relative Energy Resolution Karoly Makonyi Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

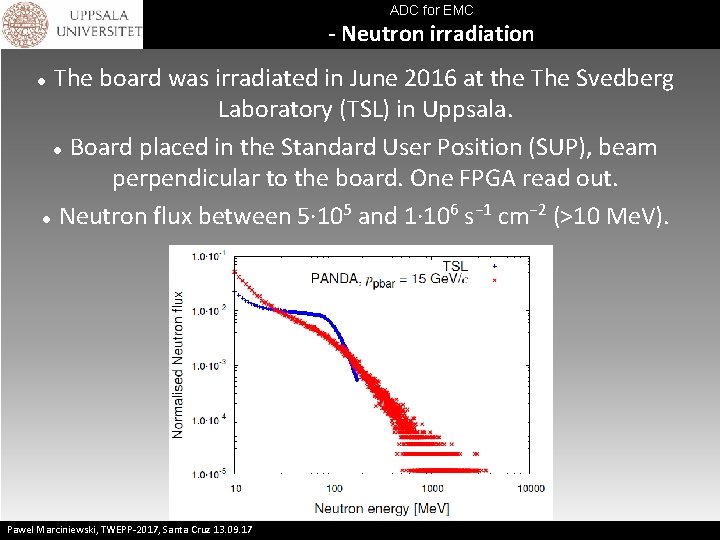

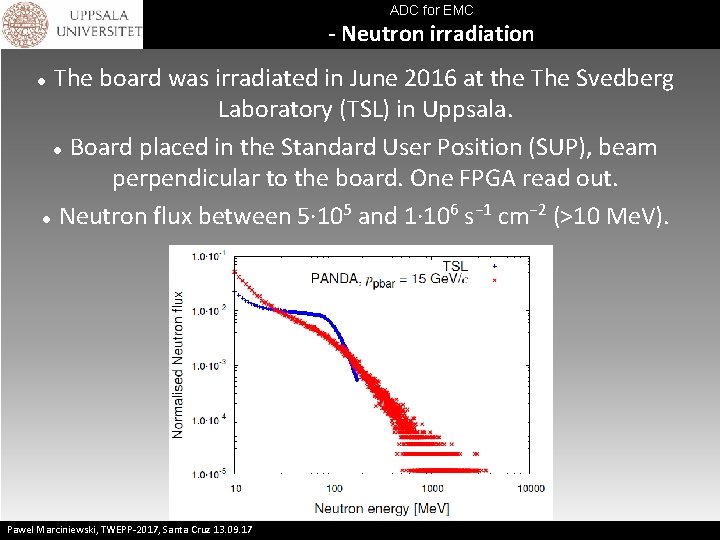

ADC for EMC - Neutron irradiation The board was irradiated in June 2016 at the The Svedberg Laboratory (TSL) in Uppsala. Board placed in the Standard User Position (SUP), beam perpendicular to the board. One FPGA read out. 5 6 − 1 Neutron flux between 5· 10 and 1· 10 s cm− 2 (>10 Me. V). Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

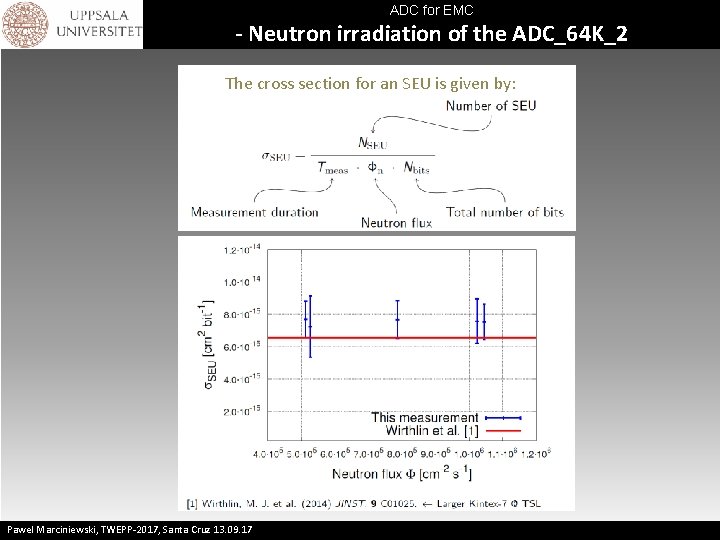

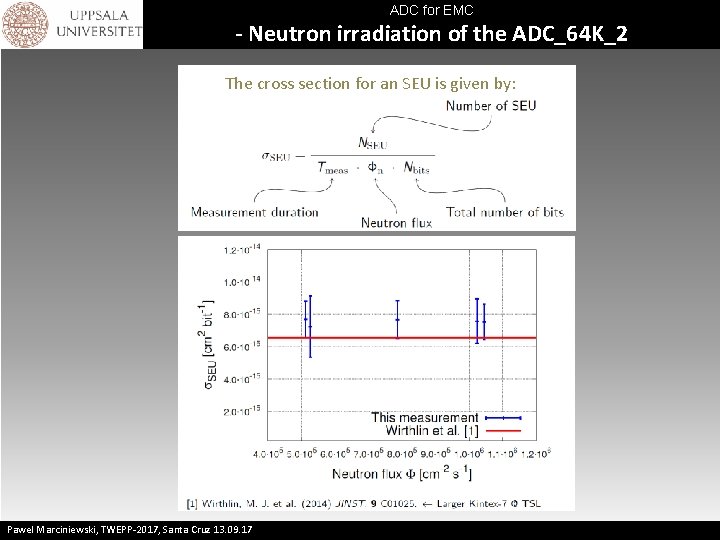

ADC for EMC - Neutron irradiation of the ADC_64 K_2 The cross section for an SEU is given by: Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

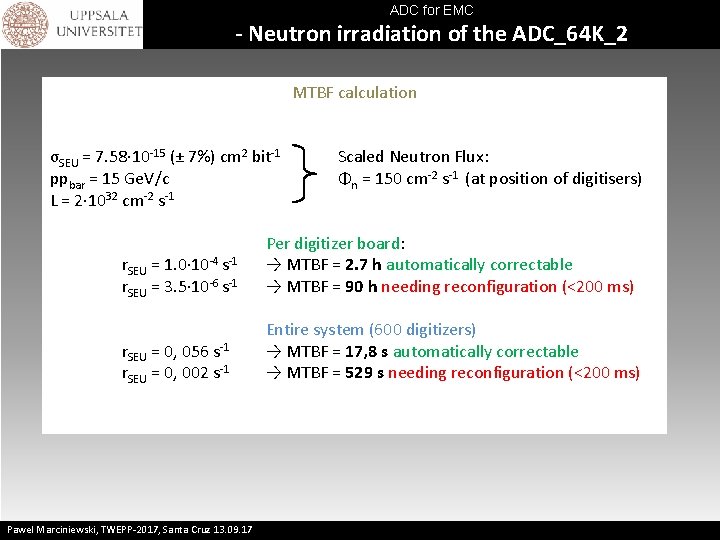

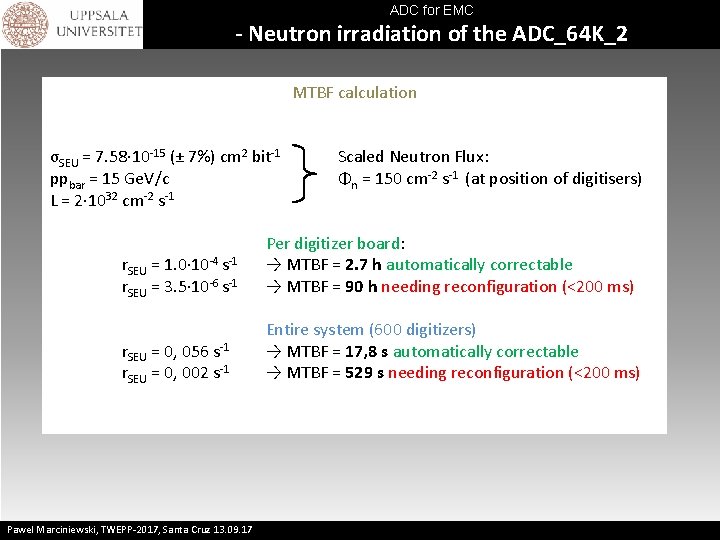

ADC for EMC - Neutron irradiation of the ADC_64 K_2 MTBF calculation σSEU = 7. 58· 10 -15 (± 7%) cm 2 bit-1 ppbar = 15 Ge. V/c L = 2· 1032 cm-2 s-1 Scaled Neutron Flux: Φn = 150 cm-2 s-1 (at position of digitisers) r. SEU = 1. 0· 10 -4 s-1 r. SEU = 3. 5· 10 -6 s-1 Per digitizer board: → MTBF = 2. 7 h automatically correctable → MTBF = 90 h needing reconfiguration (<200 ms) r. SEU = 0, 056 s-1 r. SEU = 0, 002 s-1 Entire system (600 digitizers) → MTBF = 17, 8 s automatically correctable → MTBF = 529 s needing reconfiguration (<200 ms) Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

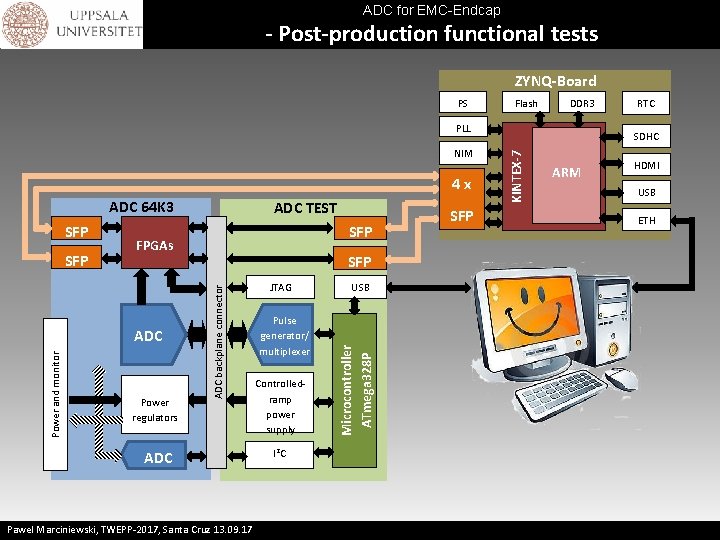

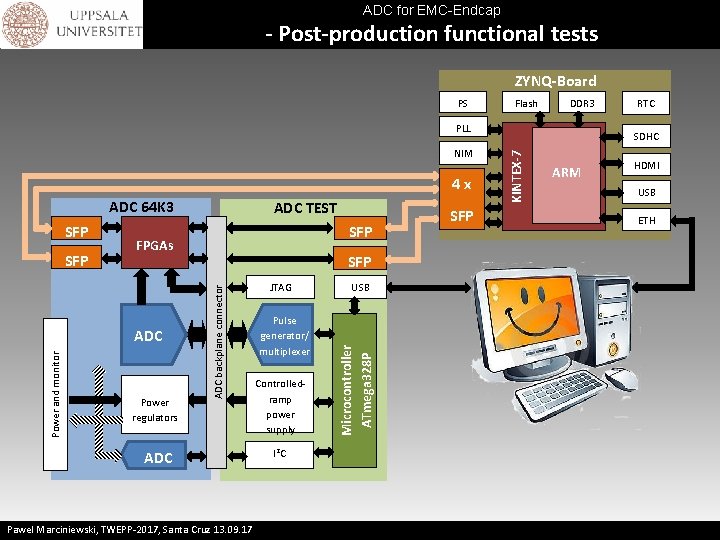

ADC for EMC-Endcap - Post-production functional tests ZYNQ-Board PS Flash DDR 3 PLL 4 x ADC 64 K 3 Power and monitor ADC Power regulators SFP ADC Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 JTAG Pulse generator/ multiplexer Controlledramp power supply I 2 C USB Microcontroller ATmega 328 P SFP FPGAs ADC backplane connector SFP ADC TEST SFP SDHC KINTEX-7 NIM RTC ARM HDMI USB ETH

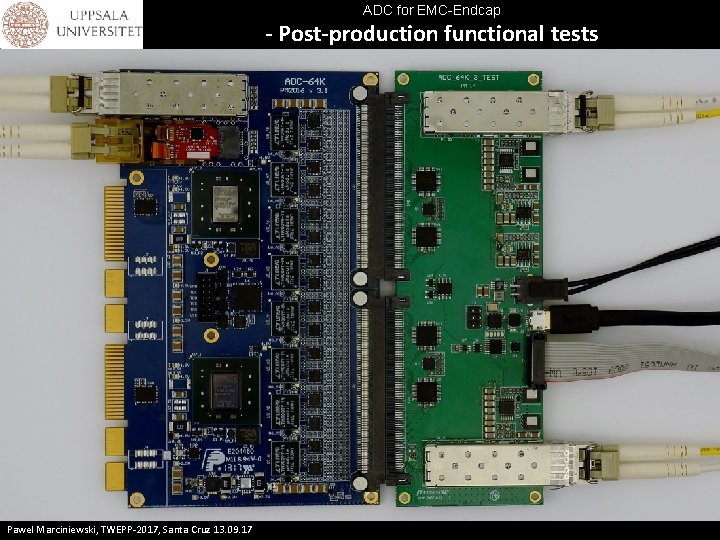

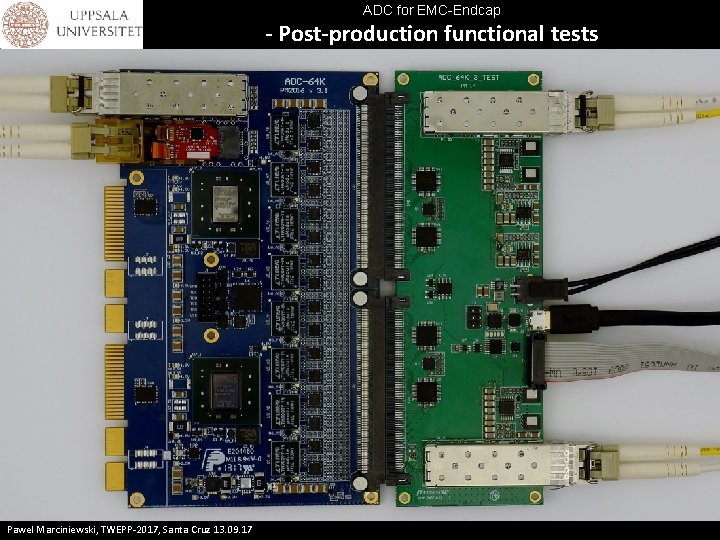

ADC for EMC-Endcap - Post-production functional tests Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

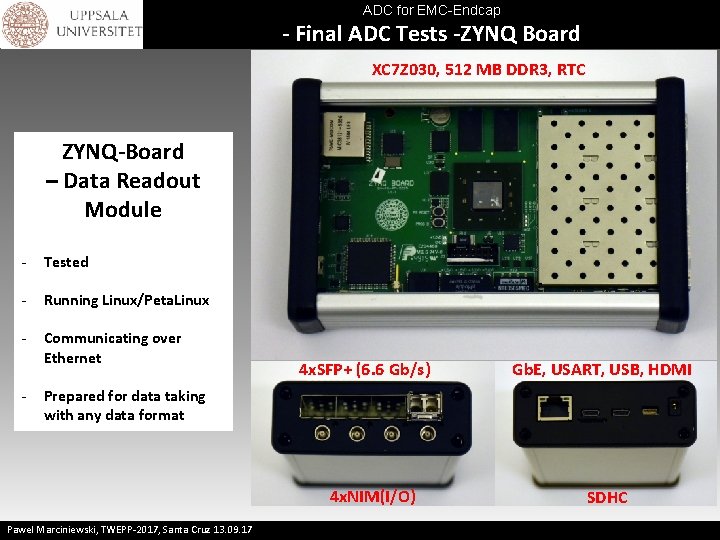

ADC for EMC-Endcap - ZYNQ Board ZYNQ-Board – Data Readout Module - Tested - Running Linux - Communicating over Ethernet - Prepared for data taking with any data format Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

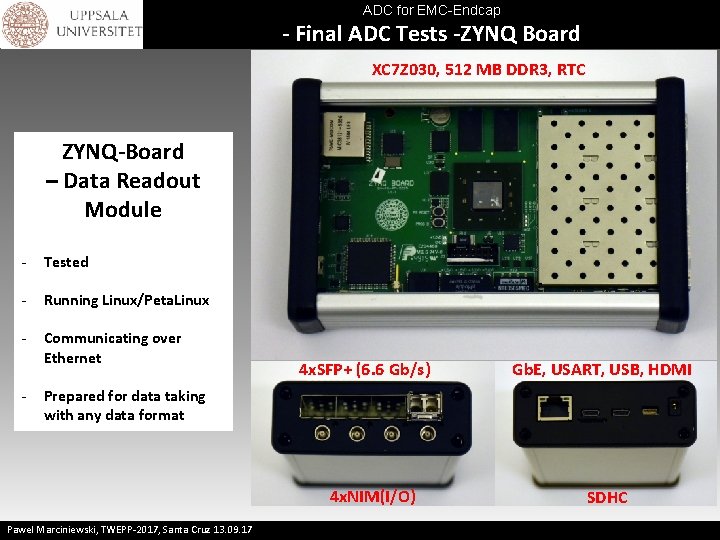

ADC for EMC-Endcap - Final ADC Tests -ZYNQ Board XC 7 Z 030, 512 MB DDR 3, RTC ZYNQ-Board – Data Readout Module - Tested - Running Linux/Peta. Linux - Communicating over Ethernet - 4 x. SFP+ (6. 6 Gb/s) Gb. E, USART, USB, HDMI Prepared for data taking with any data format 4 x. NIM(I/O) Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 SDHC

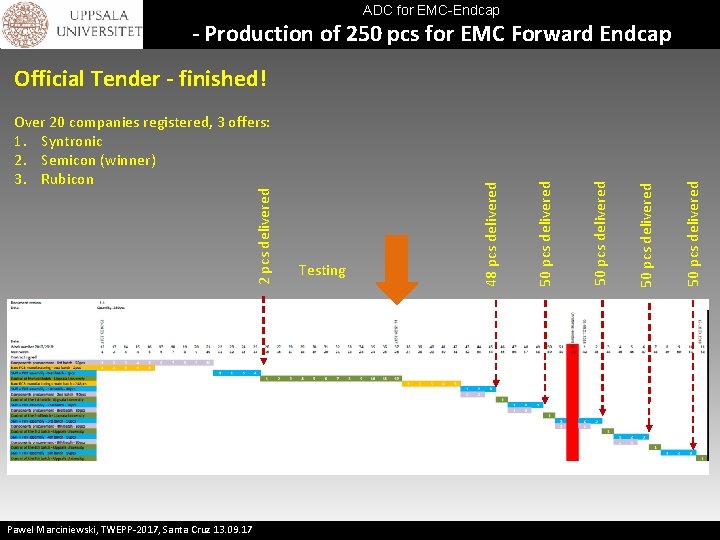

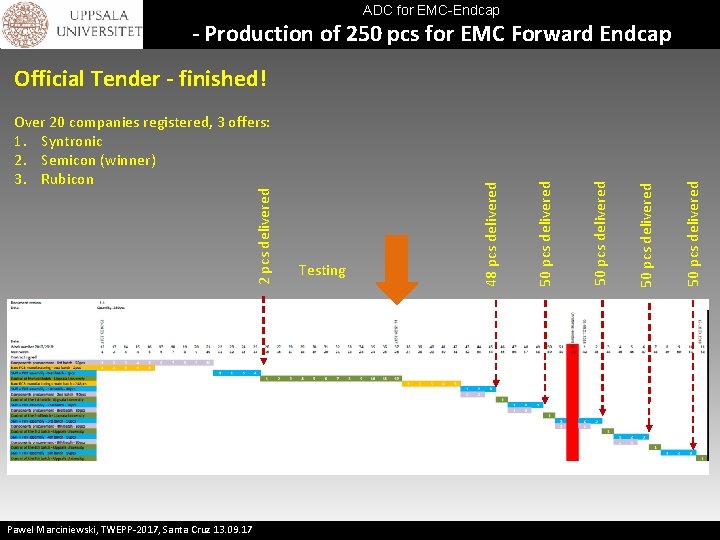

ADC for EMC-Endcap - Production of 250 pcs for EMC Forward Endcap Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17 50 pcs delivered Testing 50 pcs delivered 2 pcs delivered Over 20 companies registered, 3 offers: 1. Syntronic 2. Semicon (winner) 3. Rubicon 48 pcs delivered Official Tender - finished!

ADC for EMC-Endcap - Manpower Hardware design Test software Uppsala - Pawel Marciniewski - Filza Saleem Software/analysis Stockholm - Markus Preston, Karoly Makonyi KVI Groningen Firmware/software - Peter Schakel, Myroslav Kavatsyuk Uni Bonn Firmware/software - Johannes Muellers Uni Bochum Software -/analysis - Malte Albrecht Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17

ADC for EMC-Endcap Thank You ! Pawel Marciniewski, TWEPP-2017, Santa Cruz 13. 09. 17