Activity Report on LAMBs Tests and Developement Hikmat

Activity Report on LAMBs Tests and Developement Hikmat Nasimi – Marco Piendibene INFN Pisa & University of Pisa IAPP Executive Board Meeting 13/10/2016

Summary • AM System • LAMB Tests • VHDL and Software Development

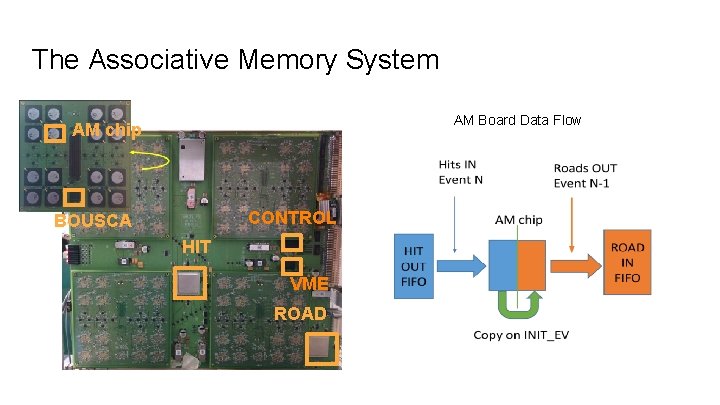

The Associative Memory System AM Board Data Flow AM chip CONTROL BOUSCA HIT VME ROAD

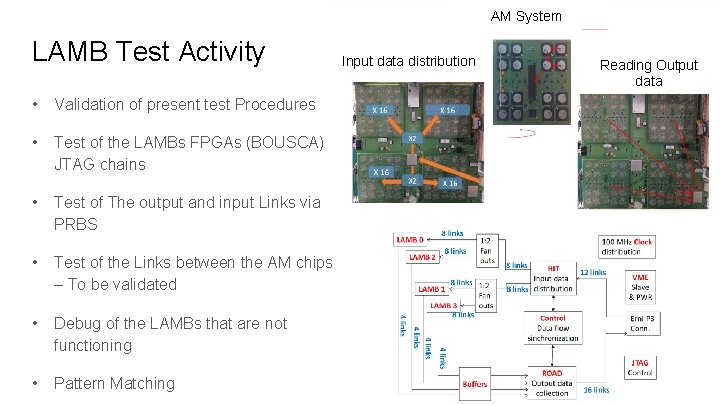

AM System LAMB Test Activity • Validation of present test Procedures • Test of the LAMBs FPGAs (BOUSCA), JTAG chains • Test of The output and input Links via PRBS • Test of the Links between the AM chips – To be validated • Debug of the LAMBs that are not functioning • Pattern Matching Input data distribution Reading Output data

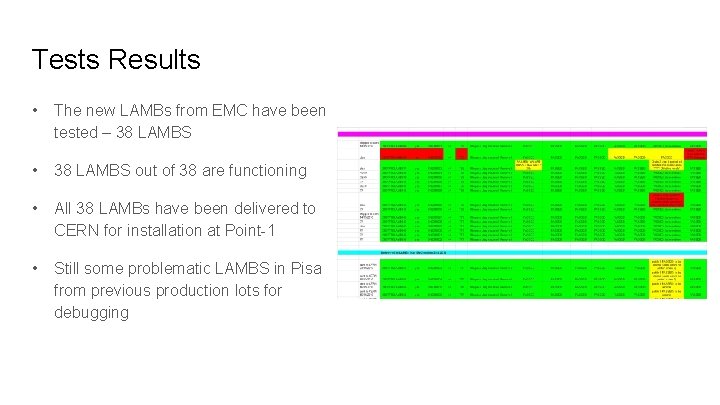

Tests Results • The new LAMBs from EMC have been tested – 38 LAMBS • 38 LAMBS out of 38 are functioning • All 38 LAMBs have been delivered to CERN for installation at Point-1 • Still some problematic LAMBS in Pisa from previous production lots for debugging

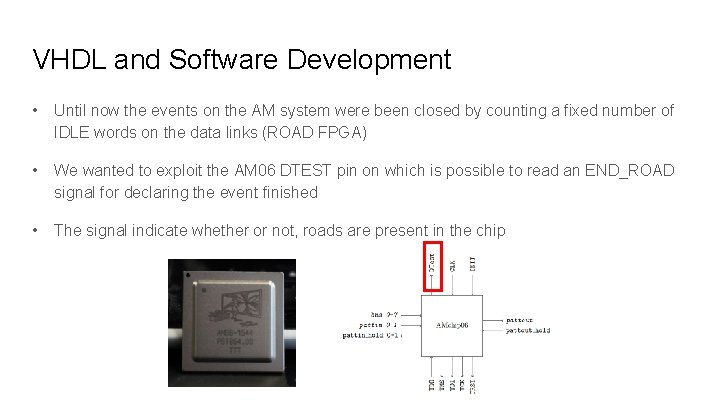

VHDL and Software Development • Until now the events on the AM system were been closed by counting a fixed number of IDLE words on the data links (ROAD FPGA) • We wanted to exploit the AM 06 DTEST pin on which is possible to read an END_ROAD signal for declaring the event finished • The signal indicate whether or not, roads are present in the chip

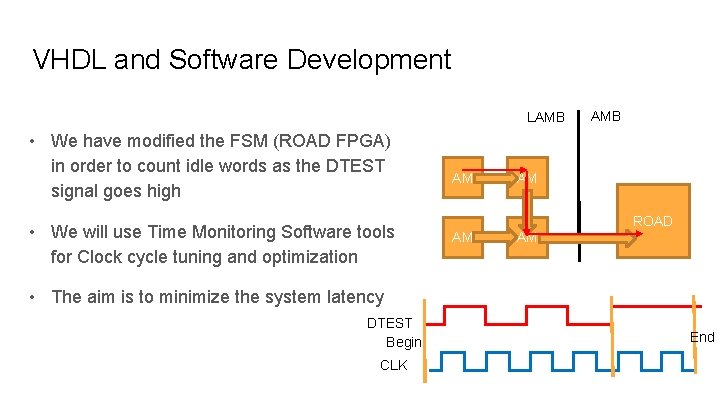

VHDL and Software Development LAMB • We have modified the FSM (ROAD FPGA) in order to count idle words as the DTEST signal goes high • We will use Time Monitoring Software tools for Clock cycle tuning and optimization AM AMB AM ROAD AM AM • The aim is to minimize the system latency DTEST Begin CLK End

VHDL and Software Development • The VHDL logic will be ready soon. Once the VHDL logic is ready: • Integrate the DTEST lines test with other «extra lines» such as HOLD and FREEZE lines in a dedicated software that will be part of the current AMB software package. • The Developement of this software is currently in progress • VHDL to measure the clock phase difference between two clock of the AM chip that can exits the DTEST signal in developement for the BOUSCA FPGA

Thank You

- Slides: 9