Activits ILC Saclay Activits acclrateur pas le sujet

- Slides: 25

Activités ILC à Saclay Activités accélérateur : pas le sujet de cette prés. Activité études de physique Activité R&D MAPS (voir présentation M. Winter) Activité R&D DHCAL (voir présentation C. Adloff) Activité R&D TPC Micromegas Contraintes Pixels Anodes résisitives Trigger Large prototype Futur EUDET suite (2010), FP 7 (2011 -2014? ) Synergies avec T 2 K, s. LHC Physique: réaction aux résultats du LHC et re-définition de l’ILC

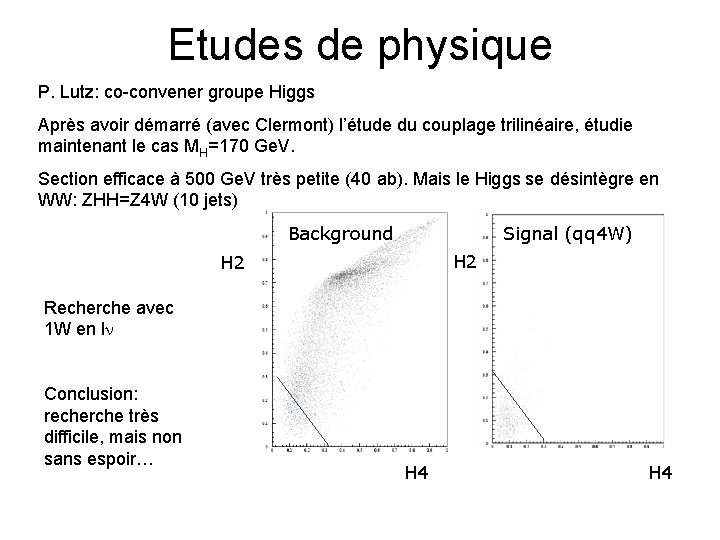

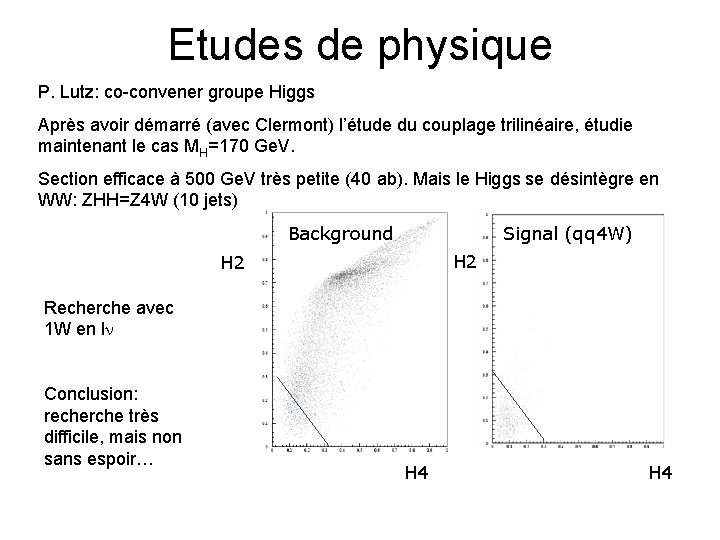

Etudes de physique P. Lutz: co-convener groupe Higgs Après avoir démarré (avec Clermont) l’étude du couplage trilinéaire, étudie maintenant le cas MH=170 Ge. V. Section efficace à 500 Ge. V très petite (40 ab). Mais le Higgs se désintègre en WW: ZHH=Z 4 W (10 jets) Background Signal (qq 4 W) H 2 Recherche avec 1 W en ln Conclusion: recherche très difficile, mais non sans espoir… H 4

TPC pour l’ILC Toute la R&D pour la TPC de l’ILC est faite dans le cadre du consortium international LCTPC Un Mo. A est en cours de signature. ~40 laboratoires, 120 physiciens Une partie des R&D 2006 -2009 est financée par l’UE: EUDET

Avantages des MPGD Les fils ne marchent pas à 3 -4 T: trop d’effet Ex. B Suppression naturelle du retour des ions (surtout Micromegas) Facilité de réalisation Robustesse (surtout ‘bulk’) Absence de cadre (pour Micromegas bulk) Rapide (plus d’ions après 30 -50 ns)

Résolution dans les MPGD La résolution est limitée par la diffusion, les fluctuations d’ionisation et les fluctuations de gain. L’avalanche est très localisée, ce qui oblige: -Soit à avoir des pixels digitaux compatibles avec la taille de l’avalanche -Soit à étaler la charge sur plusieurs pads

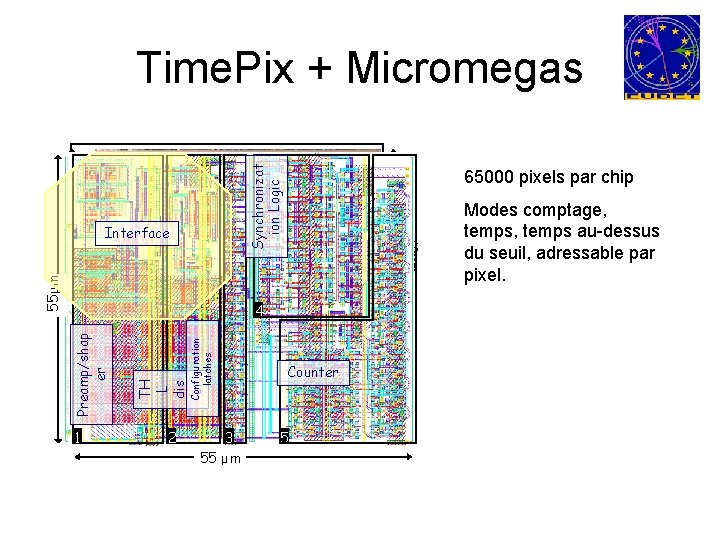

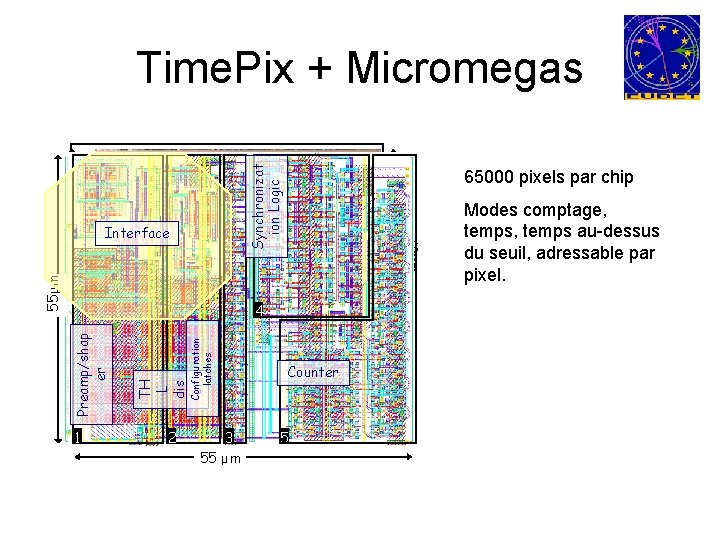

Time. Pix + Micromegas Synchronizat ion Logic 55 m 1 14080 m (pixel array) 4 latches TH L dis Configuration c. Preamp/shap er 55 μm 16120 m Interface 65000 pixels par chip 2 55 m Counter 14111 3 m 5 55 μ m Modes comptage, temps au-dessus du seuil, adressable par pixel.

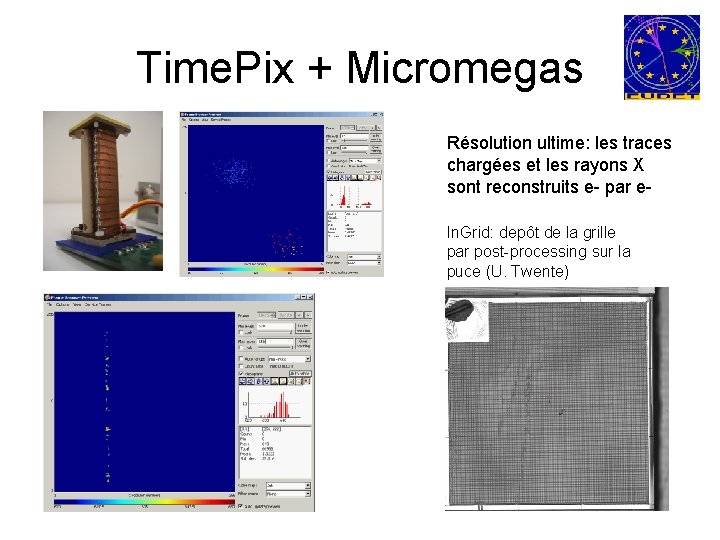

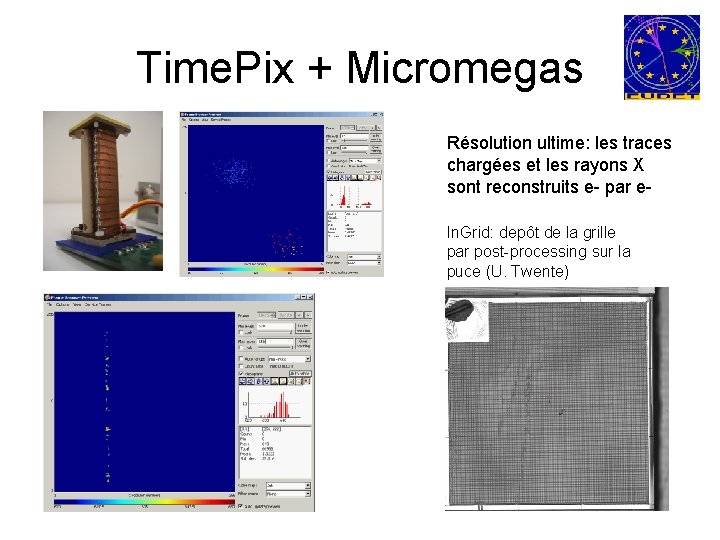

Time. Pix + Micromegas Résolution ultime: les traces chargées et les rayons X sont reconstruits e- par e. In. Grid: depôt de la grille par post-processing sur la puce (U. Twente)

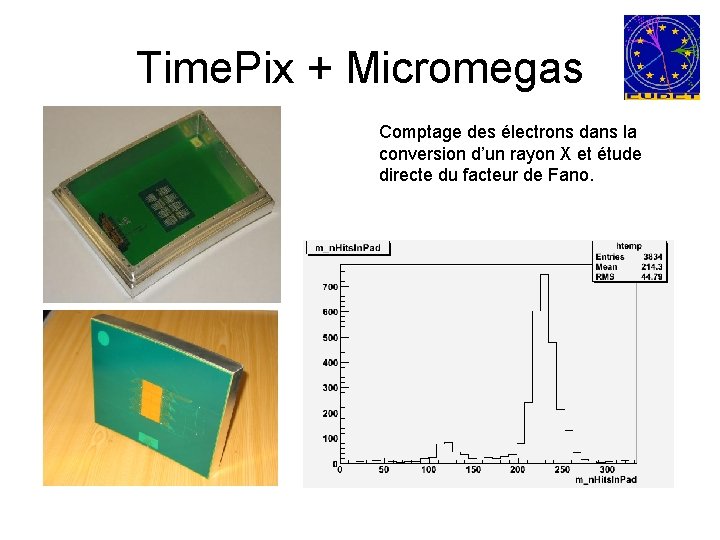

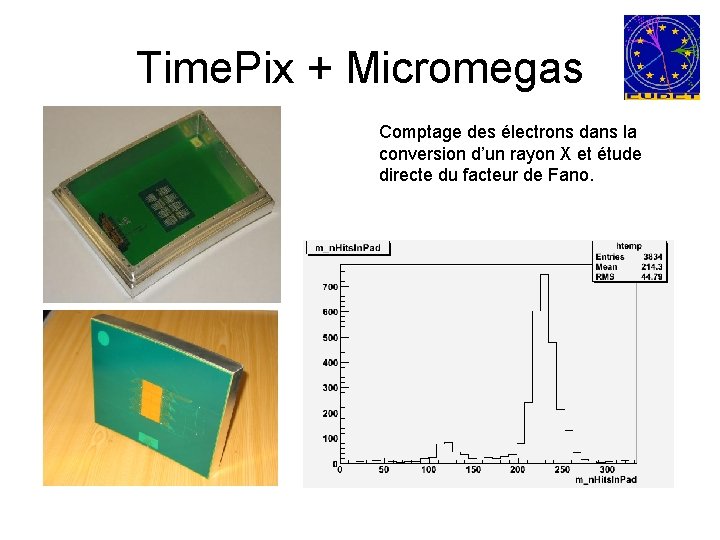

Time. Pix + Micromegas Comptage des électrons dans la conversion d’un rayon X et étude directe du facteur de Fano. Déliverable EUDET par Saclay: endplate 8 -chips

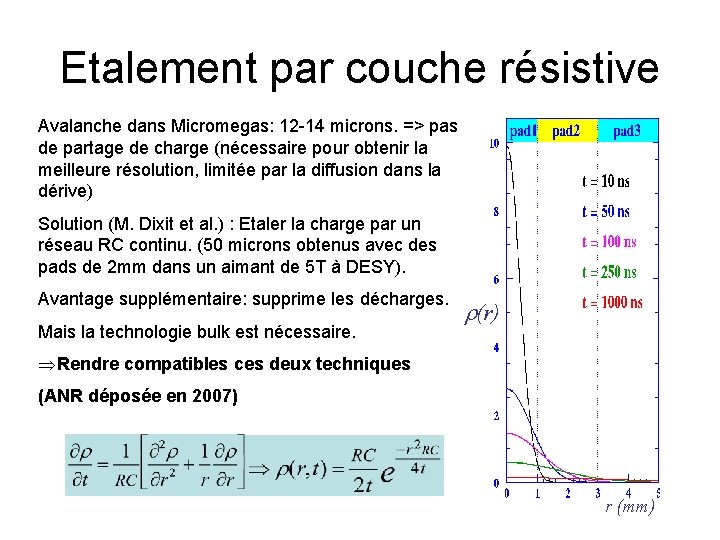

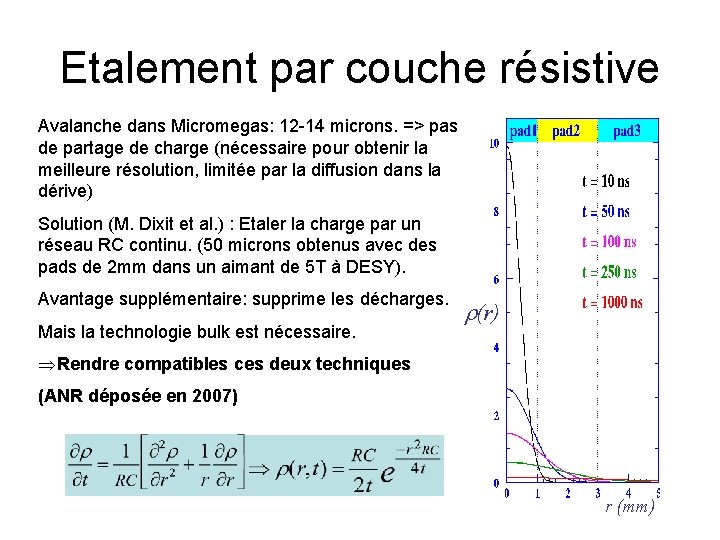

Etalement par couche résistive Avalanche dans Micromegas: 12 -14 microns. => pas de partage de charge (nécessaire pour obtenir la meilleure résolution, limitée par la diffusion dans la dérive) Solution (M. Dixit et al. ) : Etaler la charge par un réseau RC continu. (50 microns obtenus avec des pads de 2 mm dans un aimant de 5 T à DESY). Avantage supplémentaire: supprime les décharges. Mais la technologie bulk est nécessaire. (r) ÞRendre compatibles ces deux techniques (ANR déposée en 2007) r (mm)

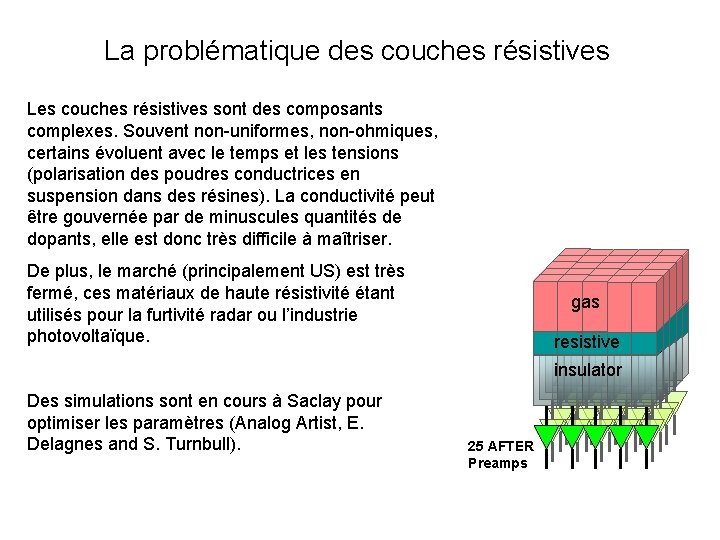

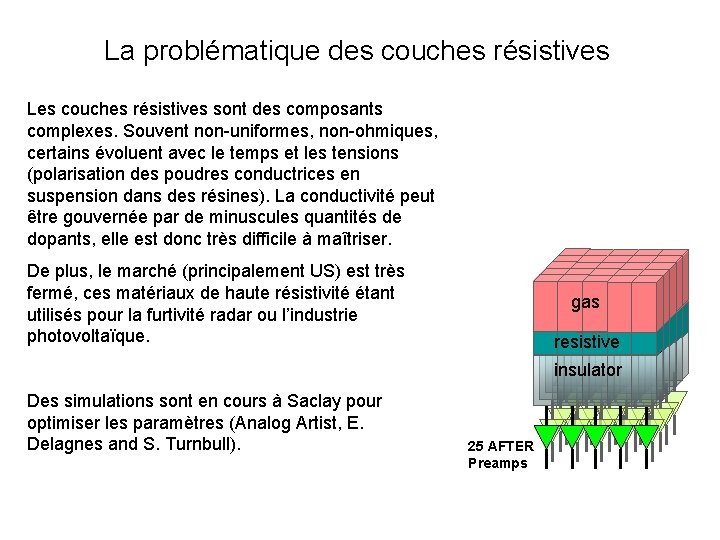

La problématique des couches résistives Les couches résistives sont des composants complexes. Souvent non-uniformes, non-ohmiques, certains évoluent avec le temps et les tensions (polarisation des poudres conductrices en suspension dans des résines). La conductivité peut être gouvernée par de minuscules quantités de dopants, elle est donc très difficile à maîtriser. De plus, le marché (principalement US) est très fermé, ces matériaux de haute résistivité étant utilisés pour la furtivité radar ou l’industrie photovoltaïque. gas resistive insulator Des simulations sont en cours à Saclay pour optimiser les paramètres (Analog Artist, E. Delagnes and S. Turnbull). 25 AFTER Preamps

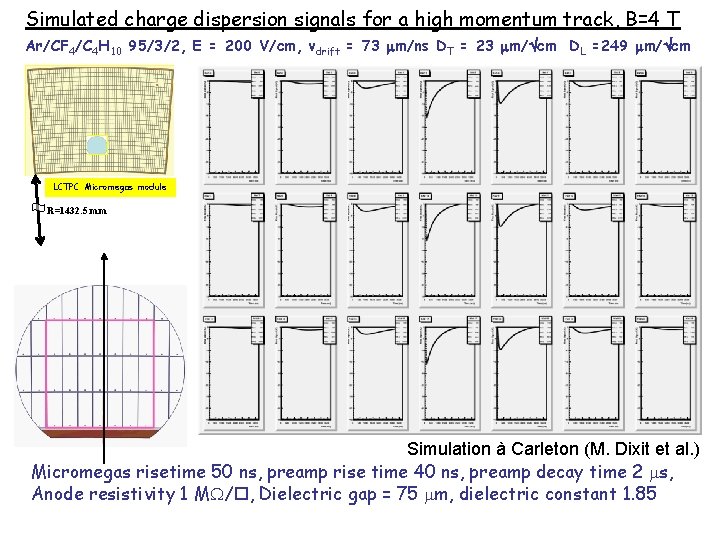

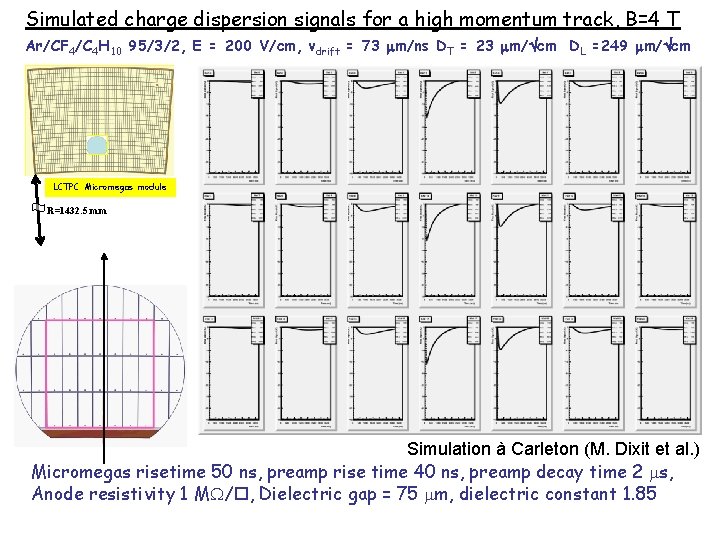

Simulated charge dispersion signals for a high momentum track, B=4 T Ar/CF 4/C 4 H 10 95/3/2, E = 200 V/cm, vdrift = 73 m/ns DT = 23 m/ cm DL =249 m/ cm LCTPC Micromegas module R=1432. 5 mm Simulation à Carleton (M. Dixit et al. ) Micromegas risetime 50 ns, preamp rise time 40 ns, preamp decay time 2 s, Anode resistivity 1 M / , Dielectric gap = 75 m, dielectric constant 1. 85

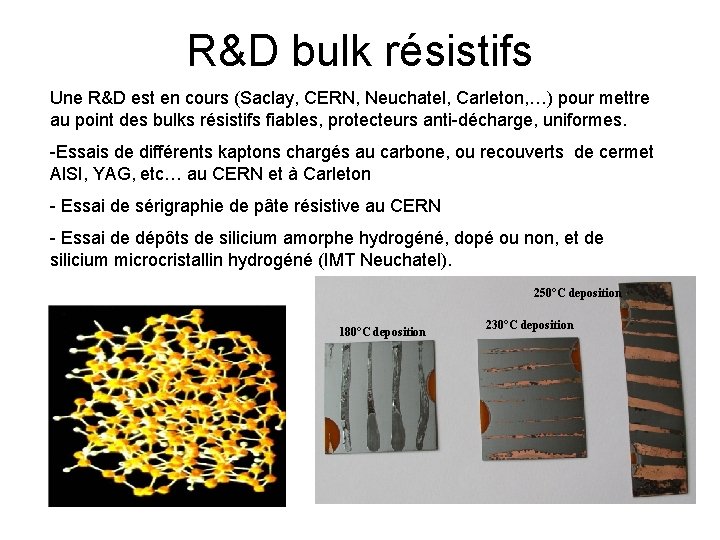

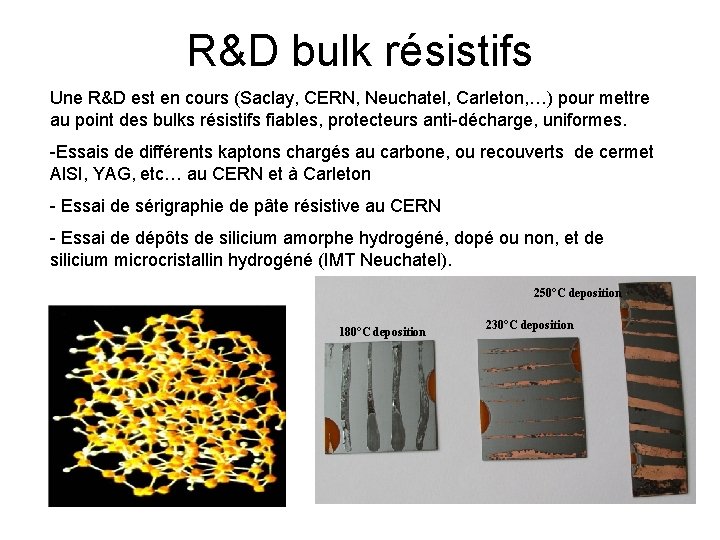

R&D bulk résistifs Une R&D est en cours (Saclay, CERN, Neuchatel, Carleton, …) pour mettre au point des bulks résistifs fiables, protecteurs anti-décharge, uniformes. -Essais de différents kaptons chargés au carbone, ou recouverts de cermet Al. SI, YAG, etc… au CERN et à Carleton - Essai de sérigraphie de pâte résistive au CERN - Essai de dépôts de silicium amorphe hydrogéné, dopé ou non, et de silicium microcristallin hydrogéné (IMT Neuchatel). 250°C deposition 180°C deposition 230°C deposition

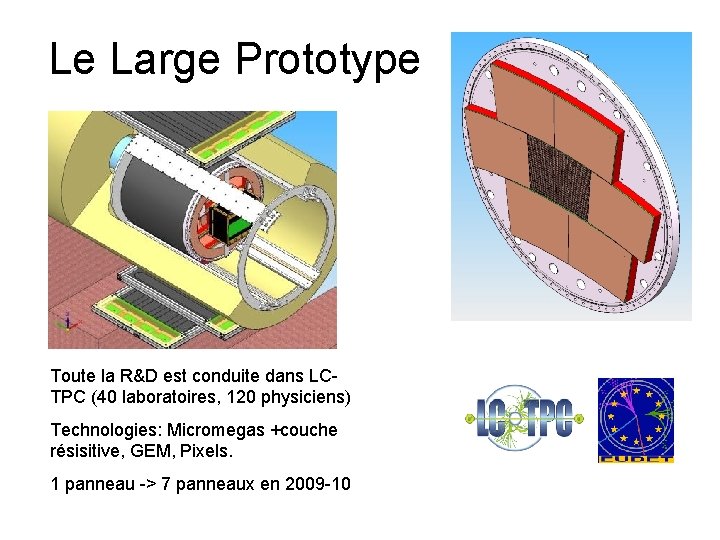

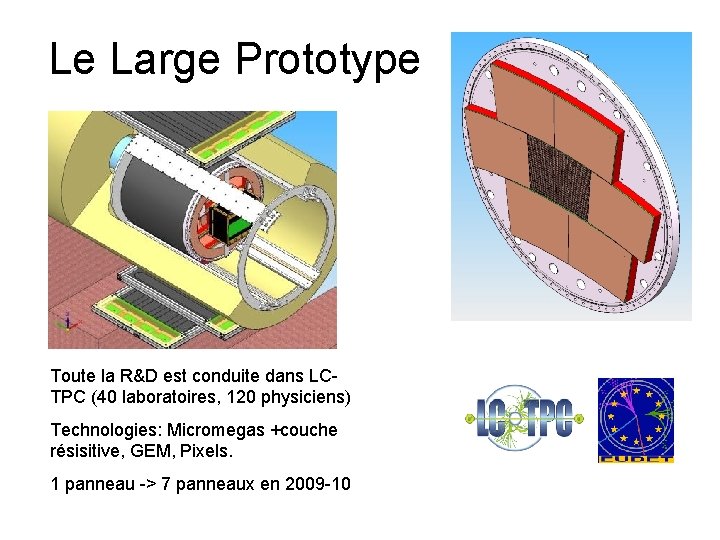

Le Large Prototype Toute la R&D est conduite dans LCTPC (40 laboratoires, 120 physiciens) Technologies: Micromegas +couche résisitive, GEM, Pixels. 1 panneau -> 7 panneaux en 2009 -10

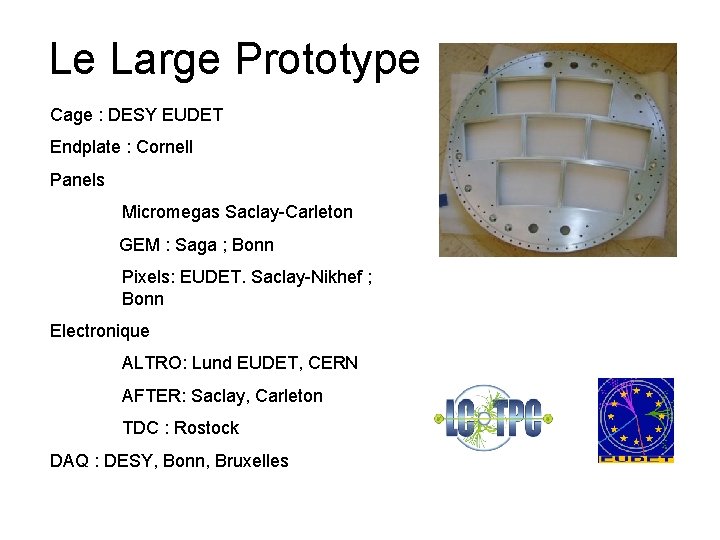

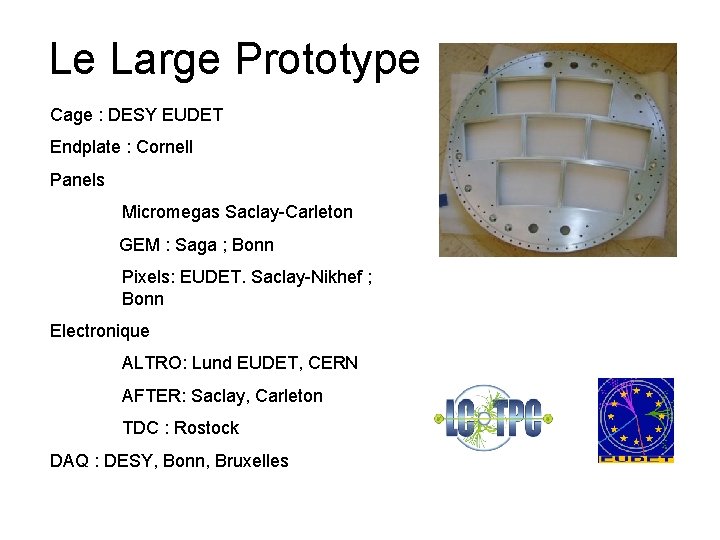

Le Large Prototype Cage : DESY EUDET Endplate : Cornell Panels Micromegas Saclay-Carleton GEM : Saga ; Bonn Pixels: EUDET. Saclay-Nikhef ; Bonn Electronique ALTRO: Lund EUDET, CERN AFTER: Saclay, Carleton TDC : Rostock DAQ : DESY, Bonn, Bruxelles

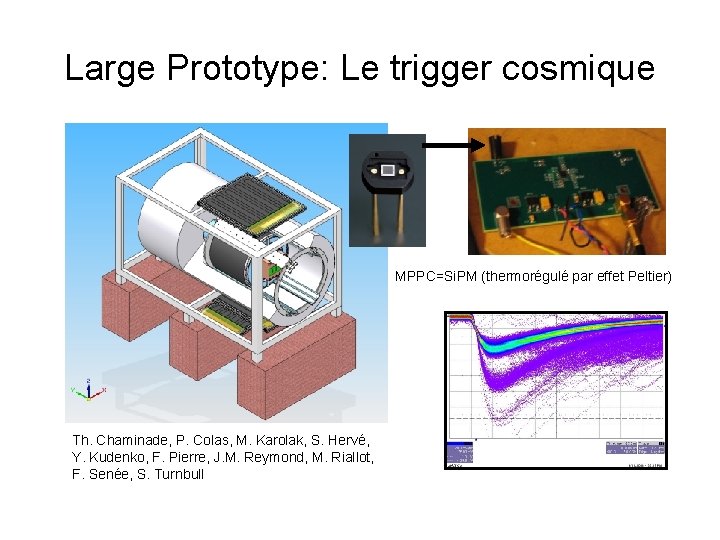

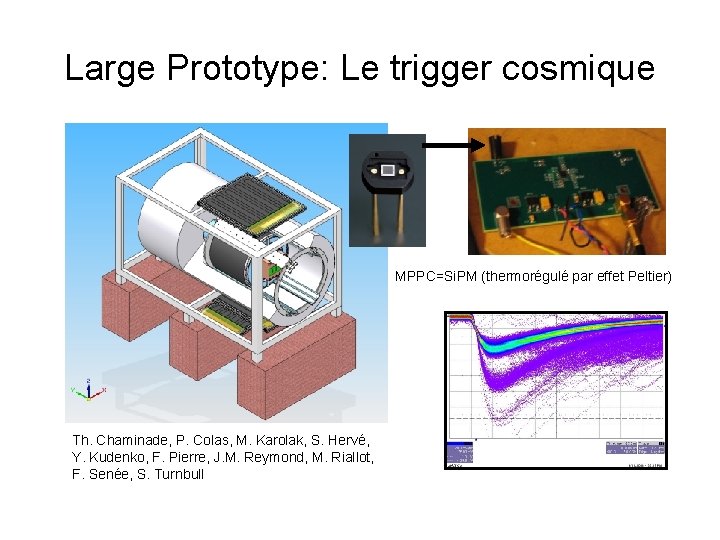

Large Prototype: Le trigger cosmique MPPC=Si. PM (thermorégulé par effet Peltier) Th. Chaminade, P. Colas, M. Karolak, S. Hervé, Y. Kudenko, F. Pierre, J. M. Reymond, M. Riallot, F. Senée, S. Turnbull

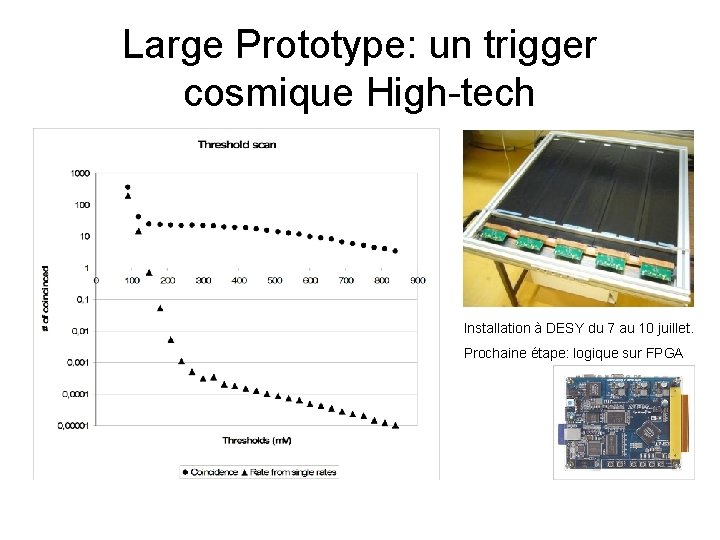

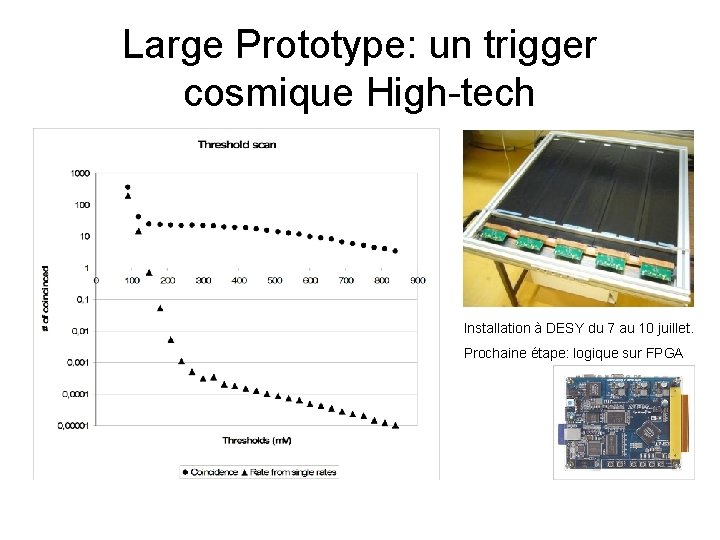

Large Prototype: un trigger cosmique High-tech Installation à DESY du 7 au 10 juillet. Prochaine étape: logique sur FPGA

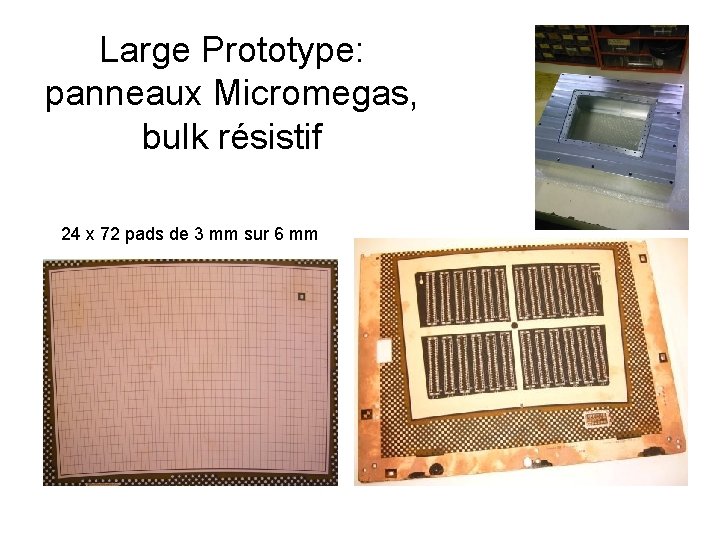

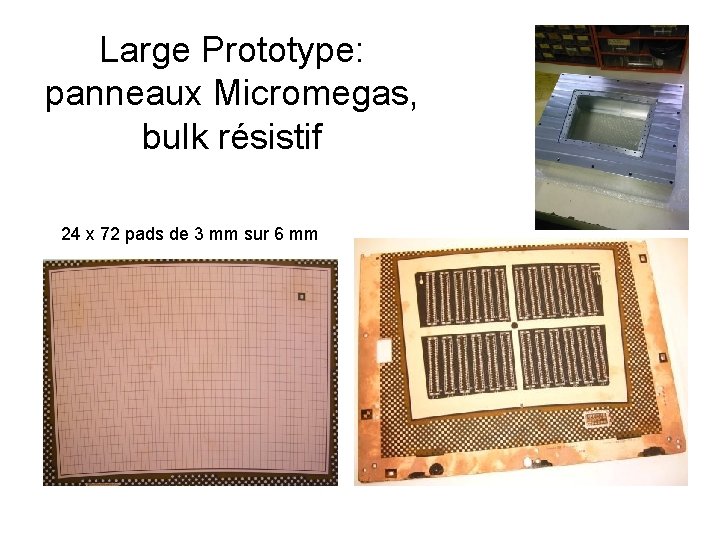

Large Prototype: panneaux Micromegas, bulk résistif 24 x 72 pads de 3 mm sur 6 mm

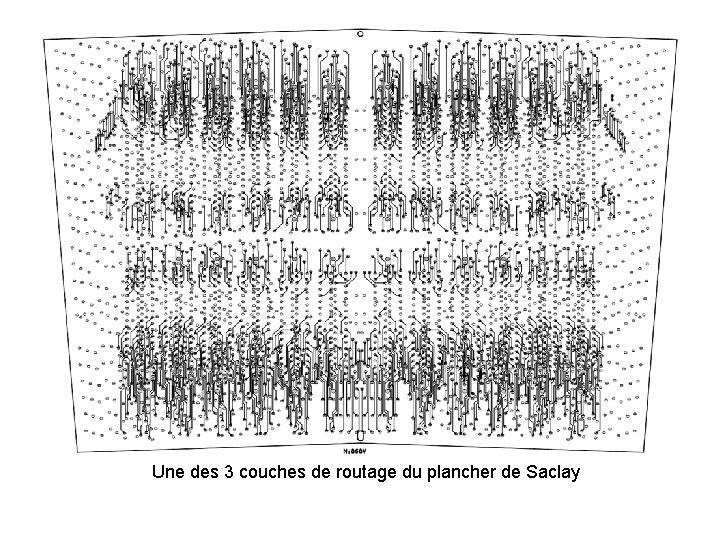

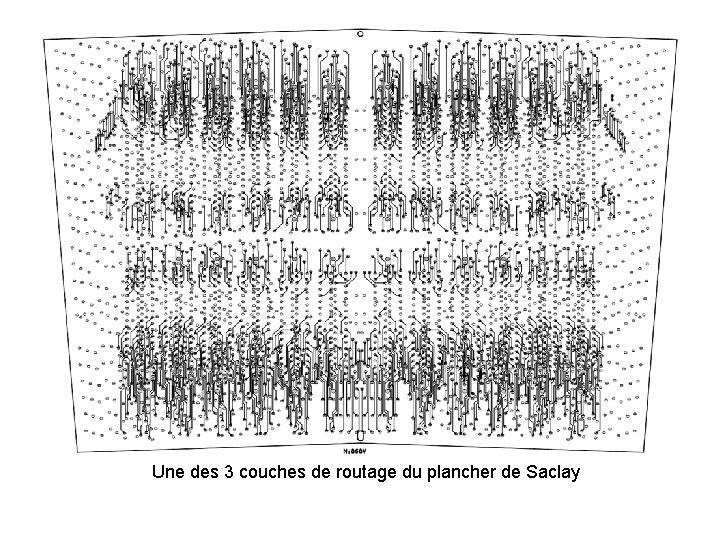

Une des 3 couches de routage du plancher de Saclay

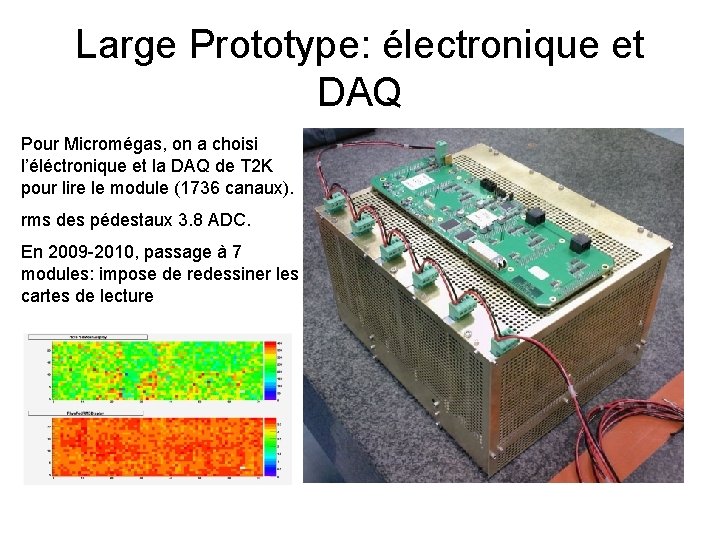

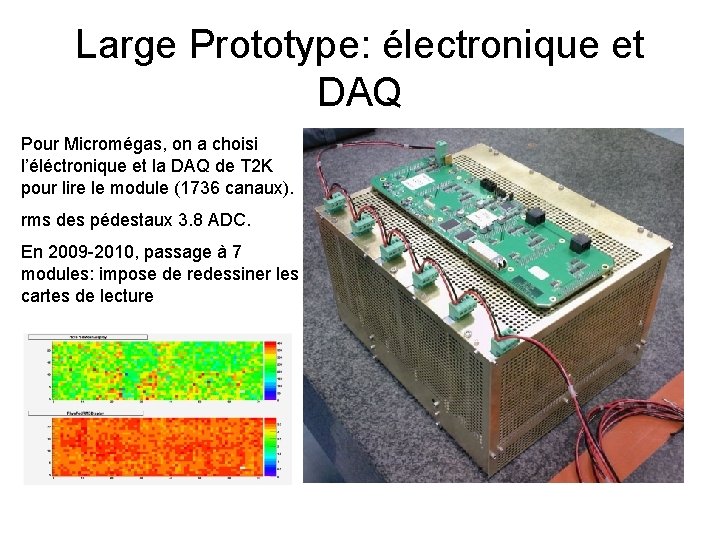

Large Prototype: électronique et DAQ Pour Micromégas, on a choisi l’éléctronique et la DAQ de T 2 K pour lire le module (1736 canaux). rms des pédestaux 3. 8 ADC. En 2009 -2010, passage à 7 modules: impose de redessiner les cartes de lecture

Le groupe LC-TPC à Saclay D. Attié, M. Chefdeville, P. Colas, E. Delagnes, A. Giganon, I. Giomataris, M. Titov, S. Turnbull Renfort technique : T. Chaminade, X. Coppolani, J. -M. Reymond, M. Riallot, F. Senée + synergie électronique T 2 K. Nouveaux locaux (CSTS 30 juin 2007): labo TPC (test de modules, tests électronique, Time. Pix, boîtes à gaz, système de 3 gaz + prémélangés.

Le groupe LC-TPC à Saclay En septembre: P. Colas, E. Delagnes, A. Giganon, I. Giomataris, M. Titov (temps très partiel) D. Attié : fin de contrat 11 octobre (embauche 2009? )– M. Chefdeville: soutenance en novembre – S. Turnbull fin de contrat 30 août – F. Senée : mutation : situation catastrophique. Suite du Large prototype, études fines de et avec Time. Pix+In. Grid, nouvelles synergies (polarimétrie, RESIST, R&D muons SLHC, 2 b sans n). Nouveaux locaux (CSTS 30 juin 2007): labo TPC (test de modules, tests électronique, Time. Pix, boîtes à gaz, système de 3 gaz + prémélangés.

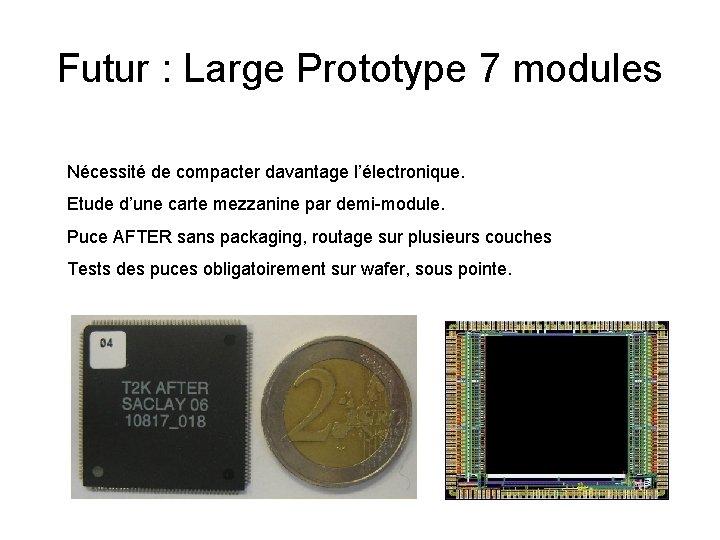

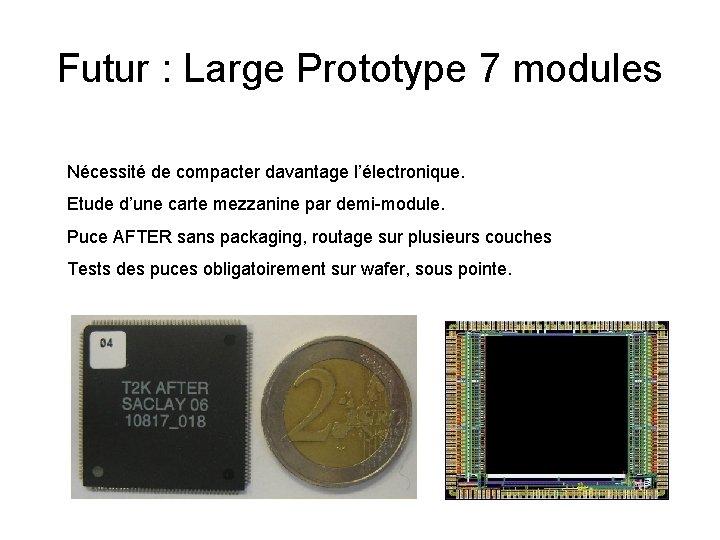

Futur : Large Prototype 7 modules Nécessité de compacter davantage l’électronique. Etude d’une carte mezzanine par demi-module. Puce AFTER sans packaging, routage sur plusieurs couches Tests des puces obligatoirement sur wafer, sous pointe.

Futur EUDET prolongé d’un an? (sans argent supplémentaire? ) FP 7: Dev. Det 2009 -2012 probablement rejeté. Nouvelle candidature en 2010? De toutes façons, Dev. Det tel quel ne représentait pas la masse financière critique par groupe ou par projet (typiquement 60 keuro par projet et par labo sur 4 ans) Un futur projet FP 7 n’a pas de sens s’il correspond à moins de 200 Keuro par labo ou groupe de labos proches sur les 4 ans: davantage sélectionner les labos? Fixer des priorités? Réduire le périmètre? Ne pas utiliser les fonds pour financer le CERN, par exemple? EUDET a bien marché dans l’ensemble (7 M€ pour ILC seul) Véritable problème de financement des postdocs ou des stages longue durée à Saclay.

Futur Résultats du LHC dans environ 2 ans (Paris ICHEP 2010? ) Quoique la justification de l’ILC n’attende pas ces résultats, on devrait être en mesure de spécifier quel ILC, quels options, quel programme Energie-Lumi sera le plus utile à éclairer/compléter les résultats du LHC. Une période passionante va s’ouvrir.