ACTIVITIES AT LBNL Carl Grace IC Group Leader

ACTIVITIES AT LBNL Carl Grace, IC Group Leader crgrace@lbl. gov January 25, 2020 Advancing Science by Design Activities at LBNL 1 ENGINEERING DIVISION

Intro to LBNL IC Group • The Integrated Circuits Group at LBNL maintains a comprehensive mixedsignal ASIC design capability and specializes in multi-channel, high-speed detector readout ASICs that operate in extreme environments (high-radiation, low temperature, in-vacuum, etc. ) • We deliver high-quality integrated circuit solutions to address challenging requirements where commercial solutions do not exist • We are tightly integrated with the Semiconductor Detector and Electronic Systems Groups at LBNL to give us the capability to provide a sensor-tosoftware solution (or anywhere in between) • We engage with our partners at a variety of levels, from implementing your design in silicon to conducting joint R&D to establish specifications for your custom ASIC • We have multiple decades of experience working closely with scientists, engineers and industrial partners to jointly develop custom readout solutions to help them meet their data acquisition requirements Advancing Science by Design Activities at LBNL 2 ENGINEERING DIVISION

Key Design Areas The LBNL IC Group currently works primarily in four areas: 1. High-Energy Physics : supported by HEP we have developed integrated detector instrumentation since the late 1980 s. Member of ATLAS and RD 53 collaborations. Heavily involved in DUNE (collaboration with BNL and FNAL). 2. Scientific Imaging: • High-speed Active Pixel Sensors and peripheral chips primarily for electron microscopy. • Leveraging the high-resistivity CCD developments at LBNL for astronomy, we develop sensors and readout ICs for high-speed CCD cameras (soft X-ray application, e. g. LCLS-II upgrade). 3. Nuclear Science: cryogenic readout front-end ASICs for LAr neutrinoless doublebeta decay experiments and R&D toward deep-cryogenic (sub 1 K) quantum sensor readout (e. g. TES) 4. Neuroscience : We develop high-channel count readout ICs for electrocorticography (ECo. G) and penetrating extracellular readout. In addition, we develop specialized neural circuits (e. g. localized heaters and neural temperature sensors). Advancing Science by Design Activities at LBNL 3 ENGINEERING DIVISION

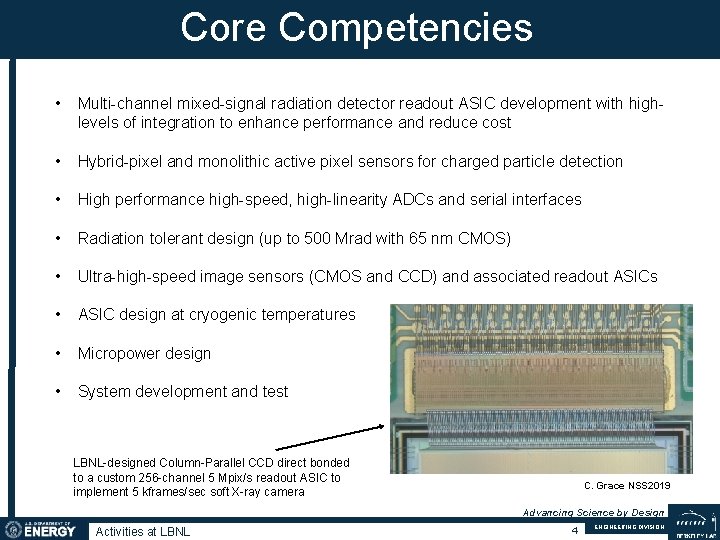

Core Competencies • Multi-channel mixed-signal radiation detector readout ASIC development with highlevels of integration to enhance performance and reduce cost • Hybrid-pixel and monolithic active pixel sensors for charged particle detection • High performance high-speed, high-linearity ADCs and serial interfaces • Radiation tolerant design (up to 500 Mrad with 65 nm CMOS) • Ultra-high-speed image sensors (CMOS and CCD) and associated readout ASICs • ASIC design at cryogenic temperatures • Micropower design • System development and test LBNL-designed Column-Parallel CCD direct bonded to a custom 256 -channel 5 Mpix/s readout ASIC to implement 5 kframes/sec soft X-ray camera C. Grace NSS 2019 Advancing Science by Design Activities at LBNL 4 ENGINEERING DIVISION

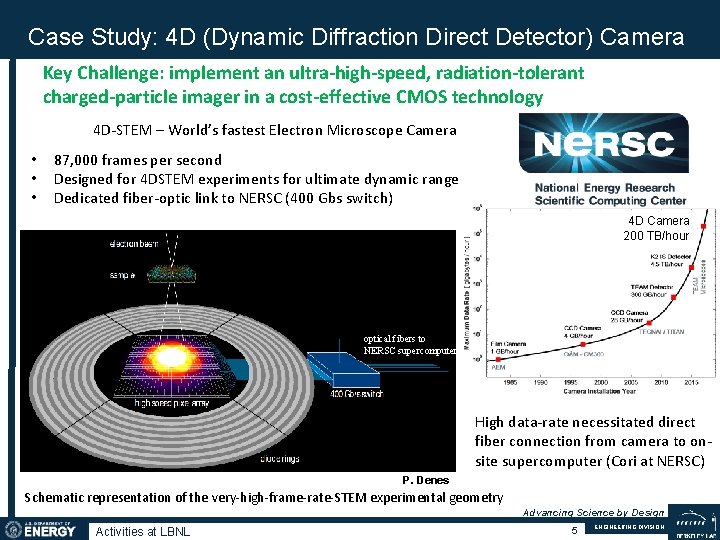

Case Study: 4 D (Dynamic Diffraction Direct Detector) Camera Key Challenge: implement an ultra-high-speed, radiation-tolerant charged-particle imager in a cost-effective CMOS technology 4 D-STEM – World’s fastest Electron Microscope Camera • • • 87, 000 frames per second Designed for 4 DSTEM experiments for ultimate dynamic range Dedicated fiber-optic link to NERSC (400 Gbs switch) 4 D Camera 200 TB/hour optical fibers to NERSC supercomputer High data-rate necessitated direct fiber connection from camera to onsite supercomputer (Cori at NERSC) P. Denes Schematic representation of the very-high-frame-rate-STEM experimental geometry Advancing Science by Design Activities at LBNL 5 ENGINEERING DIVISION

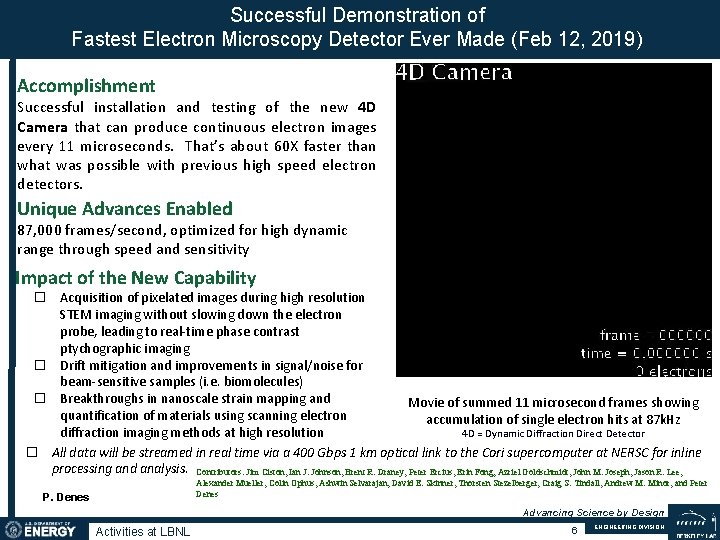

Successful Demonstration of Fastest Electron Microscopy Detector Ever Made (Feb 12, 2019) Accomplishment Successful installation and testing of the new 4 D Camera that can produce continuous electron images every 11 microseconds. That’s about 60 X faster than what was possible with previous high speed electron detectors. Unique Advances Enabled 87, 000 frames/second, optimized for high dynamic range through speed and sensitivity Impact of the New Capability � Acquisition of pixelated images during high resolution STEM imaging without slowing down the electron probe, leading to real-time phase contrast ptychographic imaging � Drift mitigation and improvements in signal/noise for beam-sensitive samples (i. e. biomolecules) � Breakthroughs in nanoscale strain mapping and Movie of summed 11 microsecond frames showing quantification of materials using scanning electron accumulation of single electron hits at 87 k. Hz diffraction imaging methods at high resolution 4 D = Dynamic Diffraction Direct Detector � All data will be streamed in real time via a 400 Gbps 1 km optical link to the Cori supercomputer at NERSC for inline processing and analysis. Contributors: Jim Ciston, Ian J. Johnson, Brent R. Draney, Peter Ercius, Erin Fong, Azriel Goldschmidt, John M. Joseph, Jason R. Lee, Alexander Mueller, Colin Ophus, Ashwin Selvarajan, David E. Skinner, Thorsten Stezelberger, Craig S. Tindall, Andrew M. Minor, and Peter Denes P. Denes Advancing Science by Design Activities at LBNL 6 ENGINEERING DIVISION

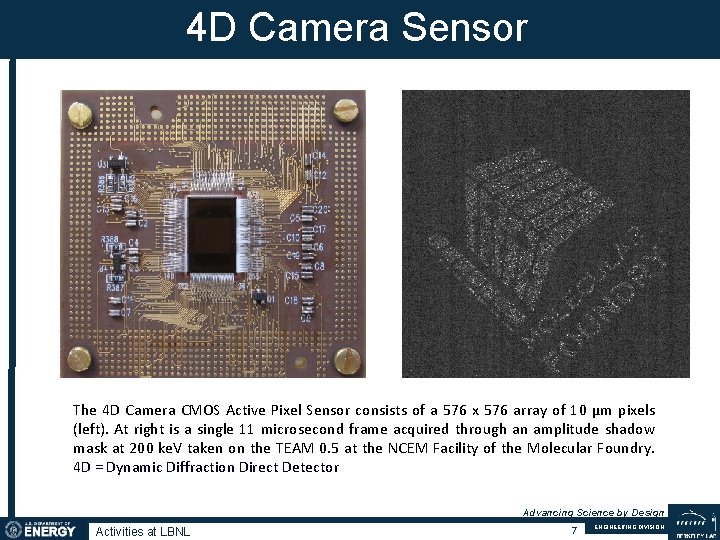

4 D Camera Sensor The 4 D Camera CMOS Active Pixel Sensor consists of a 576 x 576 array of 10 μm pixels (left). At right is a single 11 microsecond frame acquired through an amplitude shadow mask at 200 ke. V taken on the TEAM 0. 5 at the NCEM Facility of the Molecular Foundry. 4 D = Dynamic Diffraction Direct Detector Advancing Science by Design Activities at LBNL 7 ENGINEERING DIVISION

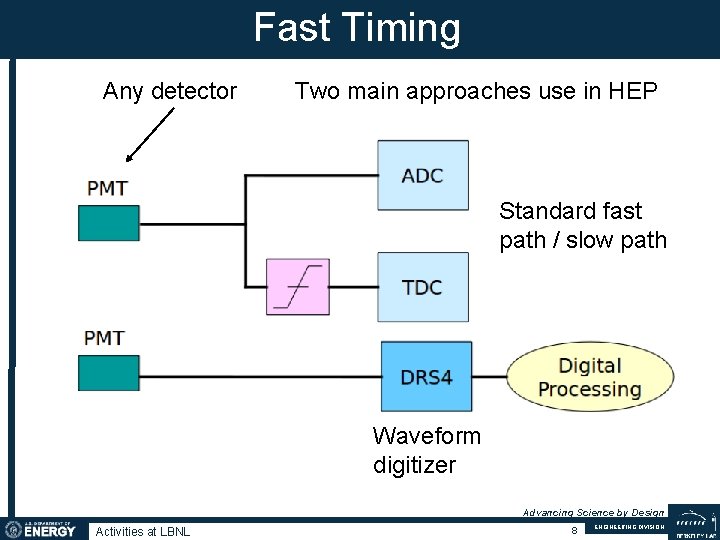

Fast Timing Any detector Two main approaches use in HEP Standard fast path / slow path Waveform digitizer Advancing Science by Design Activities at LBNL 8 ENGINEERING DIVISION

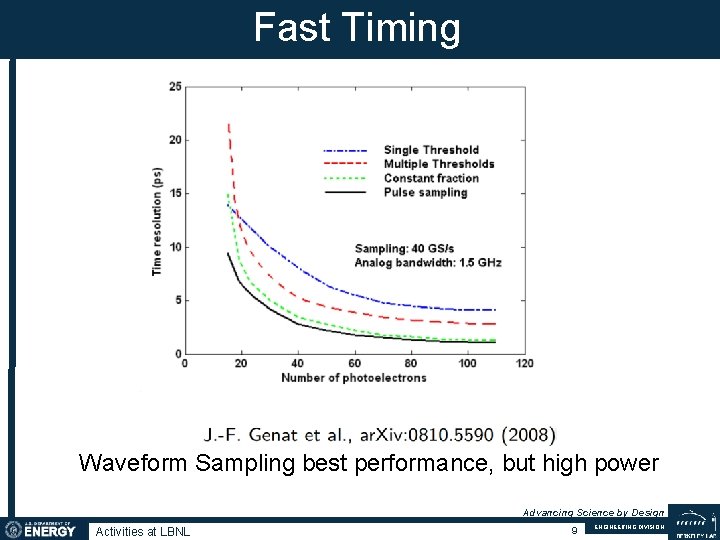

Fast Timing Waveform Sampling best performance, but high power Advancing Science by Design Activities at LBNL 9 ENGINEERING DIVISION

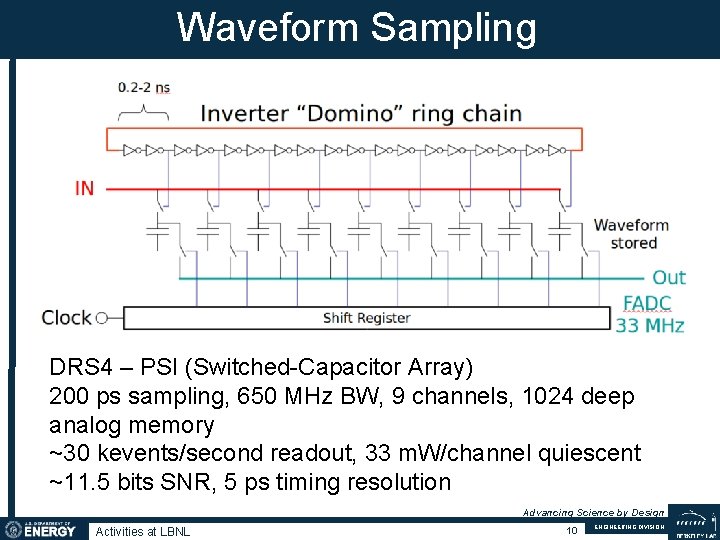

Waveform Sampling DRS 4 – PSI (Switched-Capacitor Array) 200 ps sampling, 650 MHz BW, 9 channels, 1024 deep analog memory ~30 kevents/second readout, 33 m. W/channel quiescent ~11. 5 bits SNR, 5 ps timing resolution Advancing Science by Design Activities at LBNL 10 ENGINEERING DIVISION

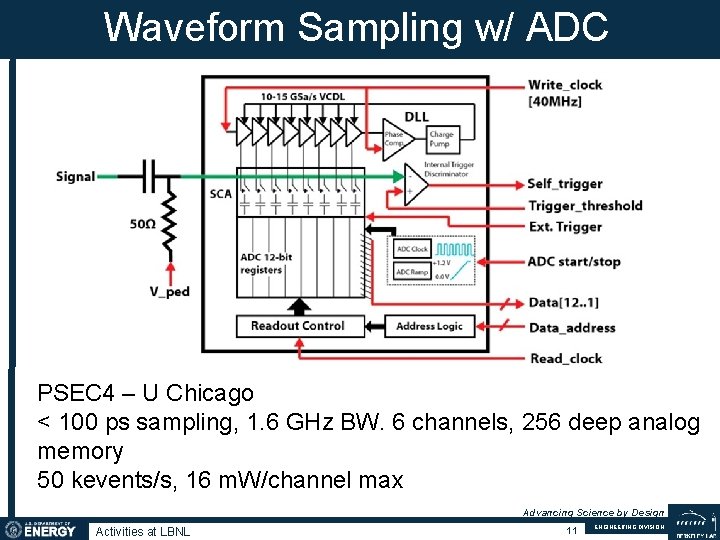

Waveform Sampling w/ ADC PSEC 4 – U Chicago < 100 ps sampling, 1. 6 GHz BW. 6 channels, 256 deep analog memory 50 kevents/s, 16 m. W/channel max Advancing Science by Design Activities at LBNL 11 ENGINEERING DIVISION

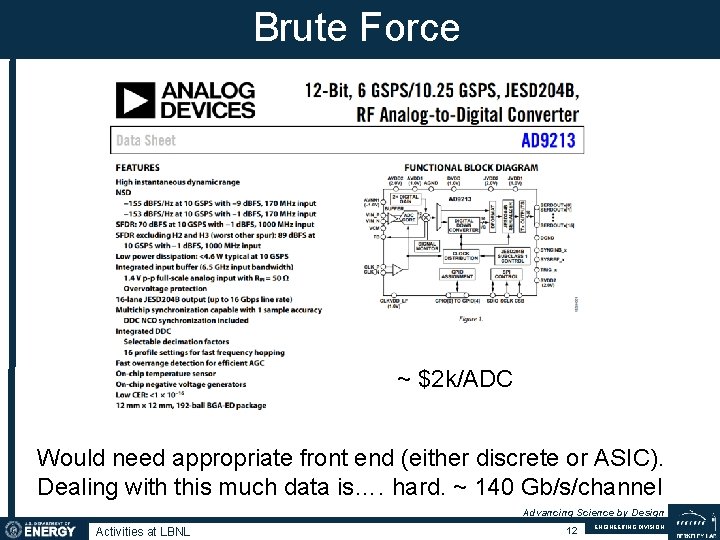

Brute Force ~ $2 k/ADC Would need appropriate front end (either discrete or ASIC). Dealing with this much data is…. hard. ~ 140 Gb/s/channel Advancing Science by Design Activities at LBNL 12 ENGINEERING DIVISION

Fast Timing without Digitizers Waveform digitization is the gold standard, but don’t always need it Many Questions: • How many channels? • What is the desired timing accuracy? • What exactly does frame rate mean? • Is power dissipation an issue? • Can the chip be cooled? • Does it need to be radiation hard? Advancing Science by Design Activities at LBNL 13 ENGINEERING DIVISION

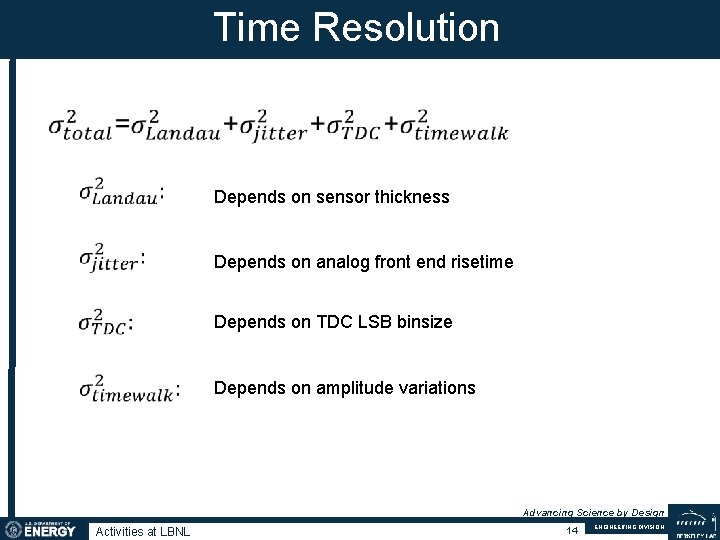

Time Resolution Depends on sensor thickness Depends on analog front end risetime Depends on TDC LSB binsize Depends on amplitude variations Advancing Science by Design Activities at LBNL 14 ENGINEERING DIVISION

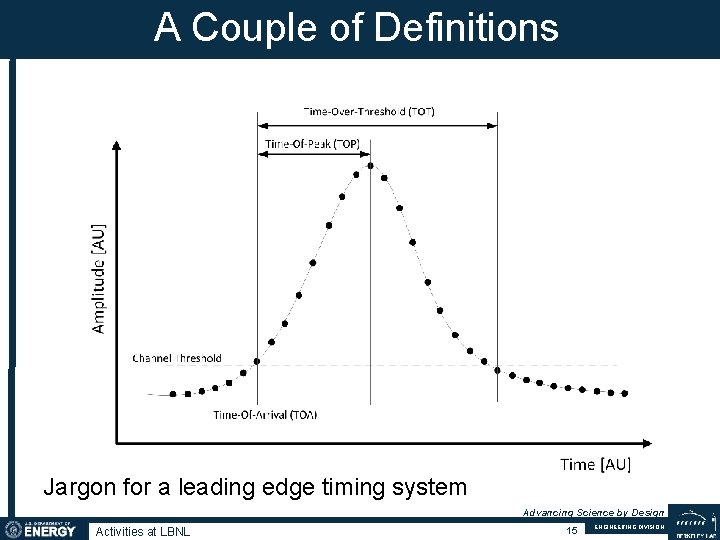

A Couple of Definitions Jargon for a leading edge timing system Advancing Science by Design Activities at LBNL 15 ENGINEERING DIVISION

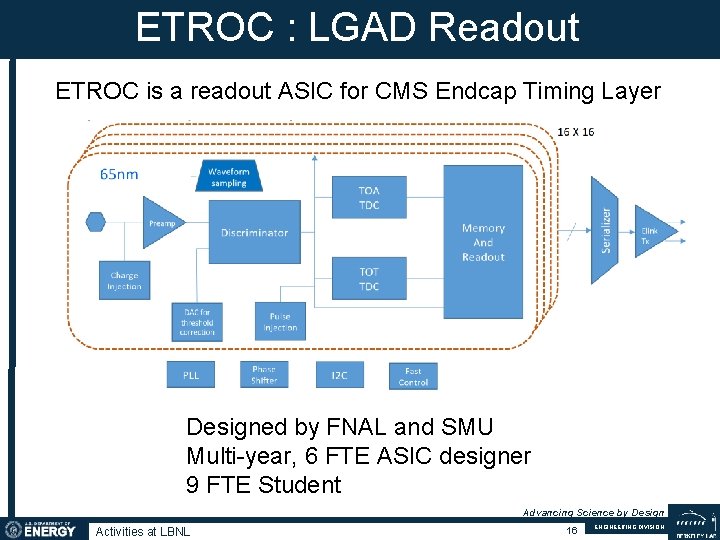

ETROC : LGAD Readout ETROC is a readout ASIC for CMS Endcap Timing Layer Designed by FNAL and SMU Multi-year, 6 FTE ASIC designer 9 FTE Student Advancing Science by Design Activities at LBNL 16 ENGINEERING DIVISION

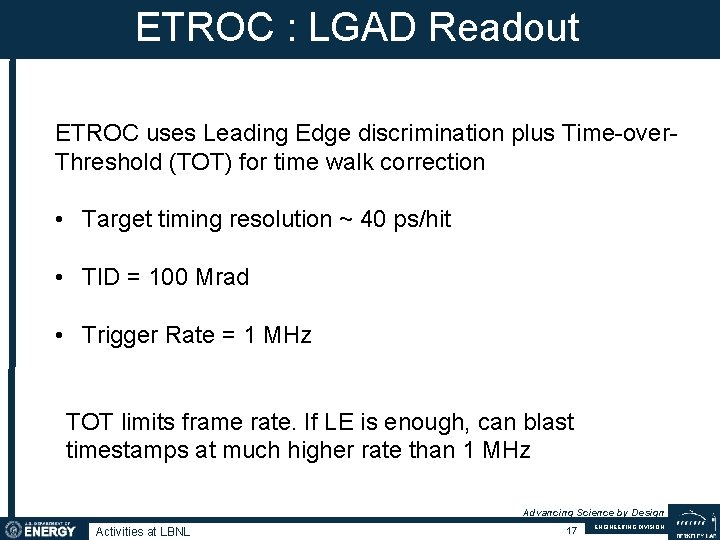

ETROC : LGAD Readout ETROC uses Leading Edge discrimination plus Time-over. Threshold (TOT) for time walk correction • Target timing resolution ~ 40 ps/hit • TID = 100 Mrad • Trigger Rate = 1 MHz TOT limits frame rate. If LE is enough, can blast timestamps at much higher rate than 1 MHz Advancing Science by Design Activities at LBNL 17 ENGINEERING DIVISION

- Slides: 17