Accumulator register Temporary register von Neumanns ISA computer

- Slides: 18

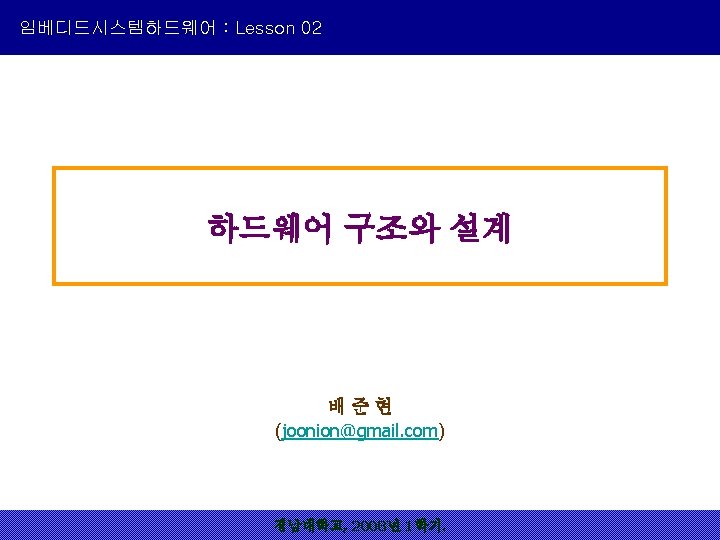

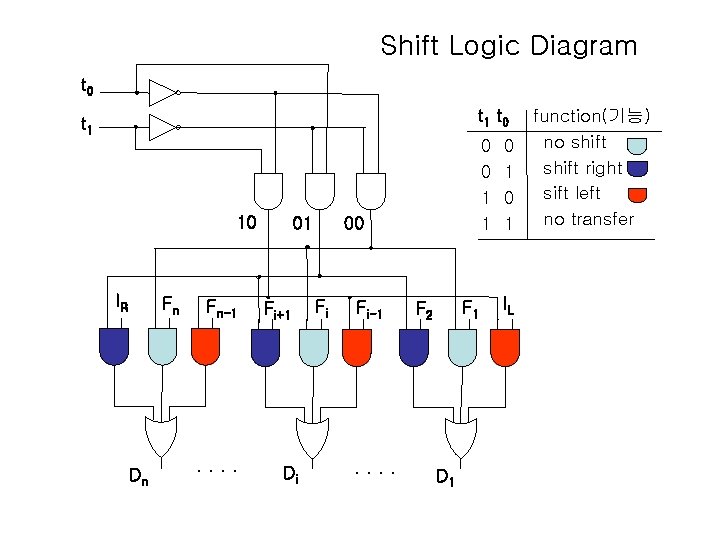

Accumulator register Temporary register von Neumann’s ISA computer ALU CPU Input output equipment Memory buffer register (MBR) Instruction buffer register (IBR) Control Unit Instruction register (IBR) Timing and control Program counter (PC) Main memory Memory address register (MAR) control signals address

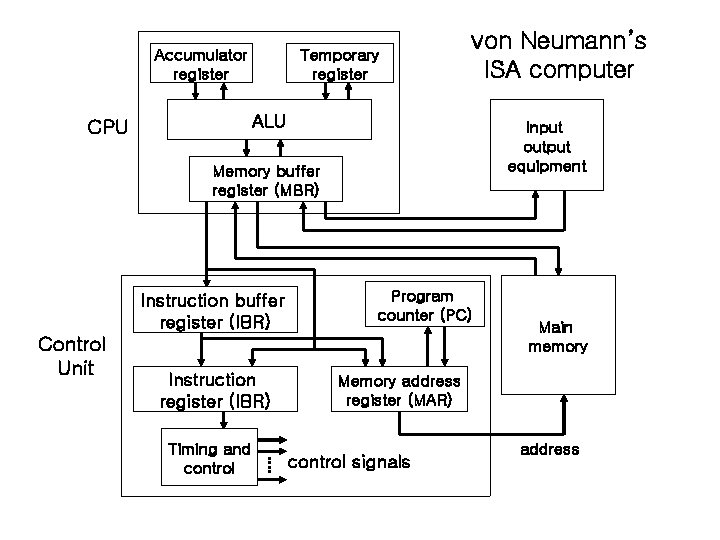

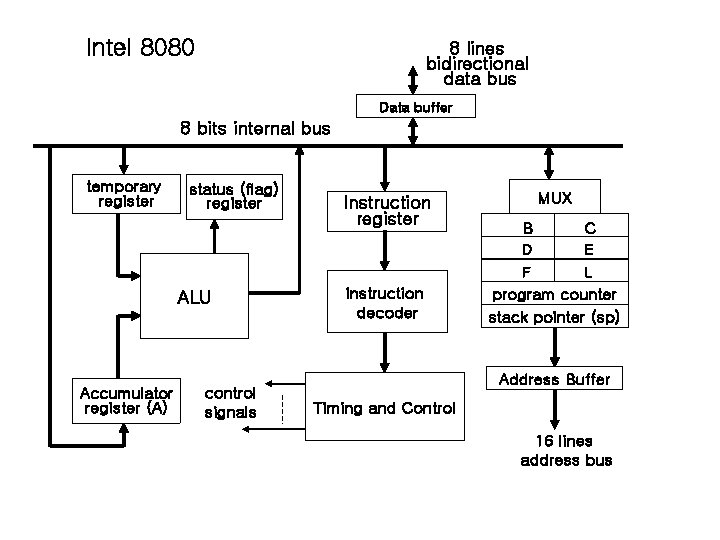

Intel 8080 8 lines bidirectional data bus Data buffer 8 bits internal bus temporary register status (flag) register ALU Accumulator register (A) control signals Instruction register instruction decoder MUX B C D E F L program counter stack pointer (sp) Address Buffer Timing and Control 16 lines address bus

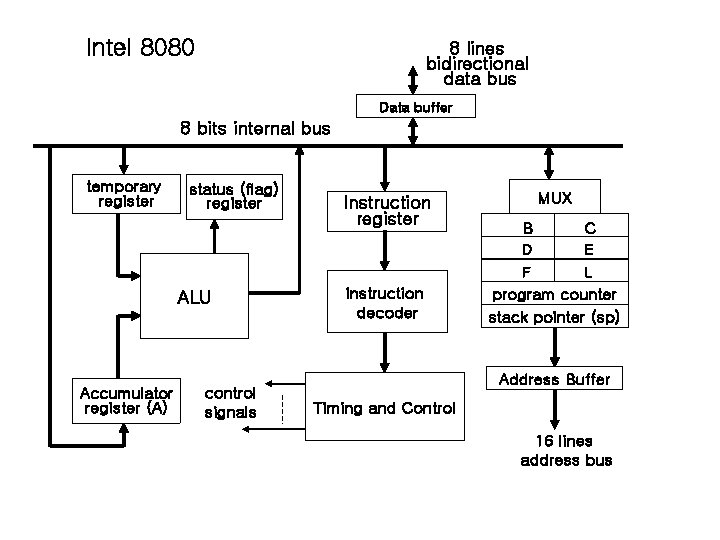

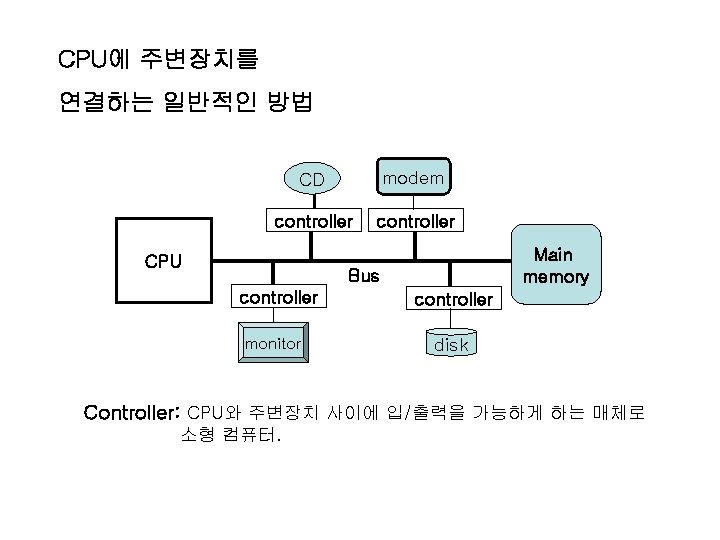

CPU에 주변장치를 연결하는 일반적인 방법 CD modem controller CPU Main memory Bus controller monitor controller disk Controller: CPU와 주변장치 사이에 입/출력을 가능하게 하는 매체로 소형 컴퓨터.

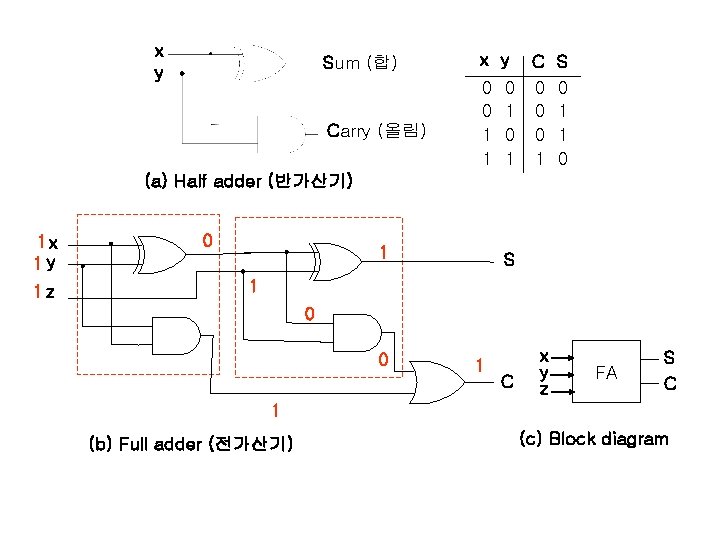

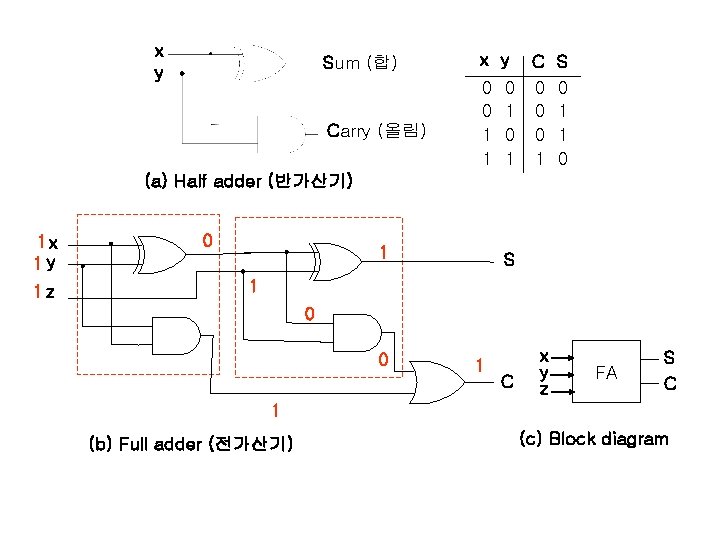

x y • Sum (합) x y Carry (올림) 0 0 1 1 0 1 C 0 0 0 1 S 0 1 1 0 (a) Half adder (반가산기) 1 x 1 y 1 z 0 1 • S 1 0 0 1 C x y z FA S C 1 (b) Full adder (전가산기) (c) Block diagram

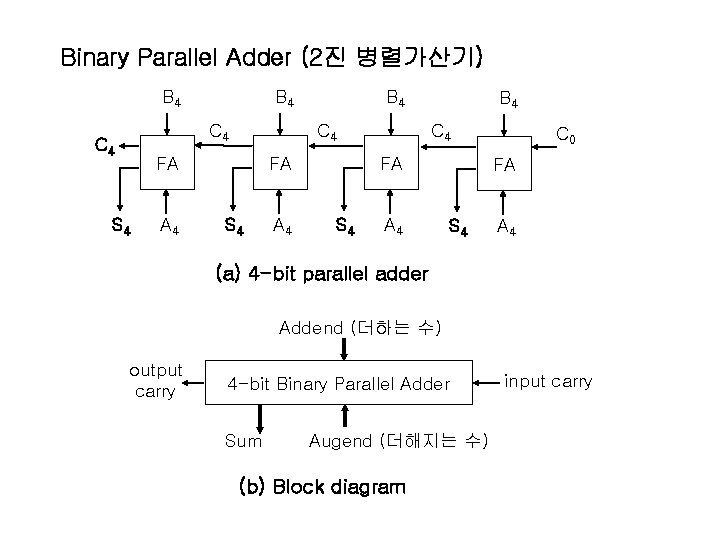

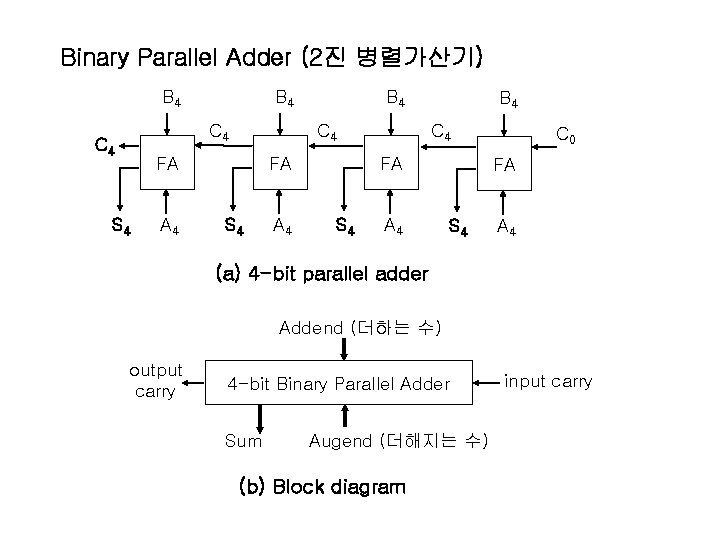

Binary Parallel Adder (2진 병렬가산기) B 4 C 4 C 4 FA S 4 A 4 B 4 C 4 FA S 4 A 4 C 0 FA S 4 A 4 (a) 4 -bit parallel adder Addend (더하는 수) output carry 4 -bit Binary Parallel Adder Sum Augend (더해지는 수) (b) Block diagram input carry

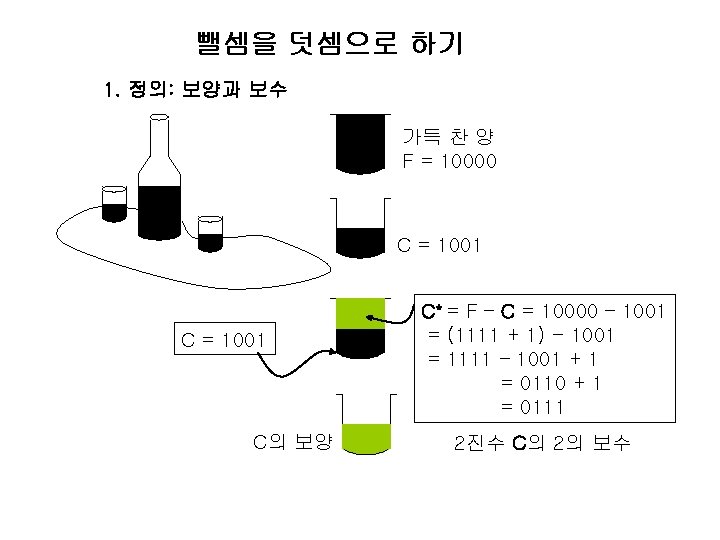

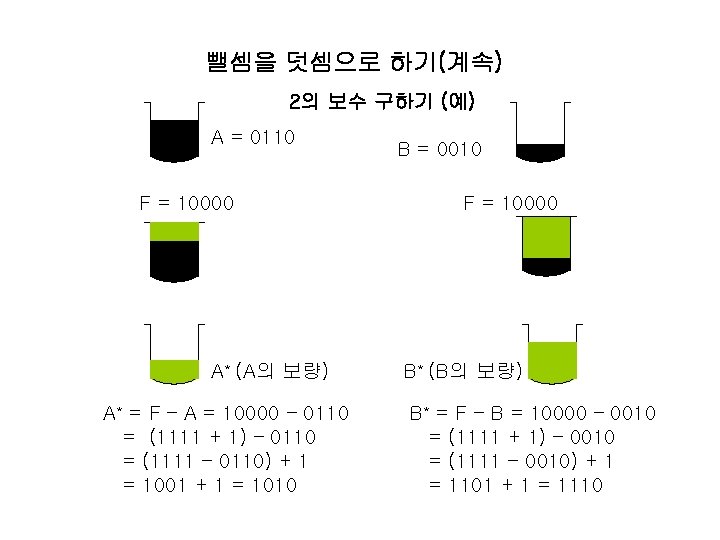

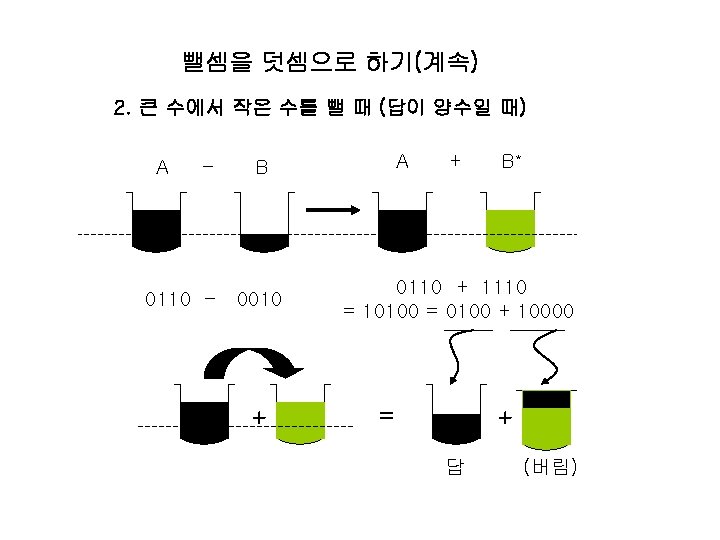

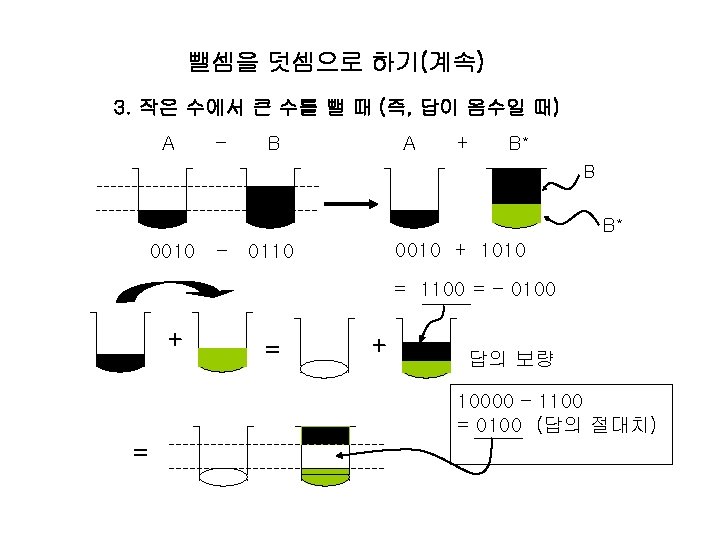

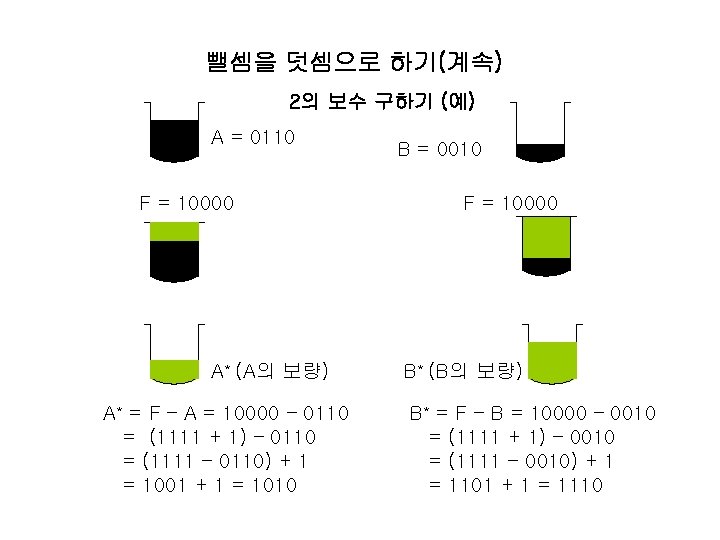

뺄셈을 덧셈으로 하기(계속) 2의 보수 구하기 (예) A = 0110 F = 10000 A* (A의 보량) A* = F – A = 10000 – 0110 = (1111 + 1) – 0110 = (1111 – 0110) + 1 = 1001 + 1 = 1010 B = 0010 F = 10000 B* (B의 보량) B* = F – B = 10000 – 0010 = (1111 + 1) – 0010 = (1111 – 0010) + 1 = 1101 + 1 = 1110

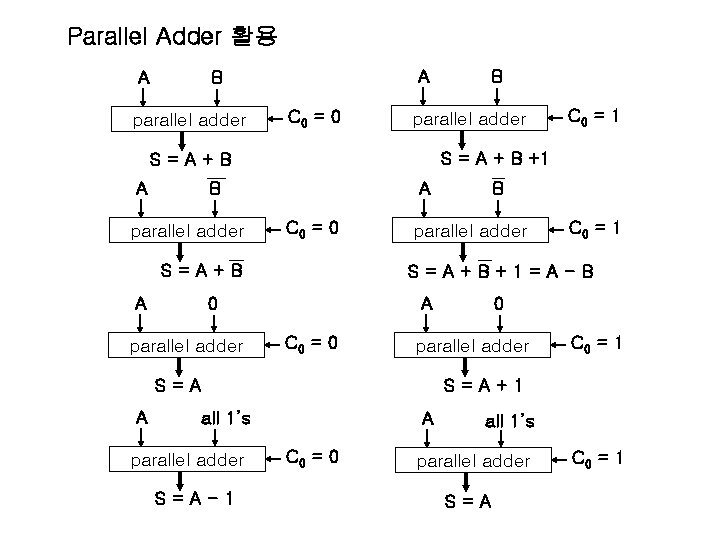

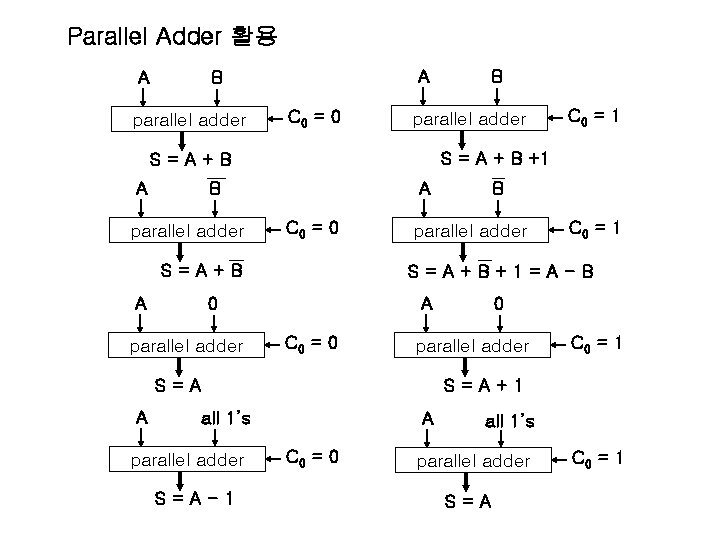

Parallel Adder 활용 A A B parallel adder C 0 = 0 parallel adder B parallel adder A C 0 = 0 S=A+B A parallel adder A C 0 = 0 S=A-1 C 0 = 1 S=A+1 all 1’s parallel adder C 0 = 1 0 parallel adder S=A A B S=A+B+1=A-B 0 parallel adder C 0 = 1 S = A + B +1 S=A+B A C 0 = 0 all 1’s parallel adder S=A C 0 = 1

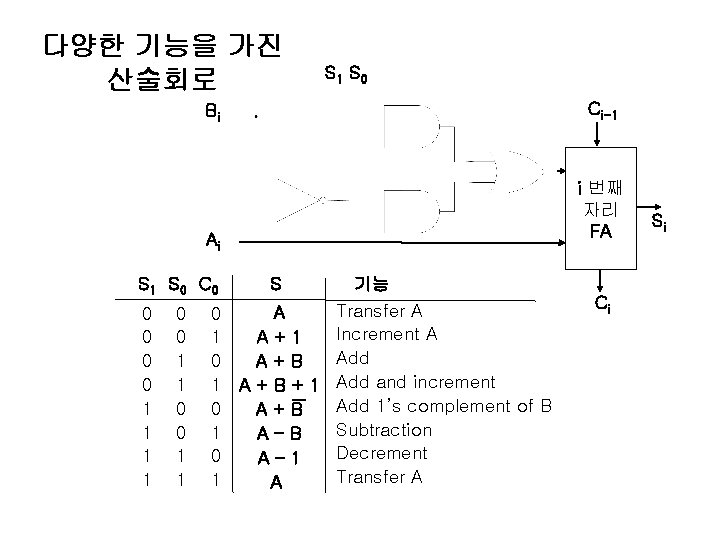

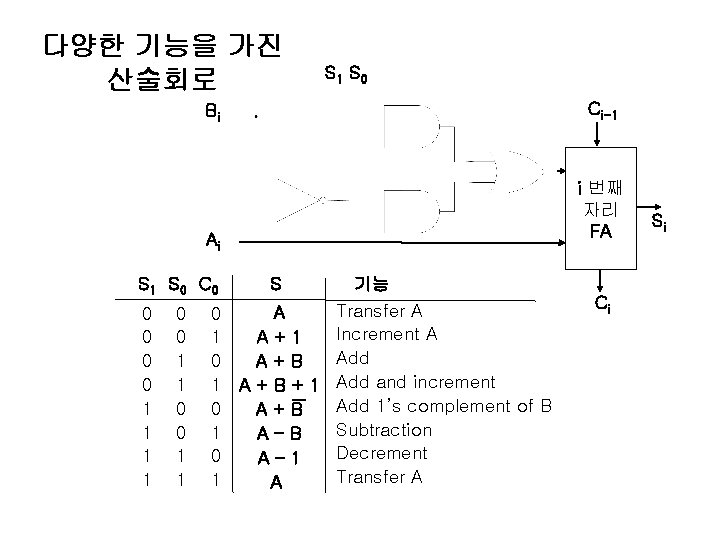

다양한 기능을 가진 산술회로 S 1 S 0 Ci-1 Bi i 번째 자리 FA Ai S 1 S 0 C 0 0 0 1 1 0 1 0 1 S 기능 Transfer A A Increment A A+1 Add A+B A + B + 1 Add and increment Add 1’s complement of B A+B Subtraction A–B Decrement A– 1 Transfer A A Ci Si

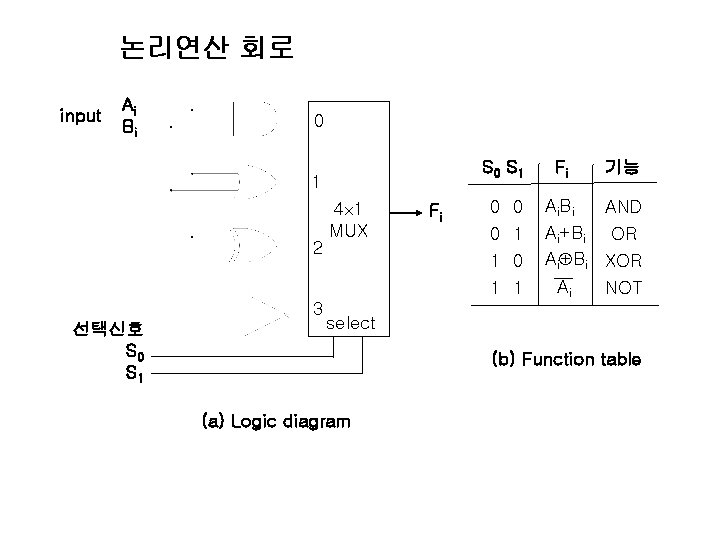

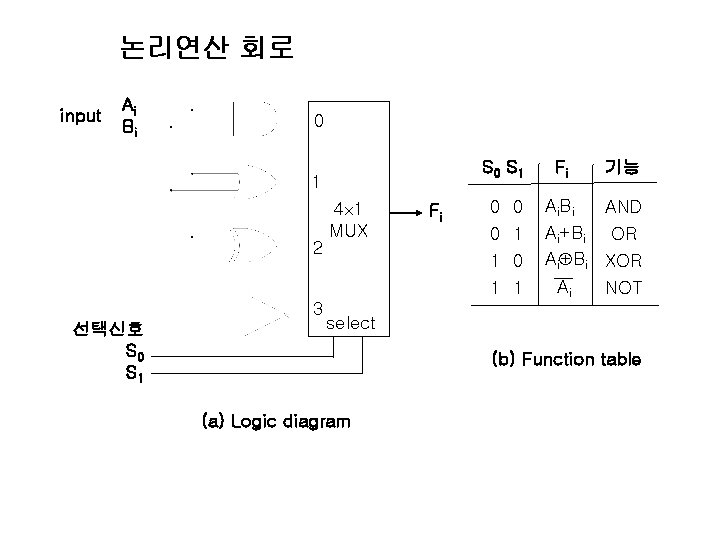

논리연산 회로 input Ai Bi 0 S 1 1 2 4 1 MUX Fi 0 0 0 1 1 3 선택신호 S 0 S 1 Fi 기능 Ai B i AND Ai+Bi OR Ai Bi XOR Ai NOT select (b) Function table (a) Logic diagram

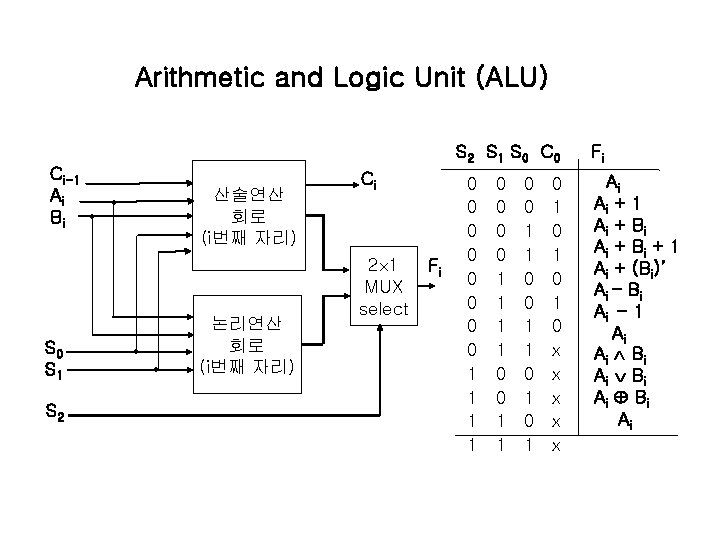

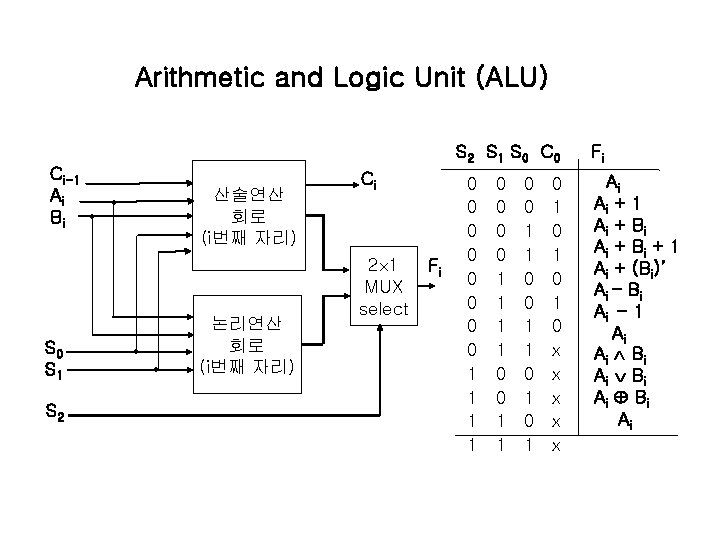

Arithmetic and Logic Unit (ALU) S 2 S 1 S 0 Ci-1 Ai • Bi • S 0 S 1 S 2 산술연산 회로 (i번째 자리) • • 논리연산 회로 (i번째 자리) Ci 2 1 MUX select Fi 0 0 0 0 1 1 0 0 1 1 0 1 0 1 0 x x x Fi Ai Ai + 1 Ai + B i + 1 Ai + (Bi)’ Ai – B i Ai - 1 Ai Ai B i Ai

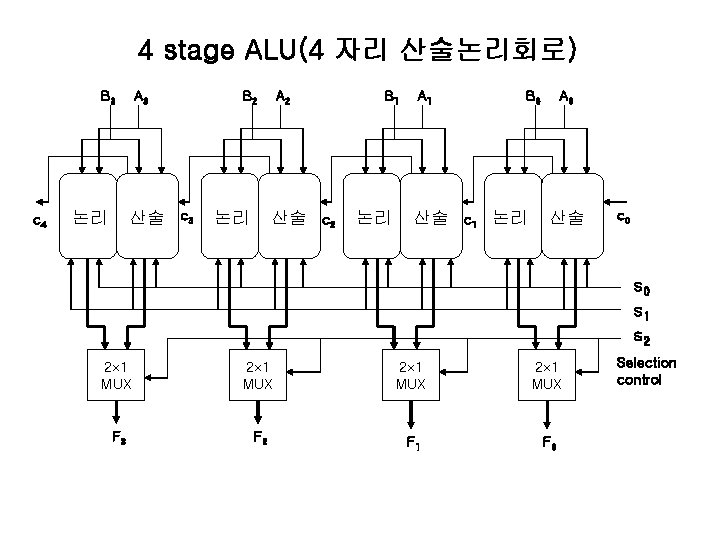

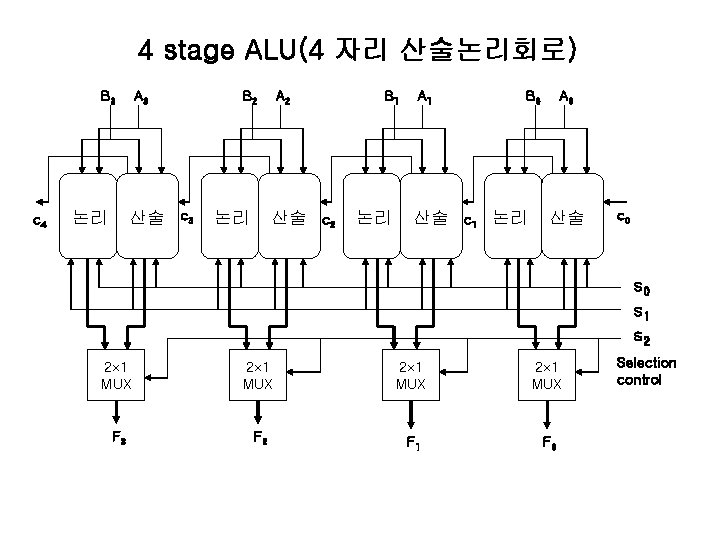

4 stage ALU(4 자리 산술논리회로) B 3 c 4 논리 A 3 산술 B 2 c 3 논리 A 2 산술 B 1 c 2 논리 A 1 산술 B 0 c 1 논리 A 0 산술 c 0 s 1 s 2 2 1 MUX F 3 F 2 F 1 F 0 Selection control

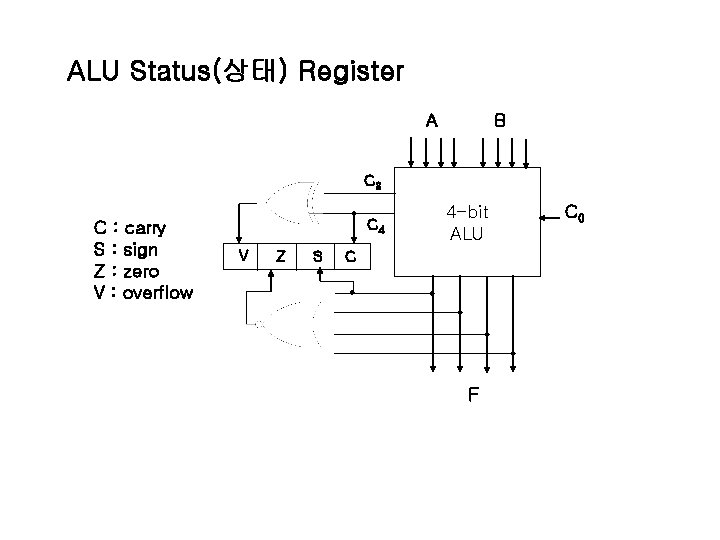

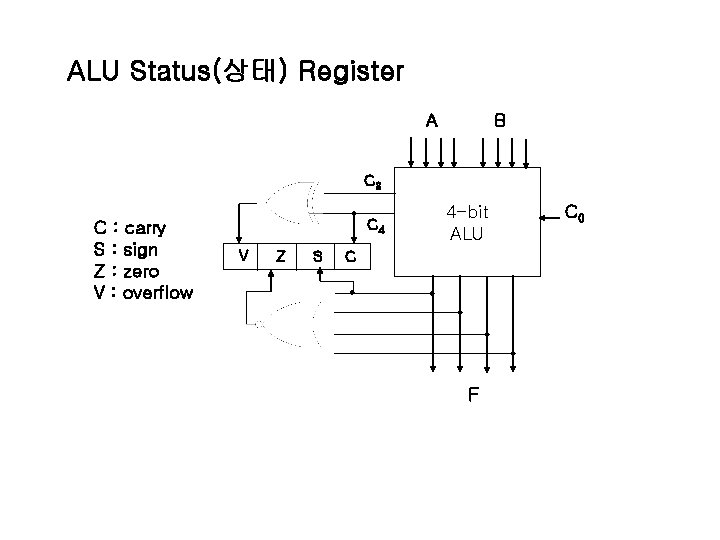

ALU Status(상태) Register A B C 3 C : carry S : sign Z : zero V : overflow • V Z S C 0 4 -bit ALU C 4 C • • • F

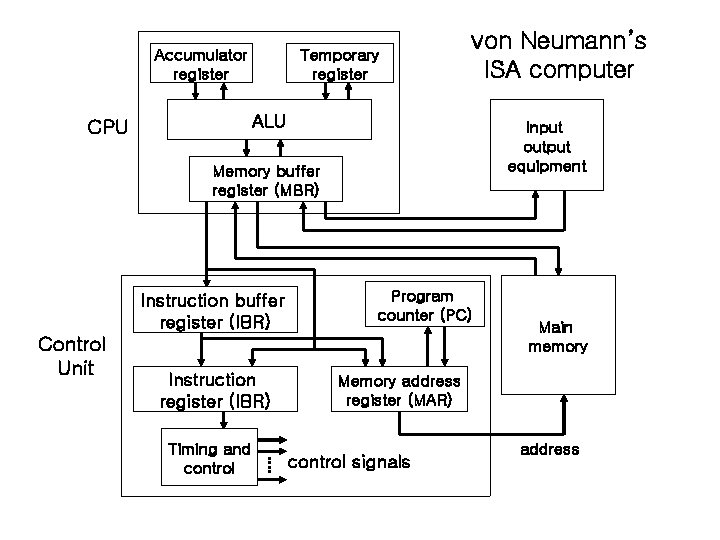

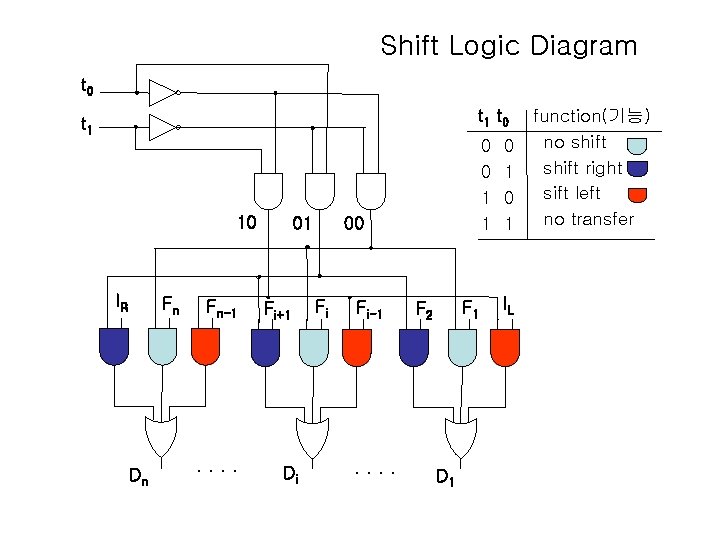

Shift Logic Diagram t 0 t 1 10 IR Fn Dn Fn-1 . . 01 Fi+1 Di 0 0 1 1 00 Fi Fi-1 . . F 1 F 2 D 1 0 1 IL function(기능) no shift right sift left no transfer

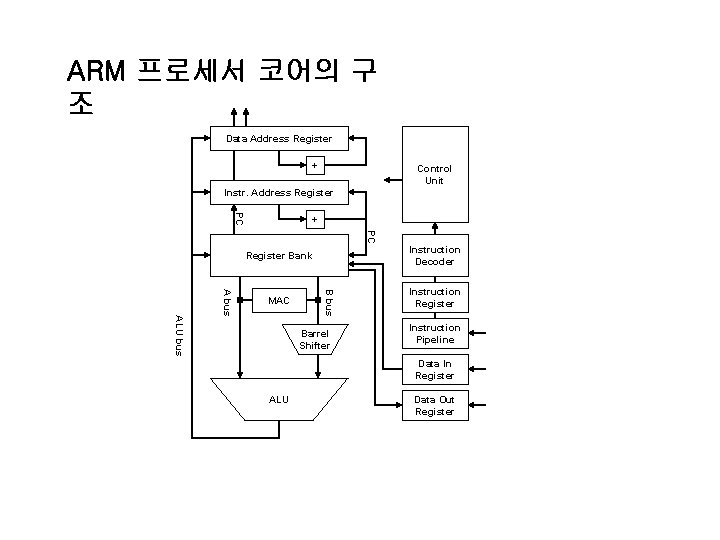

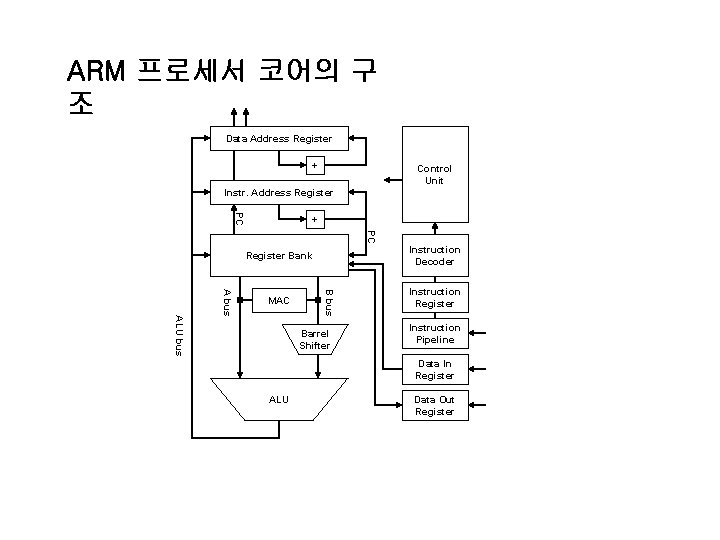

ARM 프로세서 코어의 구 조 Data Address Register + Control Unit Instr. Address Register PC + PC Instruction Decoder MAC Instruction Register B bus ALU bus A bus Register Bank Barrel Shifter Instruction Pipeline Data In Register ALU Data Out Register