ABCN 130 RTL status Running functional rtl code

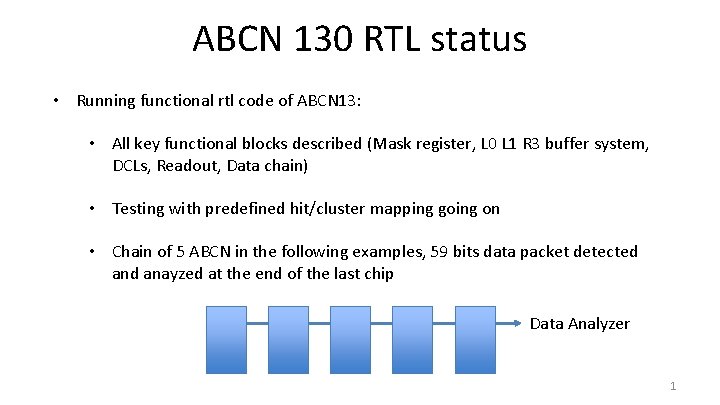

ABCN 130 RTL status • Running functional rtl code of ABCN 13: • All key functional blocks described (Mask register, L 0 L 1 R 3 buffer system, DCLs, Readout, Data chain) • Testing with predefined hit/cluster mapping going on • Chain of 5 ABCN in the following examples, 59 bits data packet detected anayzed at the end of the last chip Data Analyzer 1

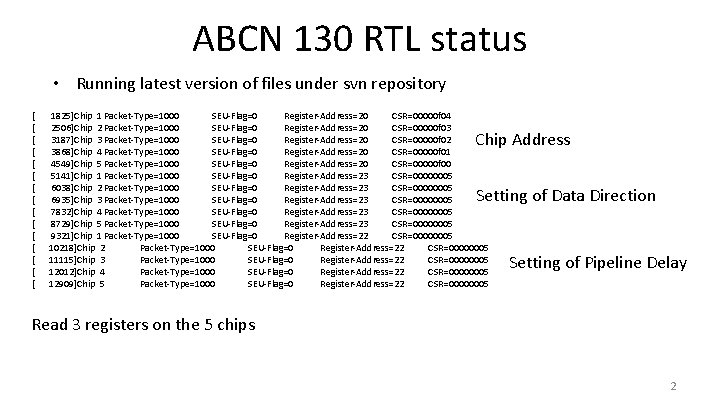

ABCN 130 RTL status • Running latest version of files under svn repository [ [ [ [ 1825]Chip 1 Packet-Type=1000 SEU-Flag=0 Register-Address=20 CSR=00000 f 04 2506]Chip 2 Packet-Type=1000 SEU-Flag=0 Register-Address=20 CSR=00000 f 03 3187]Chip 3 Packet-Type=1000 SEU-Flag=0 Register-Address=20 CSR=00000 f 02 3868]Chip 4 Packet-Type=1000 SEU-Flag=0 Register-Address=20 CSR=00000 f 01 4549]Chip 5 Packet-Type=1000 SEU-Flag=0 Register-Address=20 CSR=00000 f 00 5141]Chip 1 Packet-Type=1000 SEU-Flag=0 Register-Address=23 CSR=00000005 6038]Chip 2 Packet-Type=1000 SEU-Flag=0 Register-Address=23 CSR=00000005 6935]Chip 3 Packet-Type=1000 SEU-Flag=0 Register-Address=23 CSR=00000005 7832]Chip 4 Packet-Type=1000 SEU-Flag=0 Register-Address=23 CSR=00000005 8729]Chip 5 Packet-Type=1000 SEU-Flag=0 Register-Address=23 CSR=00000005 9321]Chip 1 Packet-Type=1000 SEU-Flag=0 Register-Address=22 CSR=00000005 10218]Chip 2 Packet-Type=1000 SEU-Flag=0 Register-Address=22 CSR=00000005 11115]Chip 3 Packet-Type=1000 SEU-Flag=0 Register-Address=22 CSR=00000005 12012]Chip 4 Packet-Type=1000 SEU-Flag=0 Register-Address=22 CSR=00000005 12909]Chip 5 Packet-Type=1000 SEU-Flag=0 Register-Address=22 CSR=00000005 Chip Address Setting of Data Direction Setting of Pipeline Delay Read 3 registers on the 5 chips 2

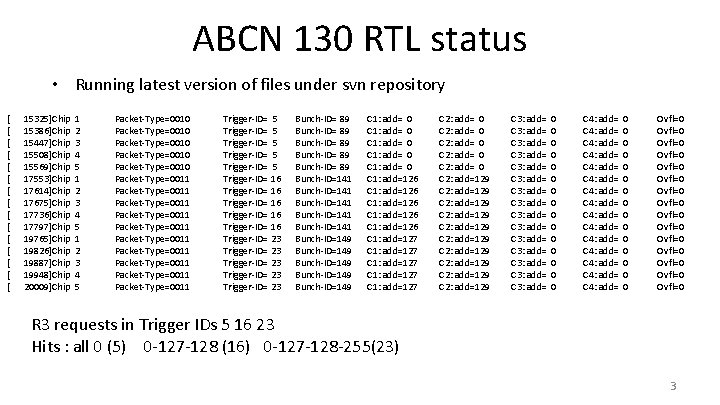

ABCN 130 RTL status • Running latest version of files under svn repository [ [ [ [ 15325]Chip 15386]Chip 15447]Chip 15508]Chip 15569]Chip 17553]Chip 17614]Chip 17675]Chip 17736]Chip 17797]Chip 19765]Chip 19826]Chip 19887]Chip 19948]Chip 20009]Chip 1 2 3 4 5 Packet-Type=0010 Packet-Type=0010 Packet-Type=0011 Packet-Type=0011 Packet-Type=0011 Trigger-ID= 5 Trigger-ID= 5 Trigger-ID= 16 Trigger-ID= 16 Trigger-ID= 23 Trigger-ID= 23 Bunch-ID= 89 Bunch-ID= 89 Bunch-ID=141 Bunch-ID=141 Bunch-ID=149 Bunch-ID=149 C 1: add= 0 C 1: add= 0 C 1: add=126 C 1: add=126 C 1: add=127 C 1: add=127 C 2: add= 0 C 2: add= 0 C 2: add=129 C 2: add=129 C 2: add=129 C 3: add= C 3: add= C 3: add= C 3: add= 0 0 0 0 C 4: add= C 4: add= C 4: add= C 4: add= 0 0 0 0 Ovfl=0 Ovfl=0 Ovfl=0 Ovfl=0 R 3 requests in Trigger IDs 5 16 23 Hits : all 0 (5) 0 -127 -128 (16) 0 -127 -128 -255(23) 3

![ABCN 130 RTL status [ [ [ [ [ 22085]Chip 22146]Chip 22207]Chip 22268]Chip 22329]Chip ABCN 130 RTL status [ [ [ [ [ 22085]Chip 22146]Chip 22207]Chip 22268]Chip 22329]Chip](http://slidetodoc.com/presentation_image/4795aaec111b9a70f9b41ff0522d67f4/image-4.jpg)

ABCN 130 RTL status [ [ [ [ [ 22085]Chip 22146]Chip 22207]Chip 22268]Chip 22329]Chip 23941]Chip 24002]Chip 24063]Chip 24124]Chip 24185]Chip 25757]Chip 25818]Chip 25879]Chip 25940]Chip 26001]Chip 26061]Chip 26121]Chip 26181]Chip 26241]Chip 26301]Chip 1 2 3 4 5 Packet-Type=0111 Packet-Type=0111 Packet-Type=0110 Packet-Type=0110 Packet-Type=0100 Packet-Type=0100 Packet-Type=0110 Packet-Type=0110 Trigger-ID= 3 Trigger-ID= 3 Trigger-ID= 13 Trigger-ID= 13 Trigger-ID= 23 Trigger-ID= 23 Trigger-ID= 23 Bunch-ID= 68 Bunch-ID= 68 Bunch-ID=109 Bunch-ID=109 Bunch-ID=150 Bunch-ID=150 Bunch-ID=150 C 1: add= 0 bits=000 C 1: add= 0 bits=000 C 1: add= 0 bits=000 C 1: add= 0 bits=000 C 1: add=255 bits=000 C 1: add=255 bits=000 C 2: add= 0 bits=000 C 2: add= 0 bits=000 C 2: add=128 bits=000 C 2: add=128 bits=000 C 2: add=128 bits=000 C 2: add=255 bits=000 C 2: add=255 bits=000 C 3: add= 0 bits=000 C 3: add= 0 bits=000 C 3: add=127 bits=000 C 3: add=127 bits=000 C 3: add=127 bits=000 C 3: add=255 bits=000 C 3: add=255 bits=000 L 1 requests in Trigger IDs 3 13 23 Hits : all 0 (3) 0 -127 -128 (13) 0 -127 -128 -255(23) 4

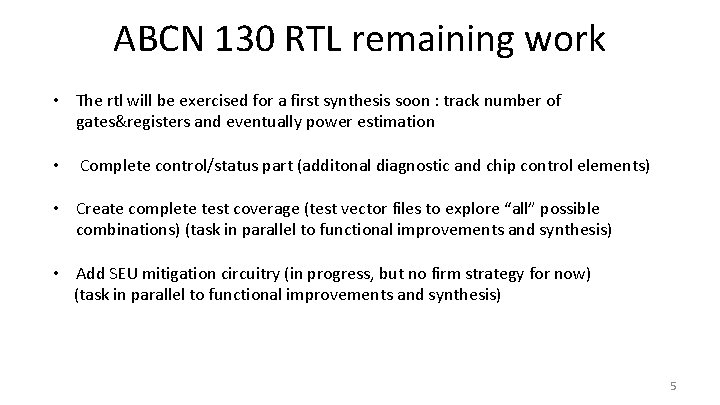

ABCN 130 RTL remaining work • The rtl will be exercised for a first synthesis soon : track number of gates®isters and eventually power estimation • Complete control/status part (additonal diagnostic and chip control elements) • Create complete test coverage (test vector files to explore “all” possible combinations) (task in parallel to functional improvements and synthesis) • Add SEU mitigation circuitry (in progress, but no firm strategy for now) (task in parallel to functional improvements and synthesis) 5

ABCN 130 Specifications • Packets definition and transmission to be presented in a document before the November AUW • Command set to be presented in a document before the November AUW • No DCDC on chip (for time being) • Some DCS functions could be added • Synthesis with 0. 9 V timing model if available on-time • In conjonction with the HCC specifications (Mitch et al. ) 6

Radiation Tests • A portable test setup is being developed by Jan Kaplon/M Noy to carry on the Front_End prototype radiations tests (Low dose rate in US was discussed with Alex/Miguel Ullan … ) • Xray test at low temperature of the Front_End prototype should be done Q 4 2011 (Jan et al. ) • RAM block SEU tests considered to be carried on at CERN facilities (IRRAD-6, support of Bruno Allongue) 1 st semester of 2012 • SEULogic test chip in IRRAD-6 at end of this month to carry on SEU sensitivity on one “ABCN” classical digital block (Command Decoder) (exercise with the IRRAD-6 setup) 7

- Slides: 7