ABC A System for Sequential Synthesis and Verification

ABC: A System for Sequential Synthesis and Verification BVSRC Berkeley Verification and Synthesis Research Center Robert Brayton , Niklas Een, Alan Mishchenko, Jiang Long, Sayak Ray, Baruch Sterin UC Berkeley Thanks to NSF, SRC, and industrial sponsors: Intel, IBM, Synopsys, Magma, Actel, Altera, Atrenta, Intrinsity, Jasper, Tabula, Verific, Real Intent, Oasys

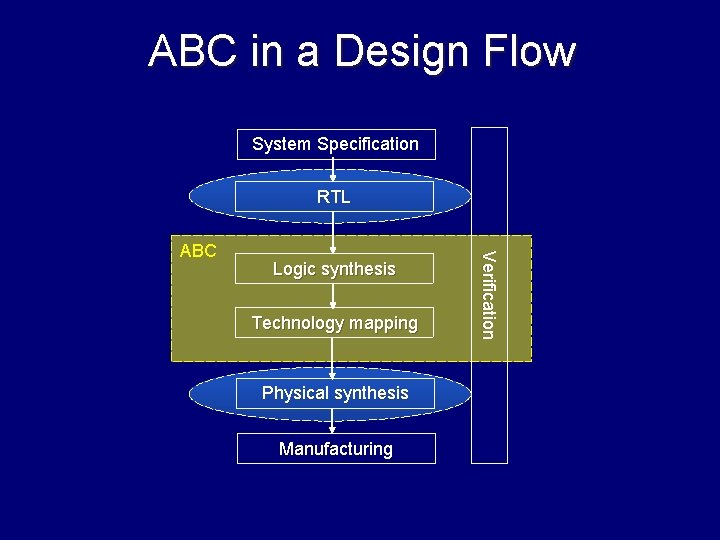

ABC in a Design Flow System Specification RTL Logic synthesis Technology mapping Physical synthesis Manufacturing Verification ABC

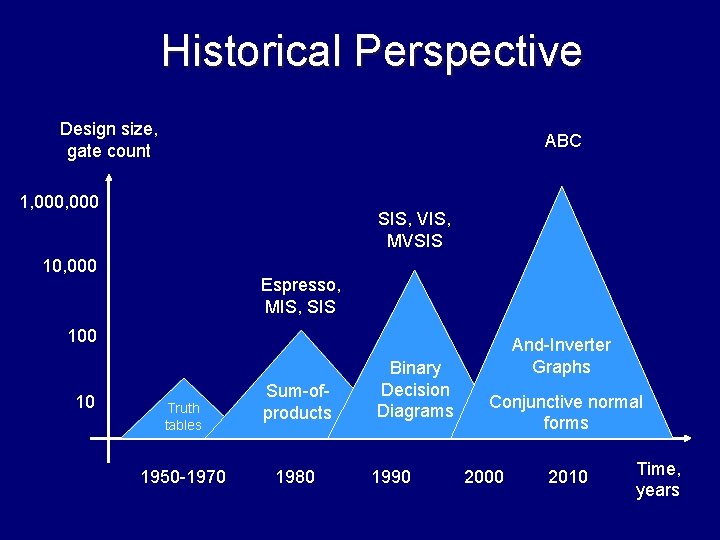

Historical Perspective Design size, gate count ABC 1, 000 SIS, VIS, MVSIS 10, 000 Espresso, MIS, SIS 100 10 Truth tables 1950 -1970 Sum-ofproducts 1980 Binary Decision Diagrams 1990 And-Inverter Graphs Conjunctive normal forms 2000 2010 Time, years

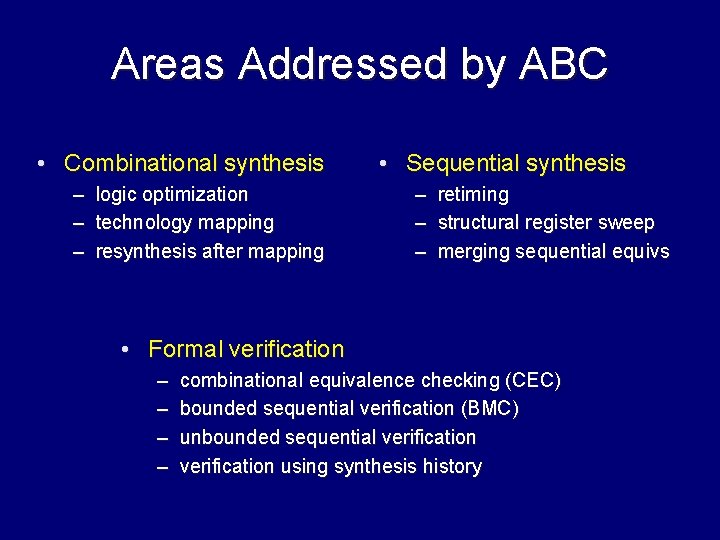

Areas Addressed by ABC • Combinational synthesis – logic optimization – technology mapping – resynthesis after mapping • Sequential synthesis – retiming – structural register sweep – merging sequential equivs • Formal verification – – combinational equivalence checking (CEC) bounded sequential verification (BMC) unbounded sequential verification using synthesis history

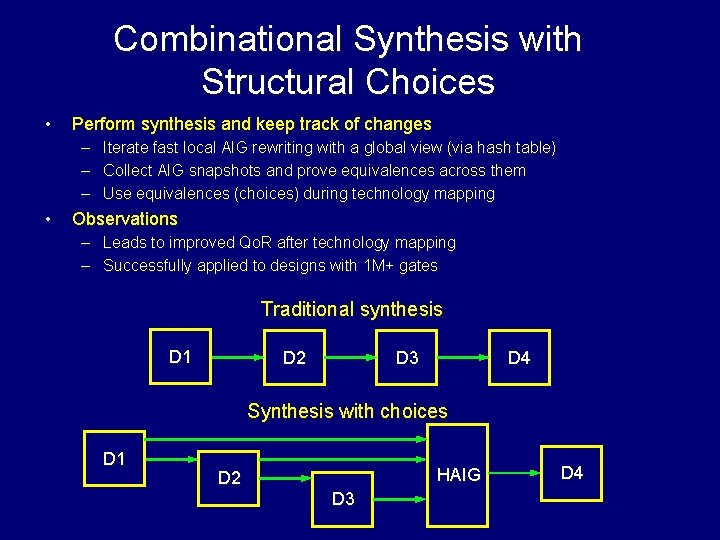

Combinational Synthesis with Structural Choices • Perform synthesis and keep track of changes – Iterate fast local AIG rewriting with a global view (via hash table) – Collect AIG snapshots and prove equivalences across them – Use equivalences (choices) during technology mapping • Observations – Leads to improved Qo. R after technology mapping – Successfully applied to designs with 1 M+ gates Traditional synthesis D 1 D 2 D 3 D 4 Synthesis with choices D 1 HAIG D 2 D 3 D 4

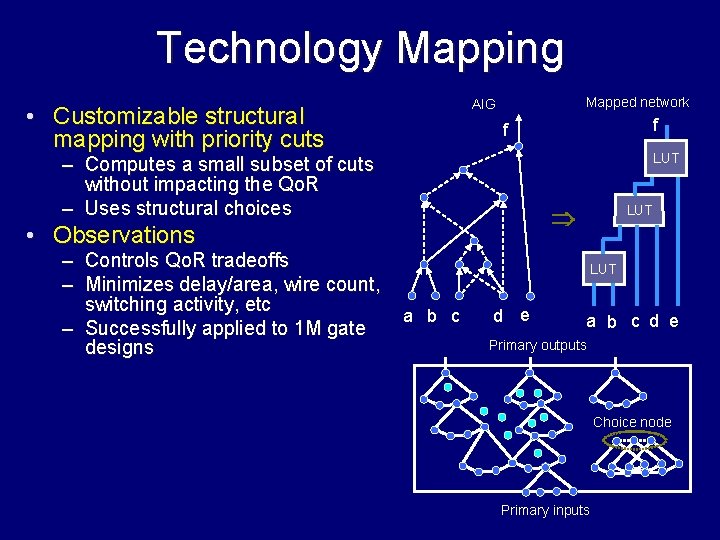

Technology Mapping Mapped network AIG • Customizable structural mapping with priority cuts f f LUT – Computes a small subset of cuts without impacting the Qo. R – Uses structural choices • Observations LUT – – Controls Qo. R tradeoffs Minimizes delay/area, wire count, switching activity, etc – Successfully applied to 1 M gate designs LUT a b c d e Primary outputs Choice node Primary inputs

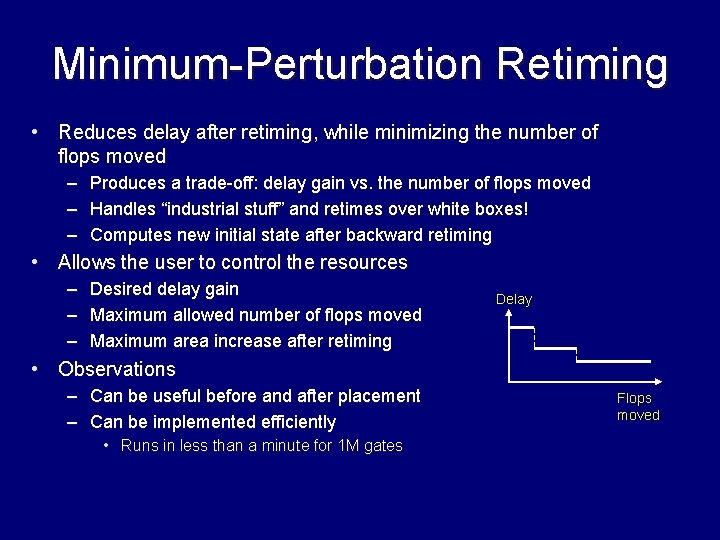

Minimum-Perturbation Retiming • Reduces delay after retiming, while minimizing the number of flops moved – Produces a trade-off: delay gain vs. the number of flops moved – Handles “industrial stuff” and retimes over white boxes! – Computes new initial state after backward retiming • Allows the user to control the resources – – – Desired delay gain Maximum allowed number of flops moved Maximum area increase after retiming Delay • Observations – Can be useful before and after placement – Can be implemented efficiently • Runs in less than a minute for 1 M gates Flops moved

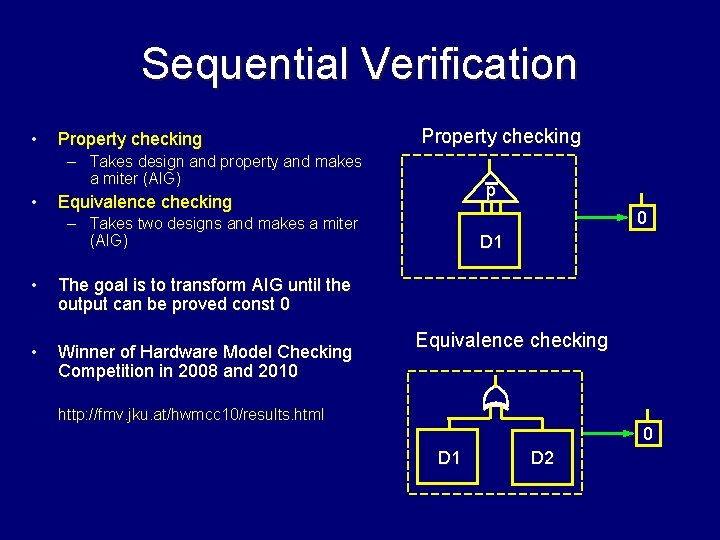

Sequential Verification • Property checking – Takes design and property and makes a miter (AIG) • p Equivalence checking 0 – Takes two designs and makes a miter (AIG) • The goal is to transform AIG until the output can be proved const 0 • Winner of Hardware Model Checking Competition in 2008 and 2010 D 1 Equivalence checking http: //fmv. jku. at/hwmcc 10/results. html 0 D 1 D 2

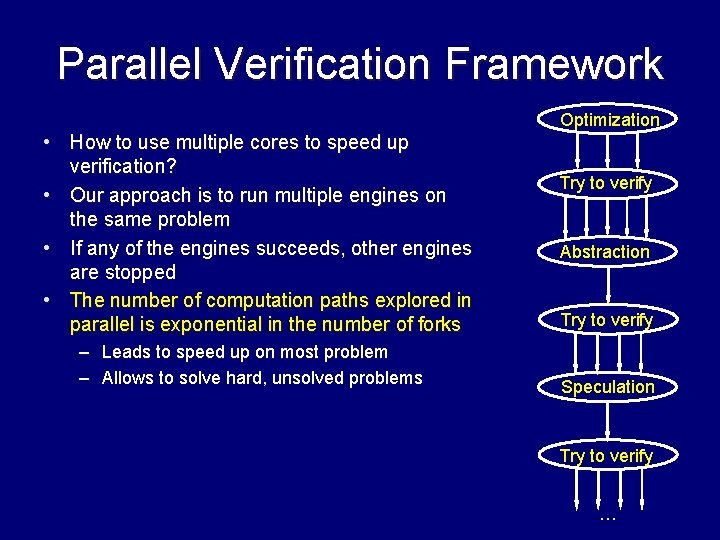

Parallel Verification Framework Optimization • How to use multiple cores to speed up verification? • Our approach is to run multiple engines on the same problem • If any of the engines succeeds, other engines are stopped • The number of computation paths explored in parallel is exponential in the number of forks – Leads to speed up on most problem – Allows to solve hard, unsolved problems Try to verify Abstraction Try to verify Speculation Try to verify …

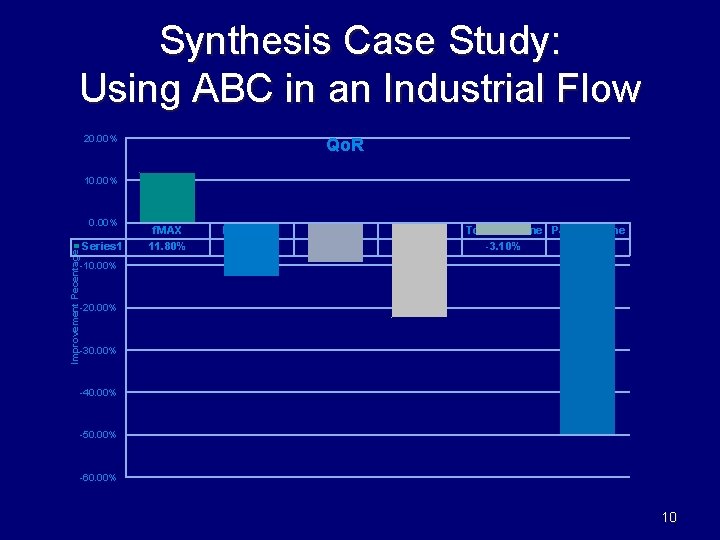

Synthesis Case Study: Using ABC in an Industrial Flow 20. 00% Qo. R 10. 00% Improvement Pecentage 0. 00% Series 1 f. MAX 11. 80% LUT count -12. 70% Registers -9. 40% Levels -22. 30% Total Runtime P&R Runtime -3. 10% -50. 00% -10. 00% -20. 00% -30. 00% -40. 00% -50. 00% -60. 00% 10

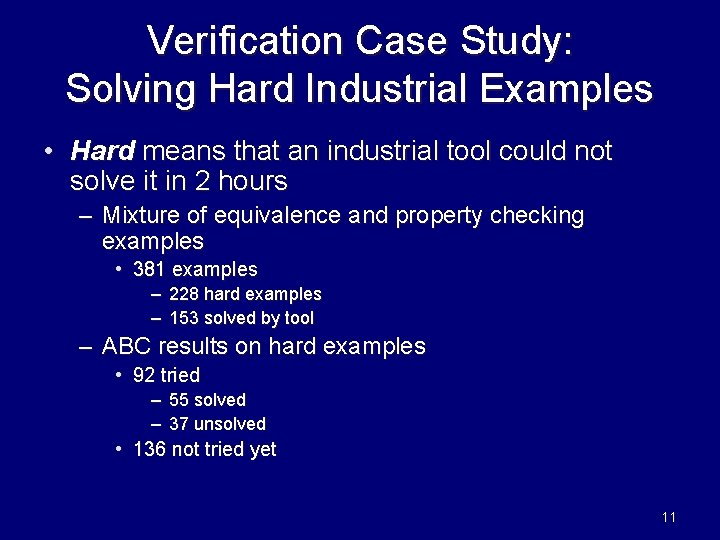

Verification Case Study: Solving Hard Industrial Examples • Hard means that an industrial tool could not solve it in 2 hours – Mixture of equivalence and property checking examples • 381 examples – 228 hard examples – 153 solved by tool – ABC results on hard examples • 92 tried – 55 solved – 37 unsolved • 136 not tried yet 11

Future Work • Developing and scaling bit-level methods • Addressing bottlenecks in the synthesis flow – – AIG rewriting Choice computation Technology mapping Sequential synthesis • Improving the verification flow – – – Application-specific, circuit-based SAT solving Extracting and using word-level information Exploiting synergies with synthesis

- Slides: 12