ABC 130 Submission F Anghinolfi 300413 ABC 130

ABC 130 Submission F. Anghinolfi 30/04/13 ABC 130 ITk Meeting 1

ABC 130 Status • What has happened since the review (3 months ago) – The Front. End has shown a tendancy to instability when simulated with all channels active (detector signal on 240 channels) and inductances of wire bonds – The FE layout has been corrected : • specific power bus for the input branch of the preamplifier • Input to Calibration line shielding (was responsible for excessive crosstalk) – The regulators have been changed : • A more stable version has been installed that has 2 drawbacks : 1. Drop Out voltage is 0. 3 V worst case 2. Switch off residual current of a few m. A (cannot be set to zero) 30/04/13 ABC 130 ITk Meeting 2

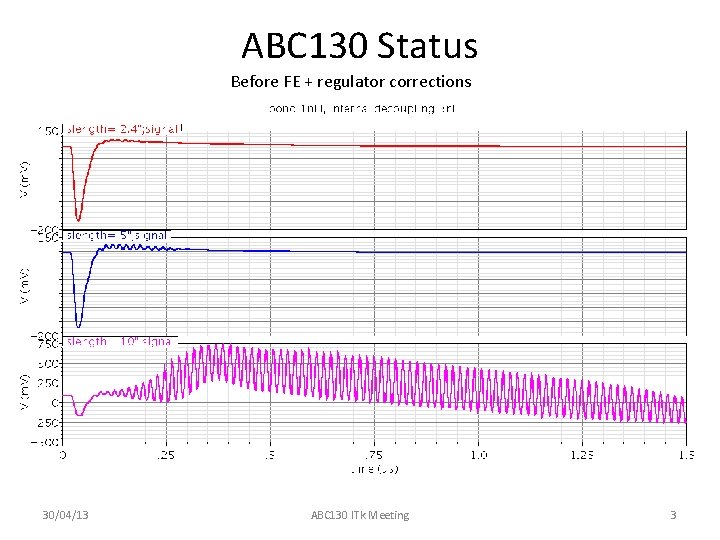

ABC 130 Status Before FE + regulator corrections 30/04/13 ABC 130 ITk Meeting 3

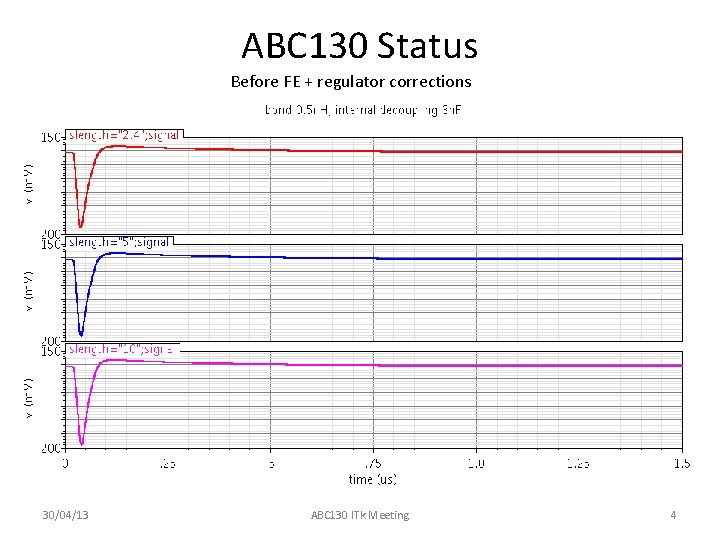

ABC 130 Status Before FE + regulator corrections 30/04/13 ABC 130 ITk Meeting 4

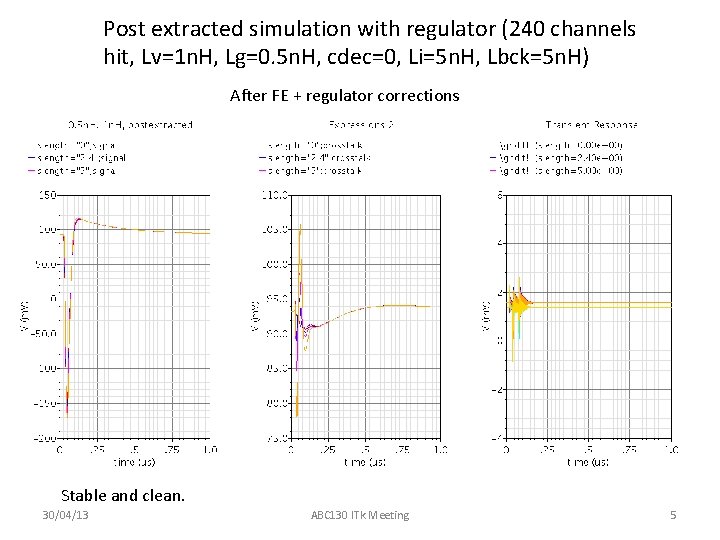

Post extracted simulation with regulator (240 channels hit, Lv=1 n. H, Lg=0. 5 n. H, cdec=0, Li=5 n. H, Lbck=5 n. H) After FE + regulator corrections Stable and clean. 30/04/13 ABC 130 ITk Meeting 5

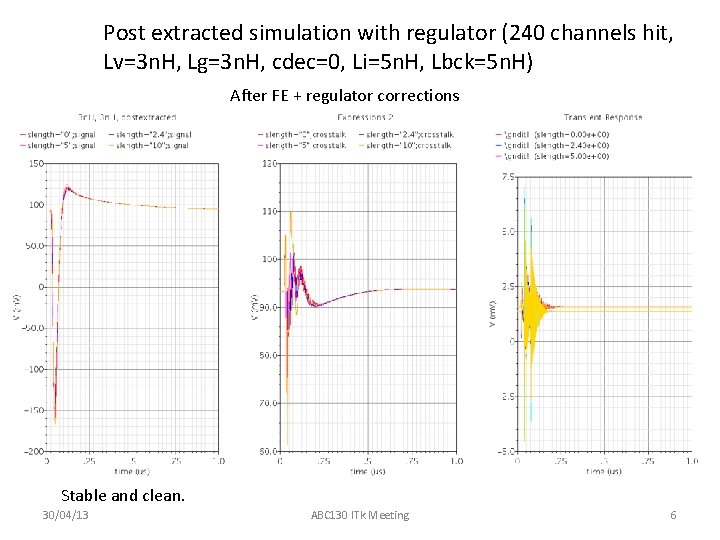

Post extracted simulation with regulator (240 channels hit, Lv=3 n. H, Lg=3 n. H, cdec=0, Li=5 n. H, Lbck=5 n. H) After FE + regulator corrections Stable and clean. 30/04/13 ABC 130 ITk Meeting 6

ABC 130 Status • Submission Preparation – Layout fixed without the FCF block – DRC almost clean (last corrections are manual) – LVS has still to be cleaned (was clean at a time but there were corrections of the FE and regulators) – Timing is built correct in the digital section by the PNR tool (and up to now verifications have shown correct functionality with timing and backannotation) 30/04/13 ABC 130 ITk Meeting 7

ABC 130 Submission on … • Shared Engineering Run (ABC + TDCpix) – ABC : Shared Engineering run with the NA 62/TDCpix submission (forecast 1 Q 2013) – Additional Eng. Run wafers at 3. 6 KUSD each (120 chips/w) – Needs Synchro btw TDCpix(NA 62) and ABC 30/04/13 ABC 130 ITk Meeting 8

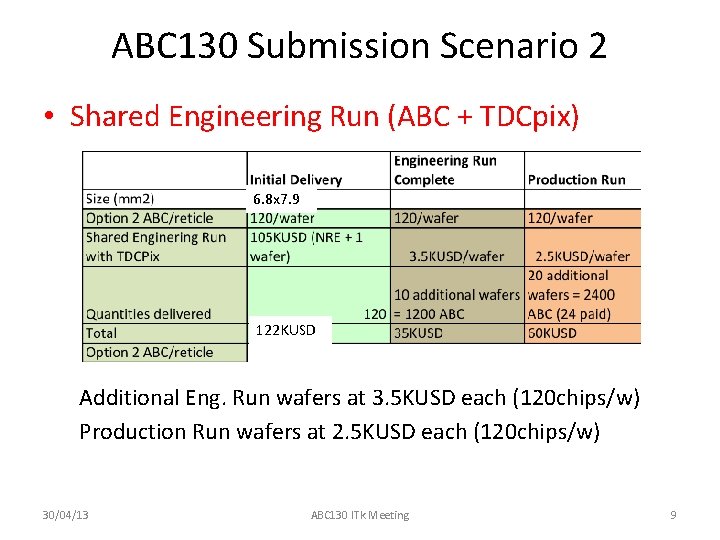

ABC 130 Submission Scenario 2 • Shared Engineering Run (ABC + TDCpix) 6. 8 x 7. 9 122 KUSD Additional Eng. Run wafers at 3. 5 KUSD each (120 chips/w) Production Run wafers at 2. 5 KUSD each (120 chips/w) 30/04/13 ABC 130 ITk Meeting 9

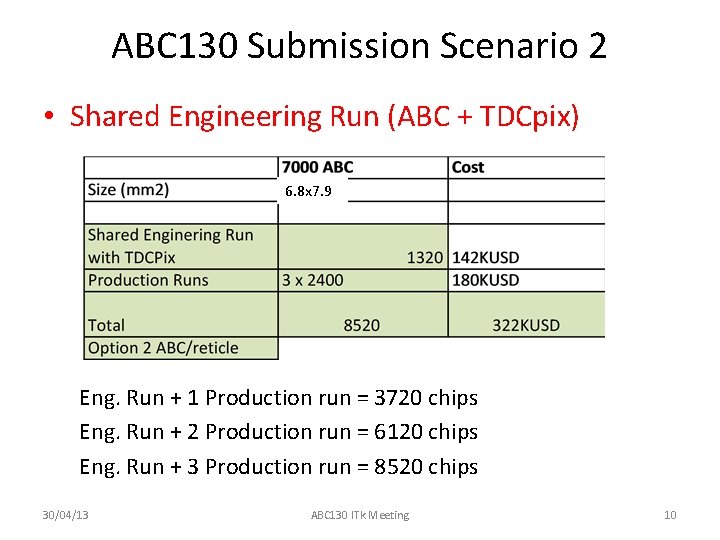

ABC 130 Submission Scenario 2 • Shared Engineering Run (ABC + TDCpix) 6. 8 x 7. 9 Eng. Run + 1 Production run = 3720 chips Eng. Run + 2 Production run = 6120 chips Eng. Run + 3 Production run = 8520 chips 30/04/13 ABC 130 ITk Meeting 10

- Slides: 10