A versatile FPGA based photon counter and correlator

A versatile FPGA based photon counter and correlator

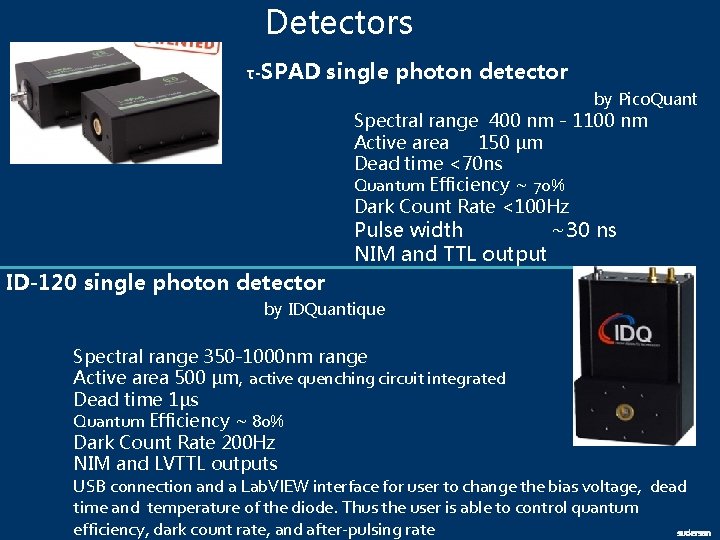

Detectors τ-SPAD single photon detector by Pico. Quant Spectral range 400 nm - 1100 nm Active area 150 µm Dead time <70 ns Quantum Efficiency ~ 70% Dark Count Rate <100 Hz Pulse width ~30 ns NIM and TTL output ID-120 single photon detector by IDQuantique Spectral range 350 -1000 nm range Active area 500 µm, active quenching circuit integrated Dead time 1µs Quantum Efficiency ~ 80% Dark Count Rate 200 Hz NIM and LVTTL outputs USB connection and a Lab. VIEW interface for user to change the bias voltage, dead time and temperature of the diode. Thus the user is able to control quantum efficiency, dark count rate, and after-pulsing rate

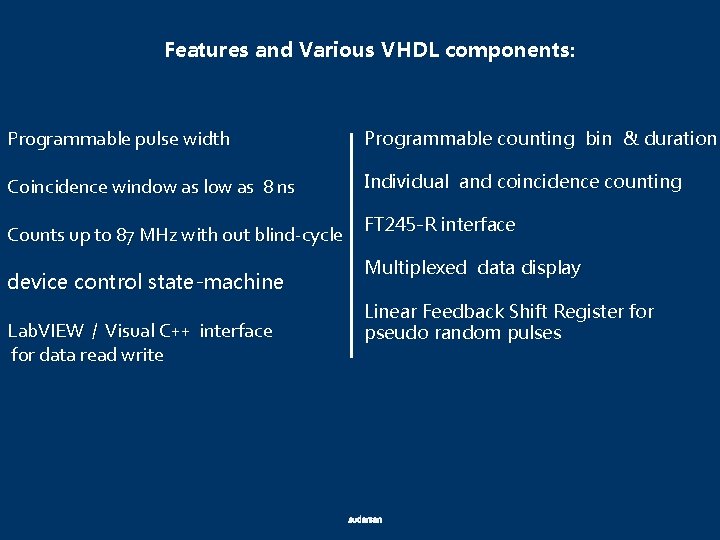

Features and Various VHDL components: Programmable pulse width Programmable counting bin & duration Coincidence window as low as 8 ns Individual and coincidence counting Counts up to 87 MHz with out blind-cycle device control state-machine Lab. VIEW / Visual C++ interface for data read write FT 245 -R interface Multiplexed data display Linear Feedback Shift Register for pseudo random pulses

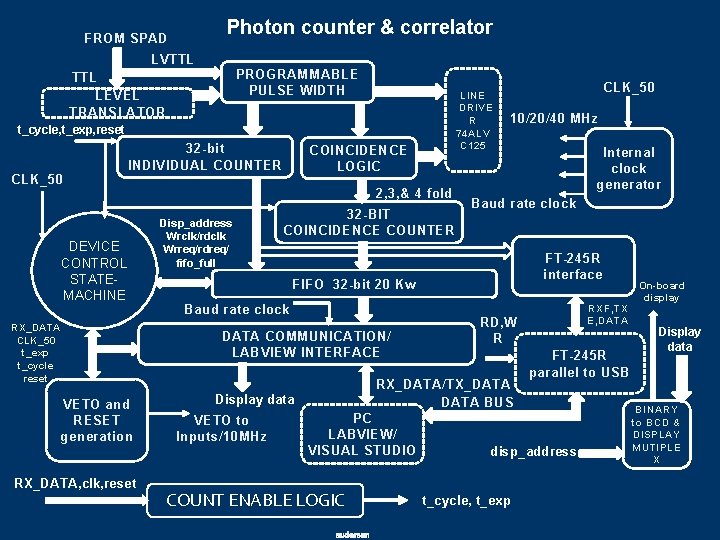

Photon counter & correlator FROM SPAD LVTTL PROGRAMMABLE PULSE WIDTH TTL LEVEL TRANSLATOR LINE DRIVE R 74 ALV C 125 t_cycle, t_exp, reset CLK_50 32 -bit INDIVIDUAL COUNTER DEVICE CONTROL STATEMACHINE RX_DATA CLK_50 t_exp t_cycle reset VETO and RESET generation RX_DATA, clk, reset COINCIDENCE LOGIC 2, 3, & 4 fold Disp_address Wrclk/rdclk Wrreq/rdreq/ fifo_full 32 -BIT COINCIDENCE COUNTER CLK_50 10/20/40 MHz Baud rate clock FT-245 R interface FIFO 32 -bit 20 Kw Baud rate clock DATA COMMUNICATION/ LABVIEW INTERFACE VETO to Inputs/10 MHz PC LABVIEW/ VISUAL STUDIO COUNT ENABLE LOGIC RXF, TX E, DATA RD, W R RX_DATA/TX_DATA BUS Display data Internal clock generator FT-245 R parallel to USB disp_address t_cycle, t_exp On-board display Display data BINARY to BCD & DISPLAY MUTIPLE X

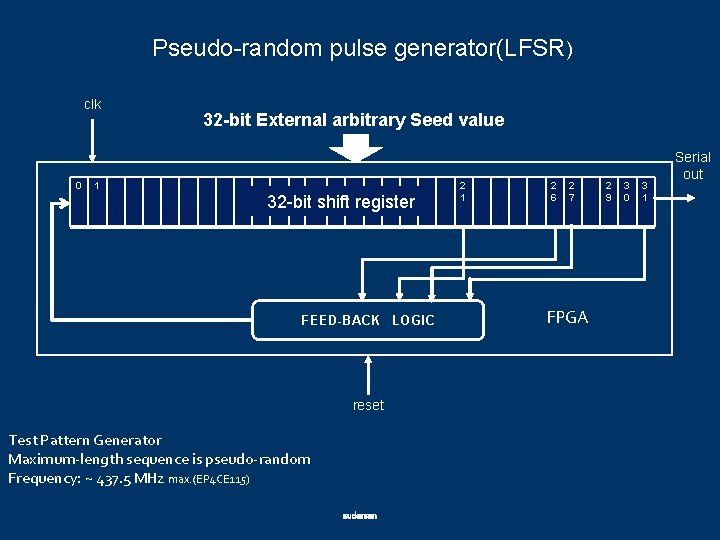

Pseudo-random pulse generator(LFSR) clk 0 1 32 -bit External arbitrary Seed value 32 -bit shift register FEED-BACK LOGIC reset Test Pattern Generator Maximum-length sequence is pseudo-random Frequency: ~ 437. 5 MHz max. (EP 4 CE 115) 2 1 2 6 2 7 FPGA 2 9 3 0 3 1 Serial out

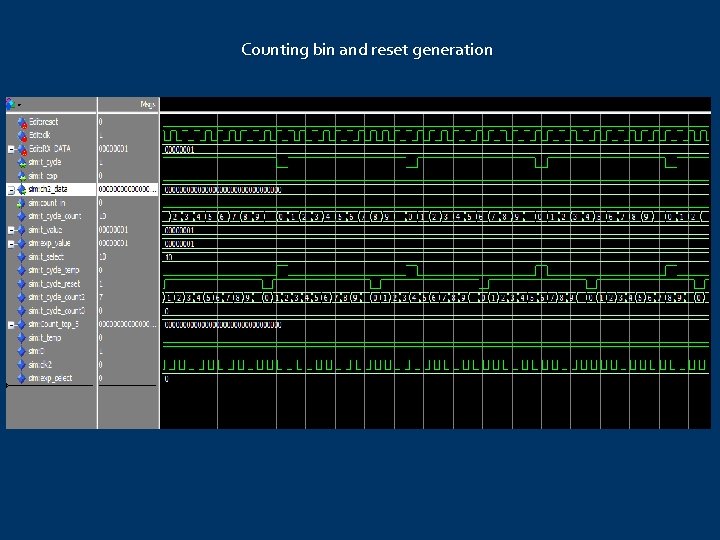

Counting bin and reset generation

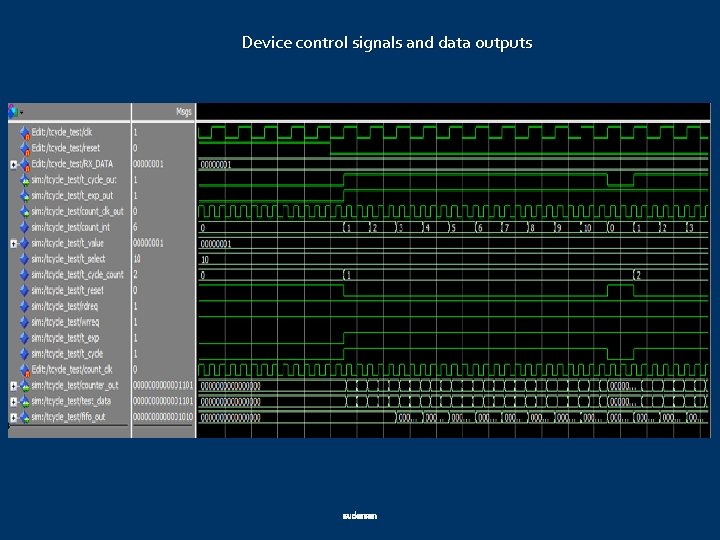

Device control signals and data outputs

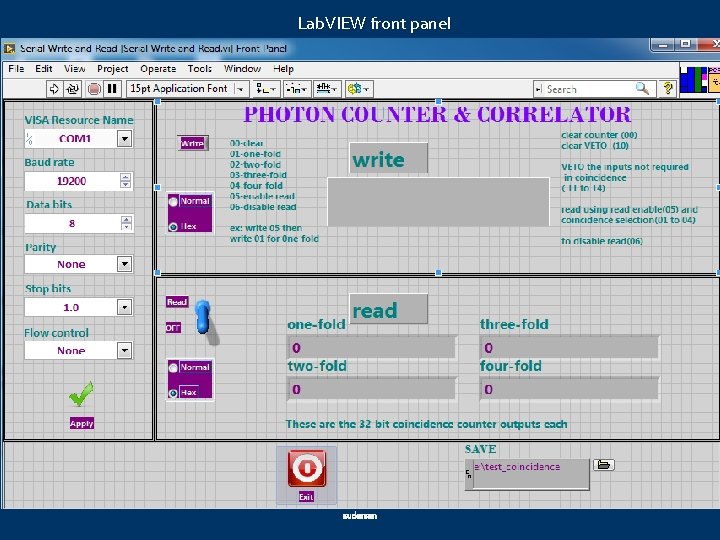

Lab. VIEW front panel

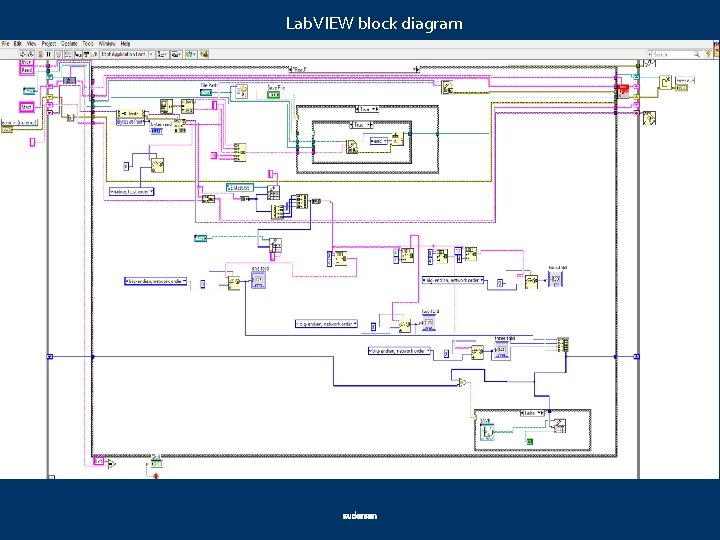

Lab. VIEW block diagram

- Slides: 10