A TestPerClock LFSR Reseeding Algorithm for Concurrent Reduction

- Slides: 22

A Test-Per-Clock LFSR Reseeding Algorithm for Concurrent Reduction on Test Sequence Length and Test Data Volume Wei-Cheng Lien 1, Kuen-Jong Lee 1 and Tong-Yu Hsieh 2 1 Dept. of Electrical Engineering, National Cheng Kung Univ. , Taiwan 2 Dept. of Electrical Engineering, National Sun Yat-sen Univ. , Taiwan NCKU EE Test. Lab

Outline n n n Introduction Previous Work Proposed Concurrent Multiple Test Embedding Procedure Experimental Results Comparisons Conclusions Asia Test Symposium 2012 2

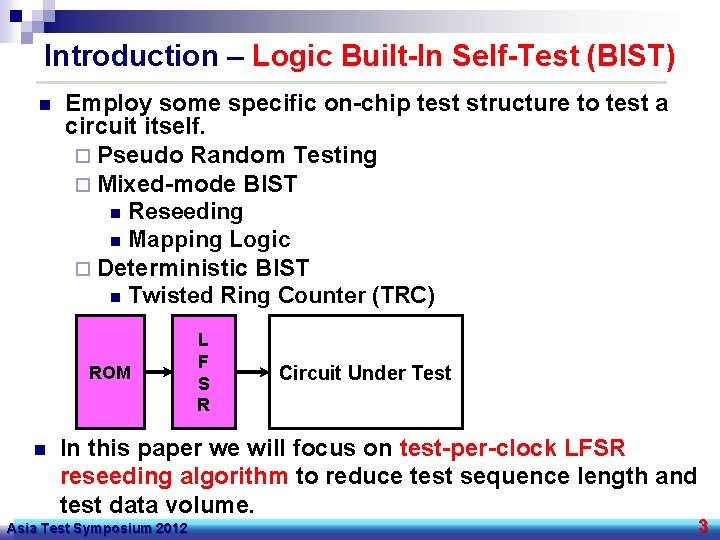

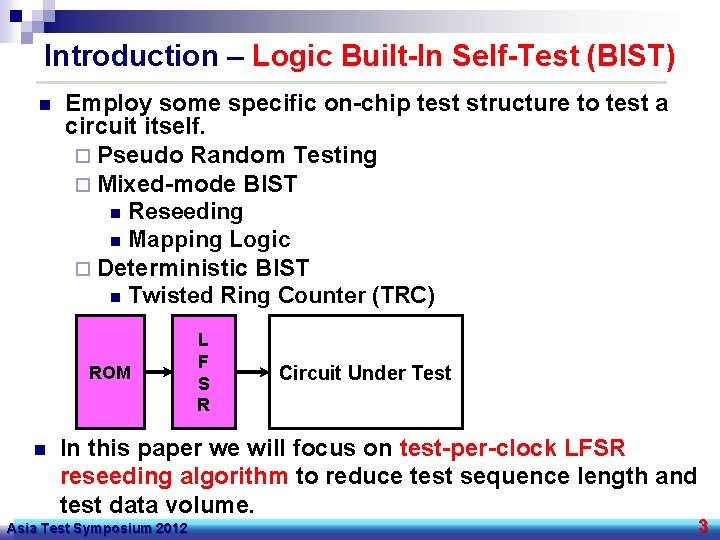

Introduction – Logic Built-In Self-Test (BIST) n Employ some specific on-chip test structure to test a circuit itself. ¨ Pseudo Random Testing ¨ Mixed-mode BIST n Reseeding n Mapping Logic ¨ Deterministic BIST n Twisted Ring Counter (TRC) ROM n L F S R Mapping Logic Circuit Under Test In this paper we will focus on test-per-clock LFSR reseeding algorithm to reduce test sequence length and test data volume. Asia Test Symposium 2012 3

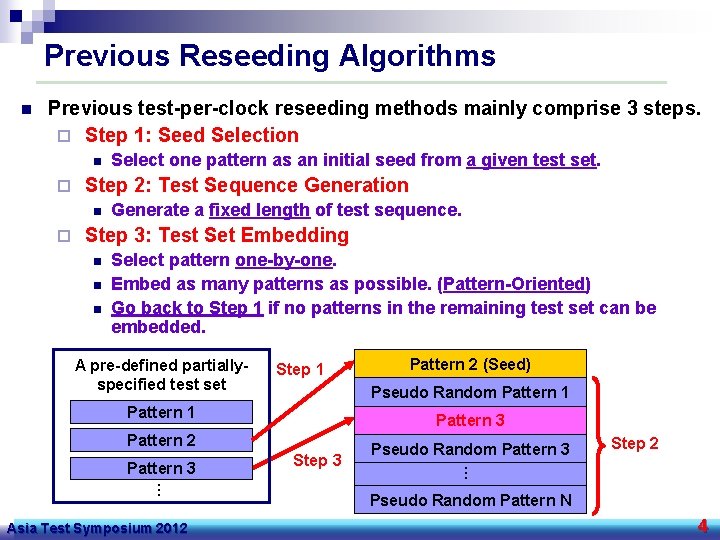

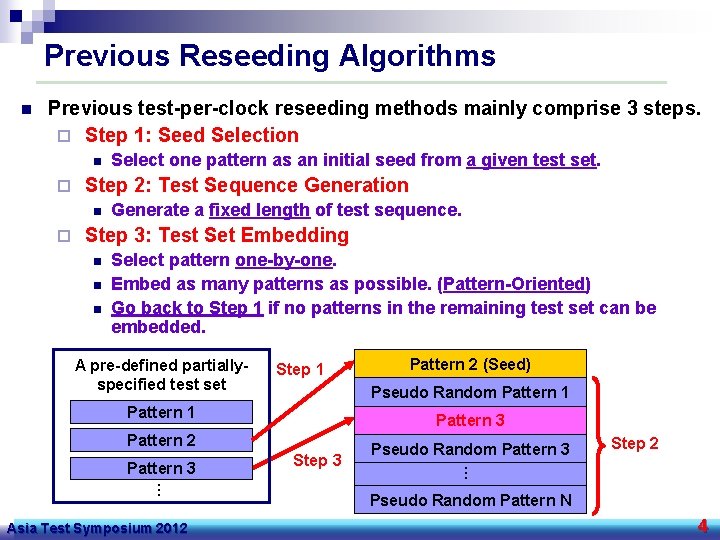

Previous Reseeding Algorithms n Previous test-per-clock reseeding methods mainly comprise 3 steps. ¨ Step 1: Seed Selection n ¨ Step 2: Test Sequence Generation n ¨ Select one pattern as an initial seed from a given test set. Generate a fixed length of test sequence. Step 3: Test Set Embedding n n n Select pattern one-by-one. Embed as many patterns as possible. (Pattern-Oriented) Go back to Step 1 if no patterns in the remaining test set can be embedded. A pre-defined partiallyspecified test set Step 1 Pseudo Random Pattern 1 Pattern 3 Pattern 2 Pseudo Random Pattern 2 … Asia Test Symposium 2012 Step 3 Pseudo Random Pattern 3 Step 2 … Pattern 3 Pattern 2 (Seed) Pseudo Random Pattern N 4

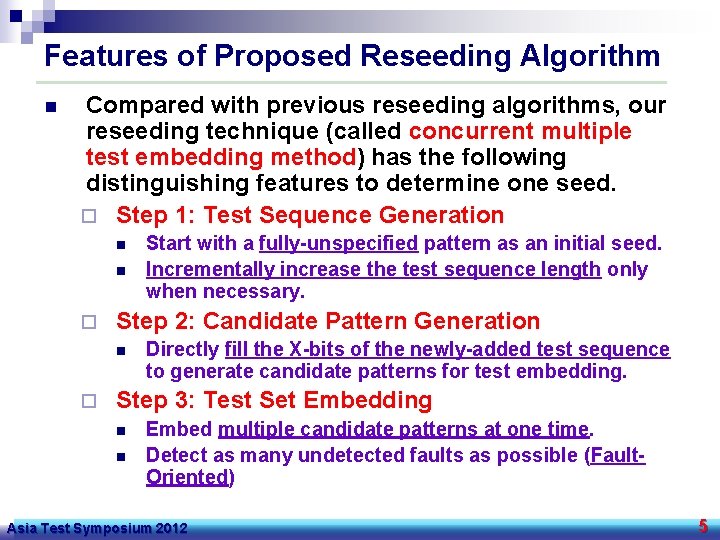

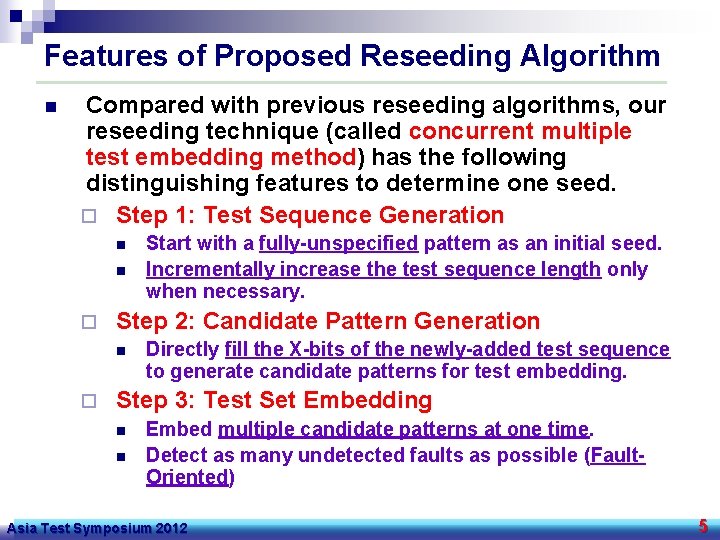

Features of Proposed Reseeding Algorithm n Compared with previous reseeding algorithms, our reseeding technique (called concurrent multiple test embedding method) has the following distinguishing features to determine one seed. ¨ Step 1: Test Sequence Generation n n ¨ Step 2: Candidate Pattern Generation n ¨ Start with a fully-unspecified pattern as an initial seed. Incrementally increase the test sequence length only when necessary. Directly fill the X-bits of the newly-added test sequence to generate candidate patterns for test embedding. Step 3: Test Set Embedding n n Embed multiple candidate patterns at one time. Detect as many undetected faults as possible (Fault. Oriented) Asia Test Symposium 2012 5

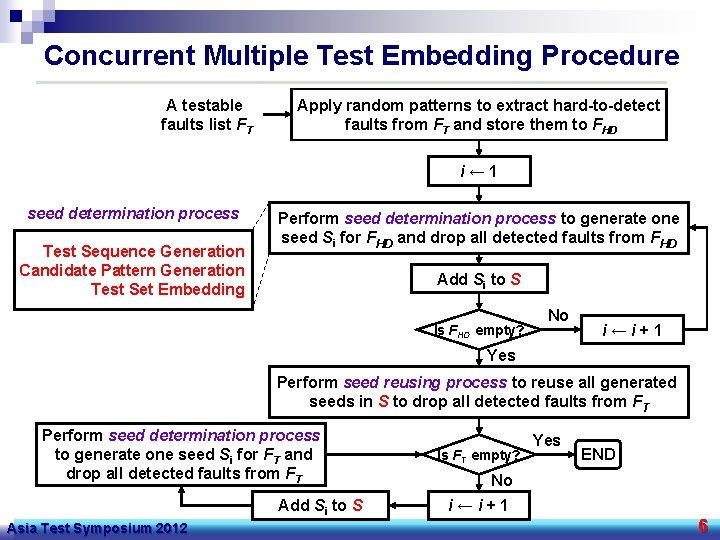

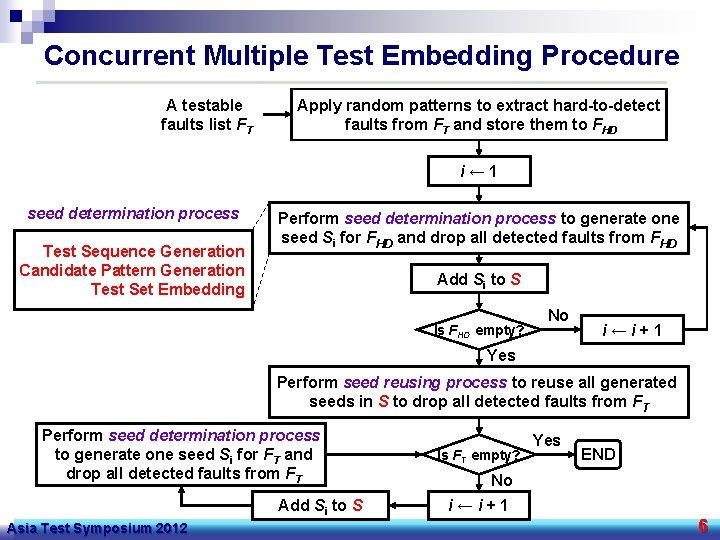

Concurrent Multiple Test Embedding Procedure A testable faults list FT Apply random patterns to extract hard-to-detect faults from FT and store them to FHD i← 1 seed determination process Test Sequence Generation Candidate Pattern Generation Test Set Embedding Perform seed determination process to generate one seed Si for FHD and drop all detected faults from FHD Add Si to S Is FHD empty? No i←i+1 Yes Perform seed reusing process to reuse all generated seeds in S to drop all detected faults from FT Perform seed determination process to generate one seed Si for FT and drop all detected faults from FT Add Si to S Asia Test Symposium 2012 Is FT empty? Yes END No i←i+1 6

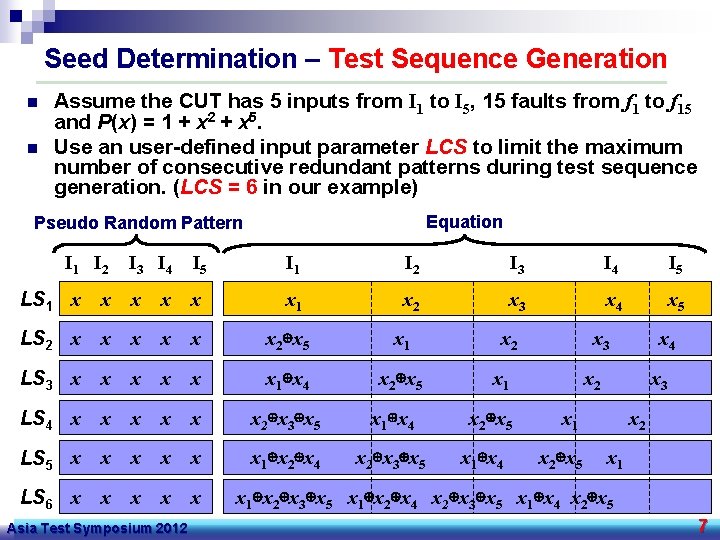

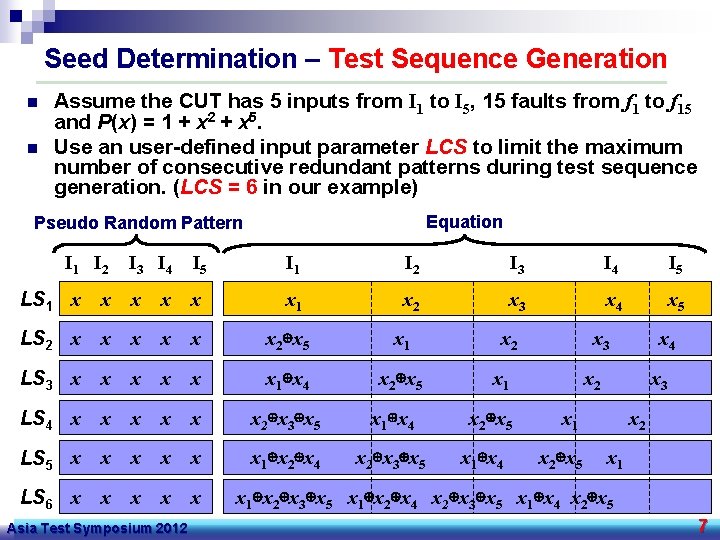

Seed Determination – Test Sequence Generation n n Assume the CUT has 5 inputs from I 1 to I 5, 15 faults from f 1 to f 15 and P(x) = 1 + x 2 + x 5. Use an user-defined input parameter LCS to limit the maximum number of consecutive redundant patterns during test sequence generation. (LCS = 6 in our example) Equation Pseudo Random Pattern I 1 I 2 I 3 I 4 I 5 x 1 x 2 x 3 x 4 x 5 LS 1 x x x LS 2 x x x 2⊕x 5 x 1 LS 3 x x x 1⊕x 4 x 2⊕x 5 LS 4 x x x 2⊕x 3⊕x 5 x 1⊕x 4 LS 5 x x x 1⊕x 2⊕x 4 x 2⊕x 3⊕x 5 LS 6 x x x Asia Test Symposium 2012 x 3 x 1 x 2⊕x 5 x 1⊕x 4 x 2 x 3 x 1 x 2⊕x 5 x 2 x 1⊕x 2⊕x 3⊕x 5 x 1⊕x 2⊕x 4 x 2⊕x 3⊕x 5 x 1⊕x 4 x 2⊕x 5 7

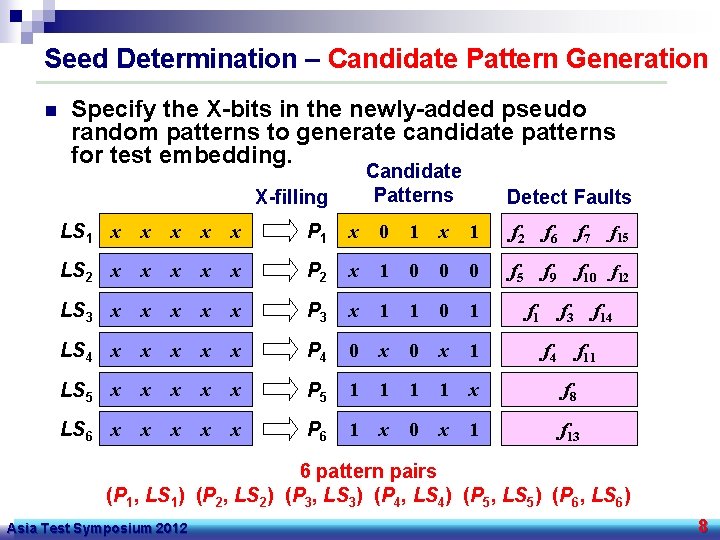

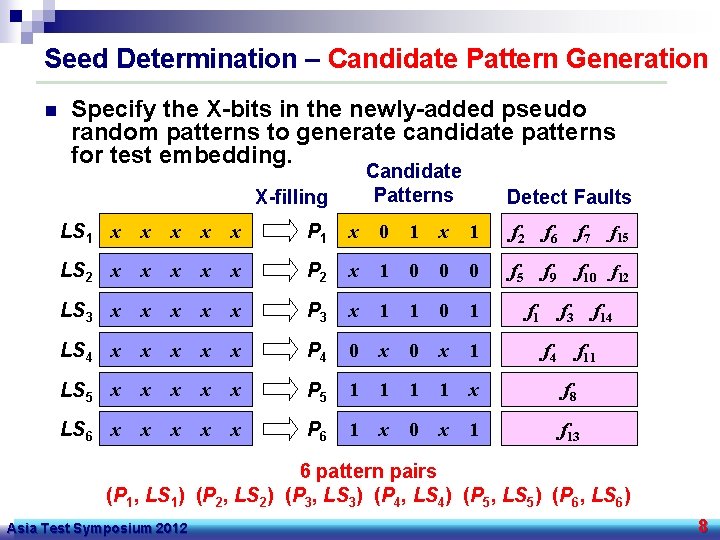

Seed Determination – Candidate Pattern Generation n Specify the X-bits in the newly-added pseudo random patterns to generate candidate patterns for test embedding. Candidate Patterns X-filling Detect Faults LS 1 x x x P 1 x 0 1 x 1 f 2 f 6 f 7 LS 2 x x x P 2 x 1 0 0 0 f 5 f 9 f 10 f 12 LS 3 x x x P 3 x 1 1 0 1 LS 4 x x x P 4 0 x 1 LS 5 x x x P 5 1 1 1 x f 8 LS 6 x x x P 6 1 x 0 x 1 f 13 1 f 3 f 4 f 15 f 14 f 11 6 pattern pairs (P 1, LS 1) (P 2, LS 2) (P 3, LS 3) (P 4, LS 4) (P 5, LS 5) (P 6, LS 6) Asia Test Symposium 2012 8

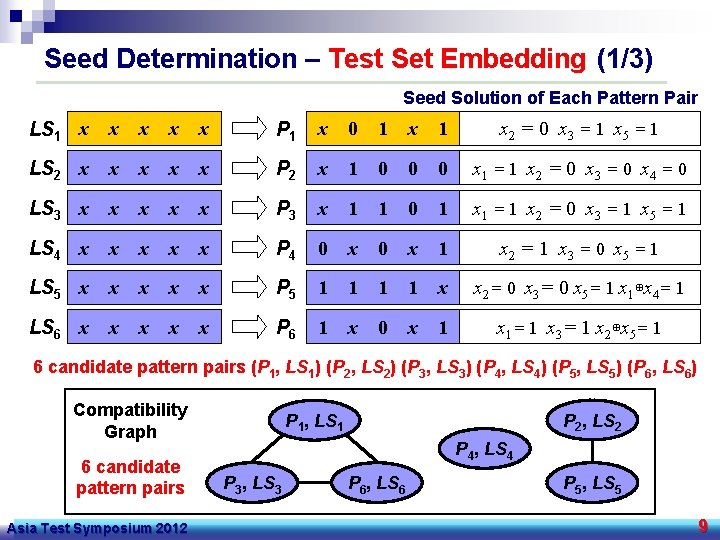

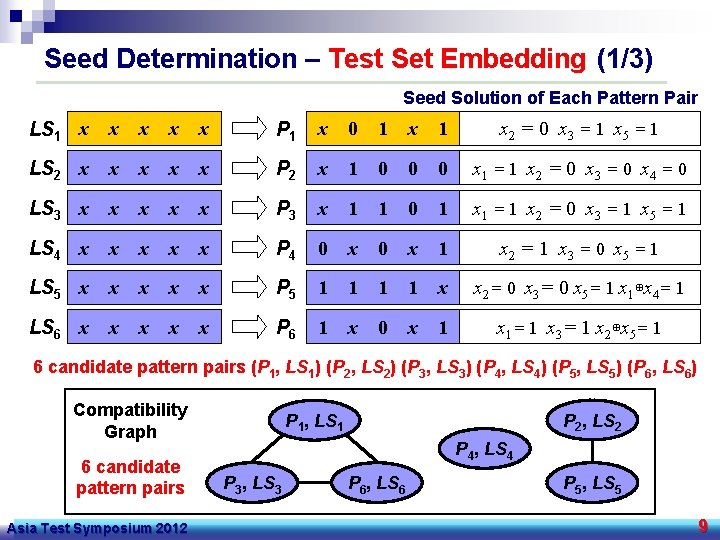

Seed Determination – Test Set Embedding (1/3) Seed Solution of Each Pattern Pair LS 1 x x x P 1 x 0 1 x 1 LS 2 x x x P 2 x 1 0 0 0 x 1 = 1 x 2 = 0 x 3 = 0 x 4 = 0 LS 3 x x x P 3 x 1 1 0 1 x 1 = 1 x 2 = 0 x 3 = 1 x 5 = 1 LS 4 x x x P 4 0 x 1 x 2 = 1 x 3 = 0 x 5 = 1 LS 5 x x x P 5 1 1 1 x x 2= 0 x 3= 0 x 5= 1 x 1⊕x 4= 1 LS 6 x x x P 6 1 x 0 x 1= 1 x 3= 1 x 2⊕x 5= 1 1 x 2 = 0 x 3 = 1 x 5 = 1 6 candidate pattern pairs (P 1, LS 1) (P 2, LS 2) (P 3, LS 3) (P 4, LS 4) (P 5, LS 5) (P 6, LS 6) Compatibility Graph 6 candidate pattern pairs Asia Test Symposium 2012 P 2, LS 2 P 1, LS 1 P 4, LS 4 P 3, LS 3 P 6, LS 6 P 5, LS 5 9

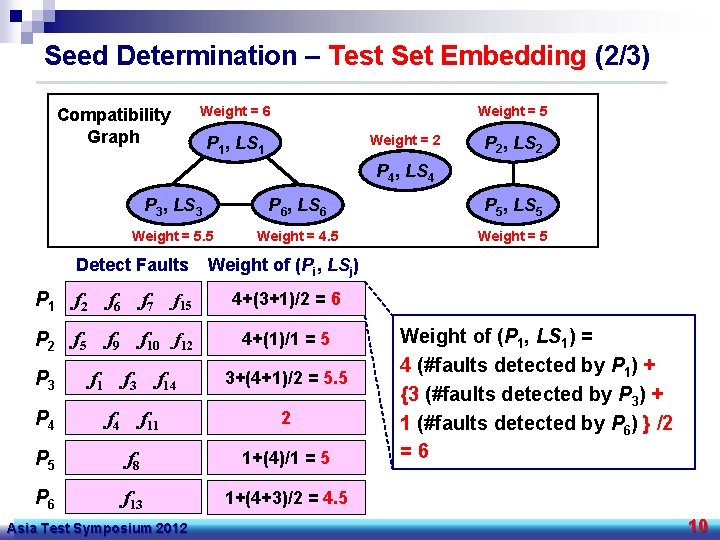

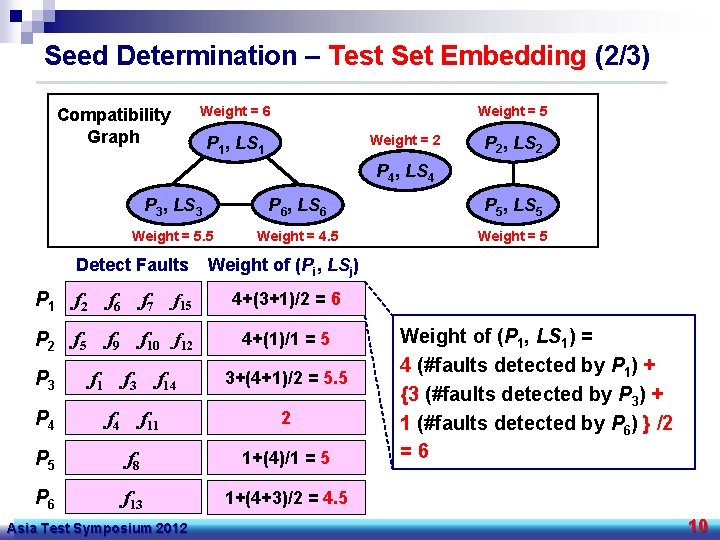

Seed Determination – Test Set Embedding (2/3) Weight = 6 Compatibility Graph Weight = 5 Weight = 2 P 1, LS 1 P 2, LS 2 P 4, LS 4 P 3, LS 3 P 6, LS 6 P 5, LS 5 Weight = 5. 5 Weight = 4. 5 Weight = 5 Detect Faults Weight of (Pi, LSj) P 1 f 2 f 6 f 7 P 2 f 5 f 9 f 10 f 12 4+(1)/1 = 5 f 14 3+(4+1)/2 = 5. 5 P 3 P 4 f 1 f 3 f 4 f 15 f 11 4+(3+1)/2 = 6 2 P 5 f 8 1+(4)/1 = 5 P 6 f 13 1+(4+3)/2 = 4. 5 Asia Test Symposium 2012 Weight of (P 1, LS 1) = 4 (#faults detected by P 1) + {3 (#faults detected by P 3) + 1 (#faults detected by P 6) } /2 =6 10

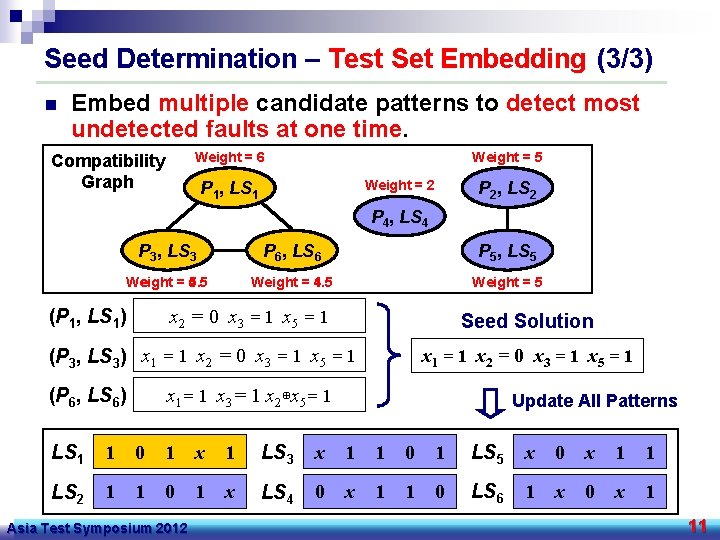

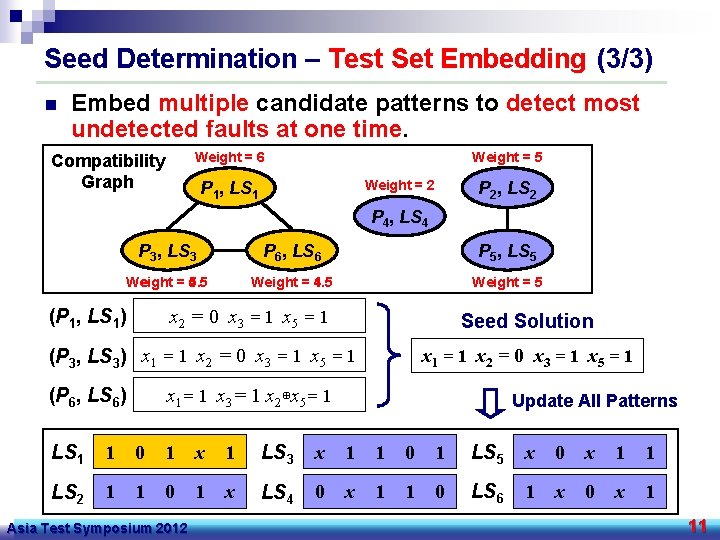

Seed Determination – Test Set Embedding (3/3) n Embed multiple candidate patterns to detect most undetected faults at one time. Weight = 5 Weight = 6 Compatibility Graph Weight = 2 P 1, LS 1 P 2, LS 2 P 4, LS 4 P 3, LS 3 P 6, LS 6 P 5, LS 5 Weight = 5. 5 4 Weight = 1 4 4. 5 Weight = 5 (P 1, LS 1) x 2 = 0 x 3 = 1 x 5 = 1 Seed Solution (P 3, LS 3) x 1 = 1 x 2 = 0 x 3 = 1 x 5 = 1 (P 6, LS 6) x 1 = 1 x 2 = 0 x 3 = 1 x 5 = 1 x 1= 1 x 3= 1 x 2⊕x 5= 1 Update All Patterns LS 1 1 0 1 x 1 LS 3 x 1 0 1 LS 5 x 0 x 1 1 LS 2 1 1 1 x LS 4 0 x 1 1 0 LS 6 1 x 0 x 1 0 Asia Test Symposium 2012 1 11

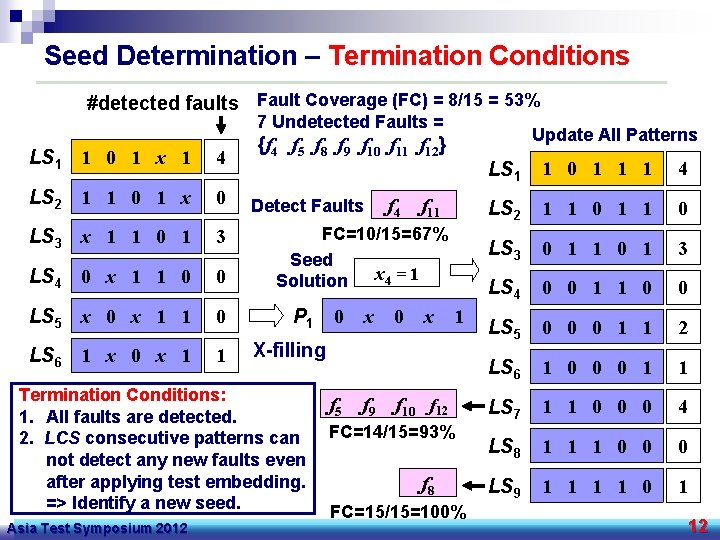

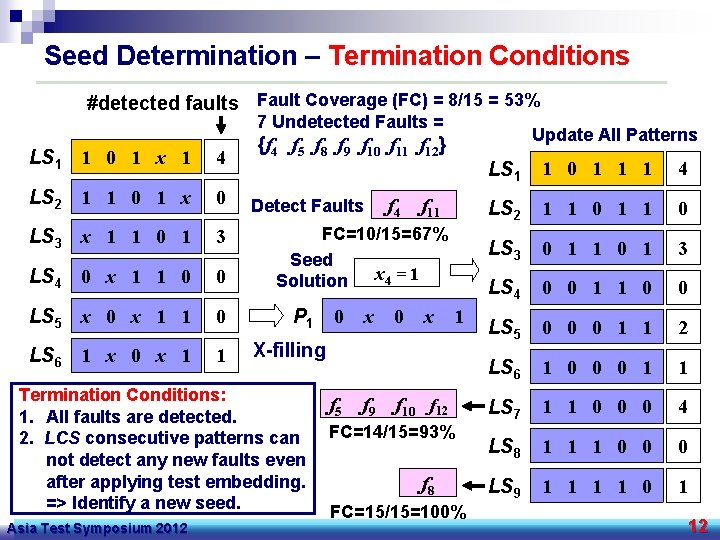

Seed Determination – Termination Conditions #detected faults Fault Coverage (FC) = 8/15 = 53% 7 Undetected Faults = LS 1 1 0 1 x 1 4 LS 2 1 1 0 1 x 0 LS 3 x 1 1 0 1 3 LS 4 0 x 1 1 0 0 LS 5 x 0 x 1 1 0 LS 6 1 x 0 x 1 1 {f 4 f 5 f 8 f 9 f 10 f 11 f 12} Detect Faults f 11 FC=10/15=67% Seed Solution x 4 = 1 P 1 0 x 1 X-filling Termination Conditions: 1. All faults are detected. 2. LCS consecutive patterns can not detect any new faults even after applying test embedding. => Identify a new seed. Asia Test Symposium 2012 f 4 f 5 f 9 f 10 f 12 FC=14/15=93% f 8 FC=15/15=100% Update All Patterns LS 1 1 0 1 1 1 4 LS 2 1 1 0 LS 3 0 1 1 0 1 3 LS 4 0 0 1 1 0 0 LS 5 0 0 0 1 1 2 LS 6 1 0 0 0 1 1 LS 7 1 1 0 0 0 4 LS 8 1 1 1 0 0 0 LS 9 1 1 0 1 12

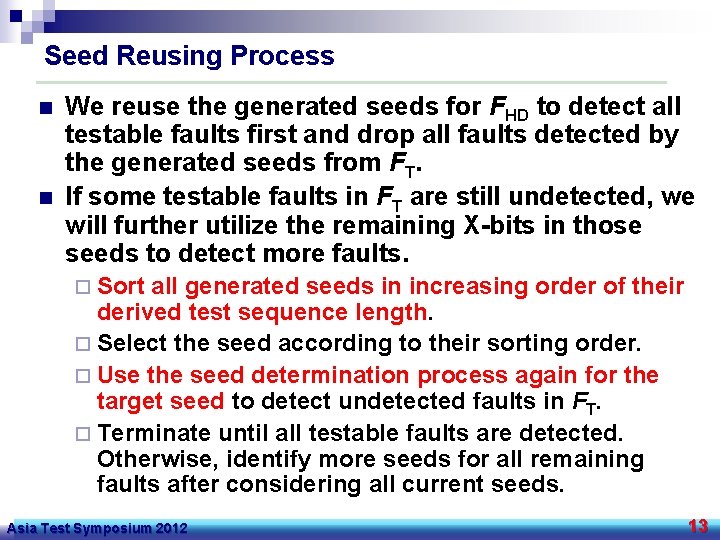

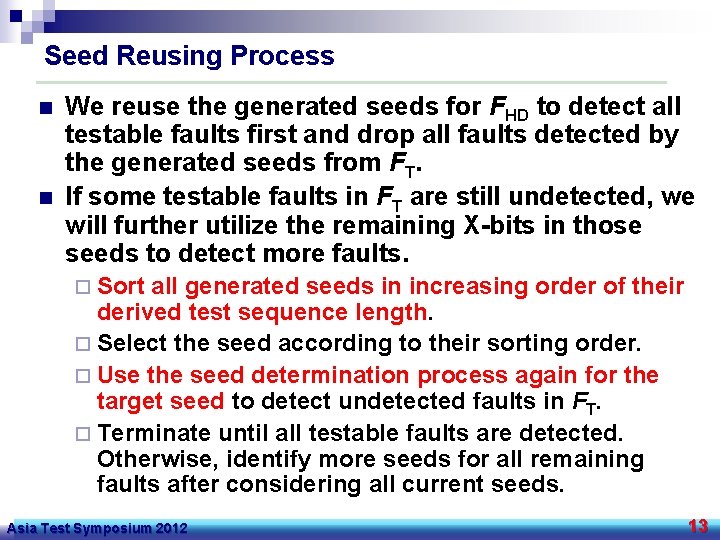

Seed Reusing Process n n We reuse the generated seeds for FHD to detect all testable faults first and drop all faults detected by the generated seeds from FT. If some testable faults in FT are still undetected, we will further utilize the remaining X-bits in those seeds to detect more faults. ¨ Sort all generated seeds in increasing order of their derived test sequence length. ¨ Select the seed according to their sorting order. ¨ Use the seed determination process again for the target seed to detect undetected faults in FT. ¨ Terminate until all testable faults are detected. Otherwise, identify more seeds for all remaining faults after considering all current seeds. Asia Test Symposium 2012 13

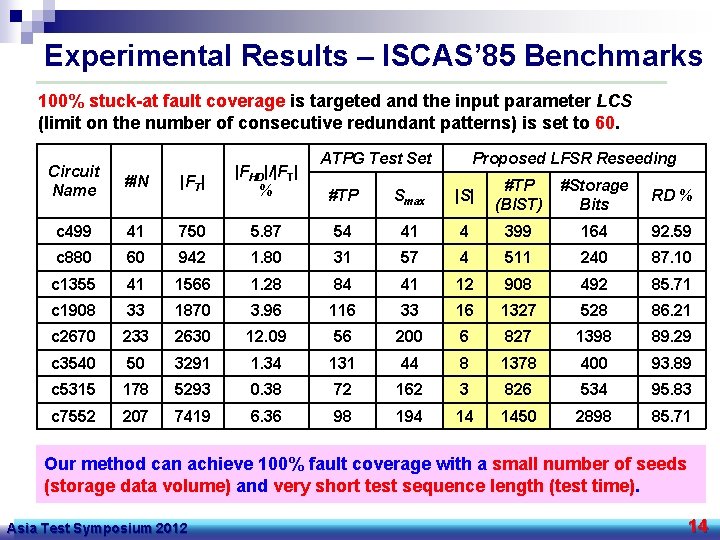

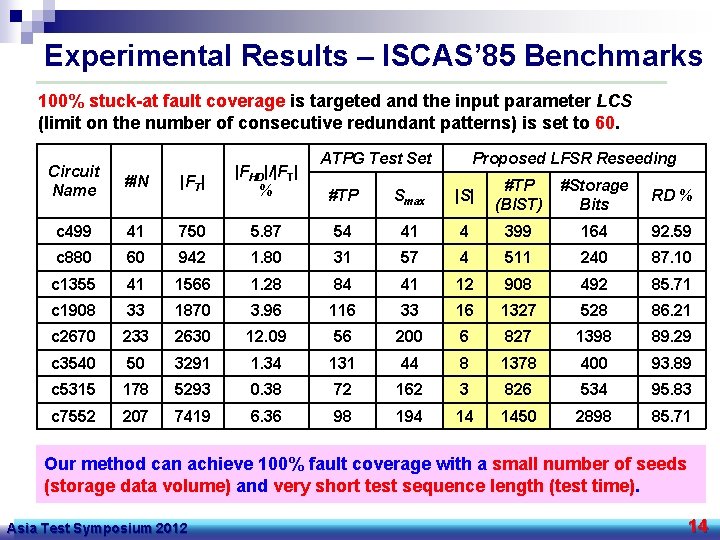

Experimental Results – ISCAS’ 85 Benchmarks 100% stuck-at fault coverage is targeted and the input parameter LCS (limit on the number of consecutive redundant patterns) is set to 60. Circuit Name #IN |FT| |FHD|/|FT| % c 499 41 750 c 880 60 c 1355 ATPG Test Set Proposed LFSR Reseeding #TP Smax |S| #TP (BIST) #Storage Bits RD % 5. 87 54 41 4 399 164 92. 59 942 1. 80 31 57 4 511 240 87. 10 41 1566 1. 28 84 41 12 908 492 85. 71 c 1908 33 1870 3. 96 116 33 16 1327 528 86. 21 c 2670 233 2630 12. 09 56 200 6 827 1398 89. 29 c 3540 50 3291 1. 34 131 44 8 1378 400 93. 89 c 5315 178 5293 0. 38 72 162 3 826 534 95. 83 c 7552 207 7419 6. 36 98 194 14 1450 2898 85. 71 Our method can achieve 100% fault coverage with a small number of seeds (storage data volume) and very short test sequence length (test time). Asia Test Symposium 2012 14

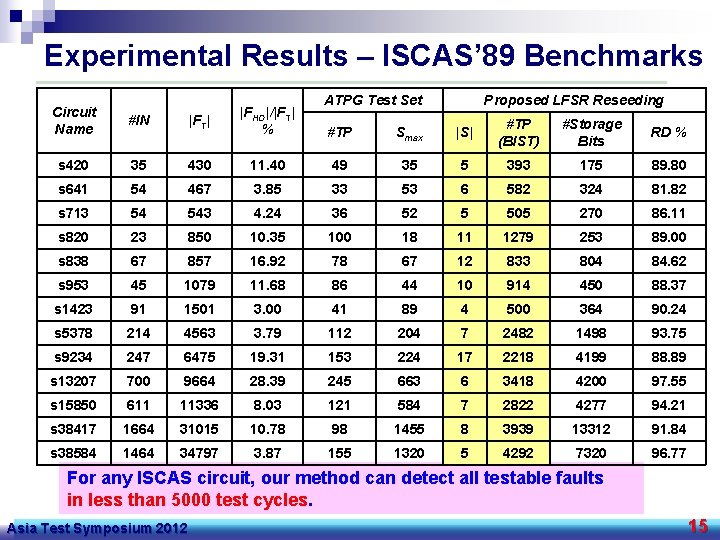

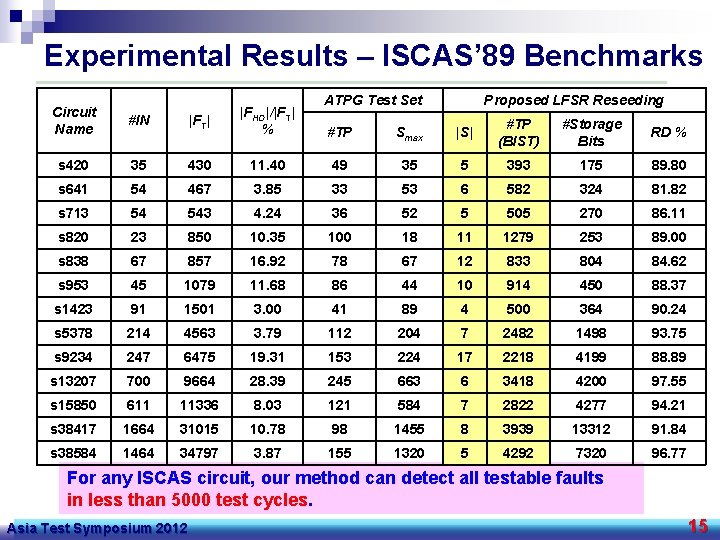

Experimental Results – ISCAS’ 89 Benchmarks Circuit Name #IN |FT| |FHD|/|FT| % s 420 35 430 s 641 54 s 713 ATPG Test Set Proposed LFSR Reseeding #TP Smax |S| #TP (BIST) #Storage Bits RD % 11. 40 49 35 5 393 175 89. 80 467 3. 85 33 53 6 582 324 81. 82 54 543 4. 24 36 52 5 505 270 86. 11 s 820 23 850 10. 35 100 18 11 1279 253 89. 00 s 838 67 857 16. 92 78 67 12 833 804 84. 62 s 953 45 1079 11. 68 86 44 10 914 450 88. 37 s 1423 91 1501 3. 00 41 89 4 500 364 90. 24 s 5378 214 4563 3. 79 112 204 7 2482 1498 93. 75 s 9234 247 6475 19. 31 153 224 17 2218 4199 88. 89 s 13207 700 9664 28. 39 245 663 6 3418 4200 97. 55 s 15850 611 11336 8. 03 121 584 7 2822 4277 94. 21 s 38417 1664 31015 10. 78 98 1455 8 3939 13312 91. 84 s 38584 1464 34797 3. 87 155 1320 5 4292 7320 96. 77 For any ISCAS circuit, our method can detect all testable faults in less than 5000 test cycles. Asia Test Symposium 2012 15

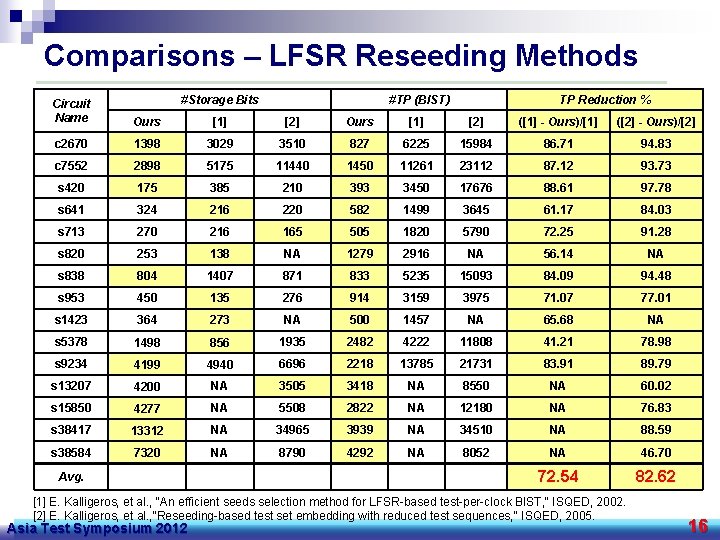

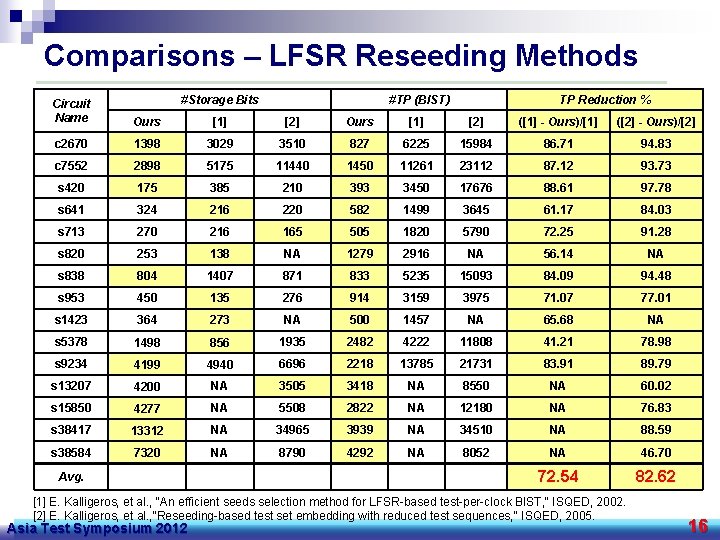

Comparisons – LFSR Reseeding Methods #Storage Bits #TP (BIST) TP Reduction % Circuit Name Ours [1] [2] ([1] - Ours)/[1] ([2] - Ours)/[2] c 2670 1398 3029 3510 827 6225 15984 86. 71 94. 83 c 7552 2898 5175 11440 1450 11261 23112 87. 12 93. 73 s 420 175 385 210 393 3450 17676 88. 61 97. 78 s 641 324 216 220 582 1499 3645 61. 17 84. 03 s 713 270 216 165 505 1820 5790 72. 25 91. 28 s 820 253 138 NA 1279 2916 NA 56. 14 NA s 838 804 1407 871 833 5235 15093 84. 09 94. 48 s 953 450 135 276 914 3159 3975 71. 07 77. 01 s 1423 364 273 NA 500 1457 NA 65. 68 NA s 5378 1498 856 1935 2482 4222 11808 41. 21 78. 98 s 9234 4199 4940 6696 2218 13785 21731 83. 91 89. 79 s 13207 4200 NA 3505 3418 NA 8550 NA 60. 02 s 15850 4277 NA 5508 2822 NA 12180 NA 76. 83 s 38417 13312 NA 34965 3939 NA 34510 NA 88. 59 s 38584 7320 NA 8790 4292 NA 8052 NA 46. 70 72. 54 82. 62 Avg. [1] E. Kalligeros, et al. , "An efficient seeds selection method for LFSR-based test-per-clock BIST, “ ISQED, 2002. [2] E. Kalligeros, et al. , "Reseeding-based test set embedding with reduced test sequences, " ISQED, 2005. Asia Test Symposium 2012 16

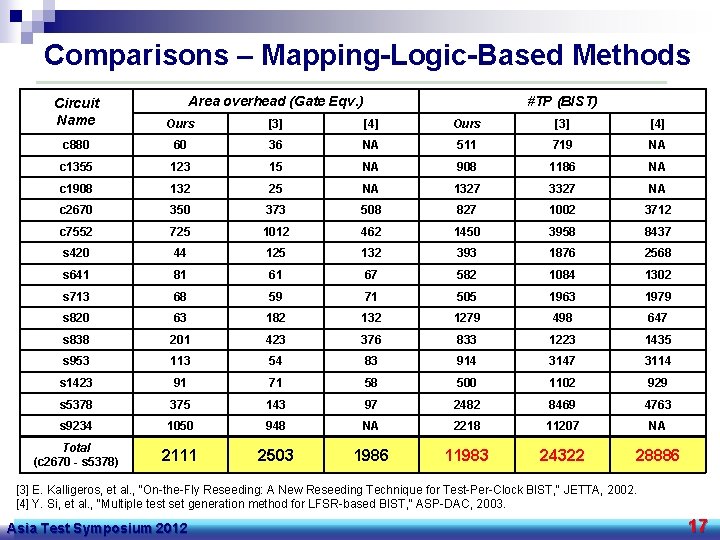

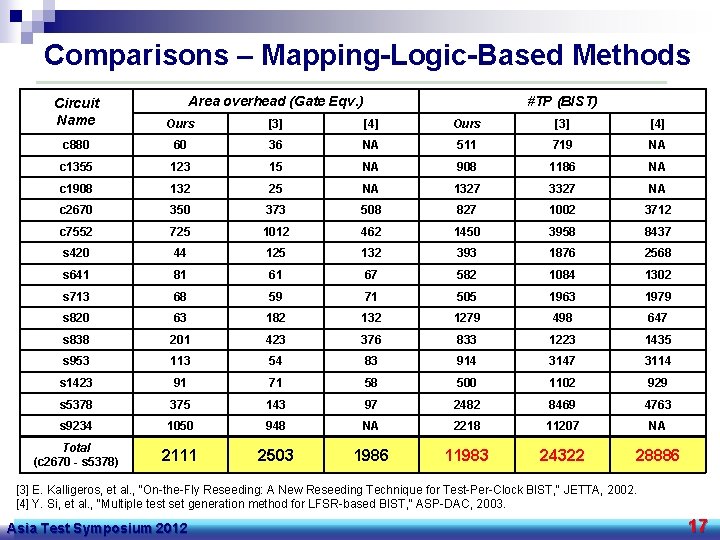

Comparisons – Mapping-Logic-Based Methods Area overhead (Gate Eqv. ) #TP (BIST) Circuit Name Ours [3] [4] c 880 60 36 NA 511 719 NA c 1355 123 15 NA 908 1186 NA c 1908 132 25 NA 1327 3327 NA c 2670 350 373 508 827 1002 3712 c 7552 725 1012 462 1450 3958 8437 s 420 44 125 132 393 1876 2568 s 641 81 61 67 582 1084 1302 s 713 68 59 71 505 1963 1979 s 820 63 182 132 1279 498 647 s 838 201 423 376 833 1223 1435 s 953 113 54 83 914 3147 3114 s 1423 91 71 58 500 1102 929 s 5378 375 143 97 2482 8469 4763 s 9234 1050 948 NA 2218 11207 NA Total (c 2670 - s 5378) 2111 2503 1986 11983 24322 28886 [3] E. Kalligeros, et al. , "On-the-Fly Reseeding: A New Reseeding Technique for Test-Per-Clock BIST, " JETTA, 2002. [4] Y. Si, et al. , "Multiple test set generation method for LFSR-based BIST, " ASP-DAC, 2003. Asia Test Symposium 2012 17

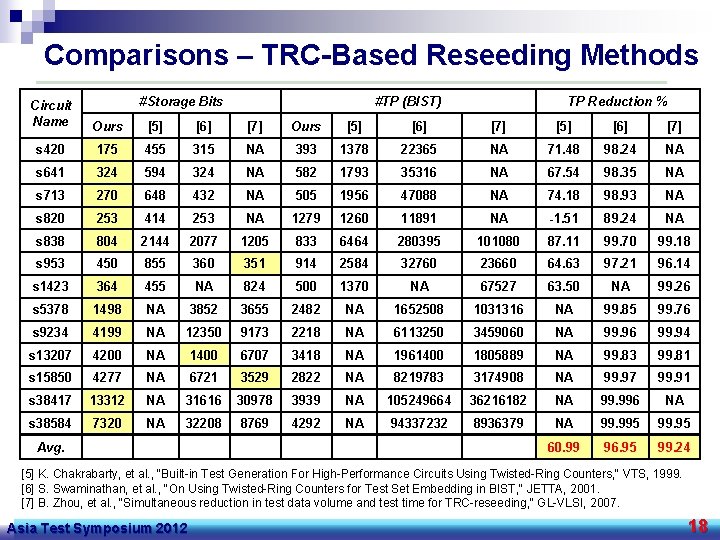

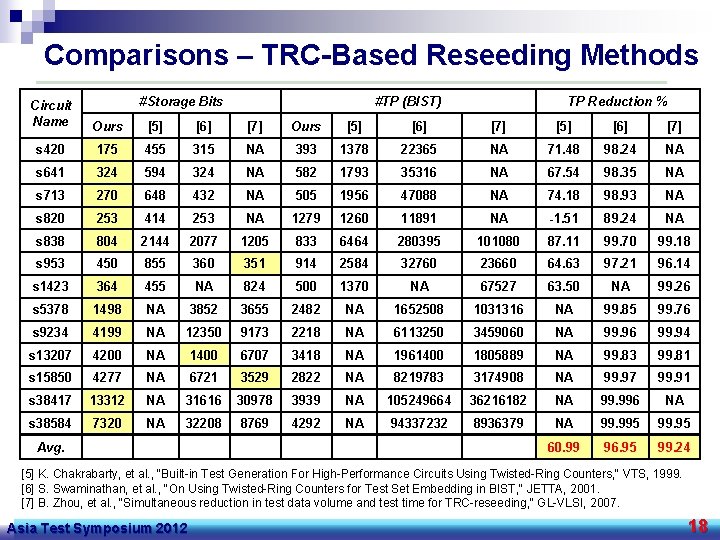

Comparisons – TRC-Based Reseeding Methods #Storage Bits #TP (BIST) TP Reduction % Circuit Name Ours [5] [6] [7] s 420 175 455 315 NA 393 1378 22365 NA 71. 48 98. 24 NA s 641 324 594 324 NA 582 1793 35316 NA 67. 54 98. 35 NA s 713 270 648 432 NA 505 1956 47088 NA 74. 18 98. 93 NA s 820 253 414 253 NA 1279 1260 11891 NA -1. 51 89. 24 NA s 838 804 2144 2077 1205 833 6464 280395 101080 87. 11 99. 70 99. 18 s 953 450 855 360 351 914 2584 32760 23660 64. 63 97. 21 96. 14 s 1423 364 455 NA 824 500 1370 NA 67527 63. 50 NA 99. 26 s 5378 1498 NA 3852 3655 2482 NA 1652508 1031316 NA 99. 85 99. 76 s 9234 4199 NA 12350 9173 2218 NA 6113250 3459060 NA 99. 96 99. 94 s 13207 4200 NA 1400 6707 3418 NA 1961400 1805889 NA 99. 83 99. 81 s 15850 4277 NA 6721 3529 2822 NA 8219783 3174908 NA 99. 97 99. 91 s 38417 13312 NA 31616 30978 3939 NA 105249664 36216182 NA 99. 996 NA s 38584 7320 NA 32208 8769 4292 NA 94337232 8936379 NA 99. 995 99. 95 60. 99 96. 95 99. 24 Avg. [5] K. Chakrabarty, et al. , "Built-in Test Generation For High-Performance Circuits Using Twisted-Ring Counters, " VTS, 1999. [6] S. Swaminathan, et al. , "On Using Twisted-Ring Counters for Test Set Embedding in BIST, " JETTA, 2001. [7] B. Zhou, et al. , "Simultaneous reduction in test data volume and test time for TRC-reseeding, " GL-VLSI, 2007. Asia Test Symposium 2012 18

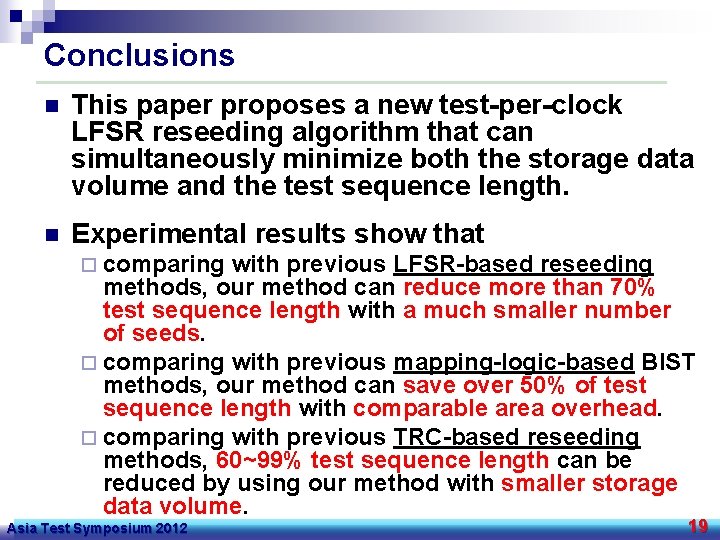

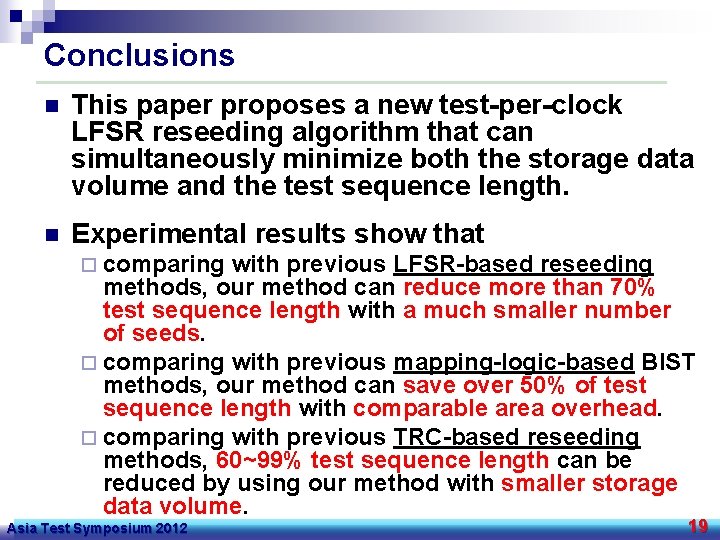

Conclusions n This paper proposes a new test-per-clock LFSR reseeding algorithm that can simultaneously minimize both the storage data volume and the test sequence length. n Experimental results show that ¨ comparing with previous LFSR-based reseeding methods, our method can reduce more than 70% test sequence length with a much smaller number of seeds. ¨ comparing with previous mapping-logic-based BIST methods, our method can save over 50% of test sequence length with comparable area overhead. ¨ comparing with previous TRC-based reseeding methods, 60~99% test sequence length can be reduced by using our method with smaller storage data volume. Asia Test Symposium 2012 19

Thank You Very Much for Your Attention. Asia Test Symposium 2012 20

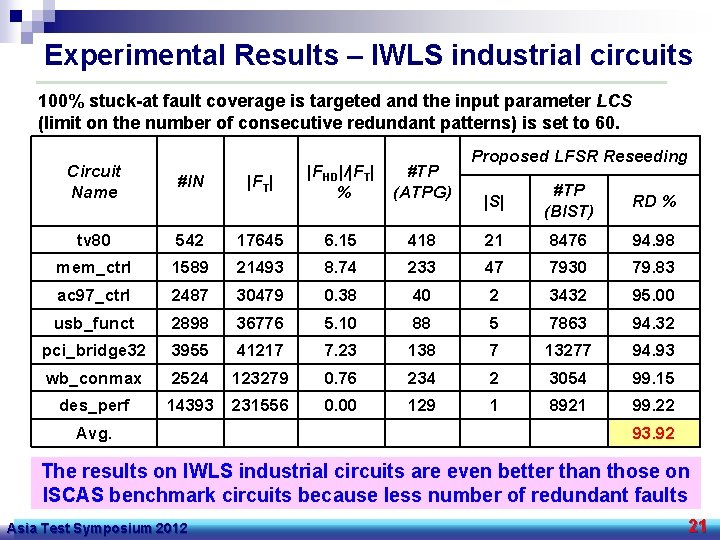

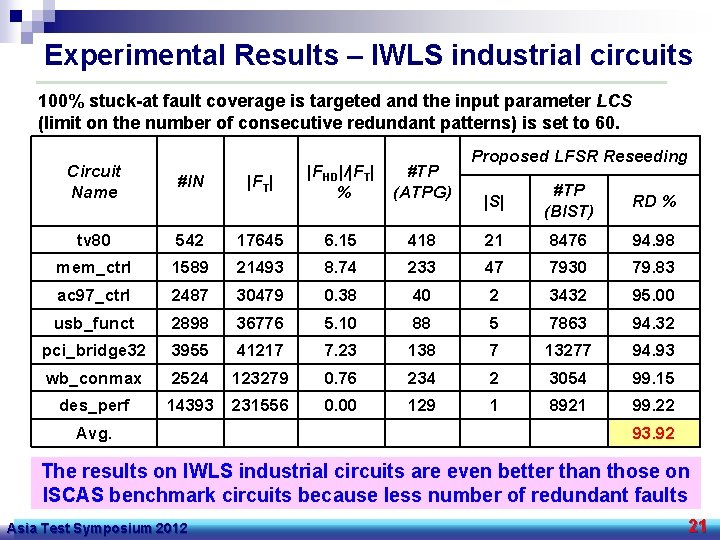

Experimental Results – IWLS industrial circuits 100% stuck-at fault coverage is targeted and the input parameter LCS (limit on the number of consecutive redundant patterns) is set to 60. Circuit Name #IN |FT| |FHD|/|FT| % #TP (ATPG) tv 80 542 17645 6. 15 mem_ctrl 1589 21493 ac 97_ctrl 2487 usb_funct Proposed LFSR Reseeding |S| #TP (BIST) RD % 418 21 8476 94. 98 8. 74 233 47 7930 79. 83 30479 0. 38 40 2 3432 95. 00 2898 36776 5. 10 88 5 7863 94. 32 pci_bridge 32 3955 41217 7. 23 138 7 13277 94. 93 wb_conmax 2524 123279 0. 76 234 2 3054 99. 15 des_perf 14393 231556 0. 00 129 1 8921 99. 22 Avg. 93. 92 The results on IWLS industrial circuits are even better than those on ISCAS benchmark circuits because less number of redundant faults Asia Test Symposium 2012 21

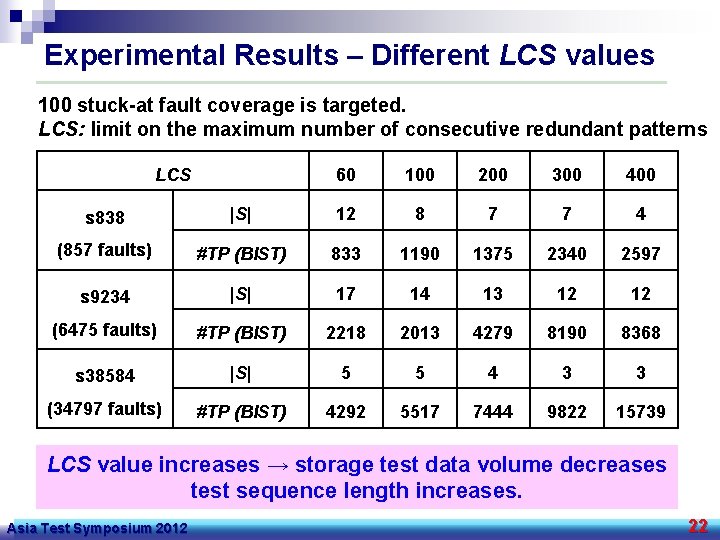

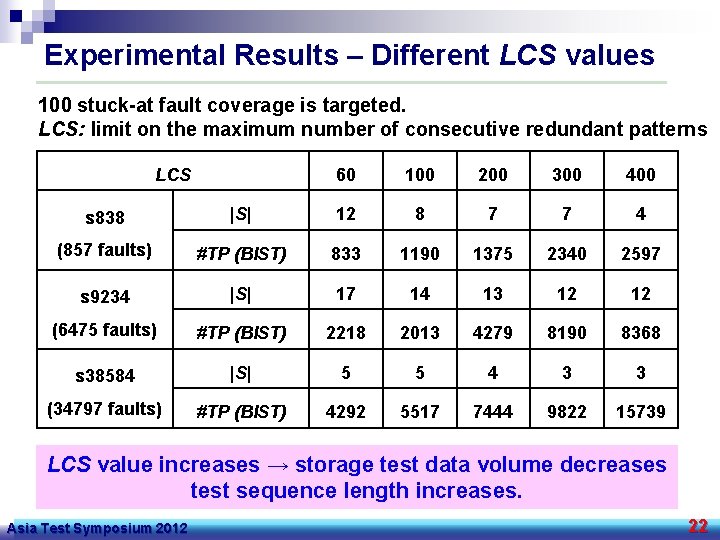

Experimental Results – Different LCS values 100 stuck-at fault coverage is targeted. LCS: limit on the maximum number of consecutive redundant patterns LCS 60 100 200 300 400 s 838 |S| 12 8 7 7 4 (857 faults) #TP (BIST) 833 1190 1375 2340 2597 s 9234 |S| 17 14 13 12 12 (6475 faults) #TP (BIST) 2218 2013 4279 8190 8368 s 38584 |S| 5 5 4 3 3 (34797 faults) #TP (BIST) 4292 5517 7444 9822 15739 LCS value increases → storage test data volume decreases test sequence length increases. Asia Test Symposium 2012 22