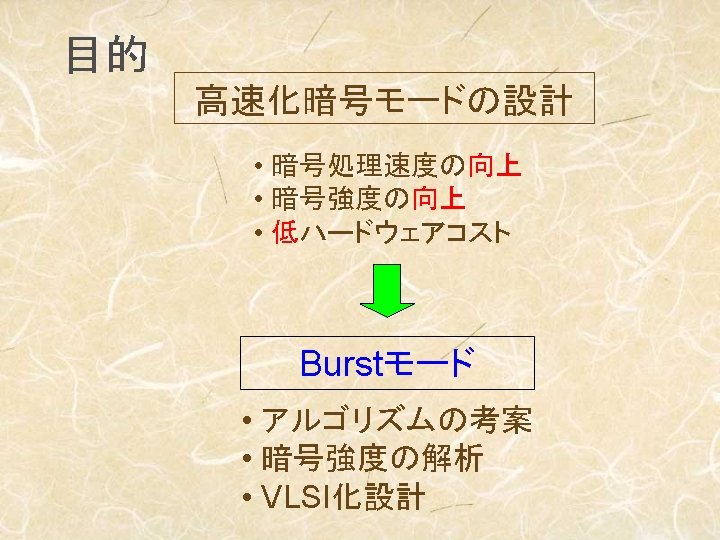

A Study on Performance Enhancement of SymmetricKey Cryptography

- Slides: 54

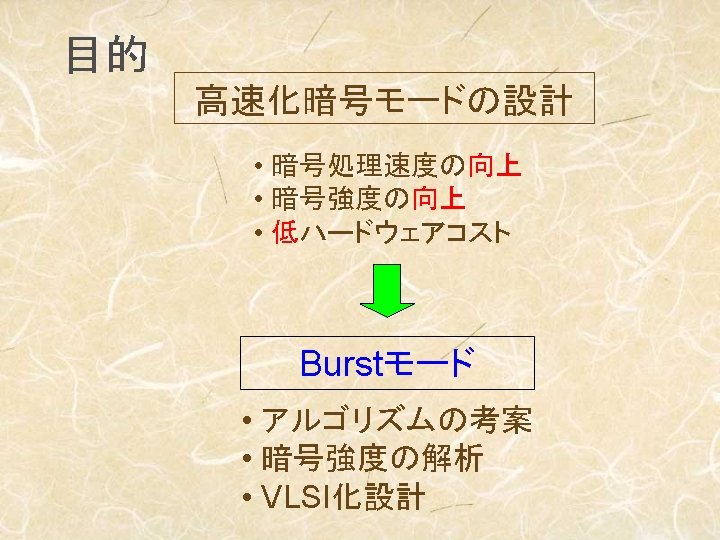

A Study on Performance Enhancement of Symmetric-Key Cryptography and its VLSI Implementation (共通鍵暗号の性能向上手法とVLSI化設計に関する研究) Zaldy ANDALES 大阪大学大学院 学研究科情報システム 学専攻 白川研究室

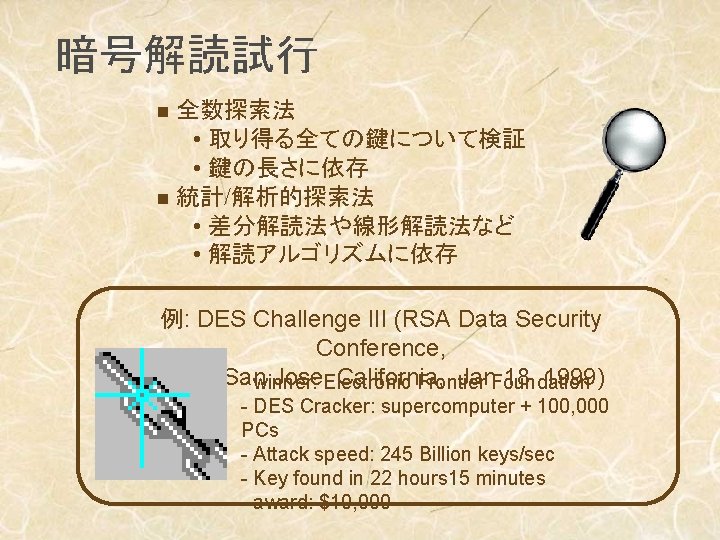

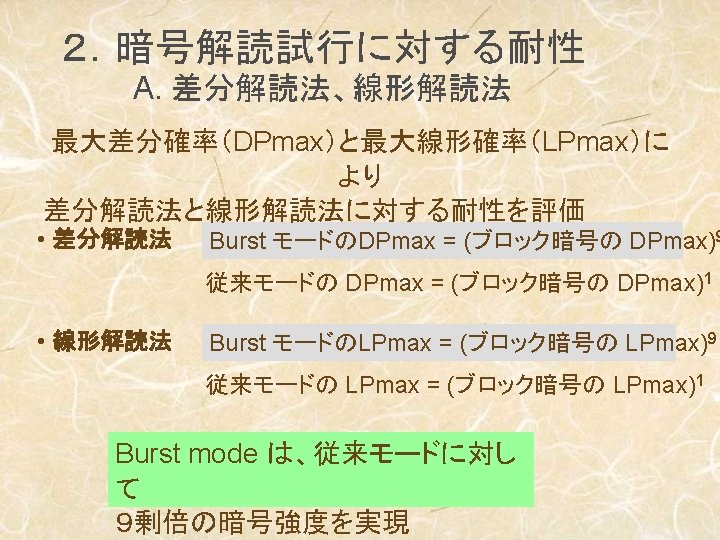

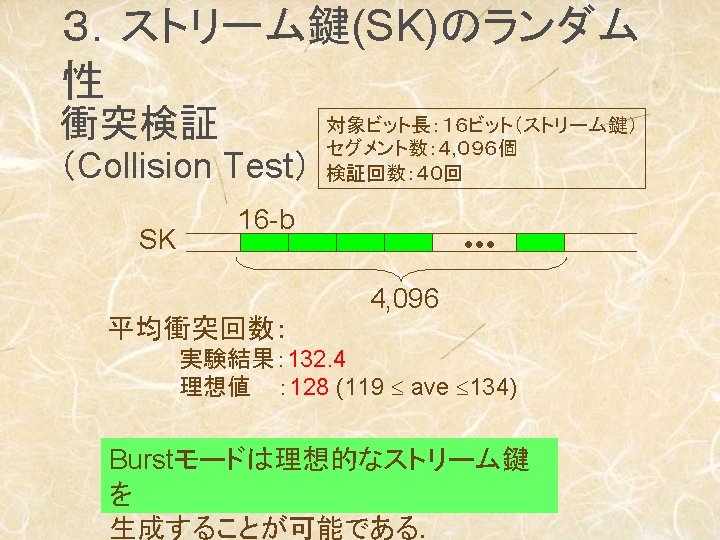

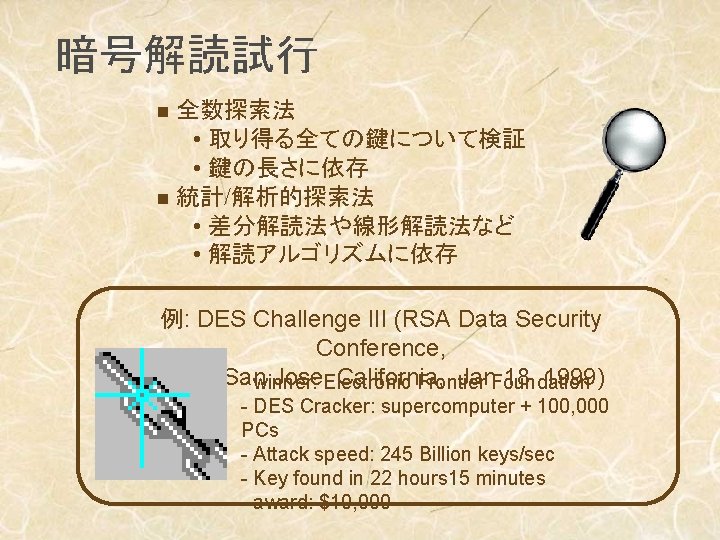

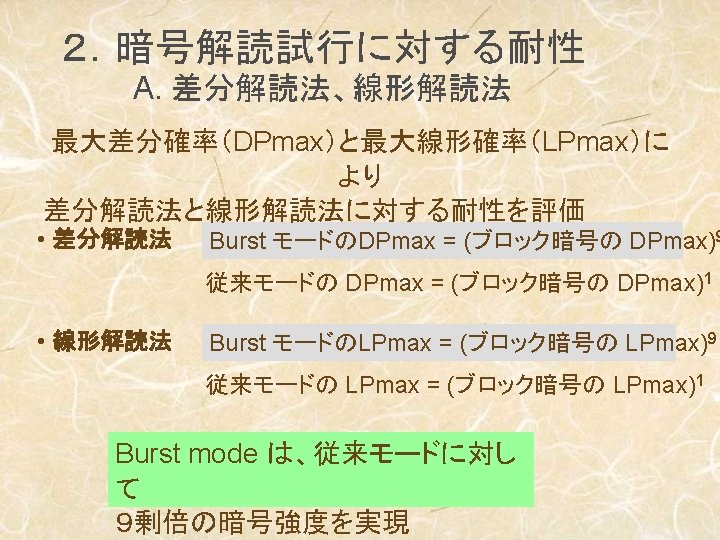

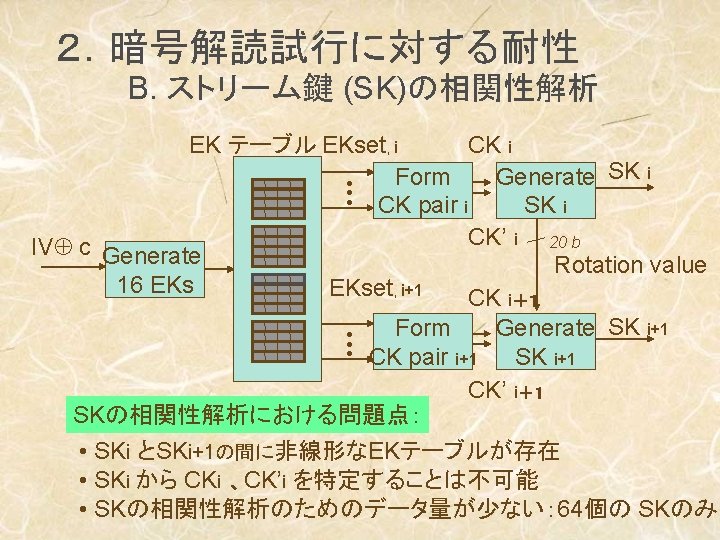

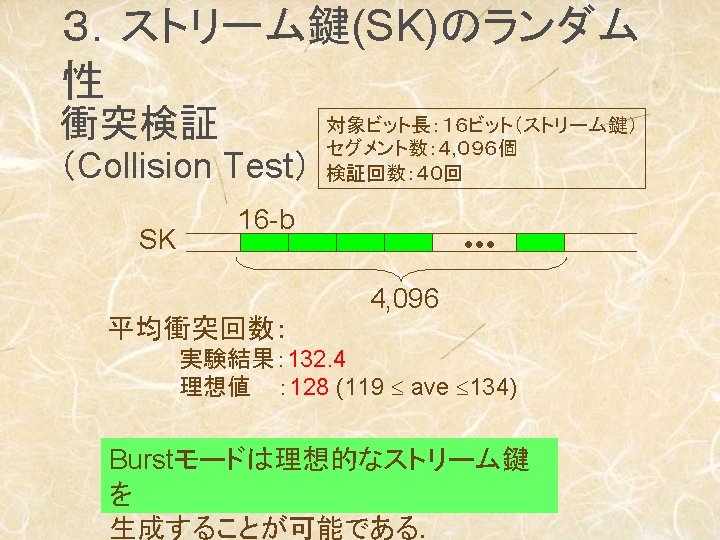

暗号解読試行 全数探索法 • 取り得る全ての鍵について検証 • 鍵の長さに依存 n 統計/解析的探索法 • 差分解読法や線形解読法など • 解読アルゴリズムに依存 n 例: DES Challenge III (RSA Data Security Conference, San Jose, Electronic California, Jan. Foundation 18, 1999) - winner: Frontier - DES Cracker: supercomputer + 100, 000 PCs - Attack speed: 245 Billion keys/sec - Key found in 22 hours 15 minutes - award: $10, 000

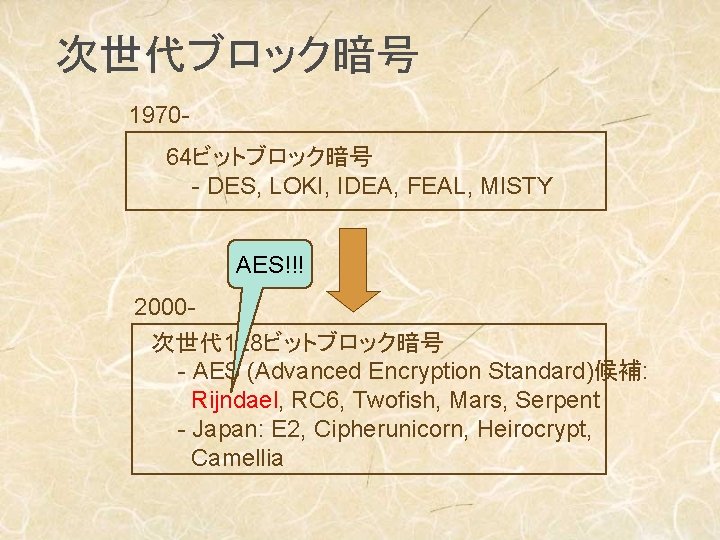

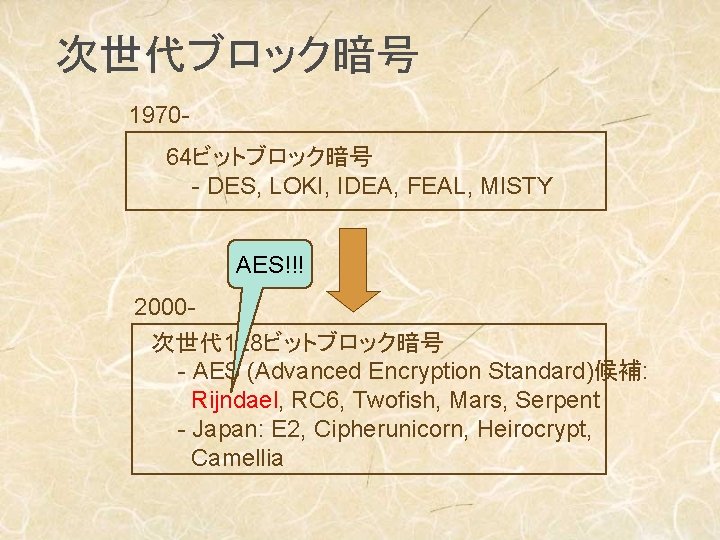

次世代ブロック暗号 197064ビットブロック暗号 - DES, LOKI, IDEA, FEAL, MISTY AES!!! 2000次世代 128ビットブロック暗号 - AES (Advanced Encryption Standard)候補: Rijndael, RC 6, Twofish, Mars, Serpent - Japan: E 2, Cipherunicorn, Heirocrypt, Camellia

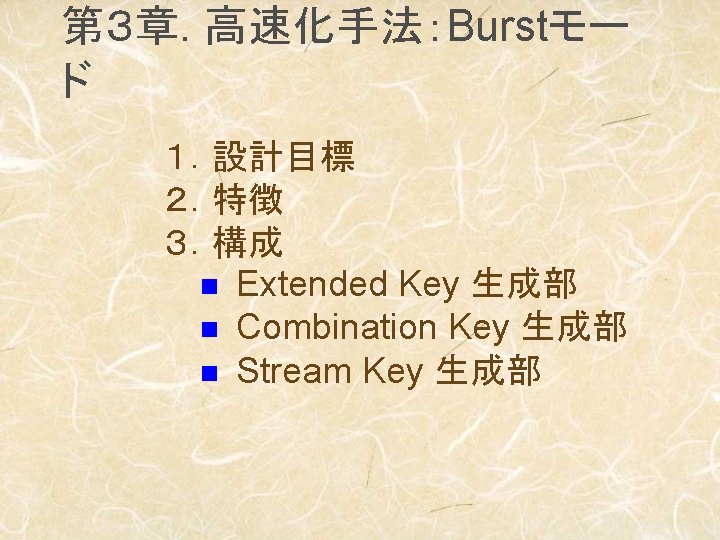

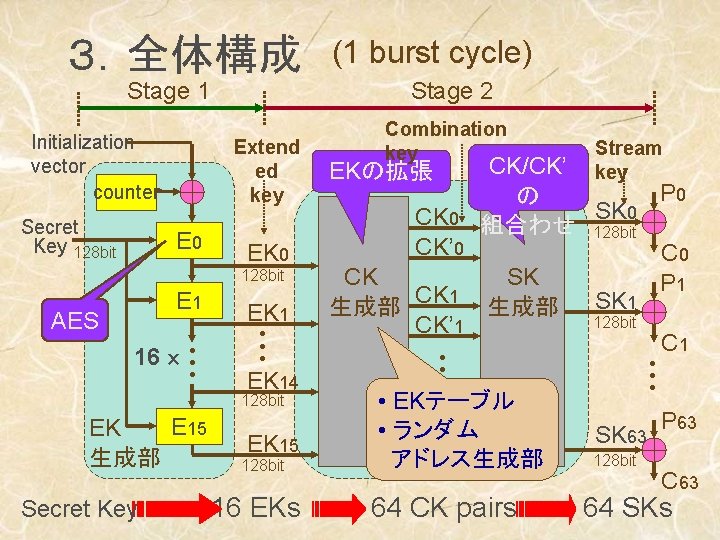

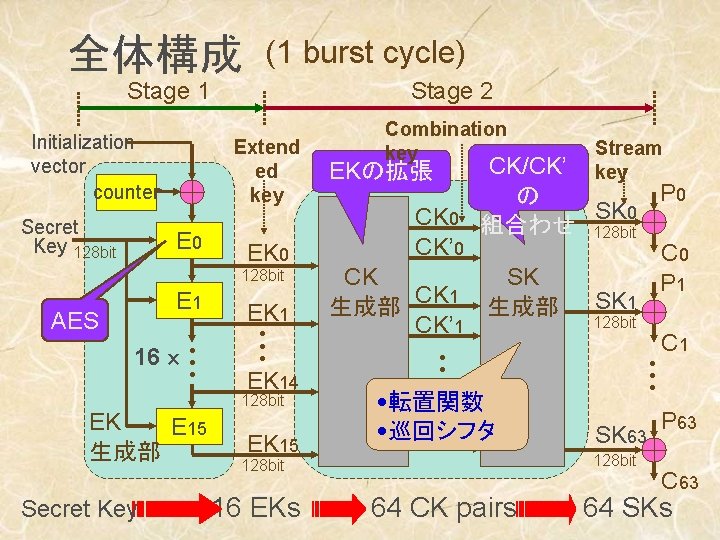

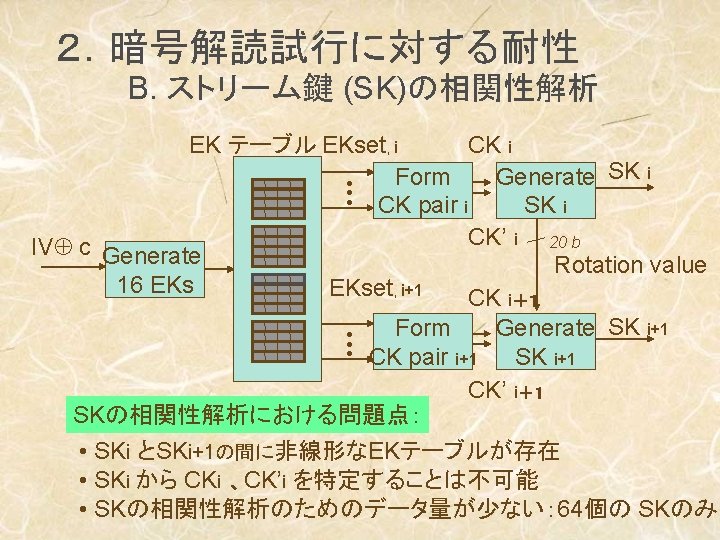

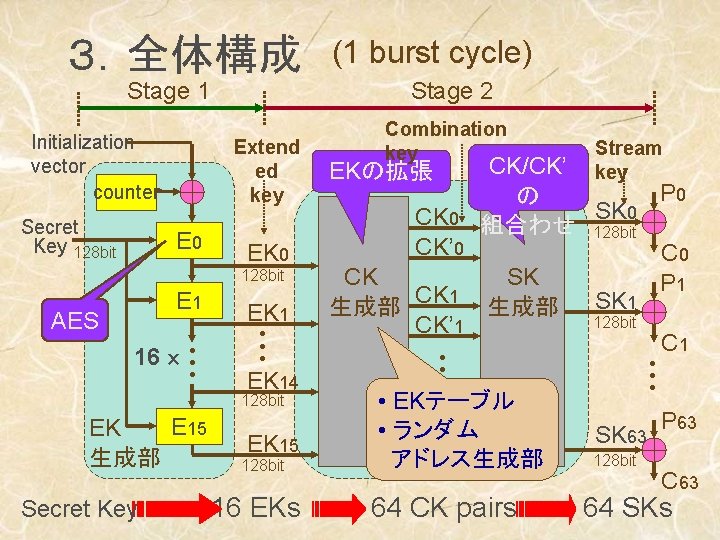

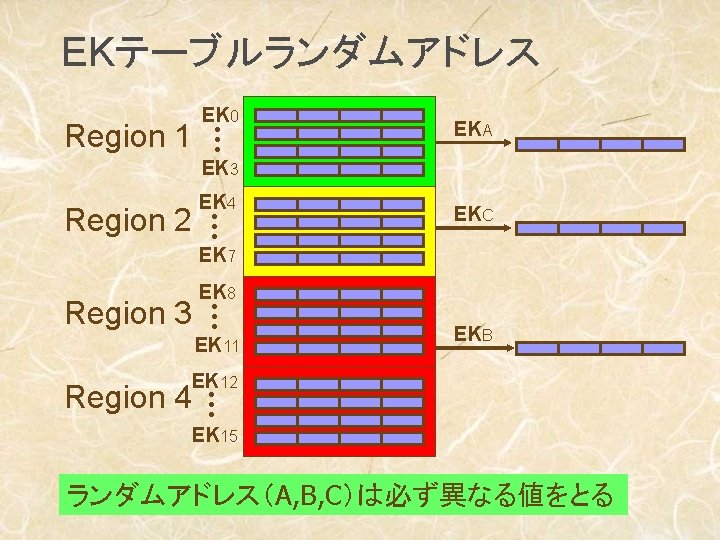

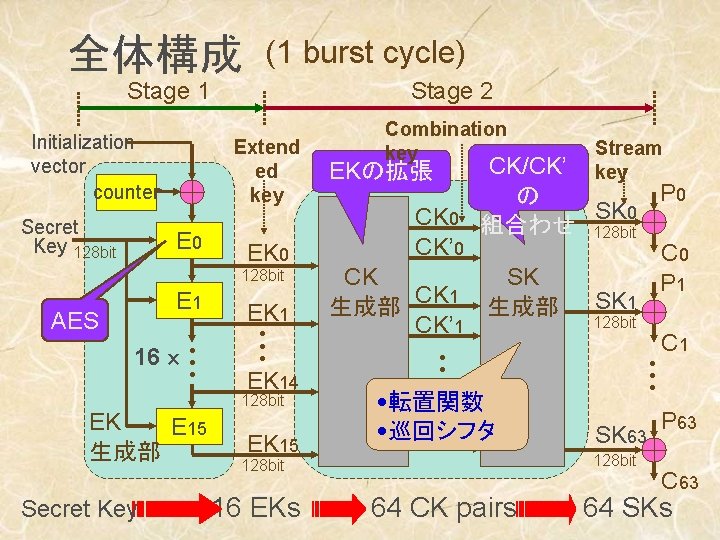

3.全体構成 Stage 1 Initialization vector counter Secret Key 128 bit Stage 2 Extend ed key E 0 EK 0 128 bit E 1 AES 16 • • • EK 1 • • • EK 14 128 bit E 15 EK 生成部 Secret Key (1 burst cycle) EK 15 128 bit 16 EKs Combination key EKの拡張 CK 0 CK’ 0 CK CK 1 生成部 CK’ 1 • • • Stream key CK/CK’ P 0 の SK 0 組合わせ 128 bit C 0 SK P 1 生成部 SK 1 128 bit C 1 • EKテーブル CK 63 • ランダム CK’ 63 アドレス生成部 64 CK pairs • • • SK 63 128 bit P 63 C 63 64 SKs

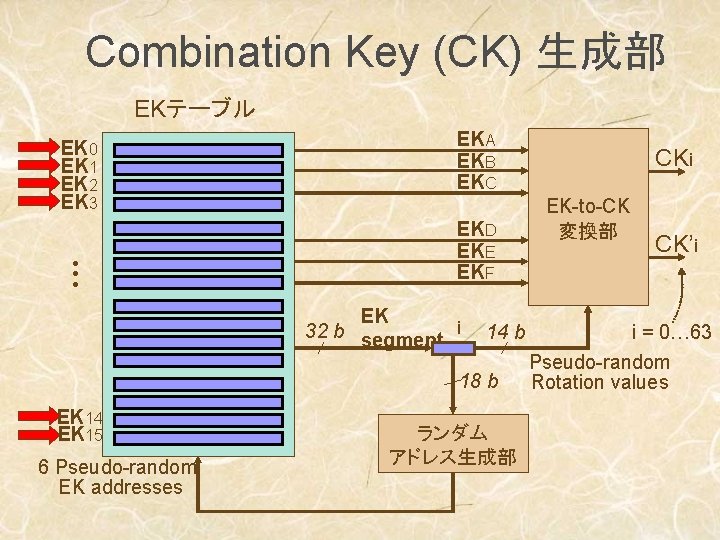

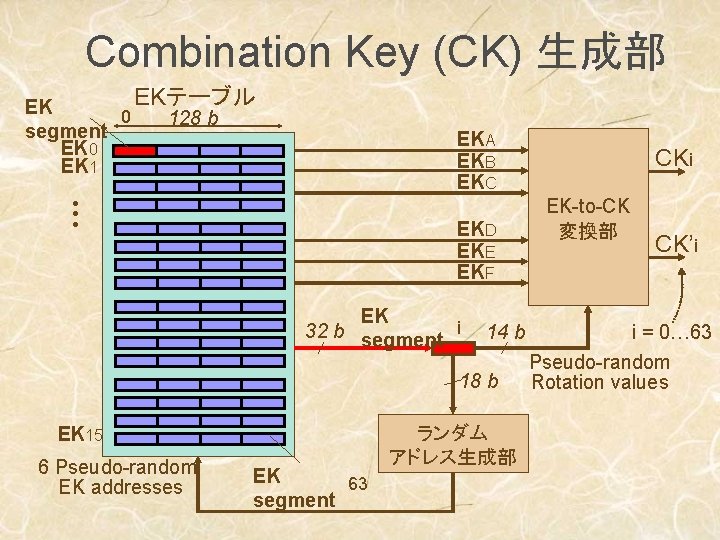

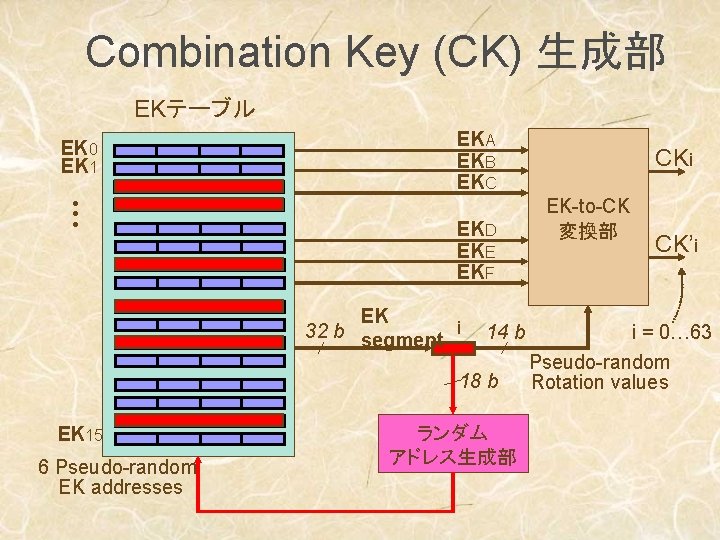

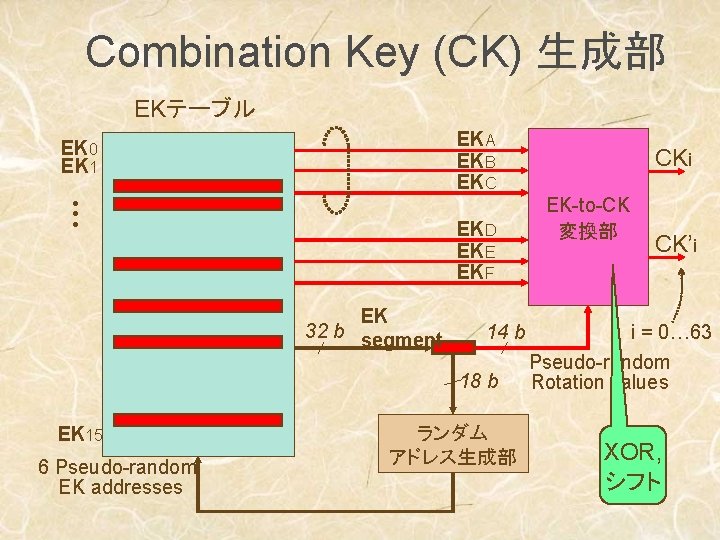

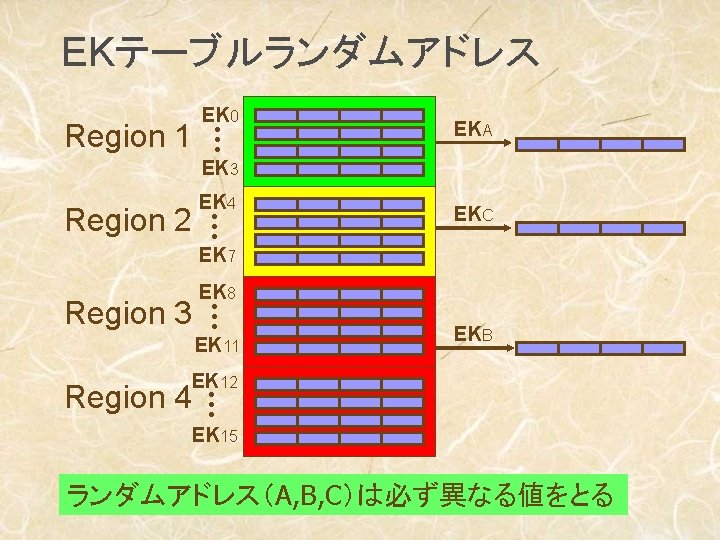

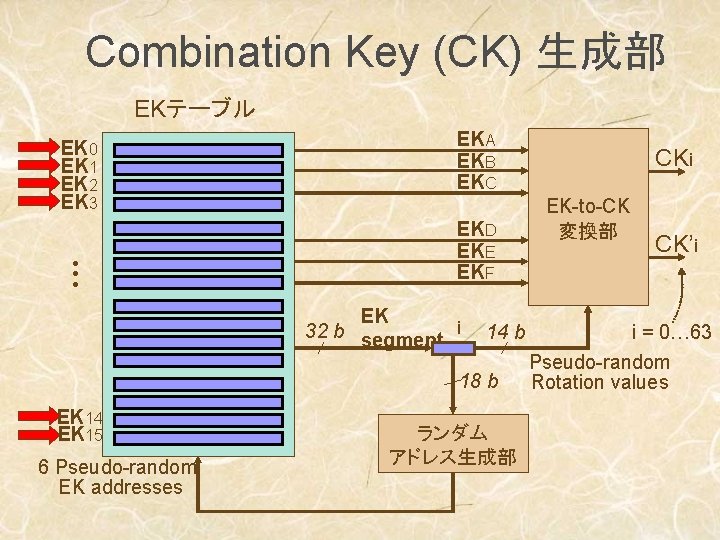

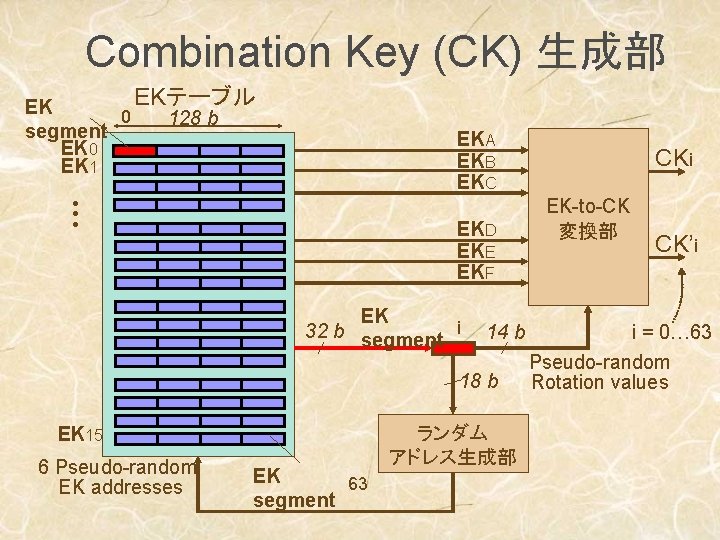

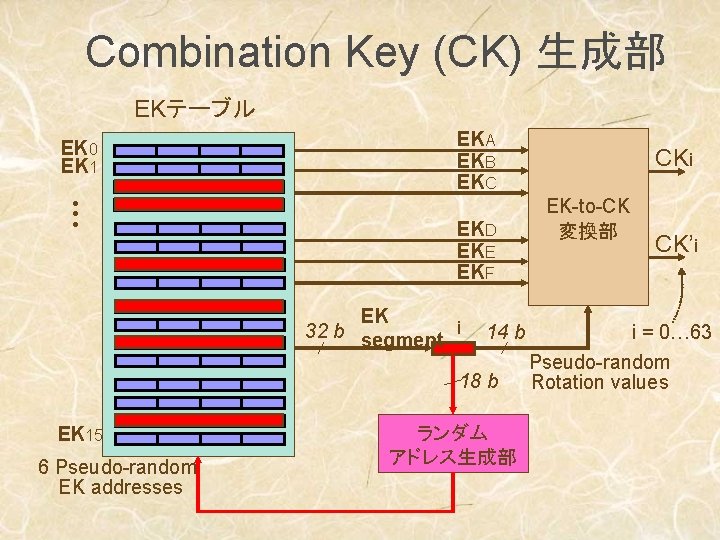

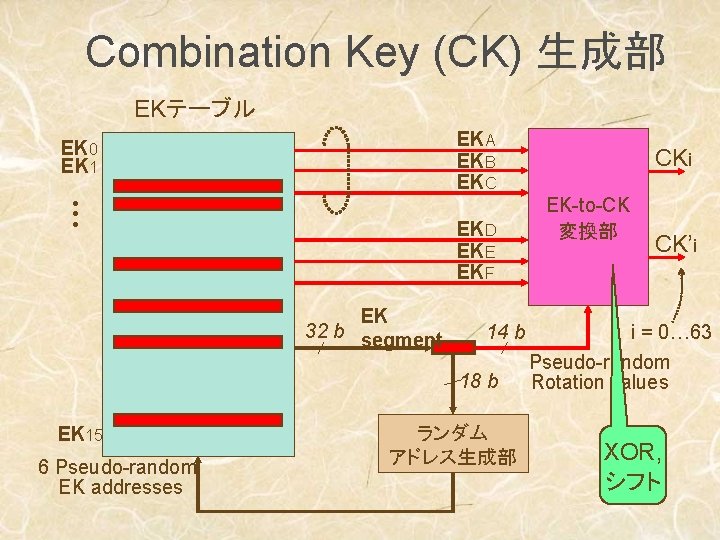

Combination Key (CK) 生成部 EKテーブル EK 0 EK 1 EK 2 EK 3 • • • EKA EKB EKC EKD EKE EKF EK 32 b segment i 14 b 18 b EK 14 EK 15 6 Pseudo-random EK addresses ランダム アドレス生成部 CKi EK-to-CK 変換部 CK’i i = 0… 63 Pseudo-random Rotation values

Combination Key (CK) 生成部 EKテーブル EK 0 128 b segment EK 0 EK 1 EKA EKB EKC • • • EKD EKE EKF EK 32 b segment i 14 b 18 b EK 15 6 Pseudo-random EK addresses EK 63 segment ランダム アドレス生成部 CKi EK-to-CK 変換部 CK’i i = 0… 63 Pseudo-random Rotation values

Combination Key (CK) 生成部 EKテーブル EK 0 EK 1 • • • EKA EKB EKC EKD EKE EKF EK 32 b segment i 14 b 18 b EK 15 6 Pseudo-random EK addresses ランダム アドレス生成部 CKi EK-to-CK 変換部 CK’i i = 0… 63 Pseudo-random Rotation values

Combination Key (CK) 生成部 EKテーブル EKA EKB EKC EK 0 EK 1 • • • EKD EKE EKF EK 32 b segment 14 b 18 b EK 15 6 Pseudo-random EK addresses ランダム アドレス生成部 CKi EK-to-CK 変換部 CK’i i = 0… 63 Pseudo-random Rotation values XOR, シフト

全体構成 (1 burst cycle) Stage 1 Initialization vector counter Secret Key 128 bit Stage 2 Extend ed key E 0 EK 0 128 bit E 1 AES 16 • • • EK E 15 生成部 Secret Key EK 1 • • • EK 14 128 bit EK 15 Combination key EKの拡張 CK 0 CK’ 0 CK CK 1 生成部 CK’ 1 • • • CK/CK’ P 0 の SK 0 組合わせ 128 bit C 0 SK P 1 生成部 SK 1 128 bit C 1 • 転置関数 CK 63 • 巡回シフタ CK’ 63 • • • SK 63 128 bit 16 EKs Stream key 64 CK pairs P 63 C 63 64 SKs

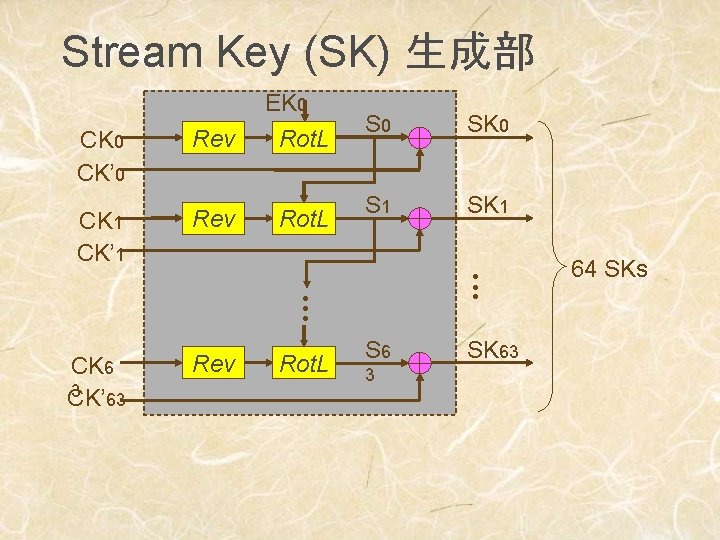

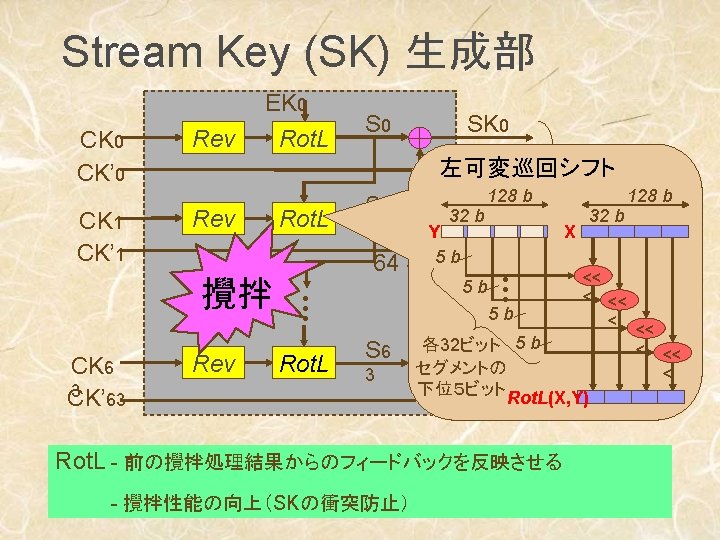

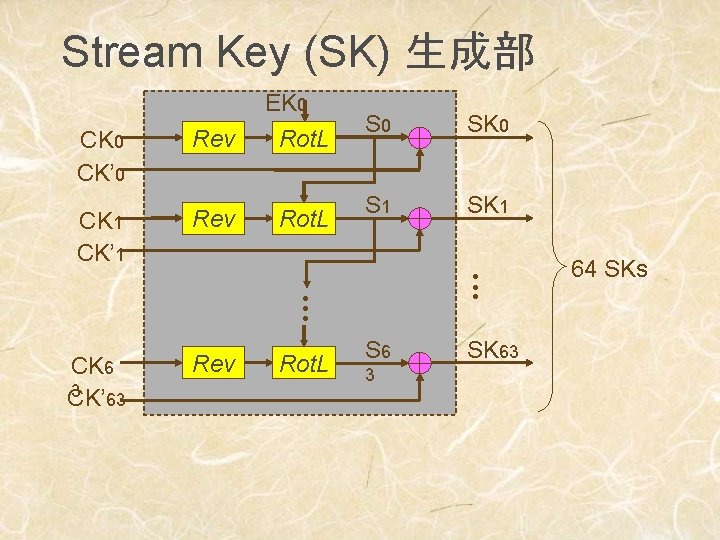

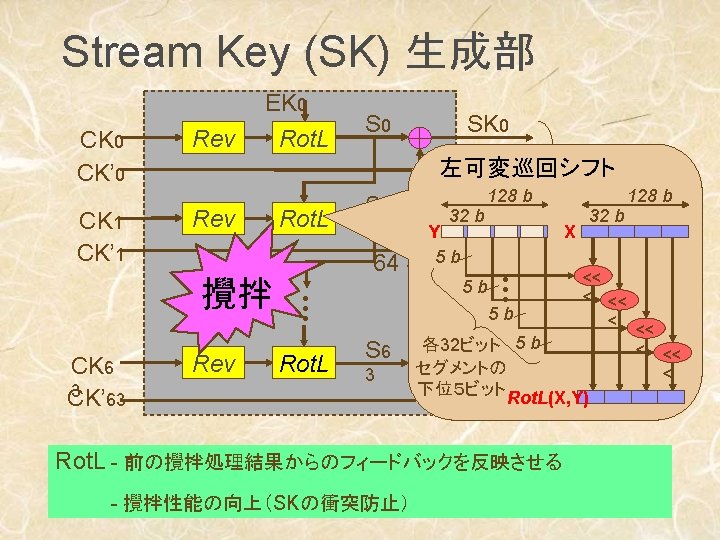

Stream Key (SK) 生成部 CK 0 CK’ 0 Rev EK 0 Rot. L CK 1 CK’ 1 Rev Rot. L S 0 SK 0 S 1 SK 1 • • • CK 6 3 CK’ 63 Rev Rot. L S 6 3 SK 63 64 SKs

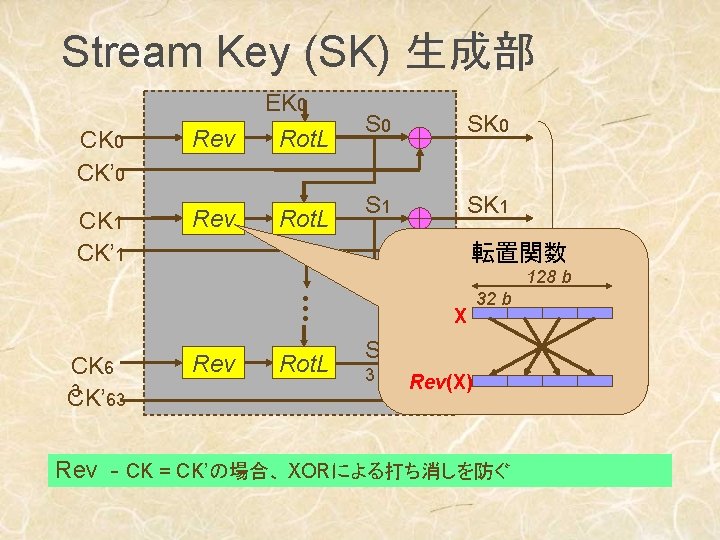

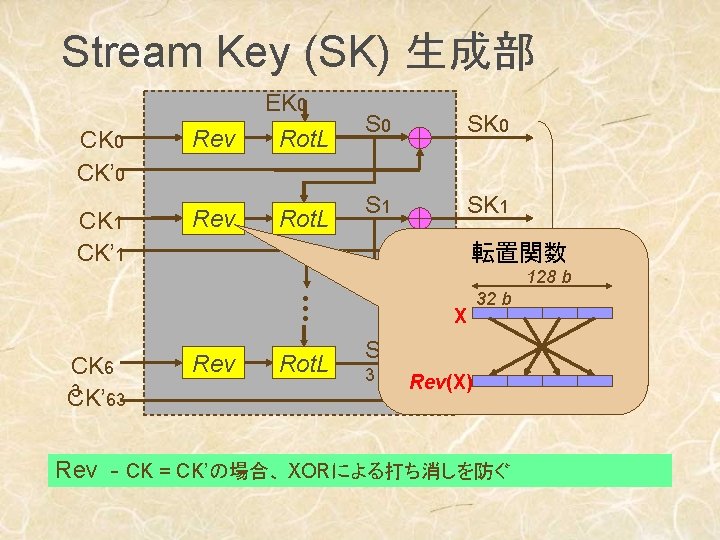

Stream Key (SK) 生成部 CK 0 CK’ 0 Rev EK 0 Rot. L CK 1 CK’ 1 Rev Rot. L S 0 SK 0 S 1 SK 1 転置関数 • • • CK 6 3 CK’ 63 Rev Rot. L X S 6 3 128 b 64 SKs • • • 32 b SK 63 Rev(X) Rev - CK = CK’の場合、 XORによる打ち消しを防ぐ

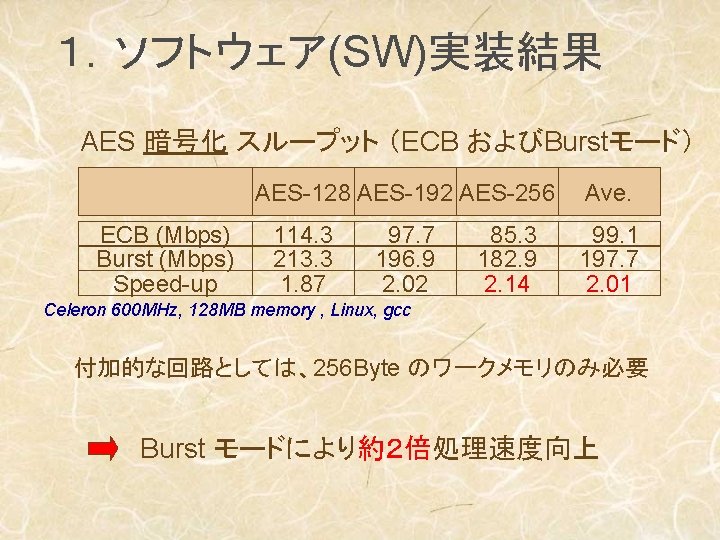

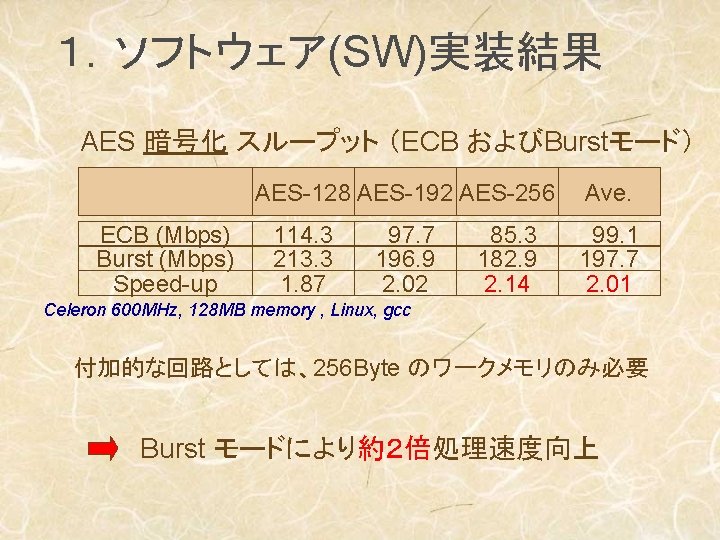

1.ソフトウェア(SW)実装結果 AES 暗号化 スループット (ECB およびBurstモード) AES-128 AES-192 AES-256 ECB (Mbps) Burst (Mbps) Speed-up 114. 3 213. 3 1. 87 97. 7 196. 9 2. 02 85. 3 182. 9 2. 14 Ave. 99. 1 197. 7 2. 01 Celeron 600 MHz, 128 MB memory , Linux, gcc 付加的な回路としては、256 Byte のワークメモリのみ必要 Burst モードにより約2倍処理速度向上

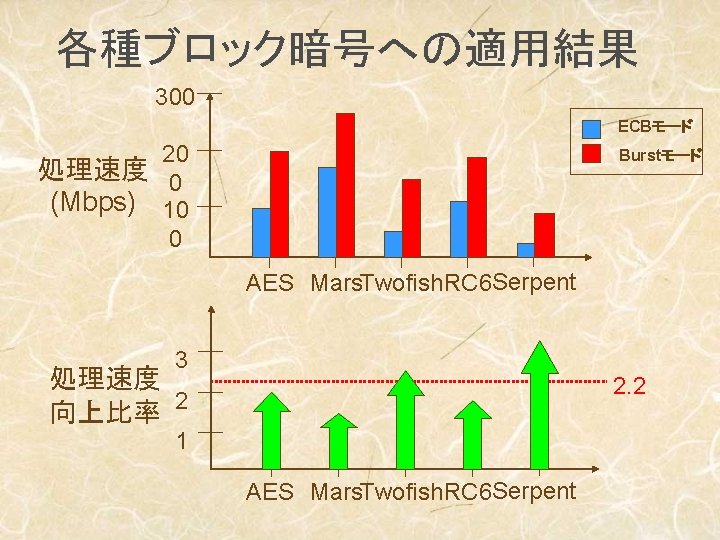

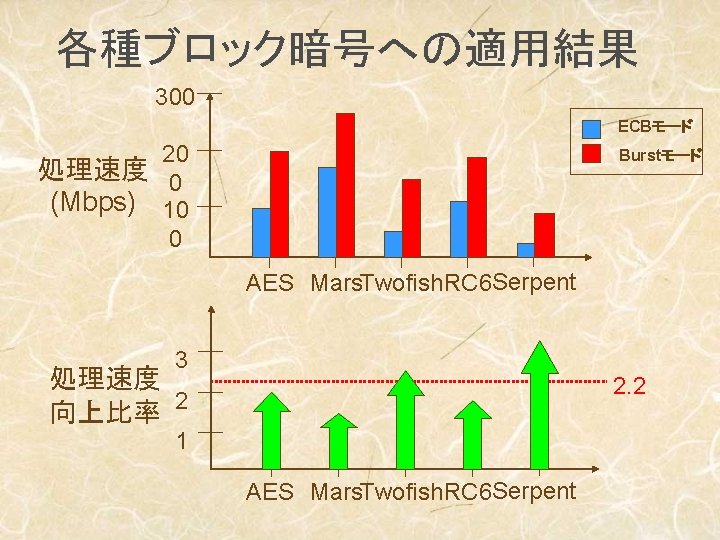

各種ブロック暗号への適用結果 300 ECBモード 20 処理速度 0 (Mbps) 10 0 Burstモード AES Mars. Twofish. RC 6 Serpent 3 処理速度 向上比率 2 2. 2 1 AES Mars. Twofish. RC 6 Serpent

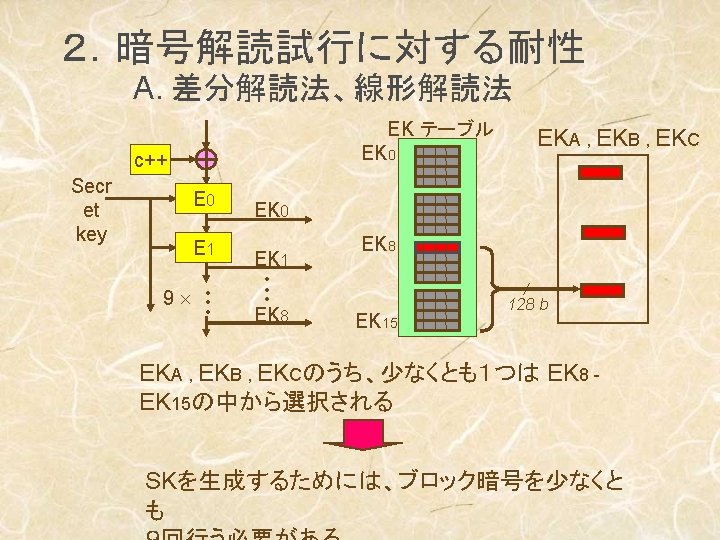

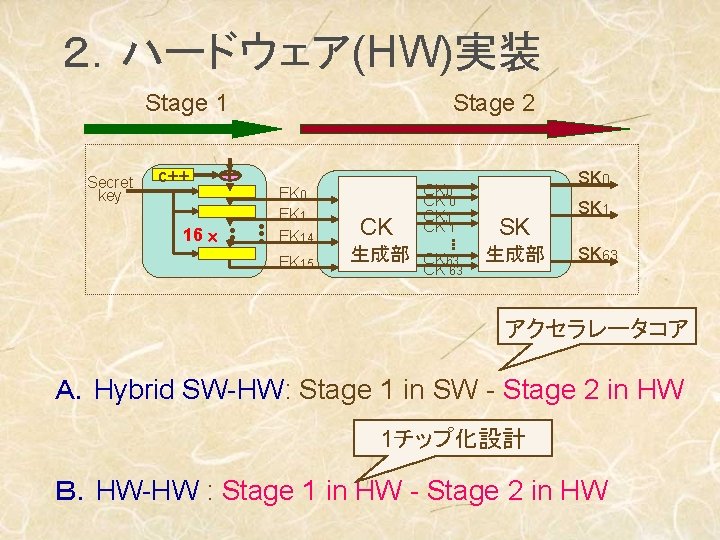

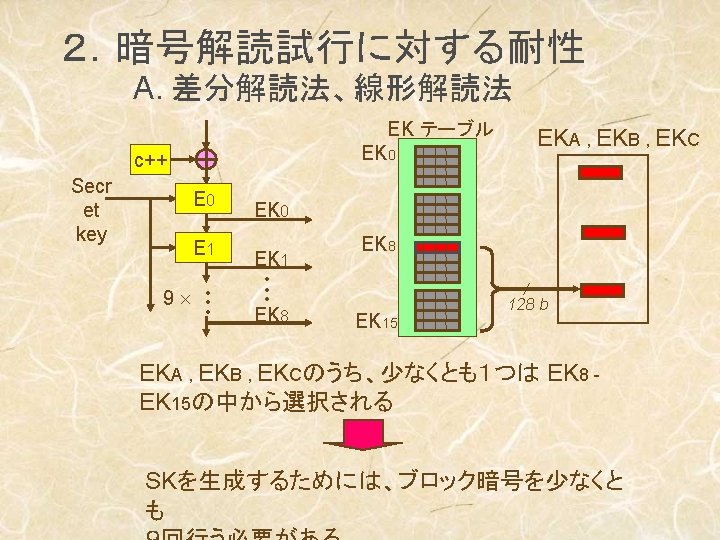

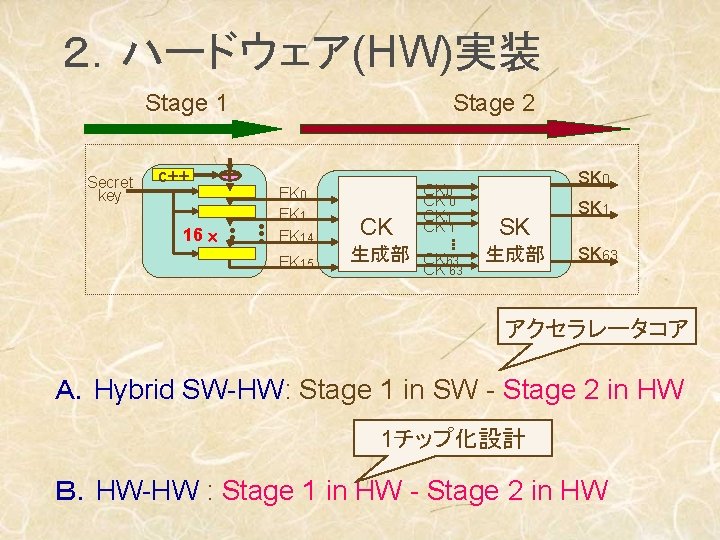

2.ハードウェア(HW)実装 Stage 1 Secret key Stage 2 c++ 16 • • • • EK 0 EK 14 EK 15 CK 生成部 CK 0 CK’ 0 CK 1 CK’ 1 • • • CK 63 CK’ 63 SK 0 SK 生成部 SK 1 SK 63 アクセラレータコア A.Hybrid SW-HW: Stage 1 in SW - Stage 2 in HW 1チップ化設計 B.HW-HW : Stage 1 in HW - Stage 2 in HW

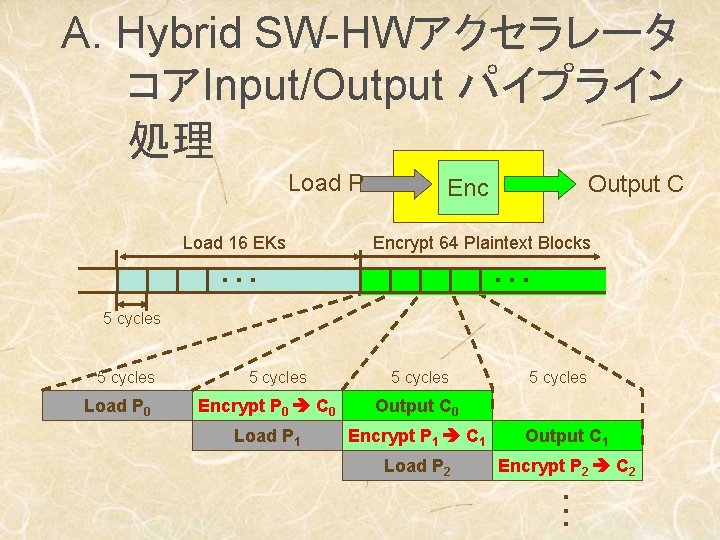

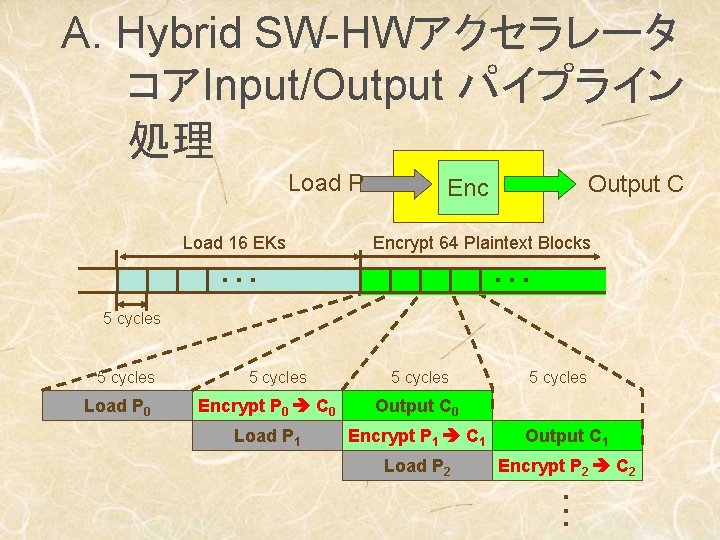

A. Hybrid SW-HWアクセラレータ コアInput/Output パイプライン 処理 Load P Load 16 EKs Output C Encrypt 64 Plaintext Blocks ・・・ 5 cycles Load P 0 5 cycles Encrypt P 0 C 0 Output C 0 Load P 1 Encrypt P 1 C 1 Output C 1 Load P 2 Encrypt P 2 C 2 ・・ ・

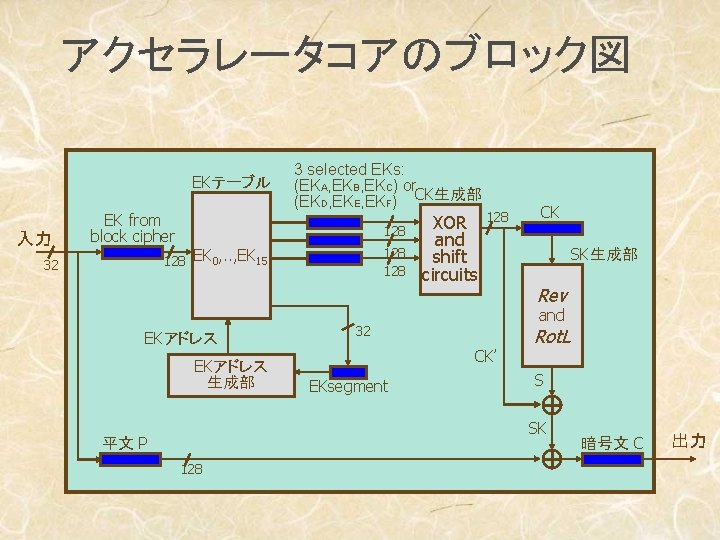

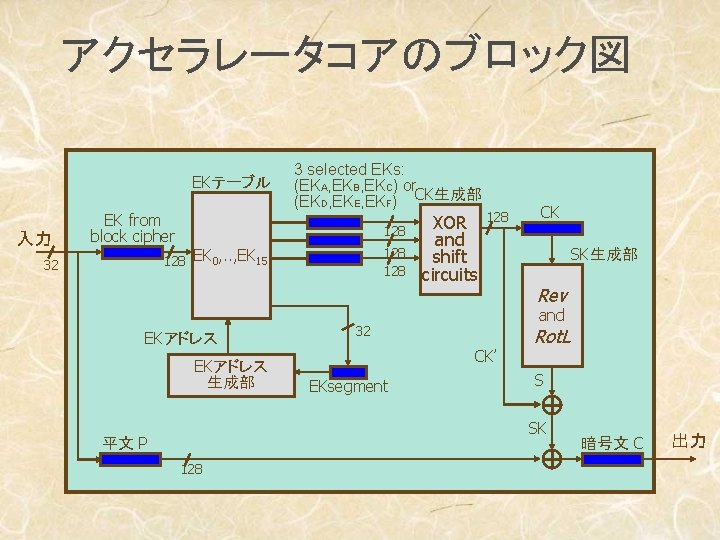

アクセラレータコアのブロック図 EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 128 EK 0, . . , EK 15 32 EKアドレス 生成部 XOR and shift circuits 128 SK生成部 Rev and 32 CK’ EKsegment CK Rot. L S SK 平文 P 128 暗号文 C 出力

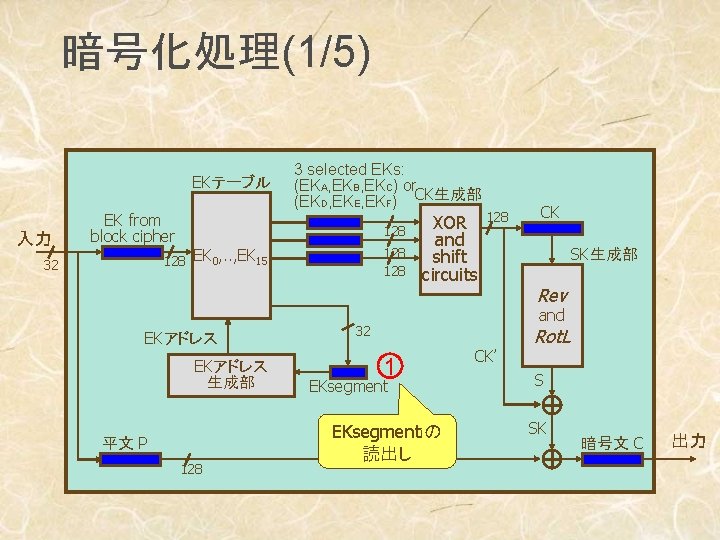

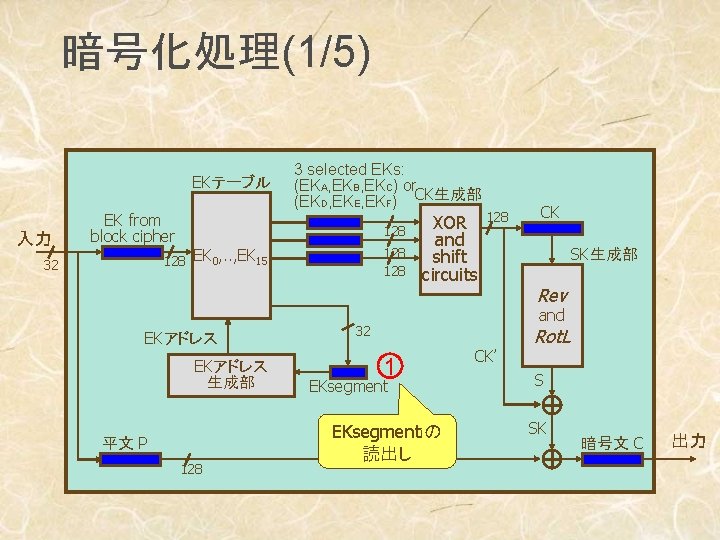

暗号化処理(1/5) EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 128 EK 0, . . , EK 15 32 EKアドレス 生成部 平文 P 128 XOR and shift circuits 128 CK SK生成部 Rev and 32 1 EKsegmentiの 読出し CK’ Rot. L S SK 暗号文 C 出力

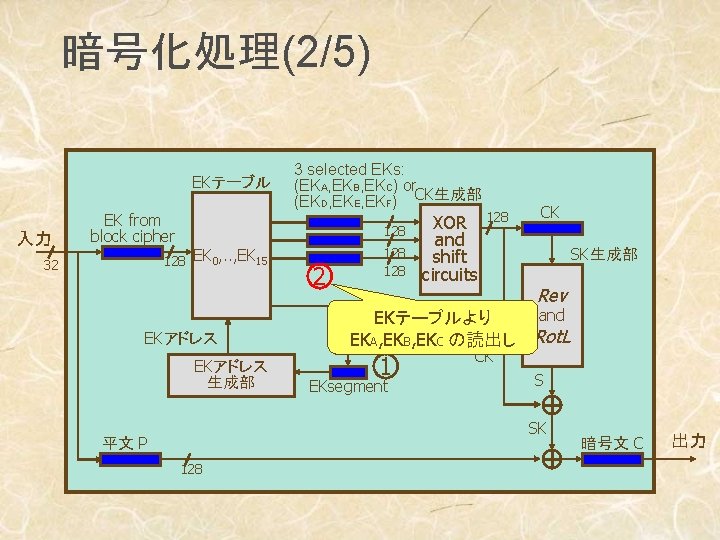

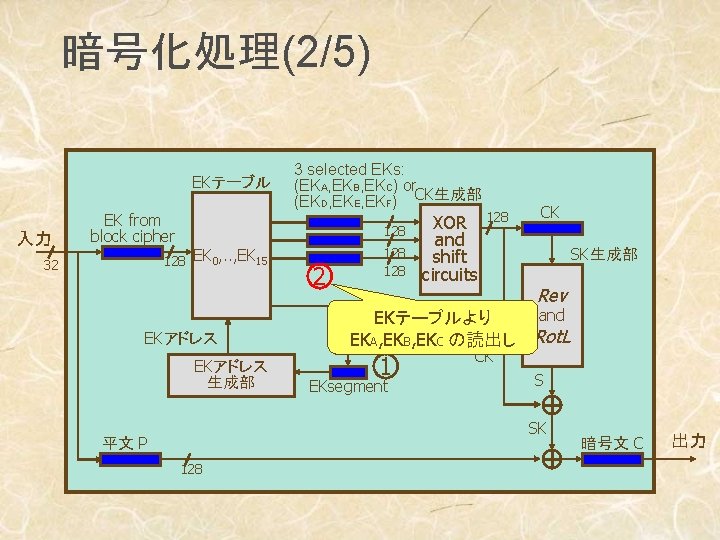

暗号化処理(2/5) EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 EK 0, . . , EK 15 32 EKアドレス 生成部 128 2 XOR and shift circuits 128 EKテーブルより EKA, EKB, EKC の読出し 32 1 EKsegment CK’ CK SK生成部 Rev and Rot. L S SK 平文 P 128 暗号文 C 出力

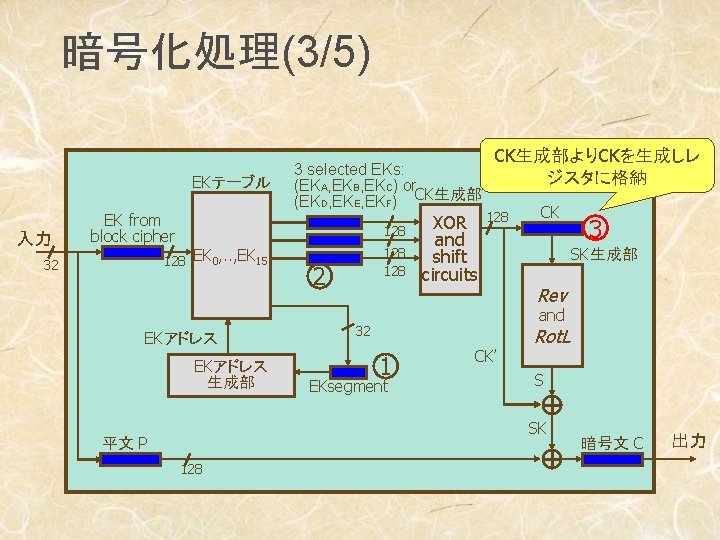

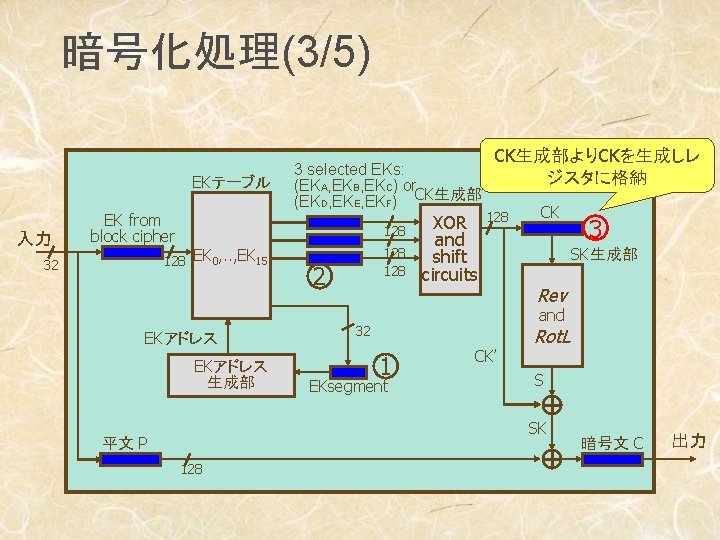

暗号化処理(3/5) EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 EK 0, . . , EK 15 32 EKアドレス 生成部 128 2 XOR and shift circuits CK生成部よりCKを生成しレ ジスタに格納 128 CK SK生成部 Rev and 32 1 EKsegment CK’ Rot. L S SK 平文 P 128 3 暗号文 C 出力

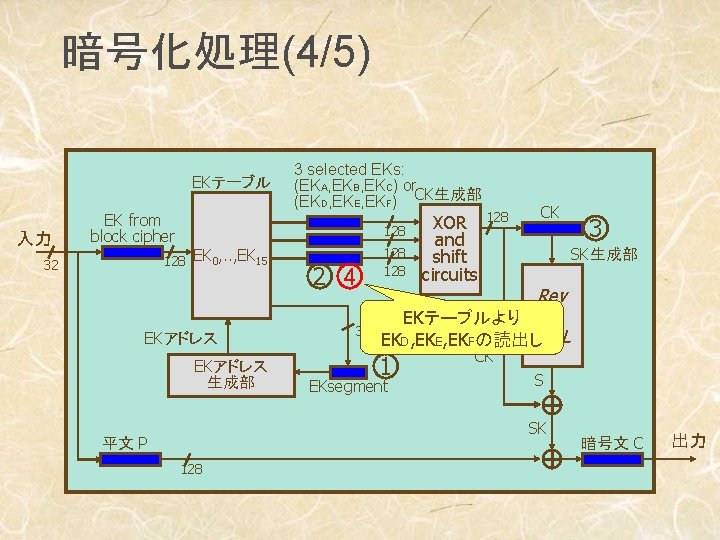

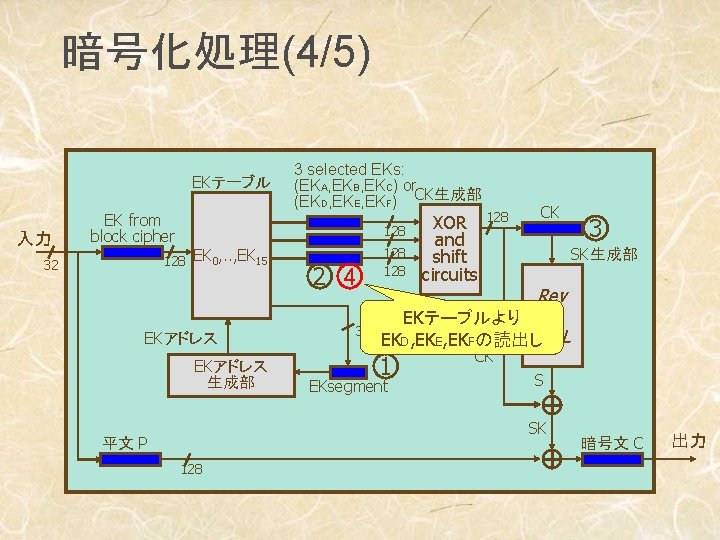

暗号化処理(4/5) EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 EK 0, . . , EK 15 32 EKアドレス 生成部 2 4 32 128 XOR and shift circuits 128 CK SK生成部 Rev EKテーブルより and EKD, EKE, EKFの読出しRot. L 1 EKsegment CK’ S SK 平文 P 128 3 暗号文 C 出力

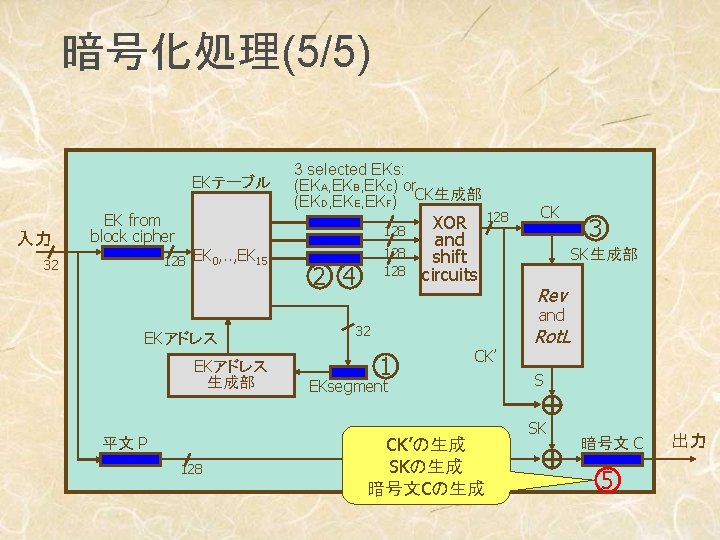

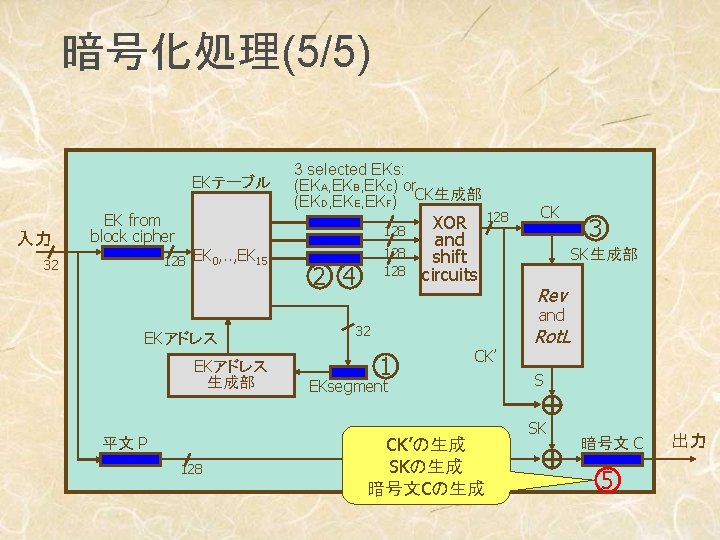

暗号化処理(5/5) EKテーブル 入力 3 selected EKs: (EKA, EKB, EKC) or (EKD, EKE, EKF) CK生成部 EK from block cipher 128 EK 0, . . , EK 15 32 EKアドレス 生成部 平文 P 128 128 2 4 XOR and shift circuits 128 CK 3 SK生成部 Rev and 32 1 CK’ EKsegment CK’の生成 SKの生成 暗号文Cの生成 Rot. L S SK 暗号文 C 5 出力

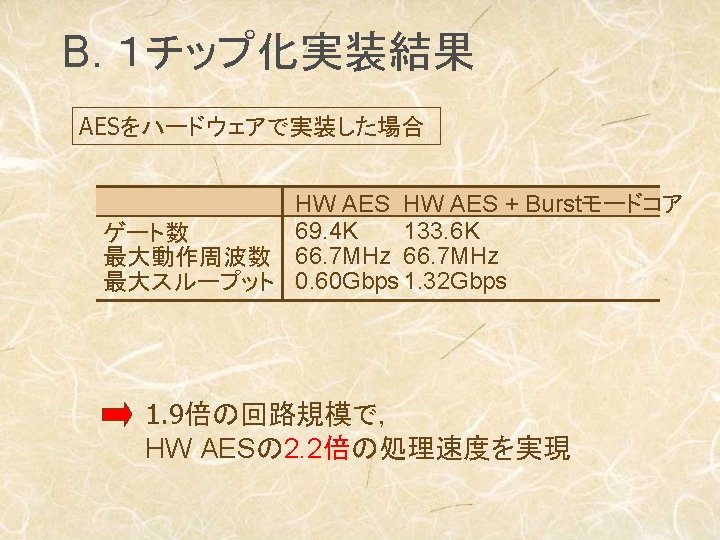

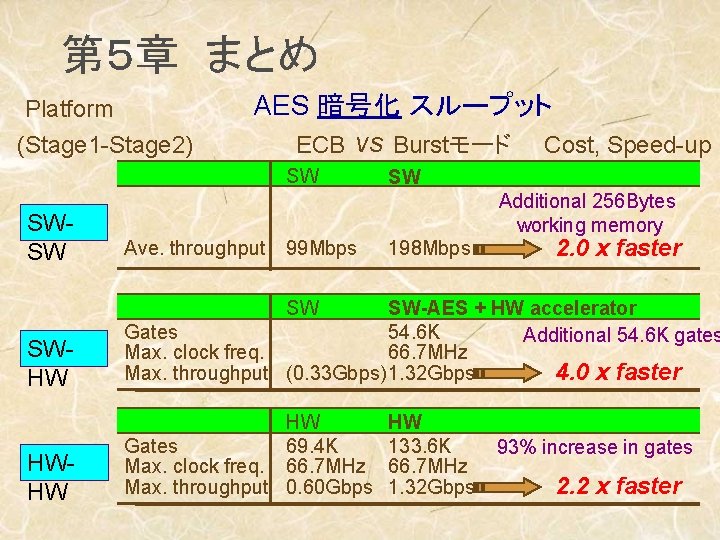

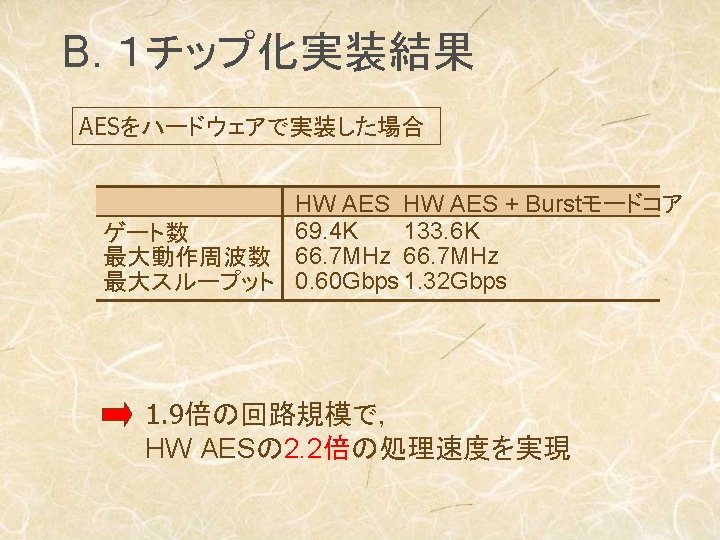

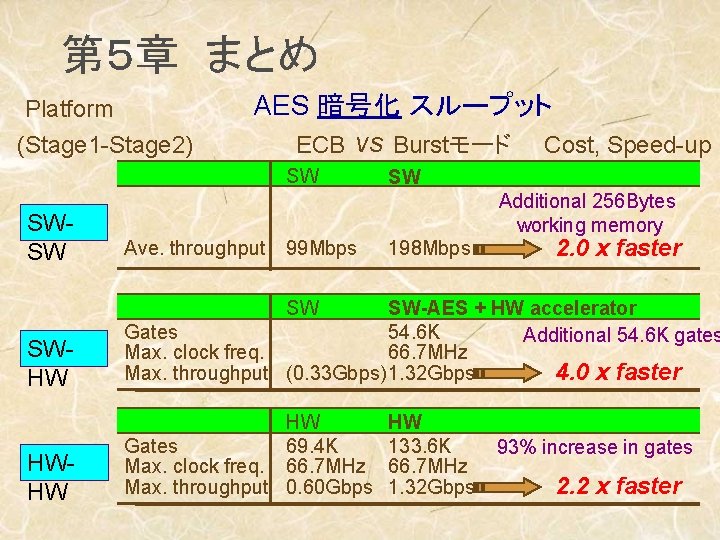

第5章 まとめ Platform (Stage 1 -Stage 2) AES 暗号化 スループット ECB vs Burstモード Cost, Speed-up SW SW Additional 256 Bytes working memory SWSW Ave. throughput SWHW SW-AES + HW accelerator Gates 54. 6 K Additional 54. 6 K gates Max. clock freq. 66. 7 MHz 4. 0 x faster Max. throughput (0. 33 Gbps) 1. 32 Gbps HWHW HW Gates 69. 4 K Max. clock freq. 66. 7 MHz Max. throughput 0. 60 Gbps 99 Mbps 198 Mbps 2. 0 x faster SW HW 133. 6 K 66. 7 MHz 1. 32 Gbps 93% increase in gates 2. 2 x faster