A Simplified CostEffective MPLS Labeling Architecture for Access

A Simplified, Cost-Effective MPLS Labeling Architecture for Access Networks Harald Widiger 1, Stephan Kubisch 1, Daniel Duchow 1, Thomas Bahls 2, Dirk Timmermann 1 1 University of Rostock, Germany 2 Siemens Communications, Greifswald, Germany University of Rostock. Unversity of Rostock, Germany

Outline o o o Access Network Architecture Multi Protocol Label Switching The MPLS-User Network Interface Implementation and Simulation Results Conclusion 3/5/2021 University of Rostock 2

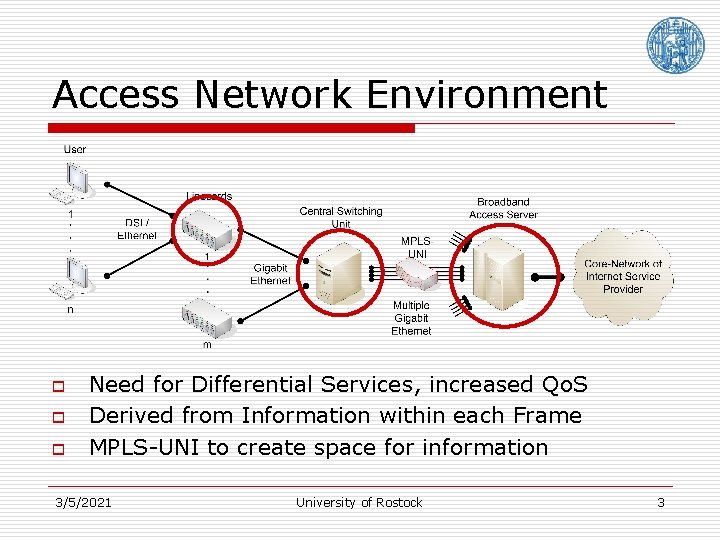

Access Network Environment o o o Need for Differential Services, increased Qo. S Derived from Information within each Frame MPLS-UNI to create space for information 3/5/2021 University of Rostock 3

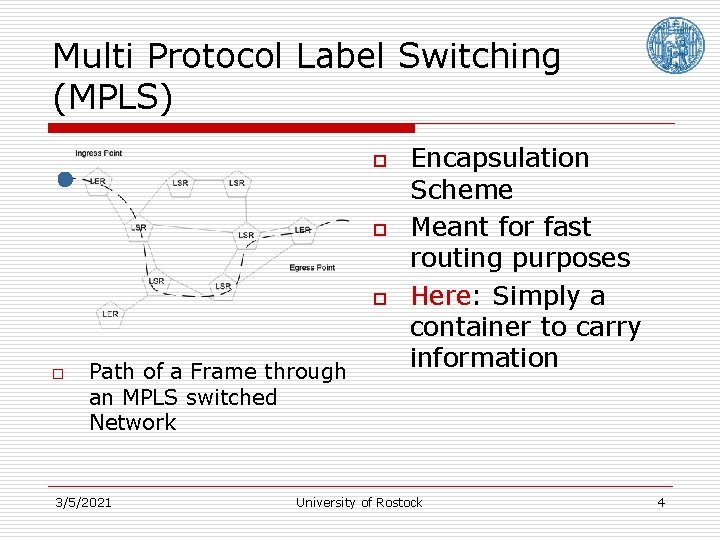

Multi Protocol Label Switching (MPLS) o o Path of a Frame through an MPLS switched Network 3/5/2021 Encapsulation Scheme Meant for fast routing purposes Here: Simply a container to carry information University of Rostock 4

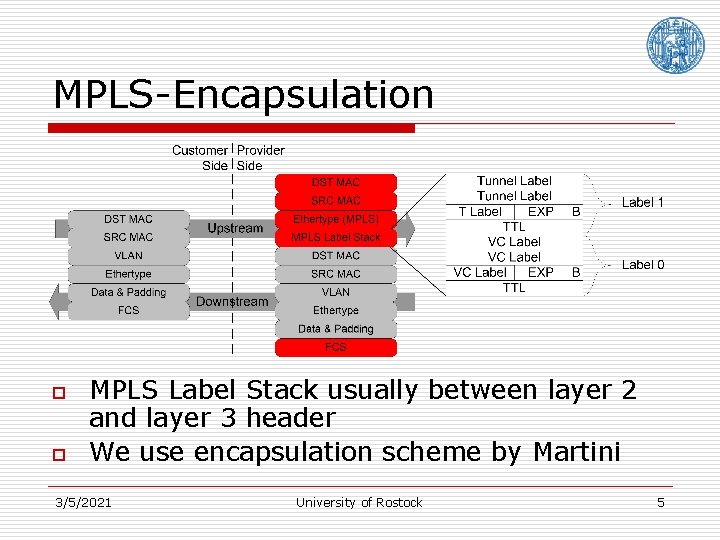

MPLS-Encapsulation o o MPLS Label Stack usually between layer 2 and layer 3 header We use encapsulation scheme by Martini 3/5/2021 University of Rostock 5

MPLS-User Network Interface (MPLS-UNI) o o MPLS Label Stack container to carry information No complete LER implementation with an LDP running is necessary n o Possibility to implement the whole system in Hardware Primary Functionality: n n 3/5/2021 Upstream direction insert an MPLS Label Stack Downstream direction remove MPLS Label Stacks University of Rostock 6

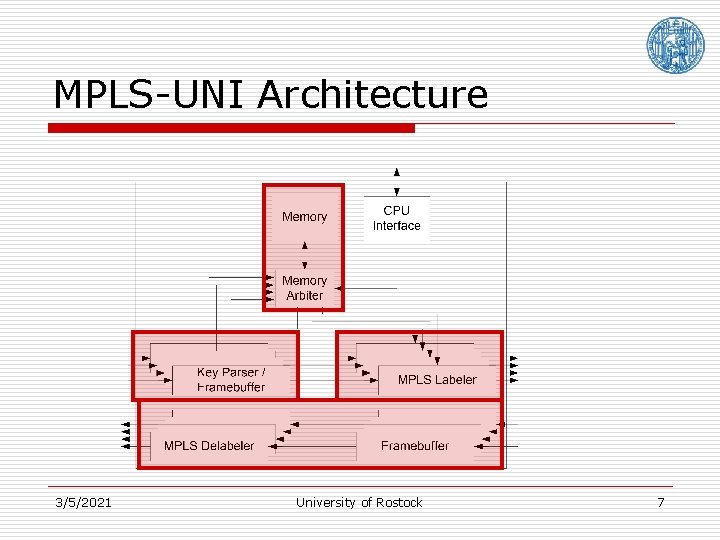

MPLS-UNI Architecture 3/5/2021 University of Rostock 7

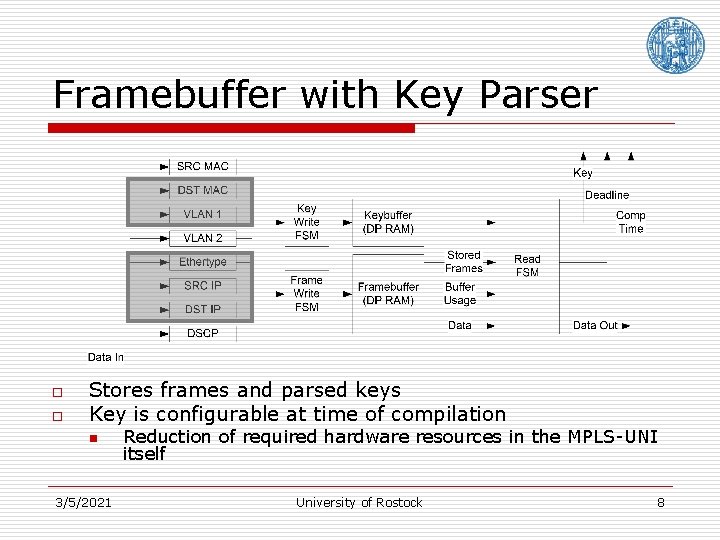

Framebuffer with Key Parser o o Stores frames and parsed keys Key is configurable at time of compilation n 3/5/2021 Reduction of required hardware resources in the MPLS-UNI itself University of Rostock 8

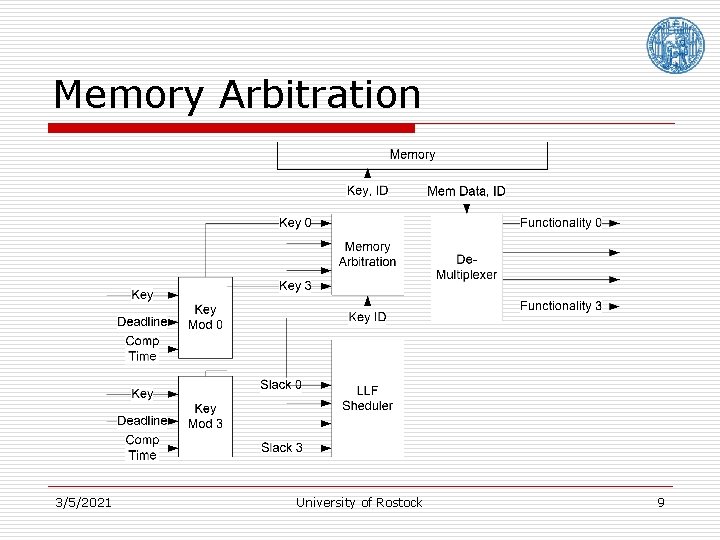

Memory Arbitration 3/5/2021 University of Rostock 9

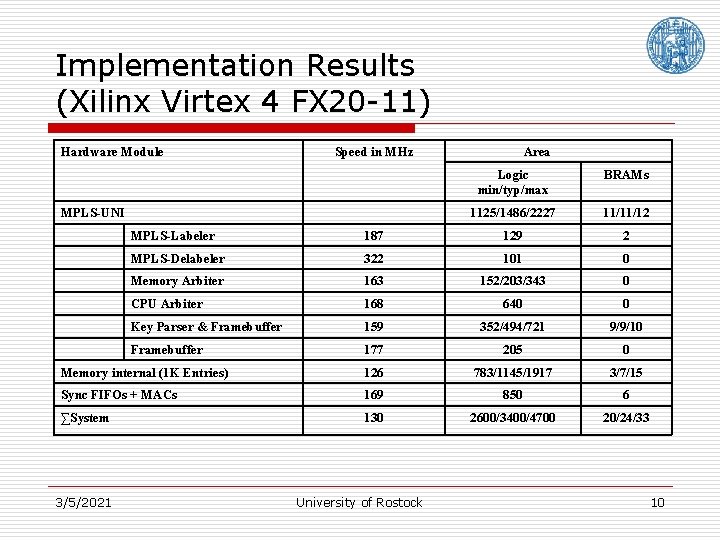

Implementation Results (Xilinx Virtex 4 FX 20 -11) Hardware Module Speed in MHz MPLS-UNI Area Logic min/typ/max BRAMs 1125/1486/2227 11/11/12 MPLS-Labeler 187 129 2 MPLS-Delabeler 322 101 0 Memory Arbiter 163 152/203/343 0 CPU Arbiter 168 640 0 Key Parser & Framebuffer 159 352/494/721 9/9/10 Framebuffer 177 205 0 Memory internal (1 K Entries) 126 783/1145/1917 3/7/15 Sync FIFOs + MACs 169 850 6 ∑System 130 2600/3400/4700 20/24/33 3/5/2021 University of Rostock 10

Performance o 4 Gbps @ „natural Traffic“ n n o o 3/5/2021 University of Rostock 30 10 11 49 % % 60 Byte 590 Byte 1514 Byte random No packet loss Average delay of 120 Cycles 860 ns @125 MHz 11

Conclusion o o Powerful and cost-effective solution to expand MPLS networks into the Access Network area @125 MHz, 4 Gbps can be handled Size of the system can be minimized considering the actual tasks Functional spectrum can be broadened, due to reconfigurable HW 3/5/2021 University of Rostock 12

- Slides: 12