A simple register allocation optimization scheme Register allocation

- Slides: 12

A simple register allocation optimization scheme

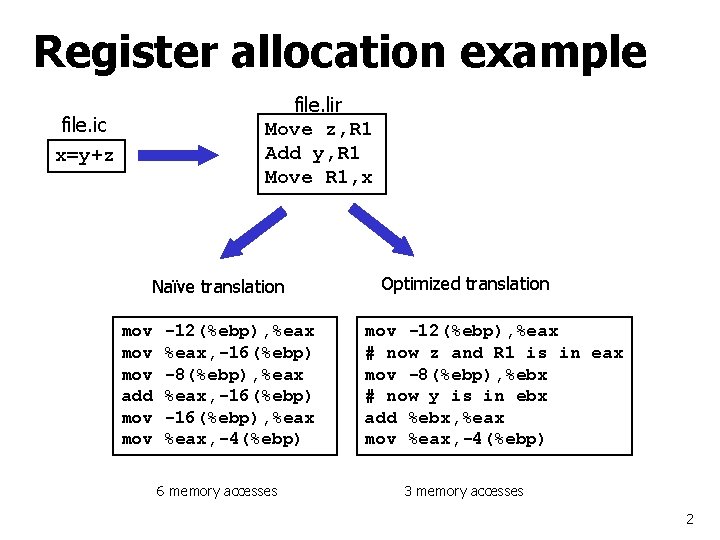

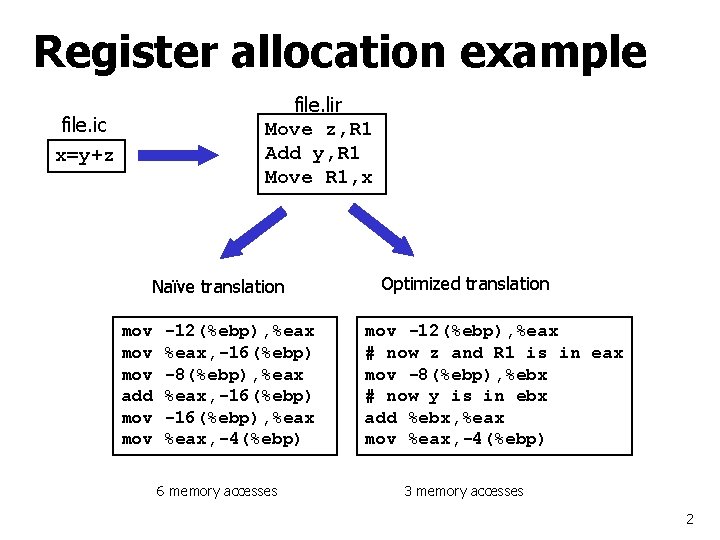

Register allocation example file. lir Move z, R 1 Add y, R 1 Move R 1, x file. ic x=y+z Naïve translation mov mov add mov -12(%ebp), %eax, -16(%ebp) -8(%ebp), %eax, -16(%ebp), %eax, -4(%ebp) 6 memory accesses Optimized translation mov -12(%ebp), %eax # now z and R 1 is in eax mov -8(%ebp), %ebx # now y is in ebx add %ebx, %eax mov %eax, -4(%ebp) 3 memory accesses 2

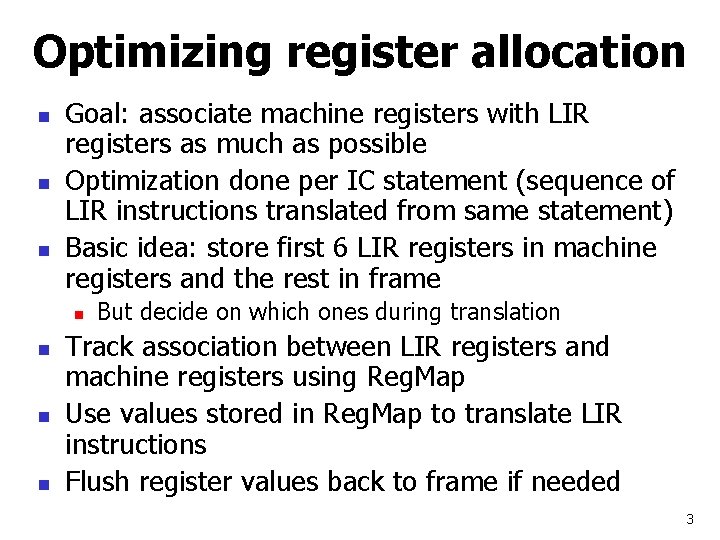

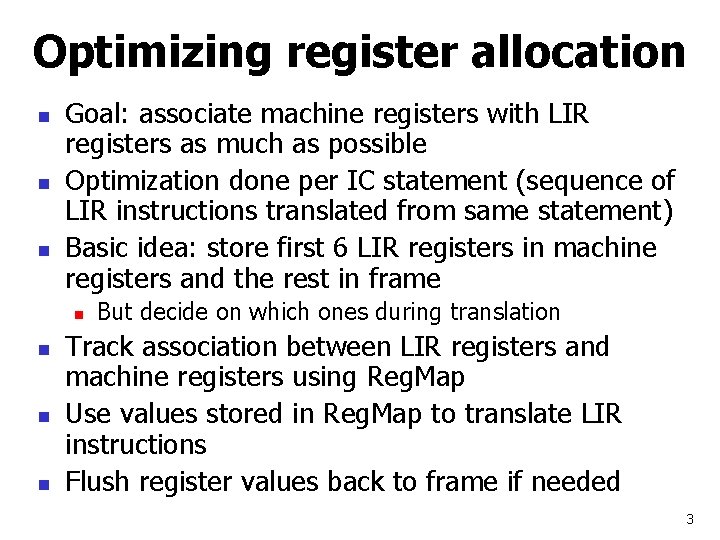

Optimizing register allocation n Goal: associate machine registers with LIR registers as much as possible Optimization done per IC statement (sequence of LIR instructions translated from same statement) Basic idea: store first 6 LIR registers in machine registers and the rest in frame n n But decide on which ones during translation Track association between LIR registers and machine registers using Reg. Map Use values stored in Reg. Map to translate LIR instructions Flush register values back to frame if needed 3

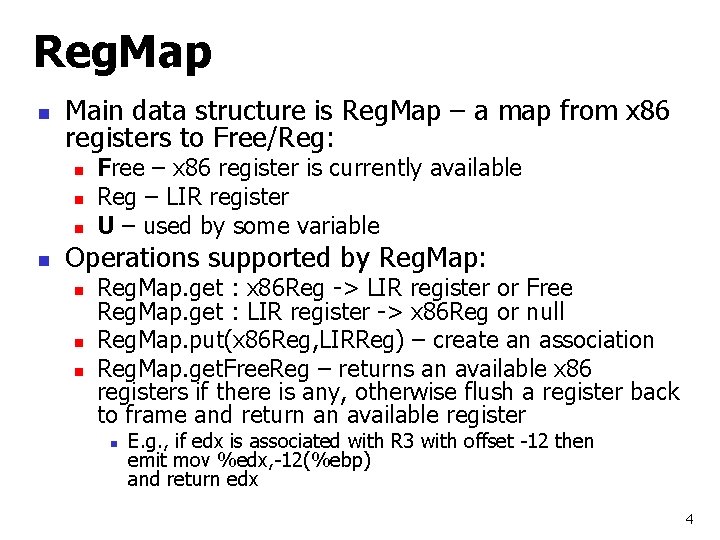

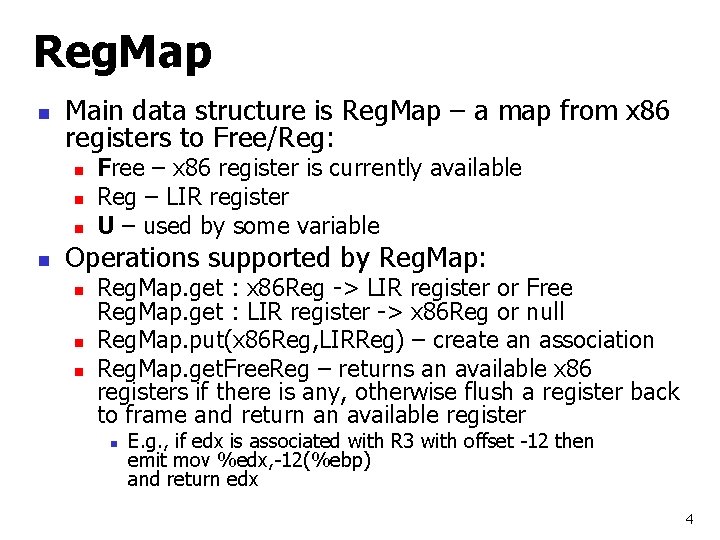

Reg. Map n Main data structure is Reg. Map – a map from x 86 registers to Free/Reg: n n Free – x 86 register is currently available Reg – LIR register U – used by some variable Operations supported by Reg. Map: n n n Reg. Map. get : x 86 Reg -> LIR register or Free Reg. Map. get : LIR register -> x 86 Reg or null Reg. Map. put(x 86 Reg, LIRReg) – create an association Reg. Map. get. Free. Reg – returns an available x 86 registers if there is any, otherwise flush a register back to frame and return an available register n E. g. , if edx is associated with R 3 with offset -12 then emit mov %edx, -12(%ebp) and return edx 4

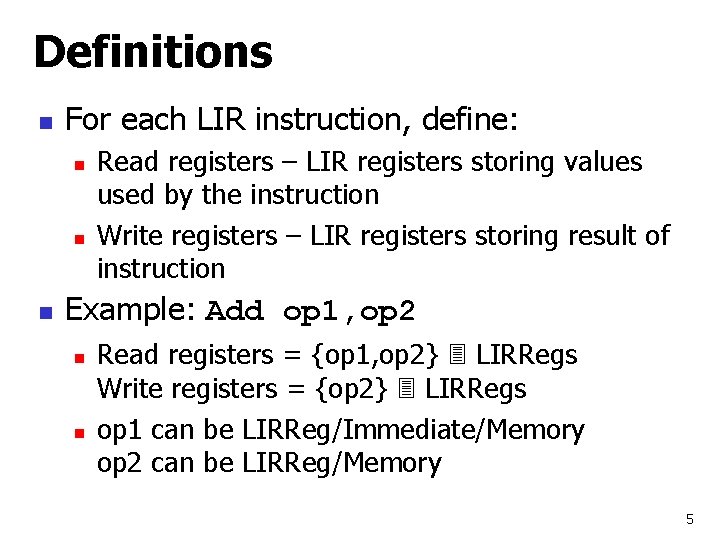

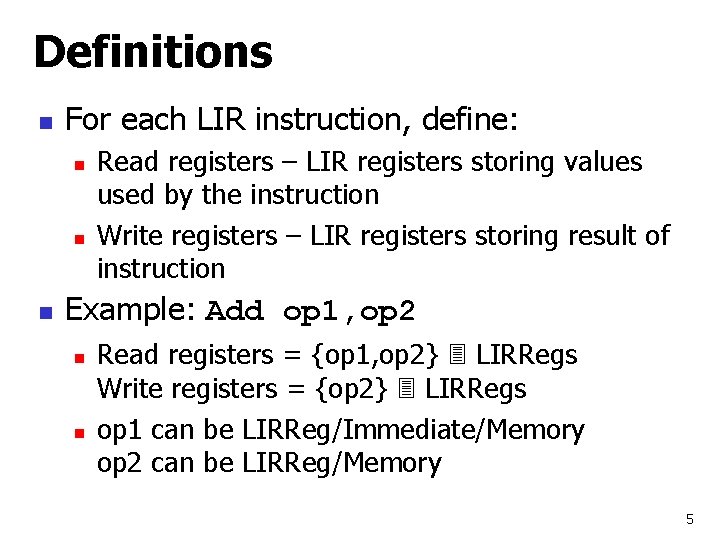

Definitions n For each LIR instruction, define: n n n Read registers – LIR registers storing values used by the instruction Write registers – LIR registers storing result of instruction Example: Add op 1, op 2 n n Read registers = {op 1, op 2} LIRRegs Write registers = {op 2} LIRRegs op 1 can be LIRReg/Immediate/Memory op 2 can be LIRReg/Memory 5

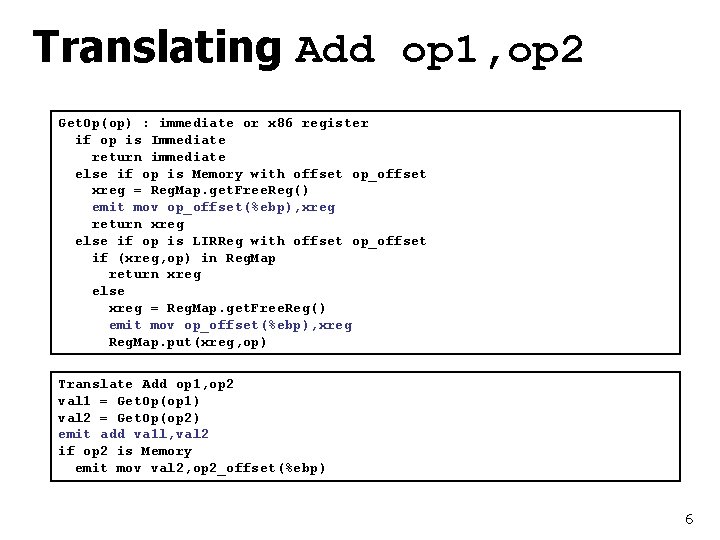

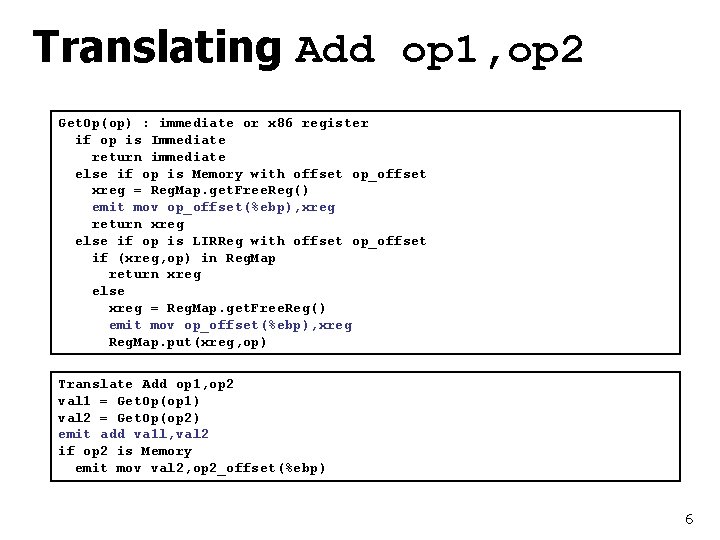

Translating Add op 1, op 2 Get. Op(op) : immediate or x 86 register if op is Immediate return immediate else if op is Memory with offset op_offset xreg = Reg. Map. get. Free. Reg() emit mov op_offset(%ebp), xreg return xreg else if op is LIRReg with offset op_offset if (xreg, op) in Reg. Map return xreg else xreg = Reg. Map. get. Free. Reg() emit mov op_offset(%ebp), xreg Reg. Map. put(xreg, op) Translate Add op 1, op 2 val 1 = Get. Op(op 1) val 2 = Get. Op(op 2) emit add va 1 l, val 2 if op 2 is Memory emit mov val 2, op 2_offset(%ebp) 6

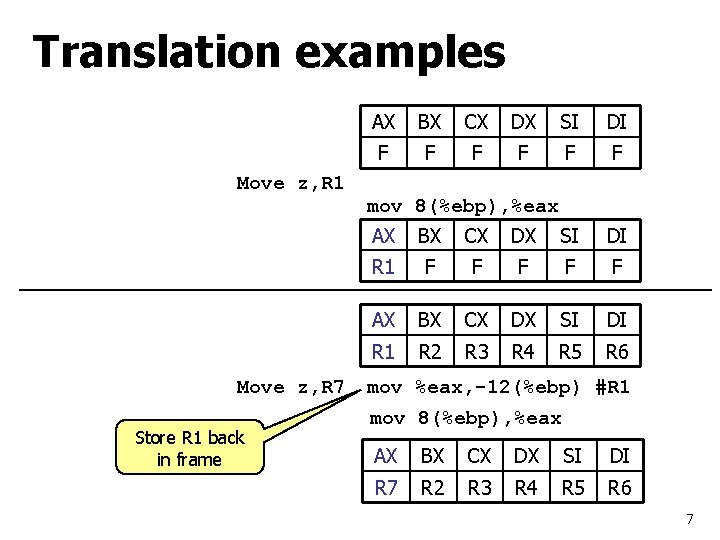

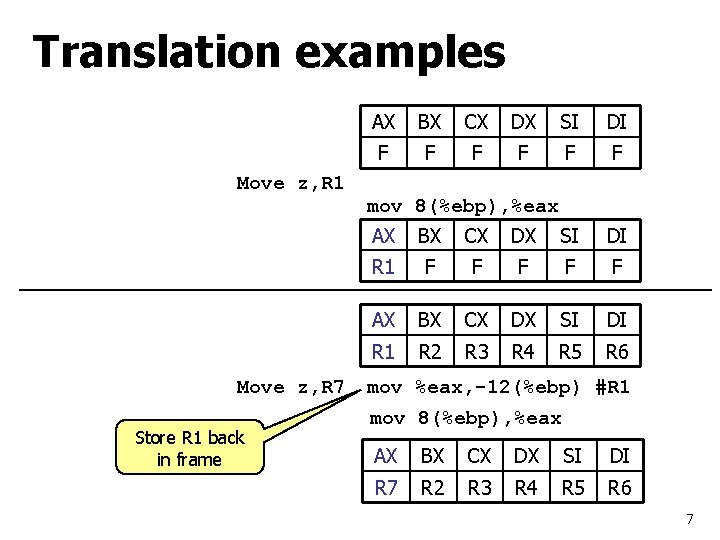

Translation examples Move z, R 1 Move z, R 7 Store R 1 back in frame AX BX CX DX SI DI F F F mov 8(%ebp), %eax AX BX CX DX SI DI R 1 F F F AX BX CX DX SI DI R 1 R 2 R 3 R 4 R 5 R 6 mov %eax, -12(%ebp) #R 1 mov 8(%ebp), %eax AX BX CX DX SI DI R 7 R 2 R 3 R 4 R 5 R 6 7

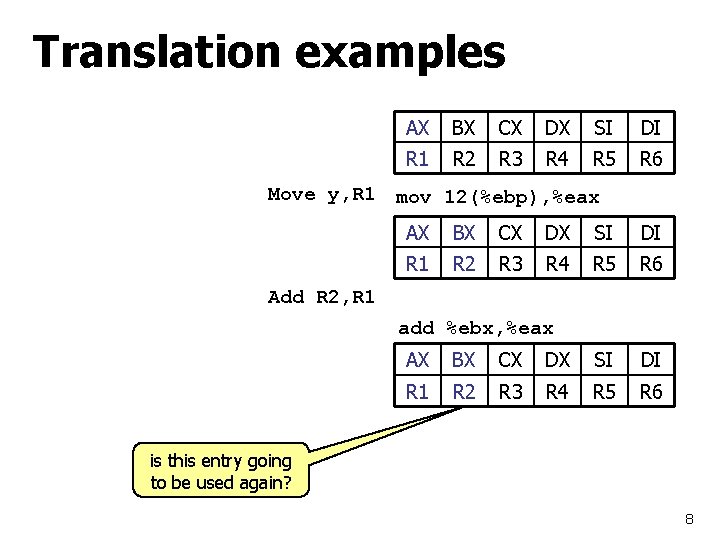

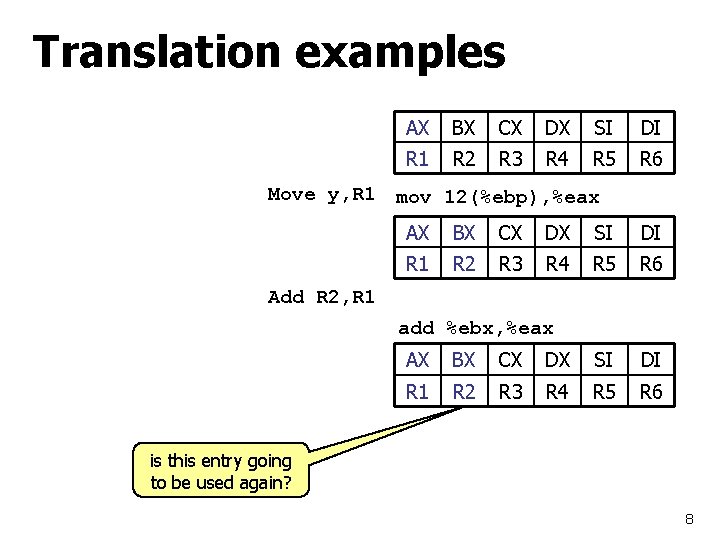

Translation examples AX BX CX DX SI DI R 1 R 2 R 3 R 4 R 5 R 6 Move y, R 1 mov 12(%ebp), %eax AX BX CX DX SI DI R 1 R 2 R 3 R 4 R 5 R 6 Add R 2, R 1 add %ebx, %eax AX BX CX DX SI DI R 1 R 2 R 3 R 4 R 5 R 6 is this entry going to be used again? 8

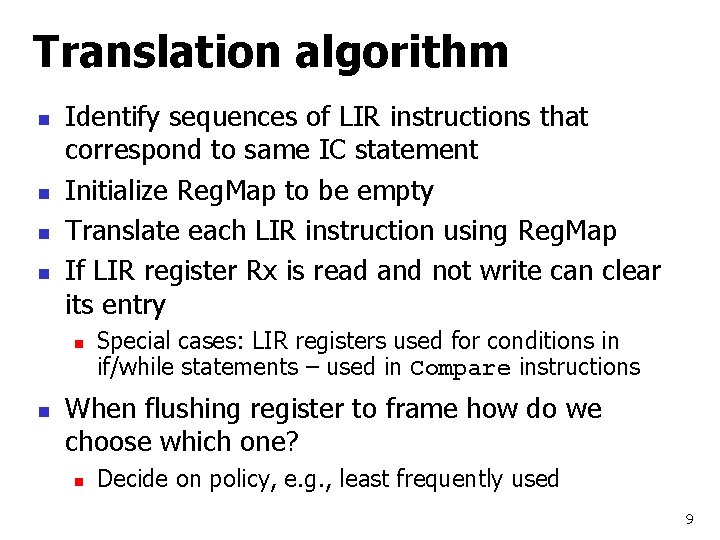

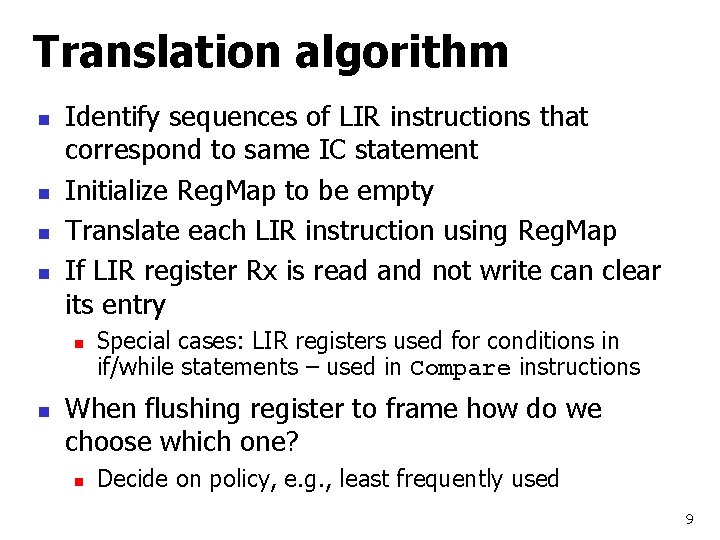

Translation algorithm n n Identify sequences of LIR instructions that correspond to same IC statement Initialize Reg. Map to be empty Translate each LIR instruction using Reg. Map If LIR register Rx is read and not write can clear its entry n n Special cases: LIR registers used for conditions in if/while statements – used in Compare instructions When flushing register to frame how do we choose which one? n Decide on policy, e. g. , least frequently used 9

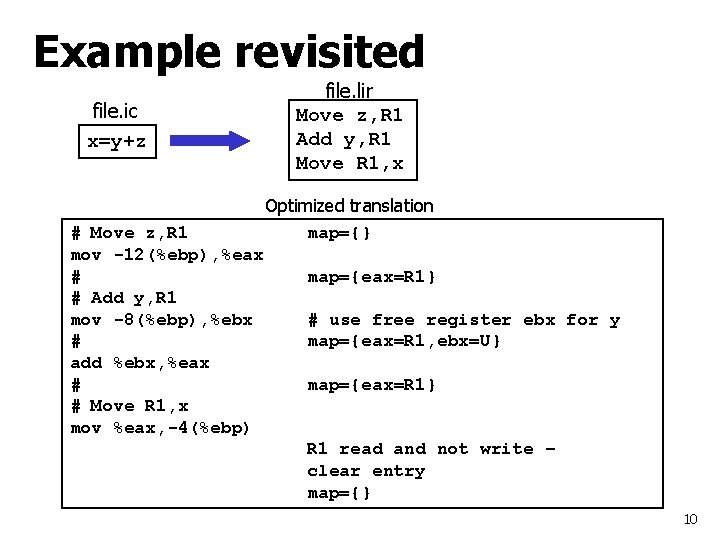

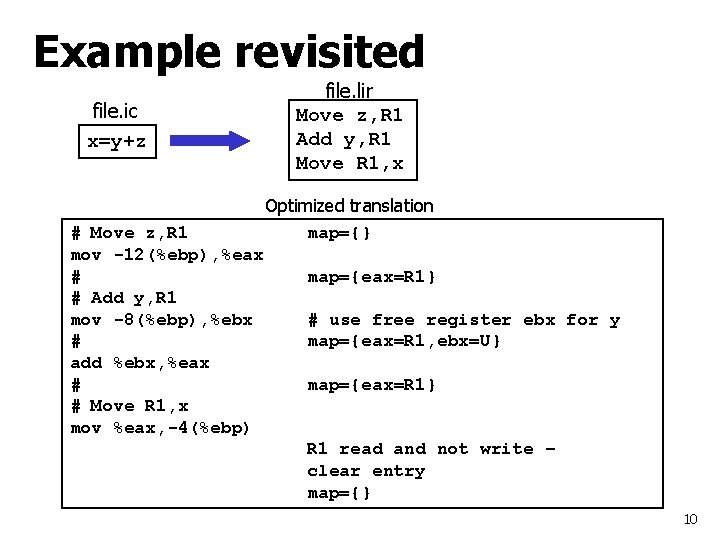

Example revisited file. ic x=y+z # Move z, R 1 mov -12(%ebp), %eax # # Add y, R 1 mov -8(%ebp), %ebx # add %ebx, %eax # # Move R 1, x mov %eax, -4(%ebp) file. lir Move z, R 1 Add y, R 1 Move R 1, x Optimized translation map={} map={eax=R 1} # use free register ebx for y map={eax=R 1, ebx=U} map={eax=R 1} R 1 read and not write – clear entry map={} 10

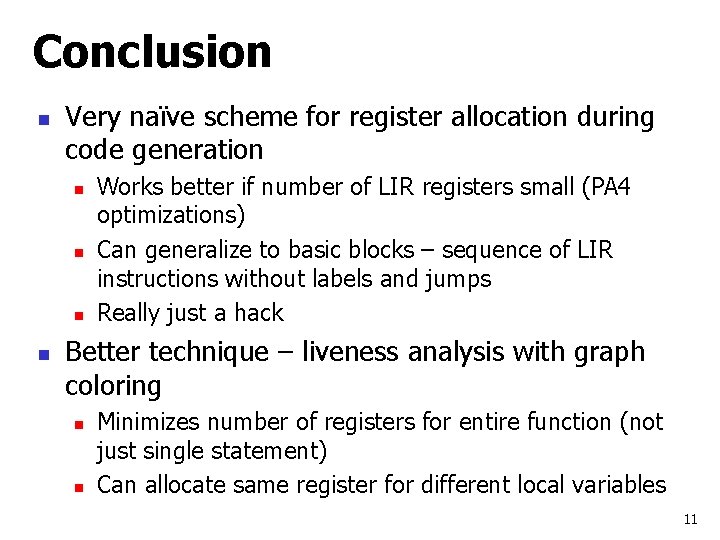

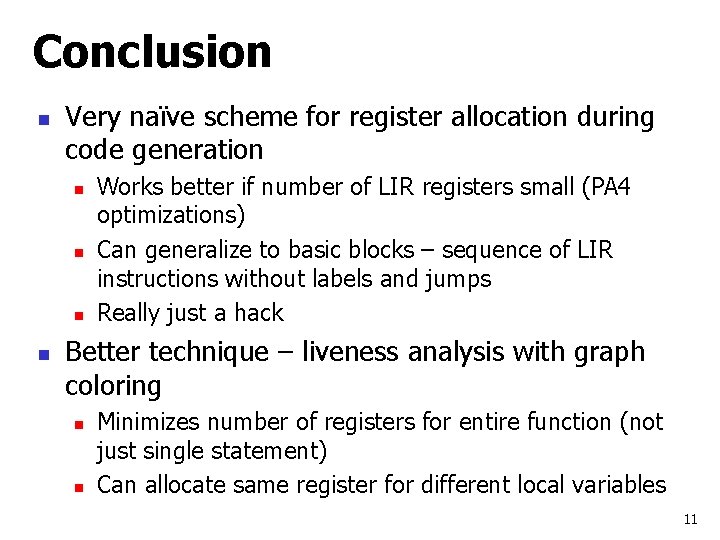

Conclusion n Very naïve scheme for register allocation during code generation n n Works better if number of LIR registers small (PA 4 optimizations) Can generalize to basic blocks – sequence of LIR instructions without labels and jumps Really just a hack Better technique – liveness analysis with graph coloring n n Minimizes number of registers for entire function (not just single statement) Can allocate same register for different local variables 11

That’s all folks 12