A Reconfigurable FTL Architecture for NAND FlashBased Applications

A Reconfigurable FTL Architecture for NAND Flash-Based Applications ACM To. ECS, 2008 2020. 3. 23 유근하

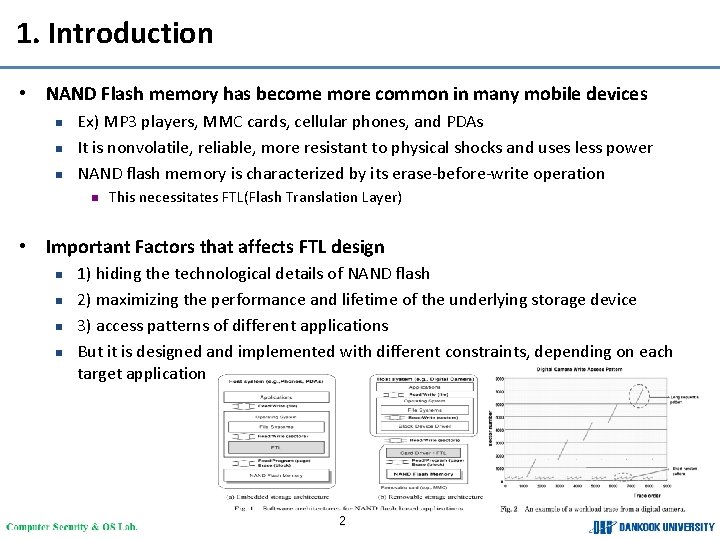

1. Introduction • NAND Flash memory has become more common in many mobile devices n n n Ex) MP 3 players, MMC cards, cellular phones, and PDAs It is nonvolatile, reliable, more resistant to physical shocks and uses less power NAND flash memory is characterized by its erase-before-write operation n This necessitates FTL(Flash Translation Layer) • Important Factors that affects FTL design n n 1) hiding the technological details of NAND flash 2) maximizing the performance and lifetime of the underlying storage device 3) access patterns of different applications But it is designed and implemented with different constraints, depending on each target application 2

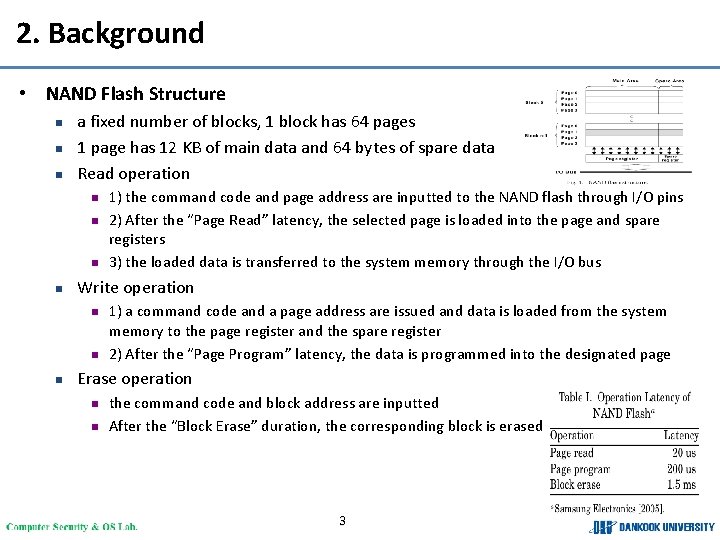

2. Background • NAND Flash Structure n n n a fixed number of blocks, 1 block has 64 pages 1 page has 12 KB of main data and 64 bytes of spare data Read operation n n Write operation n 1) the command code and page address are inputted to the NAND flash through I/O pins 2) After the “Page Read” latency, the selected page is loaded into the page and spare registers 3) the loaded data is transferred to the system memory through the I/O bus 1) a command code and a page address are issued and data is loaded from the system memory to the page register and the spare register 2) After the “Page Program” latency, the data is programmed into the designated page Erase operation n n the command code and block address are inputted After the “Block Erase” duration, the corresponding block is erased 3

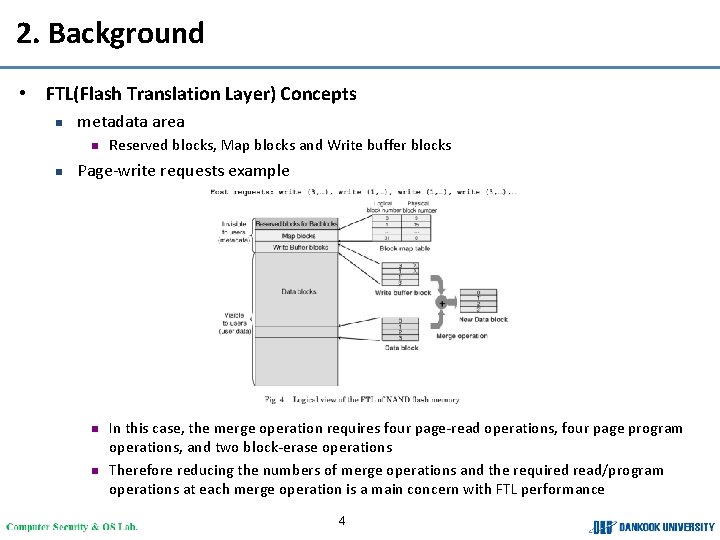

2. Background • FTL(Flash Translation Layer) Concepts n metadata area n n Reserved blocks, Map blocks and Write buffer blocks Page-write requests example n n In this case, the merge operation requires four page-read operations, four page program operations, and two block-erase operations Therefore reducing the numbers of merge operations and the required read/program operations at each merge operation is a main concern with FTL performance 4

3. Mapping Schemes and Related Work • Scheme 1 – Page Mapping n LPN : Logical Page Number PPN : Physical Page Number n Limitation n An efficient “garbage collection” technique should be devised It requires a very large amount of memory space for the map table 5

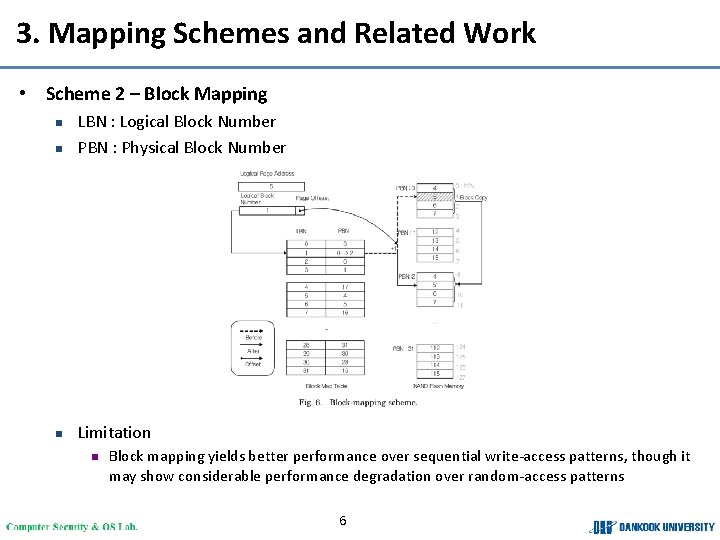

3. Mapping Schemes and Related Work • Scheme 2 – Block Mapping n LBN : Logical Block Number PBN : Physical Block Number n Limitation n n Block mapping yields better performance over sequential write-access patterns, though it may show considerable performance degradation over random-access patterns 6

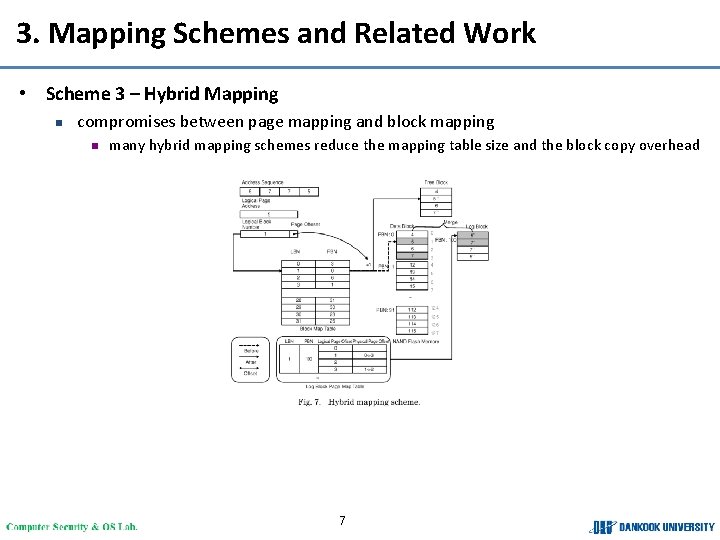

3. Mapping Schemes and Related Work • Scheme 3 – Hybrid Mapping n compromises between page mapping and block mapping n many hybrid mapping schemes reduce the mapping table size and the block copy overhead 7

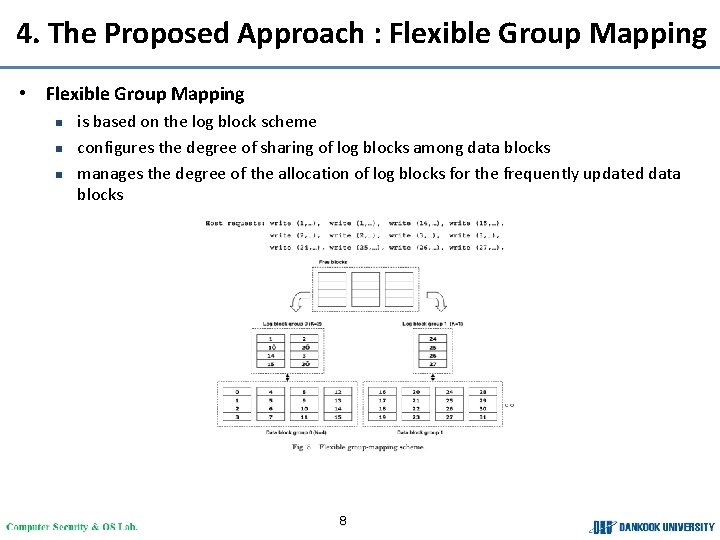

4. The Proposed Approach : Flexible Group Mapping • Flexible Group Mapping n n n is based on the log block scheme configures the degree of sharing of log blocks among data blocks manages the degree of the allocation of log blocks for the frequently updated data blocks 8

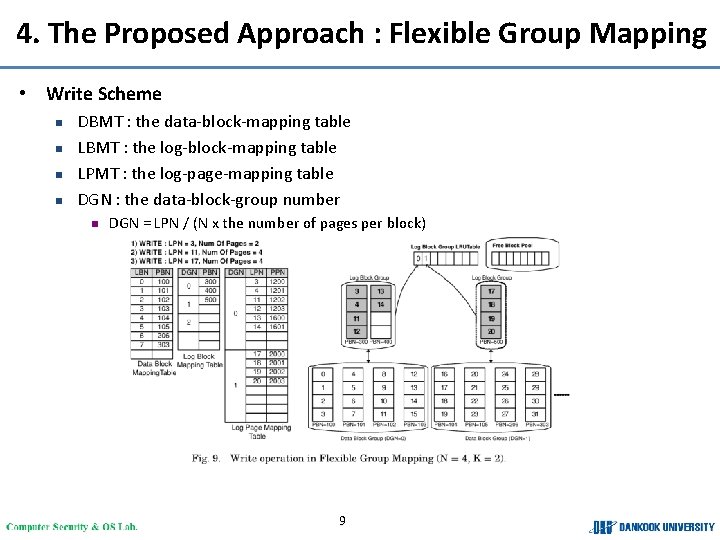

4. The Proposed Approach : Flexible Group Mapping • Write Scheme n n DBMT : the data-block-mapping table LBMT : the log-block-mapping table LPMT : the log-page-mapping table DGN : the data-block-group number n DGN = LPN / (N x the number of pages per block) 9

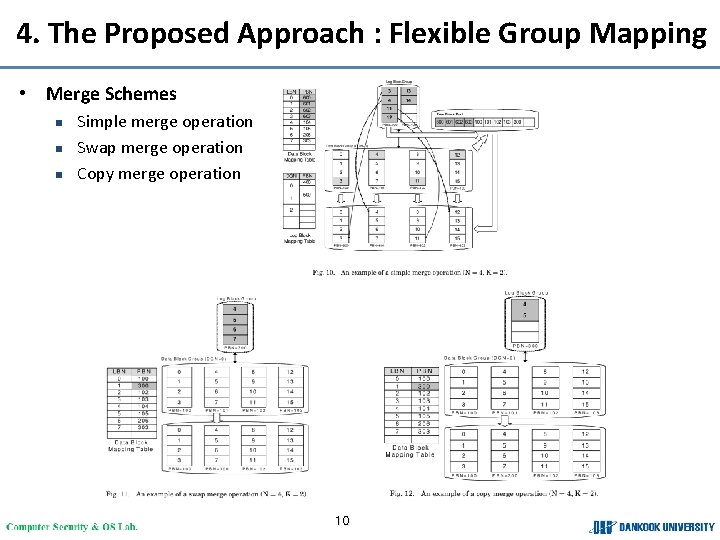

4. The Proposed Approach : Flexible Group Mapping • Merge Schemes n n n Simple merge operation Swap merge operation Copy merge operation 10

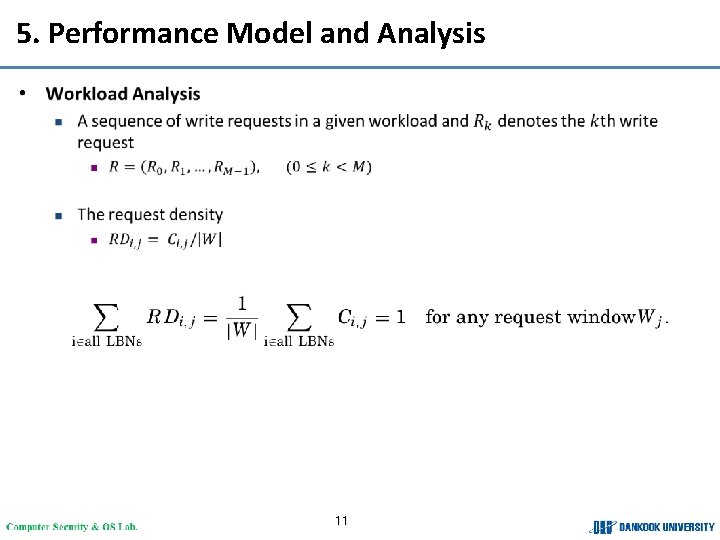

5. Performance Model and Analysis • 11

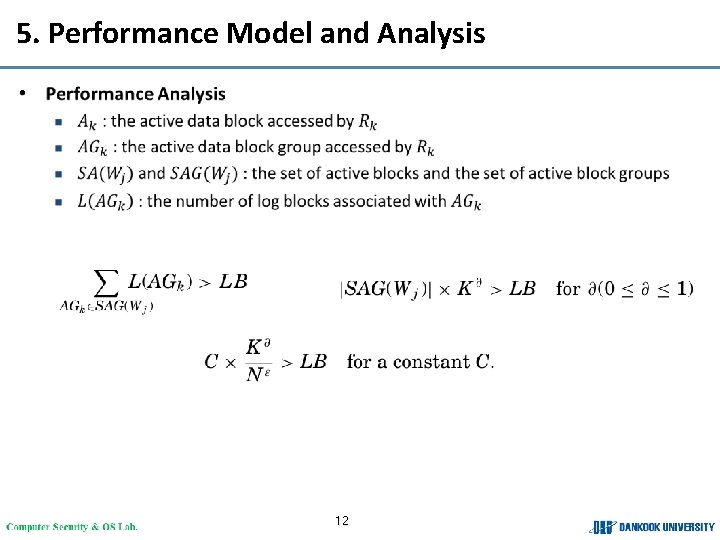

5. Performance Model and Analysis • 12

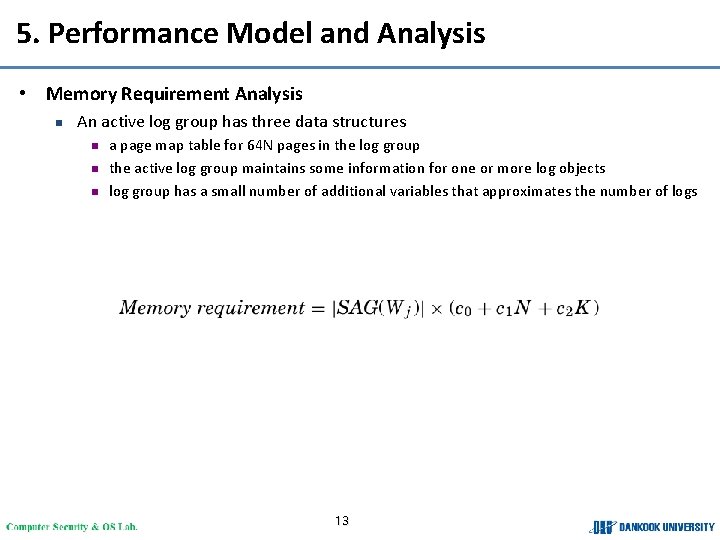

5. Performance Model and Analysis • Memory Requirement Analysis n An active log group has three data structures n n n a page map table for 64 N pages in the log group the active log group maintains some information for one or more log objects log group has a small number of additional variables that approximates the number of logs 13

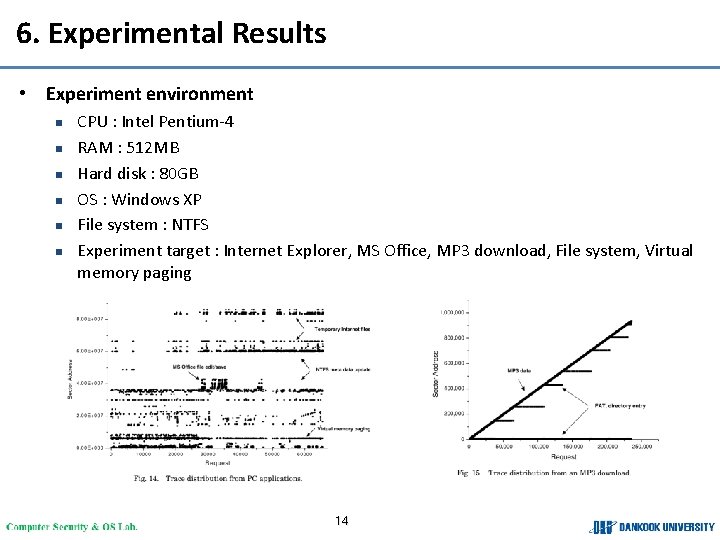

6. Experimental Results • Experiment environment n n n CPU : Intel Pentium-4 RAM : 512 MB Hard disk : 80 GB OS : Windows XP File system : NTFS Experiment target : Internet Explorer, MS Office, MP 3 download, File system, Virtual memory paging 14

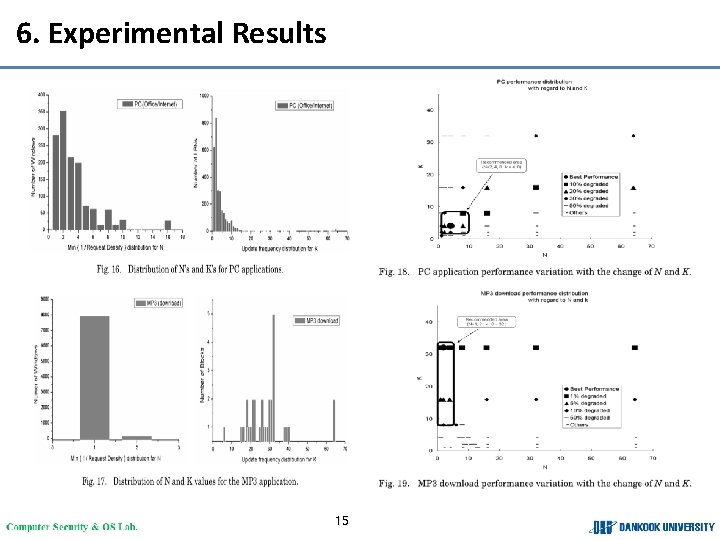

6. Experimental Results 15

7. Conclusions • The proposed reconfigurable FTL architecture efficiently handles diverse NAND flash applications ranging from MP 3 to SSD for a PC • In order to efficiently explore the design space, a workload analysis method based on the density distribution of given requests and the update frequency is proposed • The experimental results show n n the proposed architecture can be reconfigured to a given workload ranging from MP 3 to PC applications the proposed analysis method can efficiently find the optimal N and K values within a reasonable amount of time 16

17

- Slides: 17