A point about electronics Dominique Breton Phone meeting

A point about electronics … Dominique Breton Phone meeting – 09/10/2008

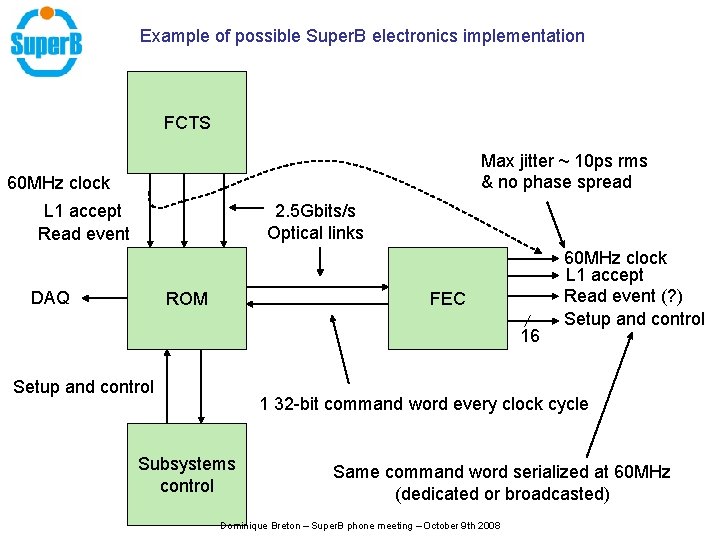

Example of possible Super. B electronics implementation FCTS Max jitter ~ 10 ps rms & no phase spread 60 MHz clock L 1 accept Read event 2. 5 Gbits/s Optical links DAQ ROM FEC 16 Setup and control 60 MHz clock L 1 accept Read event (? ) Setup and control 1 32 -bit command word every clock cycle Subsystems control Same command word serialized at 60 MHz (dedicated or broadcasted) Dominique Breton – Super. B phone meeting – October 9 th 2008

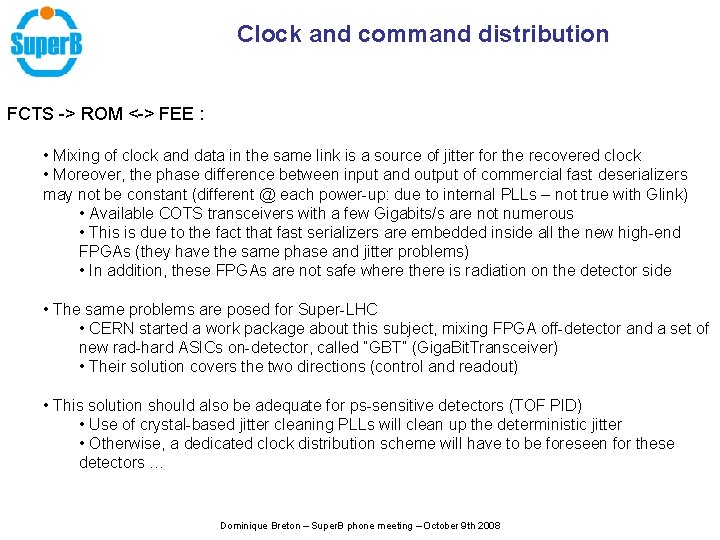

Clock and command distribution FCTS -> ROM <-> FEE : • Mixing of clock and data in the same link is a source of jitter for the recovered clock • Moreover, the phase difference between input and output of commercial fast deserializers may not be constant (different @ each power-up: due to internal PLLs – not true with Glink) • Available COTS transceivers with a few Gigabits/s are not numerous • This is due to the fact that fast serializers are embedded inside all the new high-end FPGAs (they have the same phase and jitter problems) • In addition, these FPGAs are not safe where there is radiation on the detector side • The same problems are posed for Super-LHC • CERN started a work package about this subject, mixing FPGA off-detector and a set of new rad-hard ASICs on-detector, called “GBT” (Giga. Bit. Transceiver) • Their solution covers the two directions (control and readout) • This solution should also be adequate for ps-sensitive detectors (TOF PID) • Use of crystal-based jitter cleaning PLLs will clean up the deterministic jitter • Otherwise, a dedicated clock distribution scheme will have to be foreseen for these detectors … Dominique Breton – Super. B phone meeting – October 9 th 2008

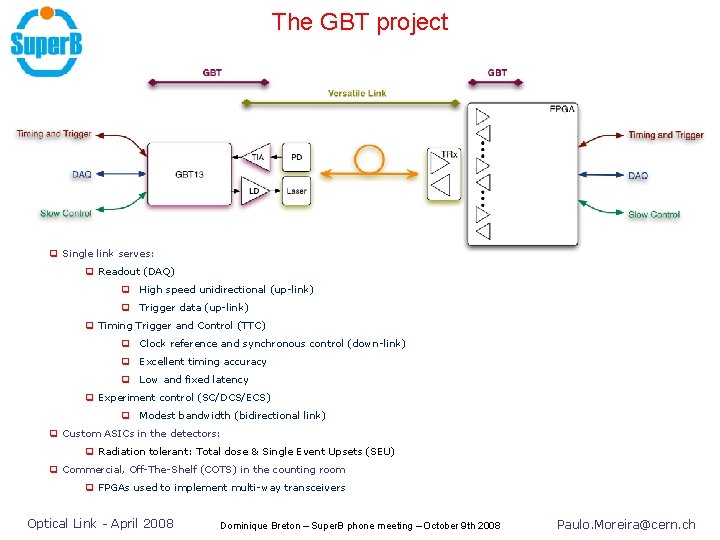

The GBT project q Single link serves: q Readout (DAQ) q High speed unidirectional (up-link) q Trigger data (up-link) q Timing Trigger and Control (TTC) q Clock reference and synchronous control (down-link) q Excellent timing accuracy q Low and fixed latency q Experiment control (SC/DCS/ECS) q Modest bandwidth (bidirectional link) q Custom ASICs in the detectors: q Radiation tolerant: Total dose & Single Event Upsets (SEU) q Commercial, Off-The-Shelf (COTS) in the counting room q FPGAs used to implement multi-way transceivers Optical Link - April 2008 Dominique Breton – Super. B phone meeting – October 9 th 2008 Paulo. Moreira@cern. ch

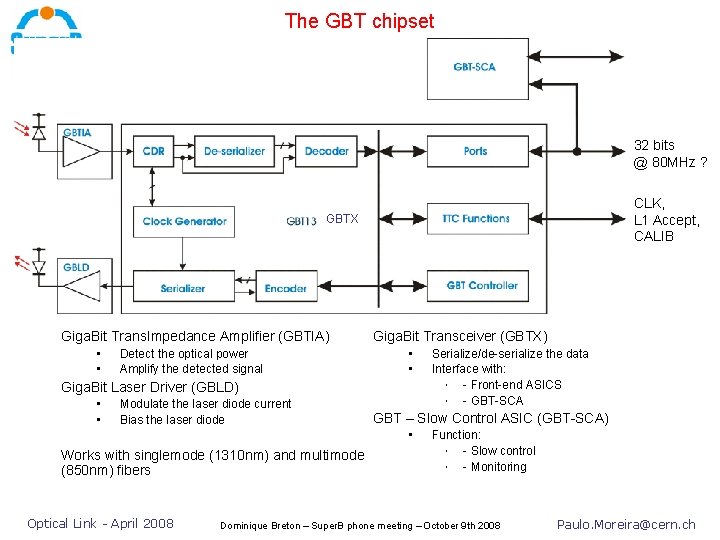

The GBT chipset 32 bits @ 80 MHz ? CLK, L 1 Accept, CALIB GBTX Giga. Bit Trans. Impedance Amplifier (GBTIA) • • Detect the optical power Amplify the detected signal Giga. Bit Transceiver (GBTX) • • Giga. Bit Laser Driver (GBLD) • • Modulate the laser diode current Bias the laser diode GBT – Slow Control ASIC (GBT-SCA) • Works with singlemode (1310 nm) and multimode (850 nm) fibers Optical Link - April 2008 Serialize/de-serialize the data Interface with: - Front-end ASICS - GBT-SCA Function: - Slow control - Monitoring Dominique Breton – Super. B phone meeting – October 9 th 2008 Paulo. Moreira@cern. ch

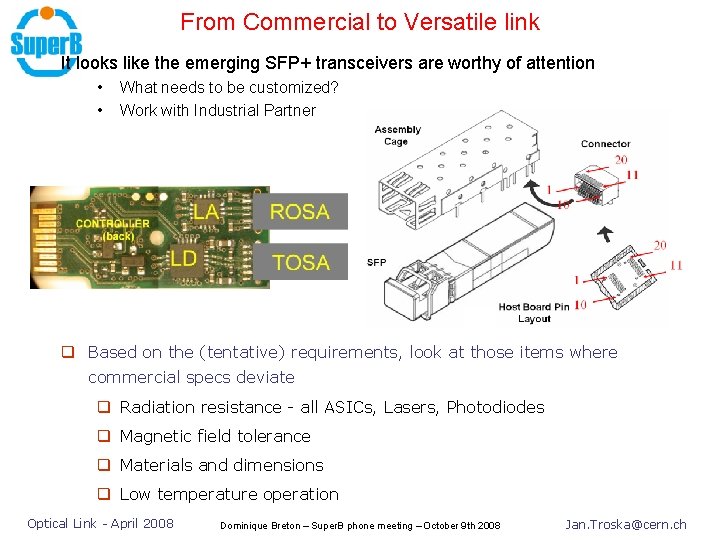

From Commercial to Versatile link It looks like the emerging SFP+ transceivers are worthy of attention • • What needs to be customized? Work with Industrial Partner q Based on the (tentative) requirements, look at those items where commercial specs deviate q Radiation resistance - all ASICs, Lasers, Photodiodes q Magnetic field tolerance q Materials and dimensions q Low temperature operation Optical Link - April 2008 Dominique Breton – Super. B phone meeting – October 9 th 2008 Jan. Troska@cern. ch

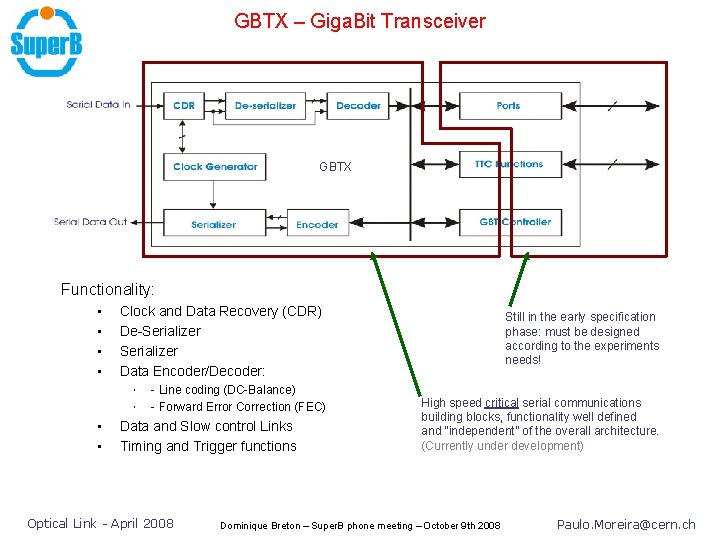

GBTX – Giga. Bit Transceiver GBTX Functionality: • • Clock and Data Recovery (CDR) De-Serializer Data Encoder/Decoder: - Line coding (DC-Balance) - Forward Error Correction (FEC) • • Data and Slow control Links Timing and Trigger functions Optical Link - April 2008 Still in the early specification phase: must be designed according to the experiments needs! High speed critical serial communications building blocks, functionality well defined and “independent” of the overall architecture. (Currently under development) Dominique Breton – Super. B phone meeting – October 9 th 2008 Paulo. Moreira@cern. ch

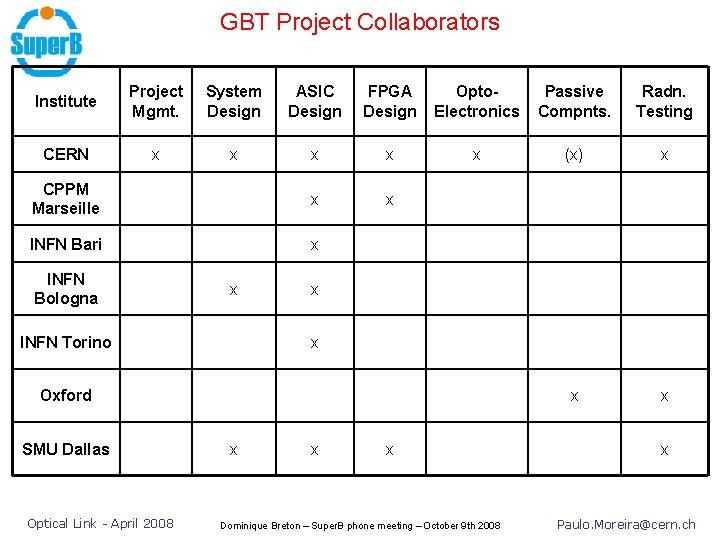

GBT Project Collaborators Institute Project Mgmt. System Design ASIC Design FPGA Design Opto. Electronics Passive Compnts. Radn. Testing CERN x x x (x) x CPPM Marseille x x INFN Bari x x x INFN Bologna x INFN Torino x x Oxford SMU Dallas Optical Link - April 2008 x x x Dominique Breton – Super. B phone meeting – October 9 th 2008 x Paulo. Moreira@cern. ch

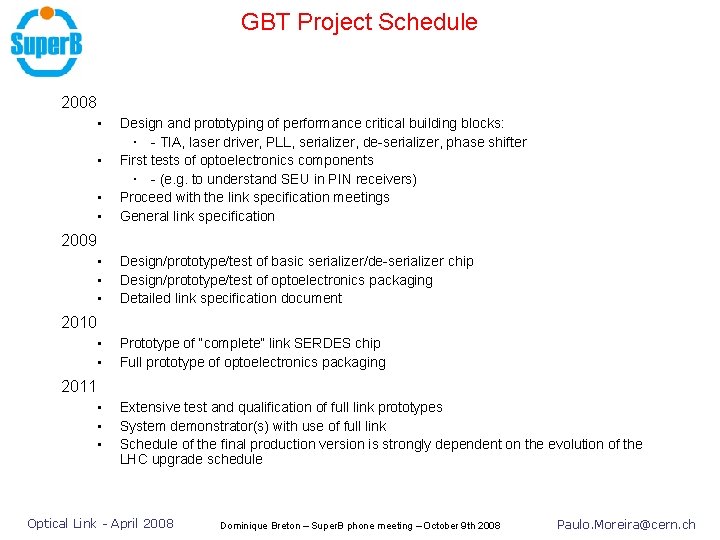

GBT Project Schedule 2008 • • • Design and prototyping of performance critical building blocks: - TIA, laser driver, PLL, serializer, de-serializer, phase shifter First tests of optoelectronics components - (e. g. to understand SEU in PIN receivers) Proceed with the link specification meetings General link specification • • • Design/prototype/test of basic serializer/de-serializer chip Design/prototype/test of optoelectronics packaging Detailed link specification document • • Prototype of “complete” link SERDES chip Full prototype of optoelectronics packaging • • • Extensive test and qualification of full link prototypes System demonstrator(s) with use of full link Schedule of the final production version is strongly dependent on the evolution of the LHC upgrade schedule • 2009 2010 2011 Optical Link - April 2008 Dominique Breton – Super. B phone meeting – October 9 th 2008 Paulo. Moreira@cern. ch

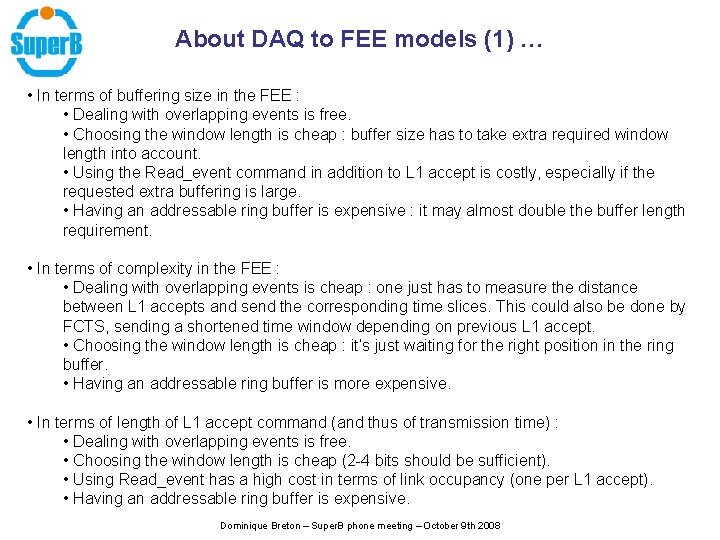

About DAQ to FEE models (1) … • In terms of buffering size in the FEE : • Dealing with overlapping events is free. • Choosing the window length is cheap : buffer size has to take extra required window length into account. • Using the Read_event command in addition to L 1 accept is costly, especially if the requested extra buffering is large. • Having an addressable ring buffer is expensive : it may almost double the buffer length requirement. • In terms of complexity in the FEE : • Dealing with overlapping events is cheap : one just has to measure the distance between L 1 accepts and send the corresponding time slices. This could also be done by FCTS, sending a shortened time window depending on previous L 1 accept. • Choosing the window length is cheap : it’s just waiting for the right position in the ring buffer. • Having an addressable ring buffer is more expensive. • In terms of length of L 1 accept command (and thus of transmission time) : • Dealing with overlapping events is free. • Choosing the window length is cheap (2 -4 bits should be sufficient). • Using Read_event has a high cost in terms of link occupancy (one per L 1 accept). • Having an addressable ring buffer is expensive. Dominique Breton – Super. B phone meeting – October 9 th 2008

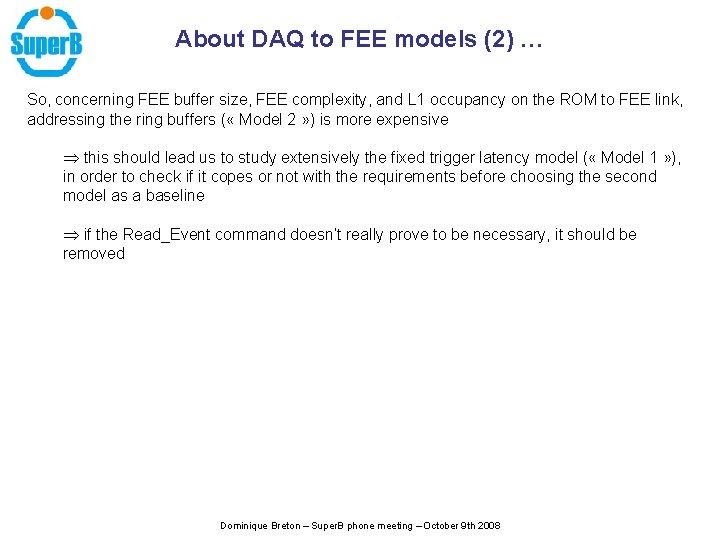

About DAQ to FEE models (2) … So, concerning FEE buffer size, FEE complexity, and L 1 occupancy on the ROM to FEE link, addressing the ring buffers ( « Model 2 » ) is more expensive Þ this should lead us to study extensively the fixed trigger latency model ( « Model 1 » ), in order to check if it copes or not with the requirements before choosing the second model as a baseline Þ if the Read_Event command doesn’t really prove to be necessary, it should be removed Dominique Breton – Super. B phone meeting – October 9 th 2008

Reuse of BABAR elements: • BABAR’s dismantling has begun last July. • Beside inner calorimeter electronics, are there items worth being kept for Super. B ? • It was shown that the distance between Super. B and its electronics hut shouldn’t be too much longer than BABAR’s • Could some cables get reused ? • Crates ? • Power supplies (LV and HV) ? • For instance, the DIRC HV supplies and their expensive cables might be good candidates • Same for calorimeter power supply cables • Reuse of optical fibers ? • Experts from BABAR subsystem should now have prepared lists of items and gotten in touch with Bill. Did they ? • We will spent time with Bill end of October at SLAC to study all these points together in front of the detector … Dominique Breton – Super. B phone meeting – October 9 th 2008

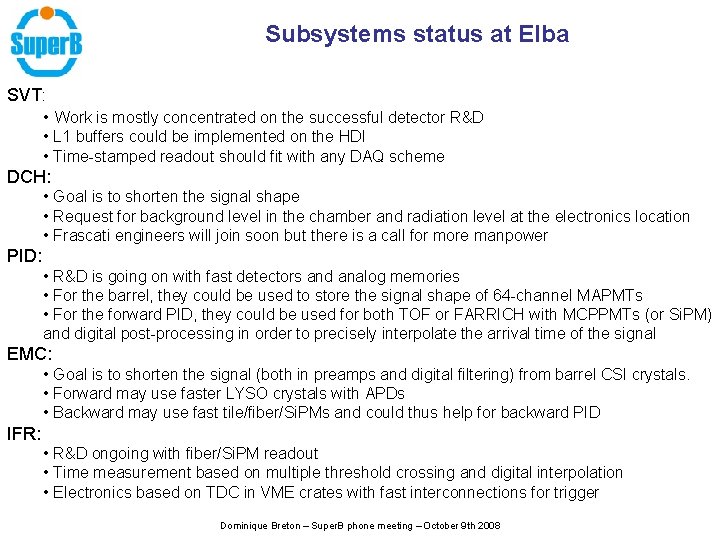

Subsystems status at Elba SVT: • Work is mostly concentrated on the successful detector R&D • L 1 buffers could be implemented on the HDI • Time-stamped readout should fit with any DAQ scheme DCH: • Goal is to shorten the signal shape • Request for background level in the chamber and radiation level at the electronics location • Frascati engineers will join soon but there is a call for more manpower PID: • R&D is going on with fast detectors and analog memories • For the barrel, they could be used to store the signal shape of 64 -channel MAPMTs • For the forward PID, they could be used for both TOF or FARRICH with MCPPMTs (or Si. PM) and digital post-processing in order to precisely interpolate the arrival time of the signal EMC: • Goal is to shorten the signal (both in preamps and digital filtering) from barrel CSI crystals. • Forward may use faster LYSO crystals with APDs • Backward may use fast tile/fiber/Si. PMs and could thus help for backward PID IFR: • R&D ongoing with fiber/Si. PM readout • Time measurement based on multiple threshold crossing and digital interpolation • Electronics based on TDC in VME crates with fast interconnections for trigger Dominique Breton – Super. B phone meeting – October 9 th 2008

Conclusion - CERN has started a generic R&D for detector control and readout. • They propose us to join them … • The key point is the production if Super-LHC is delayed … - We would like to discuss farther about the two DAQ models with Gregory and Stephen during the last week of October. • Are they available at this period ? - We will study the reuse of BABAR elements at SLAC with Bill end of October. - In order to be able to write down the TDR, we need simulations on the radiation background in the detector • Was anything done yet ? - Next electronics discussion ? Dominique Breton – Super. B phone meeting – October 9 th 2008

- Slides: 14