A Play Lab 2 Task 8 Core Timer

A Play Lab. 2 Task 8 Core Timer Interrupts Acted by the Human Microcontroller Ensemble from ENCM 415 CORE Timer Interrupts -- a play,

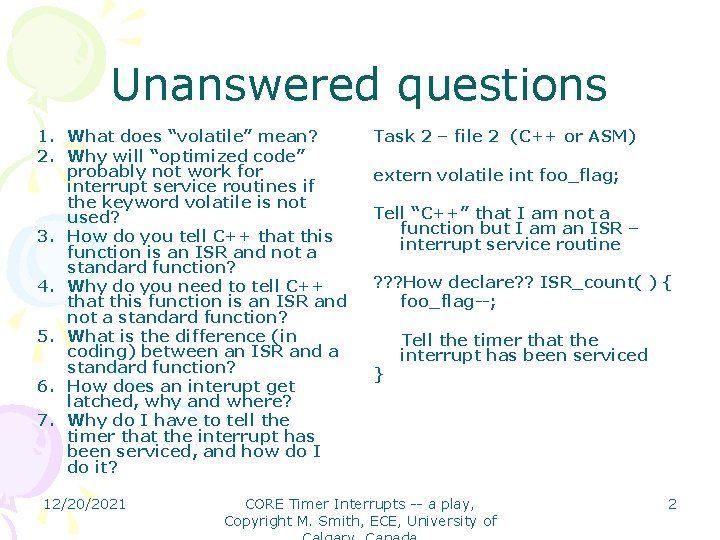

Unanswered questions 1. What does “volatile” mean? 2. Why will “optimized code” probably not work for interrupt service routines if the keyword volatile is not used? 3. How do you tell C++ that this function is an ISR and not a standard function? 4. Why do you need to tell C++ that this function is an ISR and not a standard function? 5. What is the difference (in coding) between an ISR and a standard function? 6. How does an interupt get latched, why and where? 7. Why do I have to tell the timer that the interrupt has been serviced, and how do I do it? 12/20/2021 Task 2 – file 2 (C++ or ASM) extern volatile int foo_flag; Tell “C++” that I am not a function but I am an ISR – interrupt service routine ? ? ? How declare? ? ISR_count( ) { foo_flag--; } Tell the timer that the interrupt has been serviced CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 2

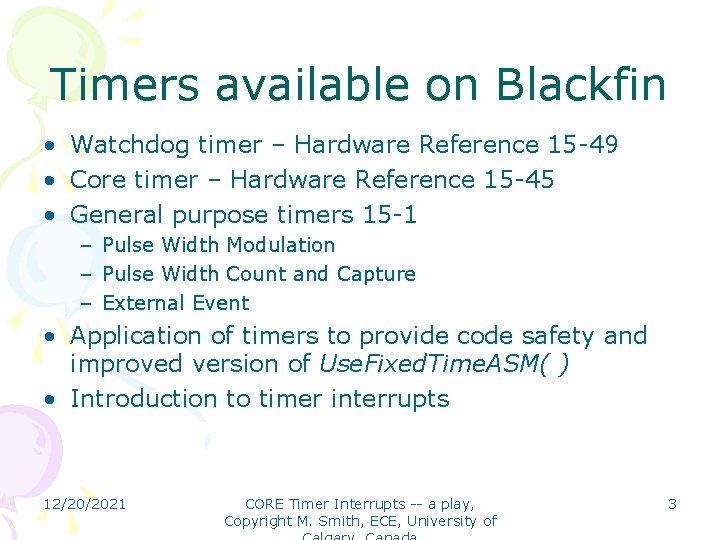

Timers available on Blackfin • Watchdog timer – Hardware Reference 15 -49 • Core timer – Hardware Reference 15 -45 • General purpose timers 15 -1 – Pulse Width Modulation – Pulse Width Count and Capture – External Event • Application of timers to provide code safety and improved version of Use. Fixed. Time. ASM( ) • Introduction to timer interrupts 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 3

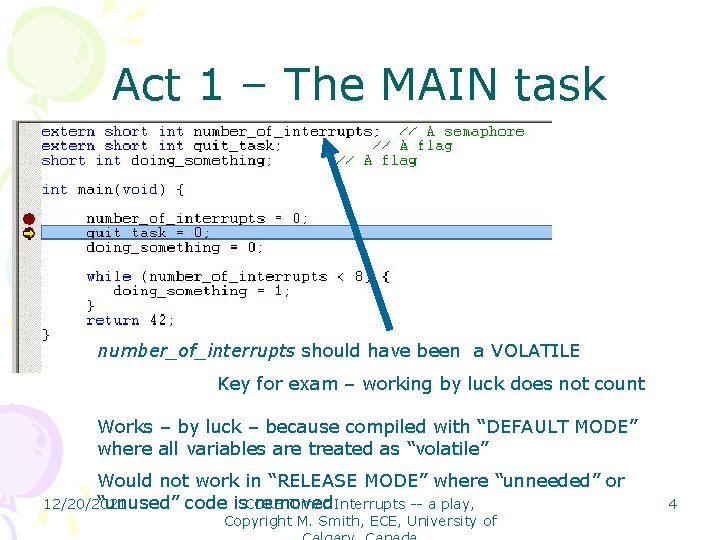

Act 1 – The MAIN task number_of_interrupts should have been a VOLATILE Key for exam – working by luck does not count Works – by luck – because compiled with “DEFAULT MODE” where all variables are treated as “volatile” Would not work in “RELEASE MODE” where “unneeded” or “unused” code is. CORE removed 12/20/2021 Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 4

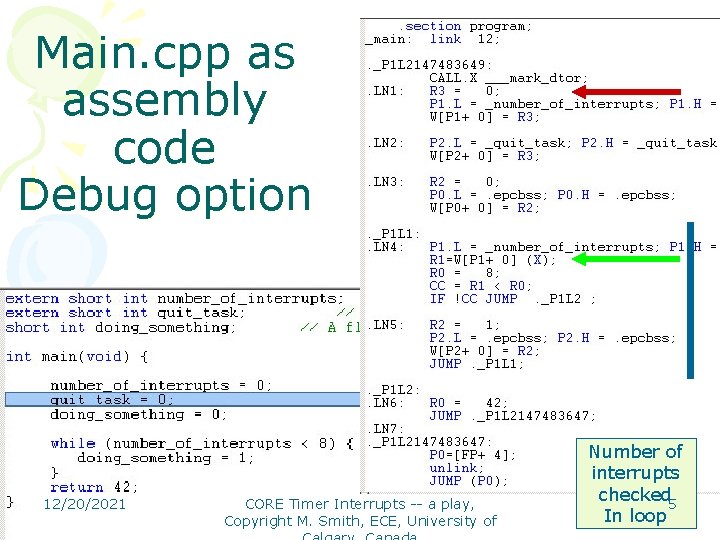

Main. cpp as assembly code Debug option 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of Number of interrupts checked 5 In loop

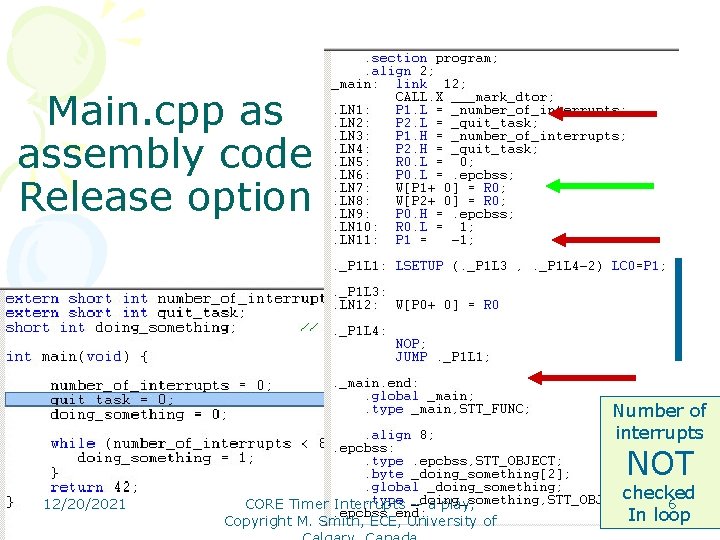

Main. cpp as assembly code Release option Number of interrupts NOT 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of checked 6 In loop

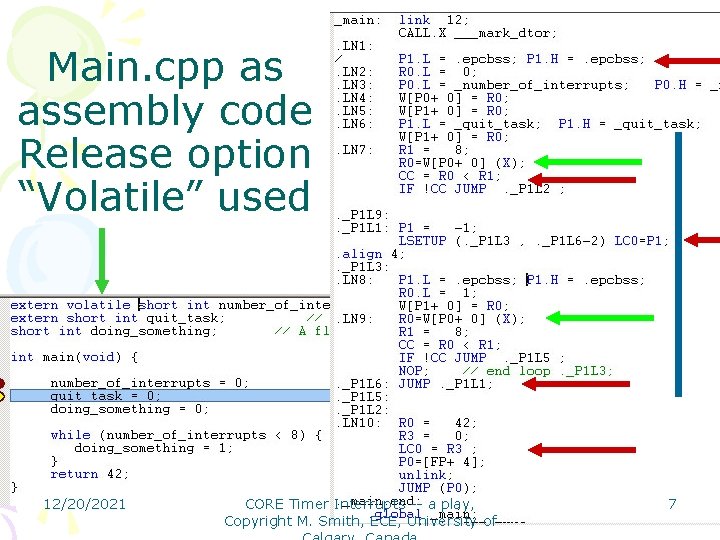

Main. cpp as assembly code Release option “Volatile” used 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 7

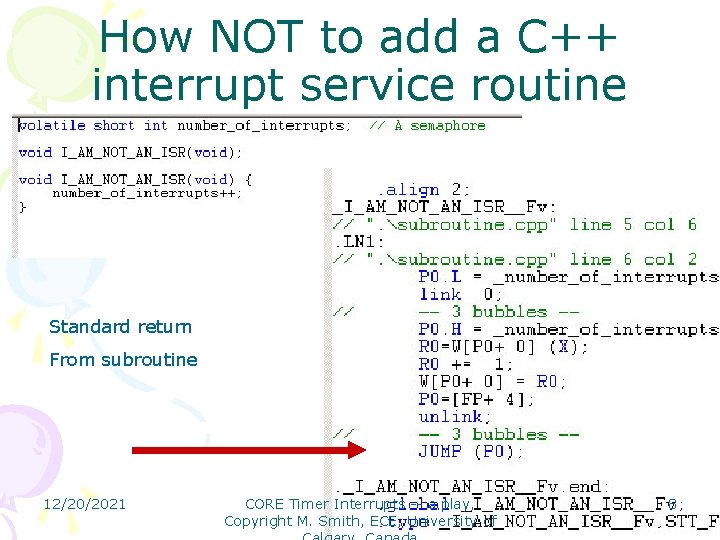

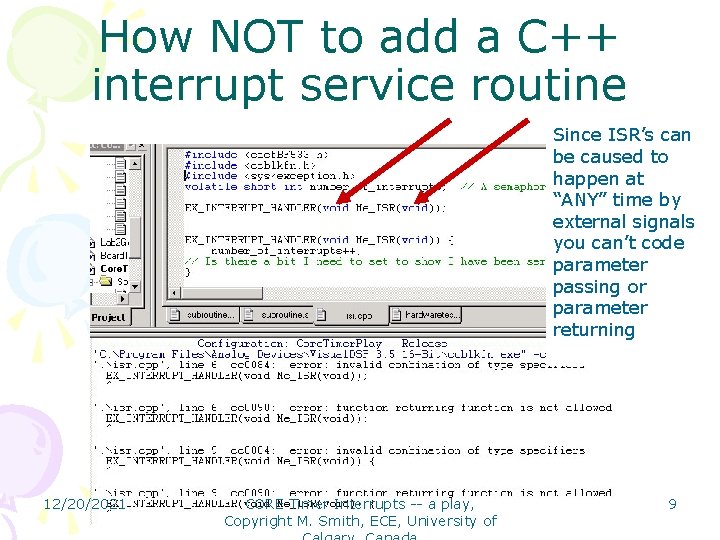

How NOT to add a C++ interrupt service routine Standard return From subroutine 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 8

How NOT to add a C++ interrupt service routine Since ISR’s can be caused to happen at “ANY” time by external signals you can’t code parameter passing or parameter returning 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 9

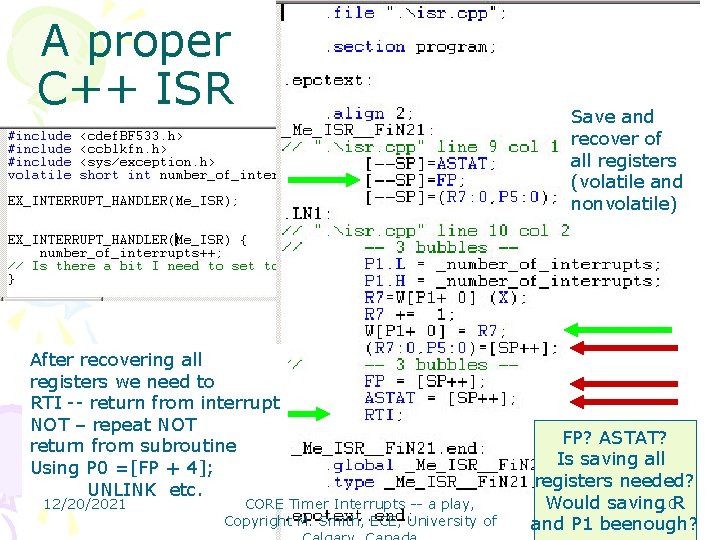

A proper C++ ISR After recovering all registers we need to RTI -- return from interrupt NOT – repeat NOT return from subroutine Using P 0 =[FP + 4]; UNLINK etc. 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of Save and recover of all registers (volatile and nonvolatile) FP? ASTAT? Is saving all registers needed? Would saving 10 R and P 1 beenough?

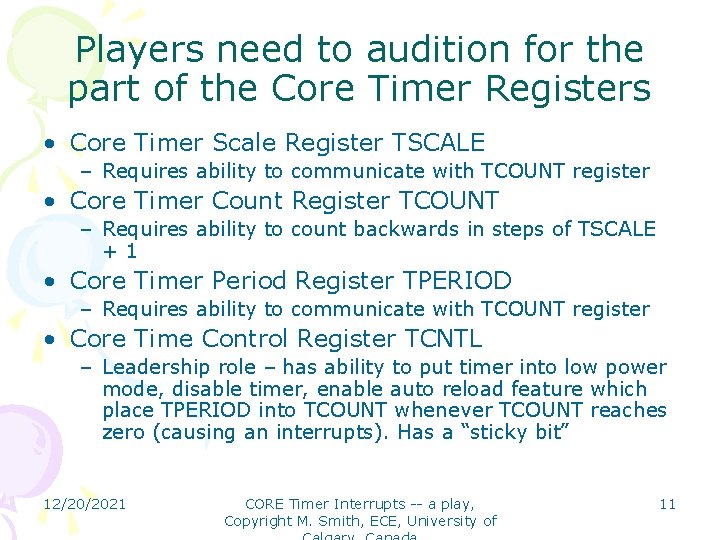

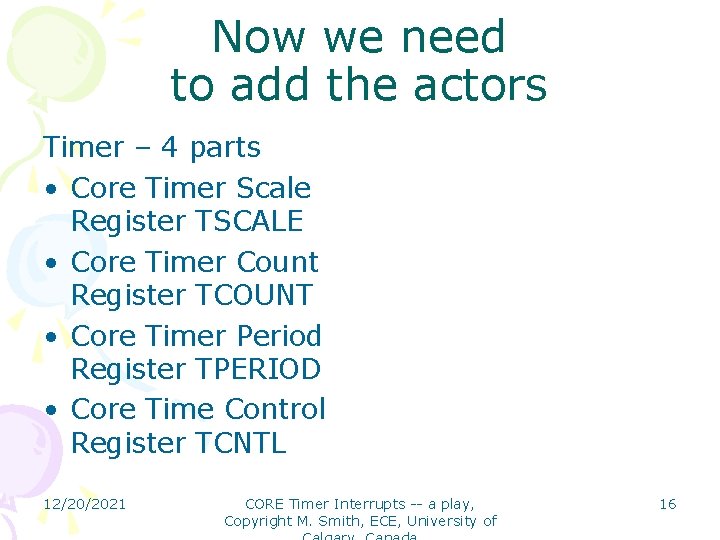

Players need to audition for the part of the Core Timer Registers • Core Timer Scale Register TSCALE – Requires ability to communicate with TCOUNT register • Core Timer Count Register TCOUNT – Requires ability to count backwards in steps of TSCALE +1 • Core Timer Period Register TPERIOD – Requires ability to communicate with TCOUNT register • Core Time Control Register TCNTL – Leadership role – has ability to put timer into low power mode, disable timer, enable auto reload feature which place TPERIOD into TCOUNT whenever TCOUNT reaches zero (causing an interrupts). Has a “sticky bit” 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 11

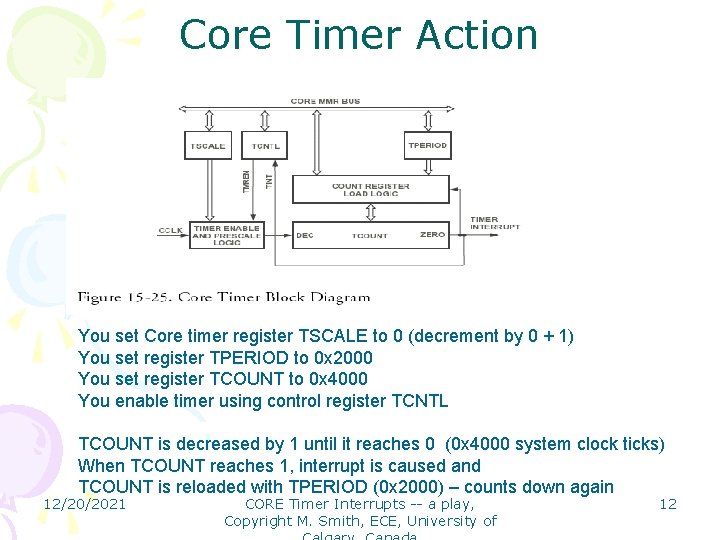

Core Timer Action You set Core timer register TSCALE to 0 (decrement by 0 + 1) You set register TPERIOD to 0 x 2000 You set register TCOUNT to 0 x 4000 You enable timer using control register TCNTL TCOUNT is decreased by 1 until it reaches 0 (0 x 4000 system clock ticks) When TCOUNT reaches 1, interrupt is caused and TCOUNT is reloaded with TPERIOD (0 x 2000) – counts down again 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 12

• The play is about to start 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 13

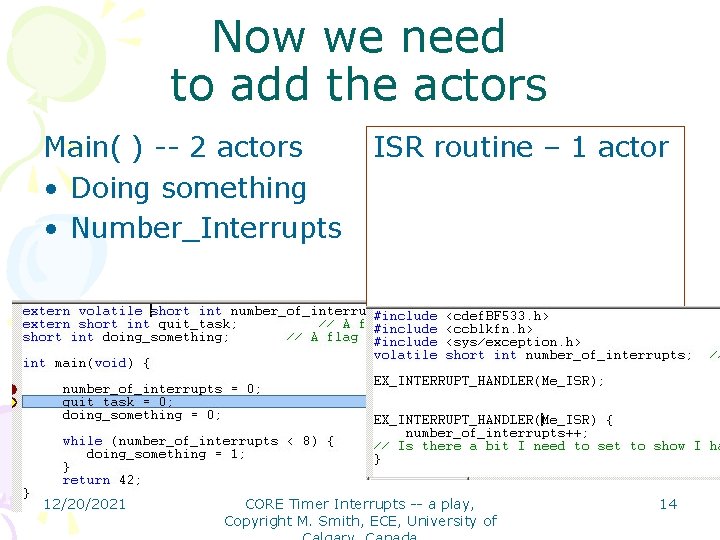

Now we need to add the actors Main( ) -- 2 actors • Doing something • Number_Interrupts 12/20/2021 ISR routine – 1 actor CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 14

The play starts • The main program and ISR operation will now be demonstrated • The narrator will now “Build ALL”, and then DEBUG | RUN • WHAT ELSE IS NEEDED MAKE THE ISR WORK? 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 15

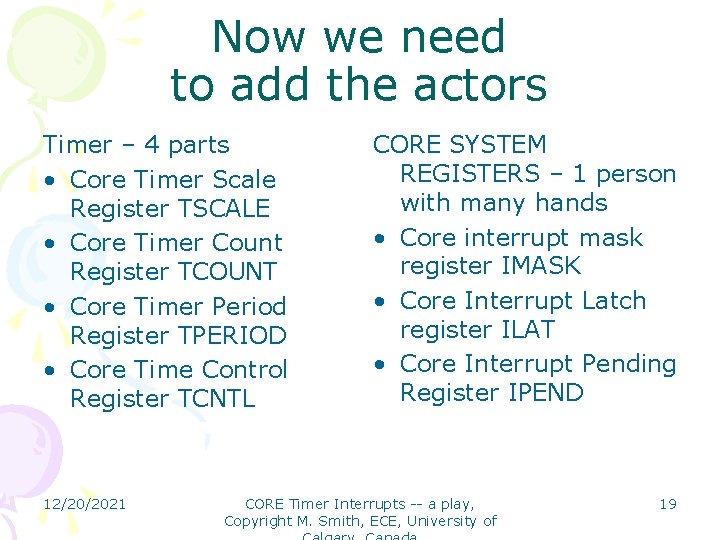

Now we need to add the actors Timer – 4 parts • Core Timer Scale Register TSCALE • Core Timer Count Register TCOUNT • Core Timer Period Register TPERIOD • Core Time Control Register TCNTL 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 16

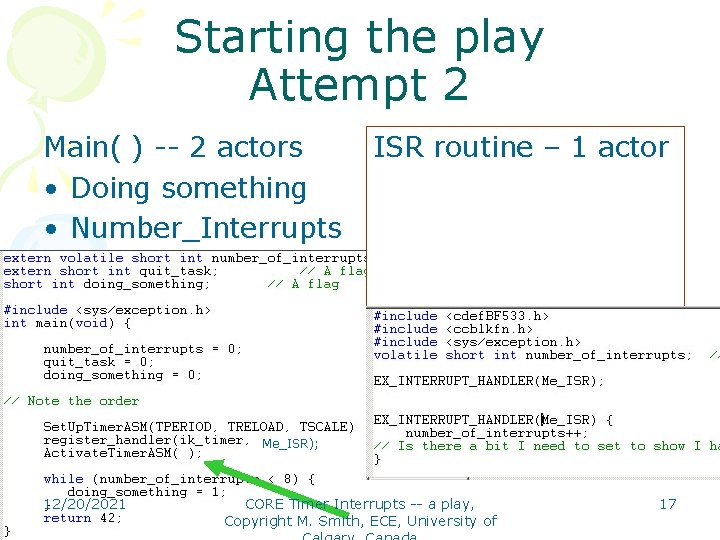

Starting the play Attempt 2 Main( ) -- 2 actors • Doing something • Number_Interrupts ISR routine – 1 actor Me_ISR); 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 17

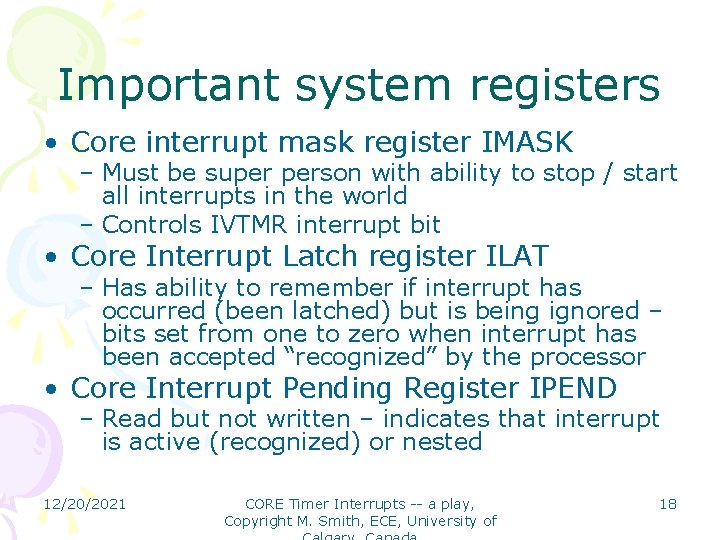

Important system registers • Core interrupt mask register IMASK – Must be super person with ability to stop / start all interrupts in the world – Controls IVTMR interrupt bit • Core Interrupt Latch register ILAT – Has ability to remember if interrupt has occurred (been latched) but is being ignored – bits set from one to zero when interrupt has been accepted “recognized” by the processor • Core Interrupt Pending Register IPEND – Read but not written – indicates that interrupt is active (recognized) or nested 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 18

Now we need to add the actors Timer – 4 parts • Core Timer Scale Register TSCALE • Core Timer Count Register TCOUNT • Core Timer Period Register TPERIOD • Core Time Control Register TCNTL 12/20/2021 CORE SYSTEM REGISTERS – 1 person with many hands • Core interrupt mask register IMASK • Core Interrupt Latch register ILAT • Core Interrupt Pending Register IPEND CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 19

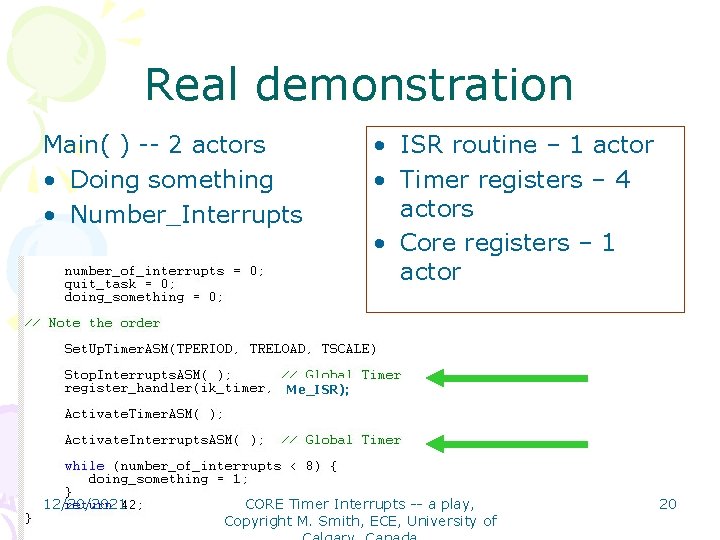

Real demonstration Main( ) -- 2 actors • Doing something • Number_Interrupts • ISR routine – 1 actor • Timer registers – 4 actors • Core registers – 1 actor Me_ISR); 12/20/2021 CORE Timer Interrupts -- a play, Copyright M. Smith, ECE, University of 20

- Slides: 20