A new concept to use 3 D vertical

![Fischer Tree (Mephisto Logic) � P. Fischer introduced the Mephisto readout architecture [1]. � Fischer Tree (Mephisto Logic) � P. Fischer introduced the Mephisto readout architecture [1]. �](https://slidetodoc.com/presentation_image_h/065a20f32f8291753a301cce337c8fe9/image-35.jpg)

- Slides: 36

A new concept to use 3 D vertical integration technology for fast pattern recognition Ted Liu, Jim Hoff, Grzegorz Deptuch, Ray Yarema Fermilab Questions or Comments: jimhoff@fnal. gov

Introduction and Outline �The development of 3 D technology for the solution of the fast pattern recognition problem is part of a broader, ongoing R&D effort that includes both 2 D and 3 D solutions. �This talk will cover: ◦ An introduction to the problem ◦ A description of the Associative Memory solution ◦ A new concept – VIPRAM – that uses emerging 3 D technology

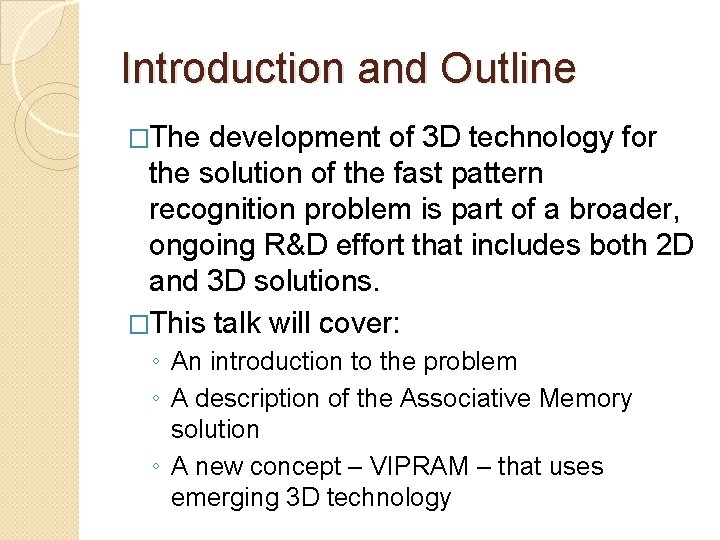

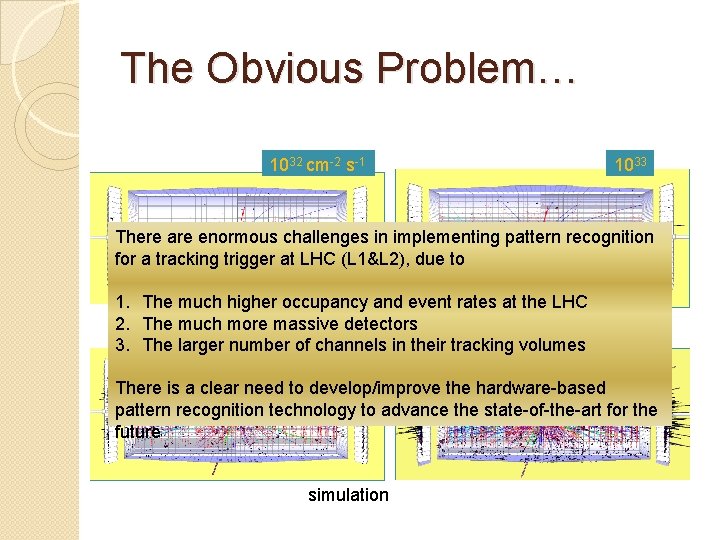

The Obvious Problem… 1032 cm-2 s-1 1033 There are enormous challenges in implementing pattern recognition for a tracking trigger at LHC (L 1&L 2), due to 1. The much higher occupancy and event rates at the LHC 2. The much more massive detectors 34 3. The larger number of 10 channels in their tracking volumes 1035 There is a clear need to develop/improve the hardware-based pattern recognition technology to advance the state-of-the-art for the future simulation

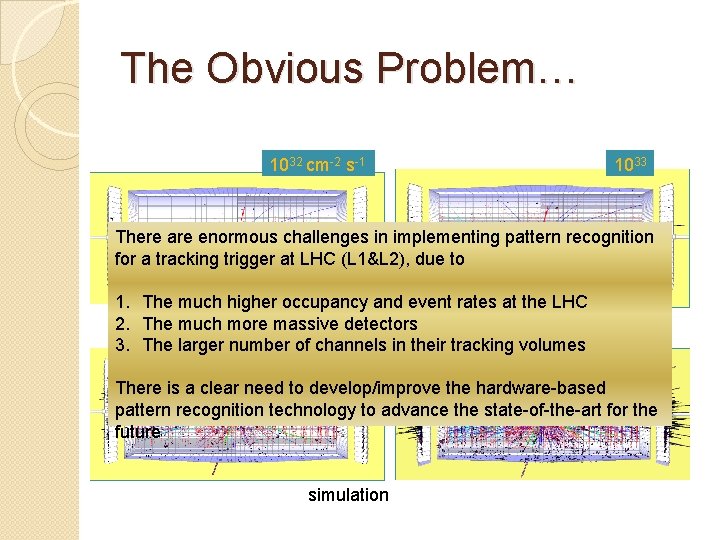

The Challenges To increase the patterns density by 3 orders of magnitude (from the original AMchips) and increase the speed by more than a factor of 3 while reducing power consumption (or at least dramatically reducing the rate of increase of power consumption)1. [1] Based on the extensive simulation studies by Atlas FTK Collaboration

Some Obvious Questions… �Can’t we just use what we currently have and just make bigger PC boards or more of them? ◦ No. This results in severe speed bottlenecks and power issues. �Can’t we just use commercial CAMs? ◦ No. CAMs are part of the fast pattern recognition process, but not all of it. Alone, CAMs lack certain necessary features, making them unsuitable for fast track triggering.

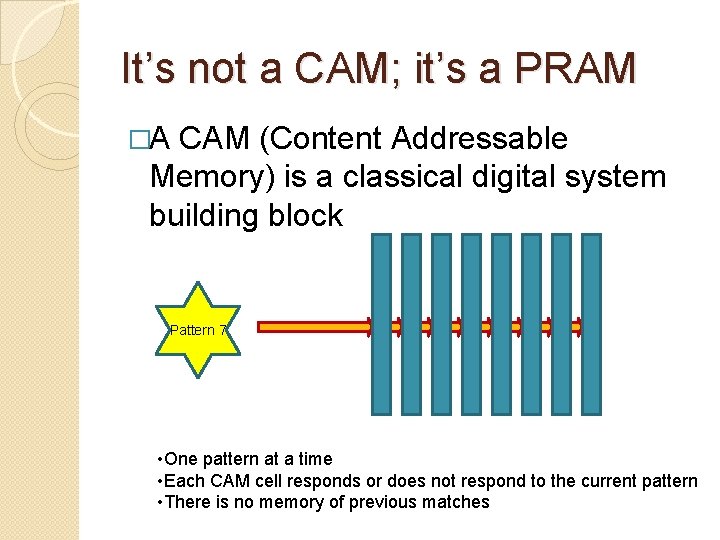

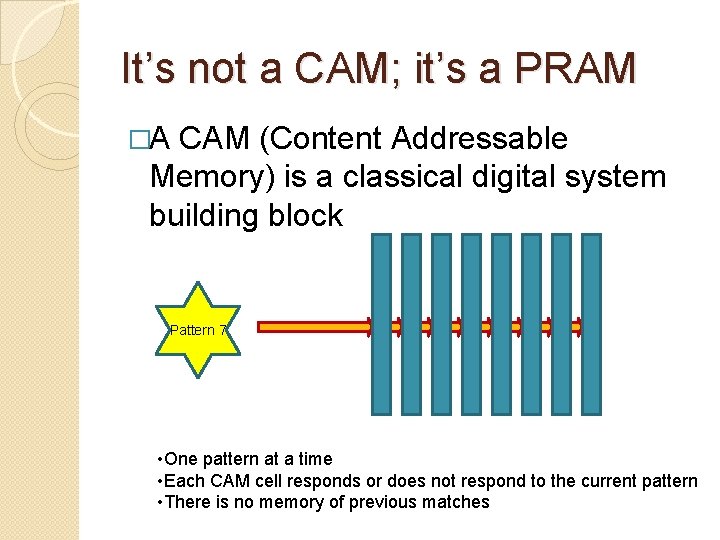

It’s not a CAM; it’s a PRAM Match Pattern 7 1 3 Match CAM (Content Addressable Memory) is a classical digital system building block Match �A • One pattern at a time • Each CAM cell responds or does not respond to the current pattern • There is no memory of previous matches

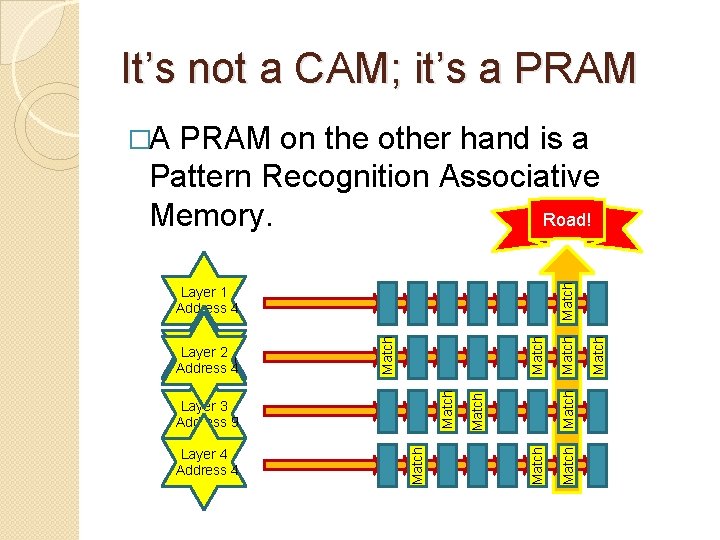

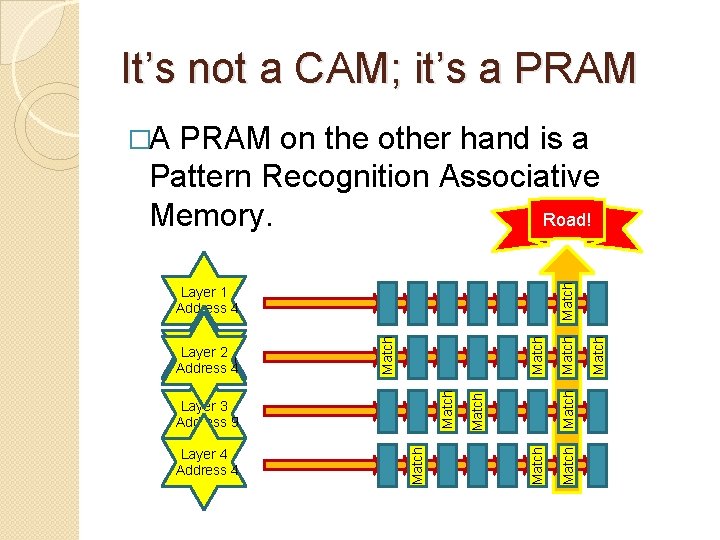

It’s not a CAM; it’s a PRAM on the other hand is a Pattern Recognition Associative Memory. Road! Match Match Layer 4 Address 4 Match Layer 3 Address 9 7 Match Layer 2 2 Layer Address 4 1 Address Match Layer 1 Address 4 Match �A

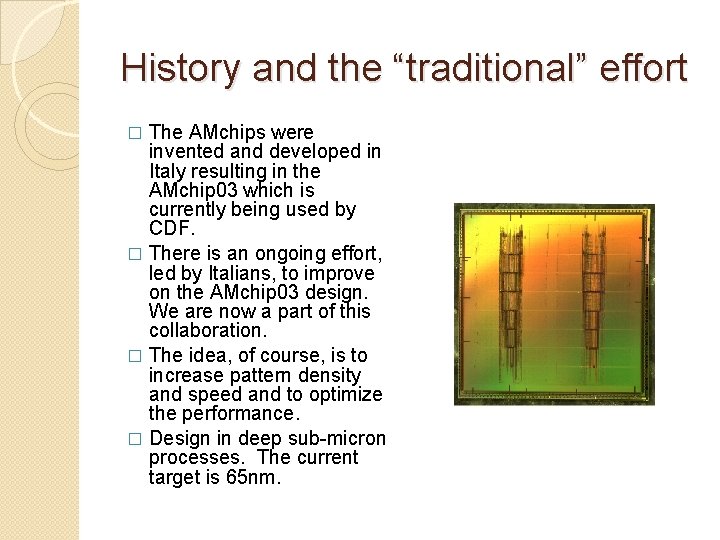

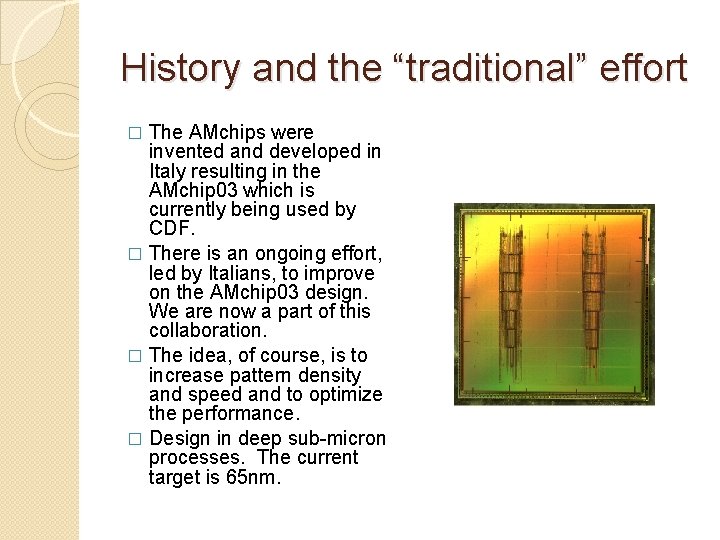

History and the “traditional” effort The AMchips were invented and developed in Italy resulting in the AMchip 03 which is currently being used by CDF. � There is an ongoing effort, led by Italians, to improve on the AMchip 03 design. We are now a part of this collaboration. � The idea, of course, is to increase pattern density and speed and to optimize the performance. � Design in deep sub-micron processes. The current target is 65 nm. �

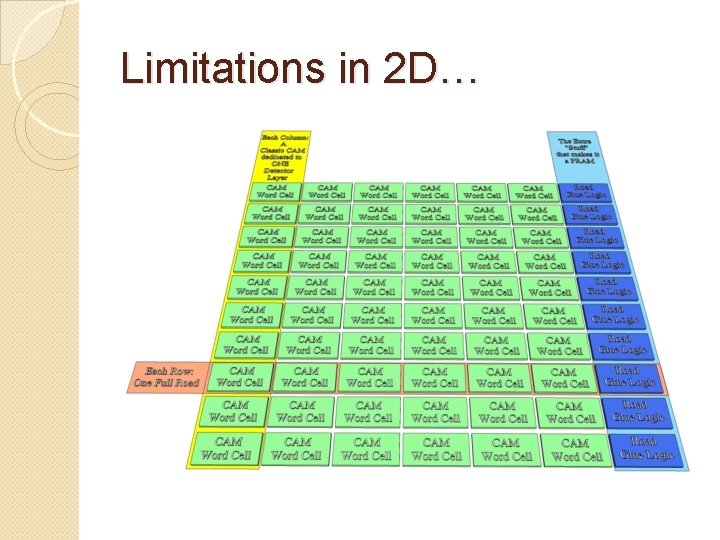

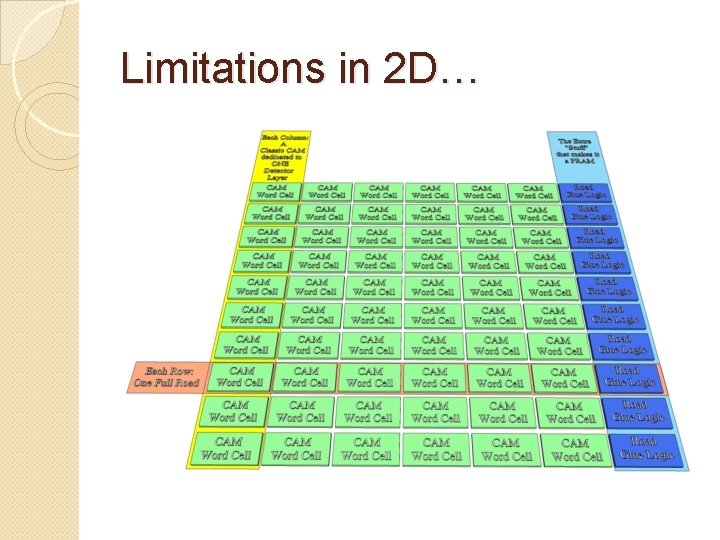

Limitations in 2 D…

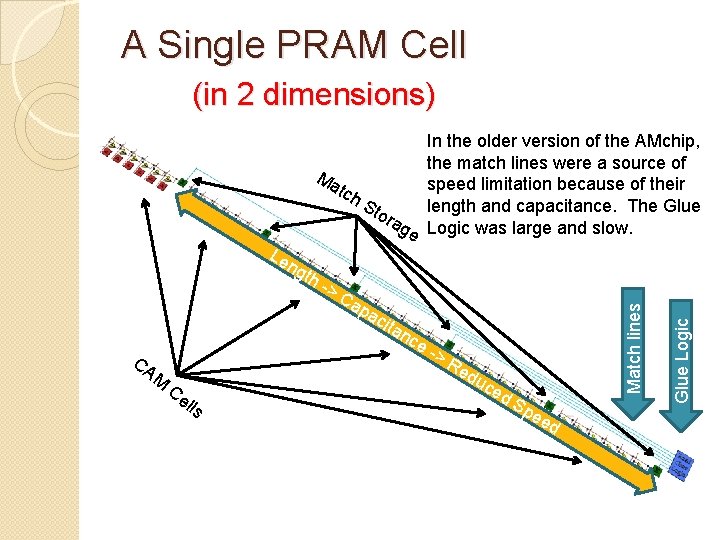

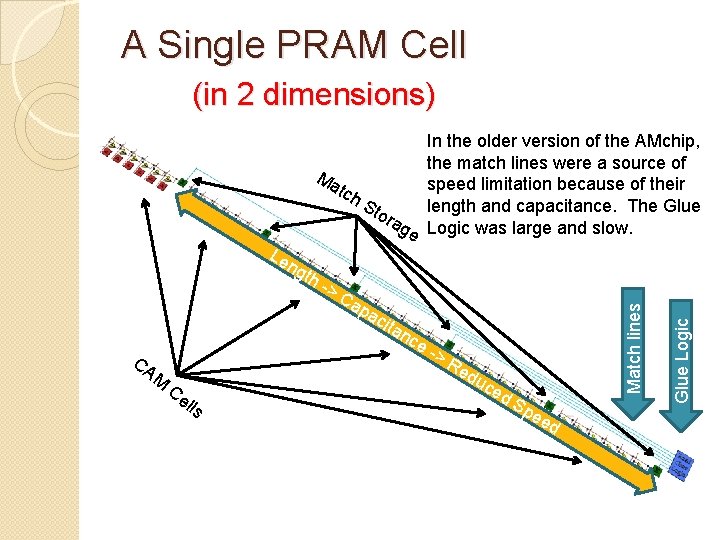

A Single PRAM Cell (in 2 dimensions) th -> C ap ac ita CA M Ce lls nc Match lines Le ng e>R ed uc ed Sp ee d Glue Logic In the older version of the AMchip, the match lines were a source of Ma speed limitation because of their tch Sto length and capacitance. The Glue rag e Logic was large and slow.

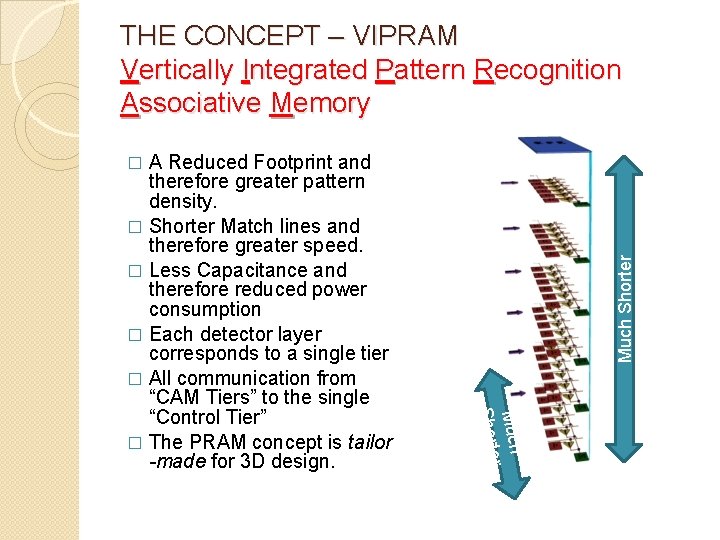

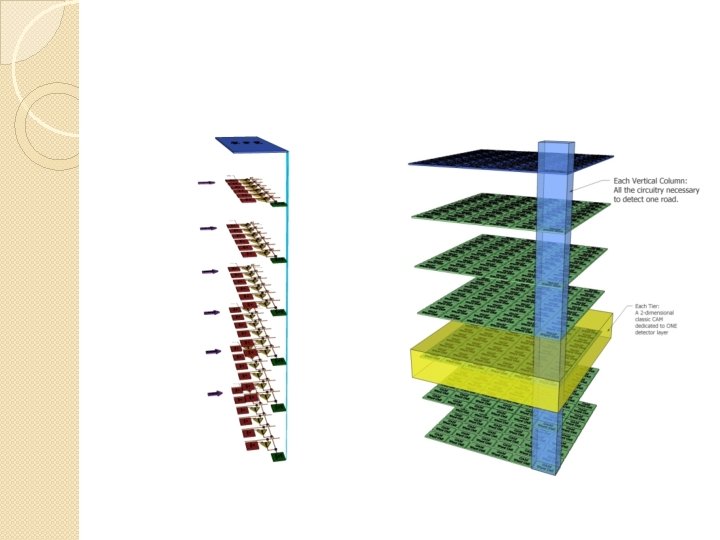

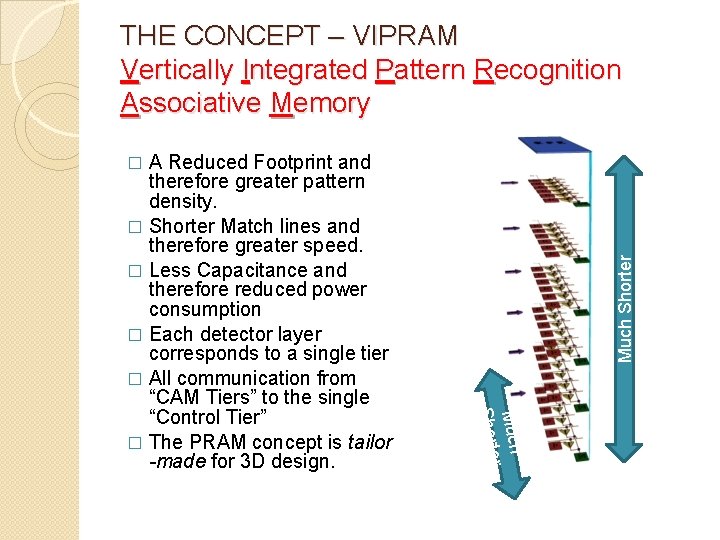

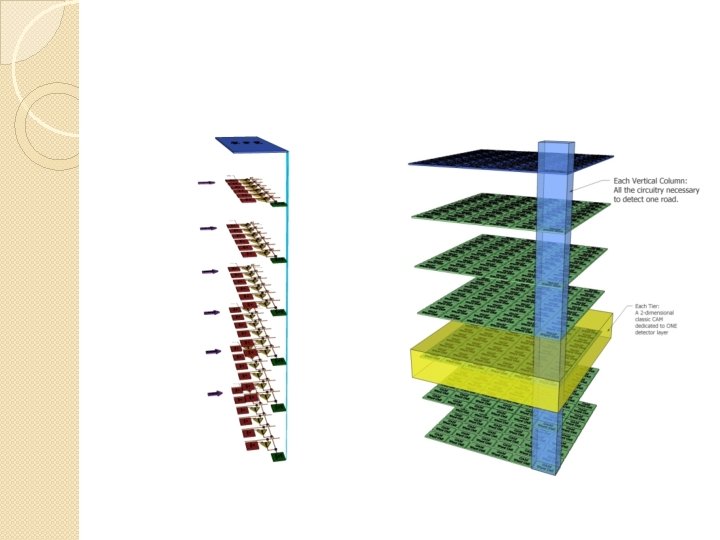

THE CONCEPT – VIPRAM Vertically Integrated Pattern Recognition Associative Memory A Reduced Footprint and therefore greater pattern density. � Shorter Match lines and therefore greater speed. � Less Capacitance and therefore reduced power consumption � Each detector layer corresponds to a single tier � All communication from “CAM Tiers” to the single “Control Tier” � The PRAM concept is tailor -made for 3 D design. Much Shorter � Much r Shorte

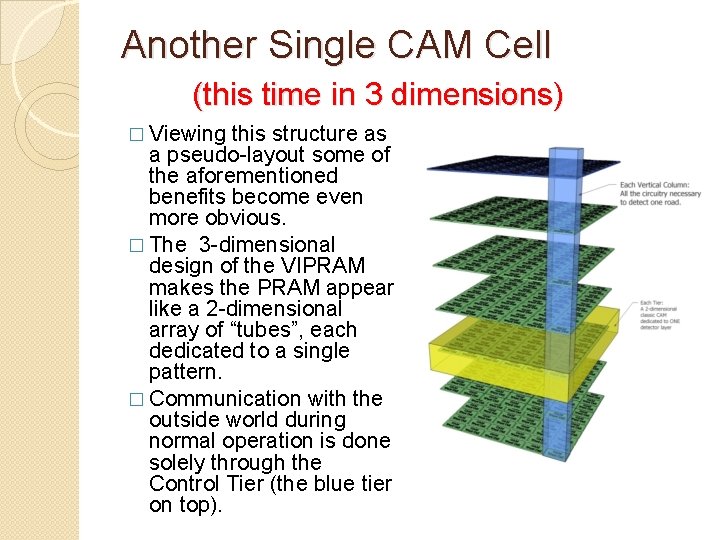

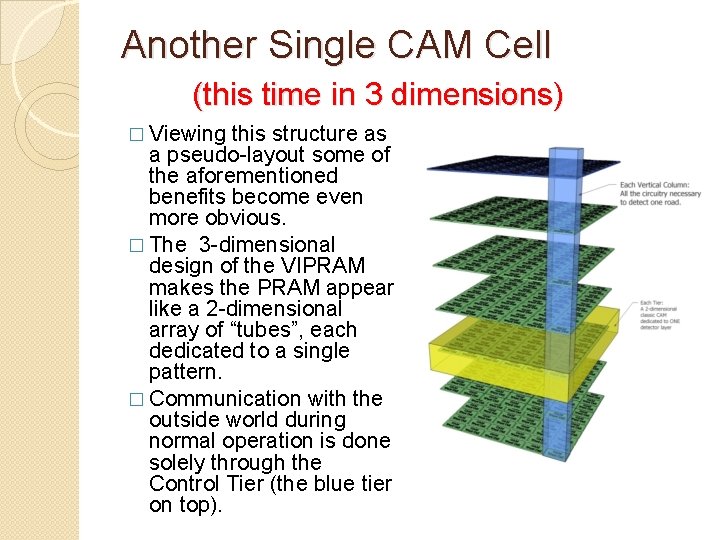

Another Single CAM Cell (this time in 3 dimensions) � Viewing this structure as a pseudo-layout some of the aforementioned benefits become even more obvious. � The 3 -dimensional design of the VIPRAM makes the PRAM appear like a 2 -dimensional array of “tubes”, each dedicated to a single pattern. � Communication with the outside world during normal operation is done solely through the Control Tier (the blue tier on top).

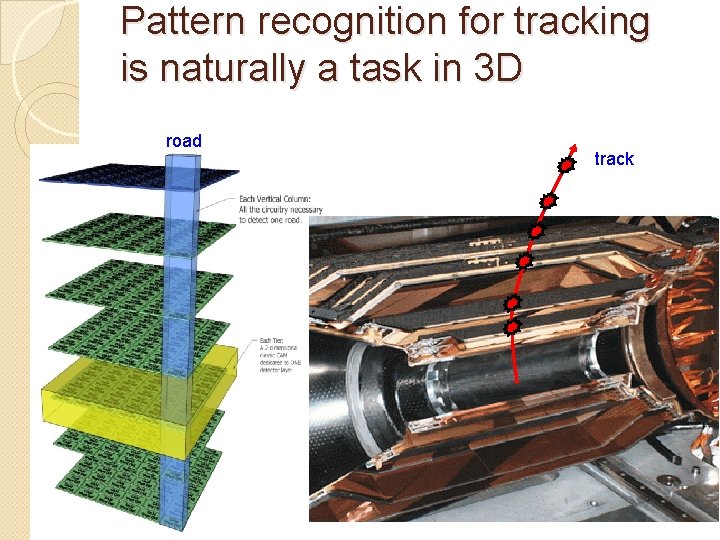

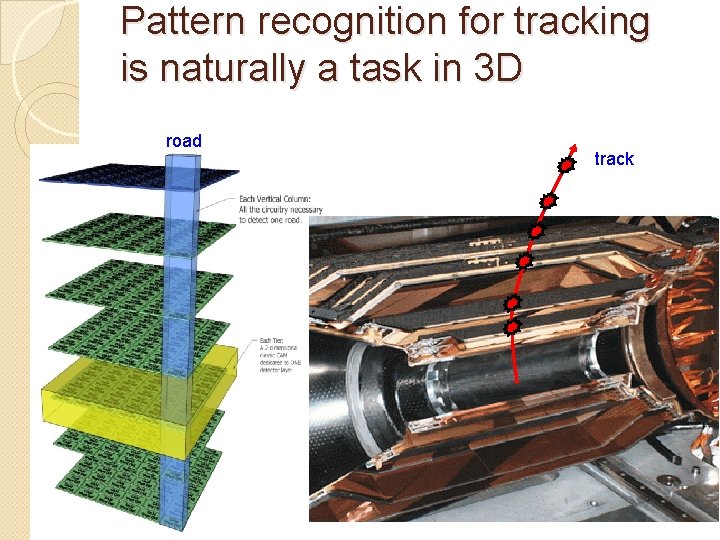

Pattern recognition for tracking is naturally a task in 3 D road track

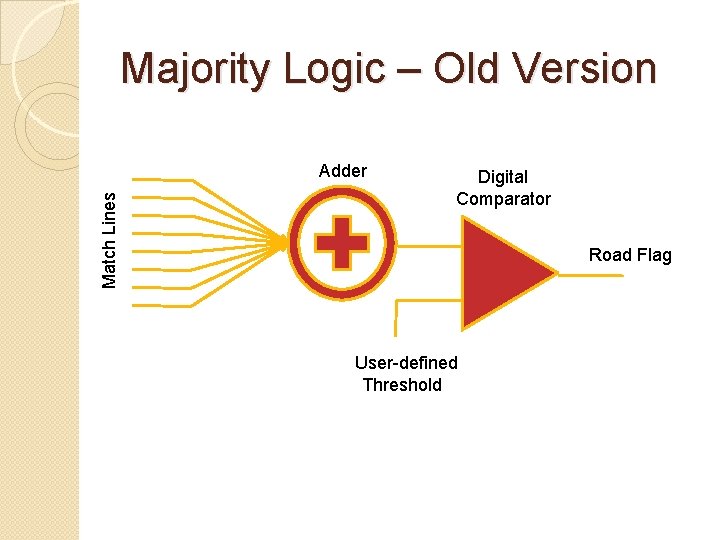

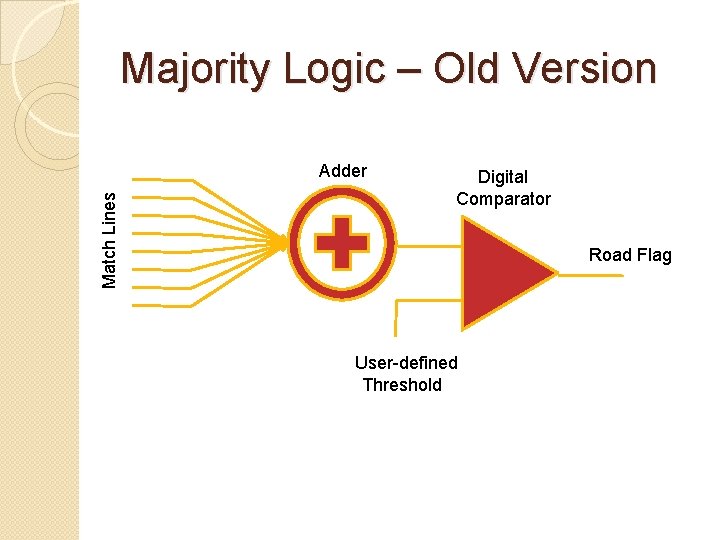

Majority Logic – Old Version Match Lines Adder Digital Comparator Road Flag User-defined Threshold

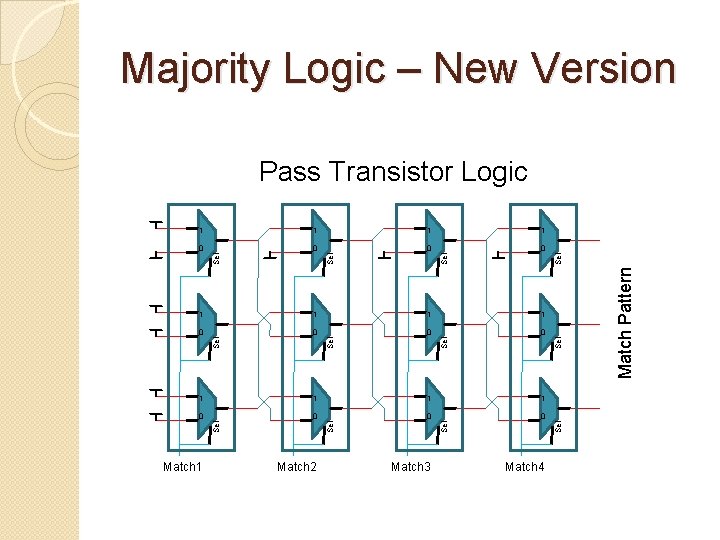

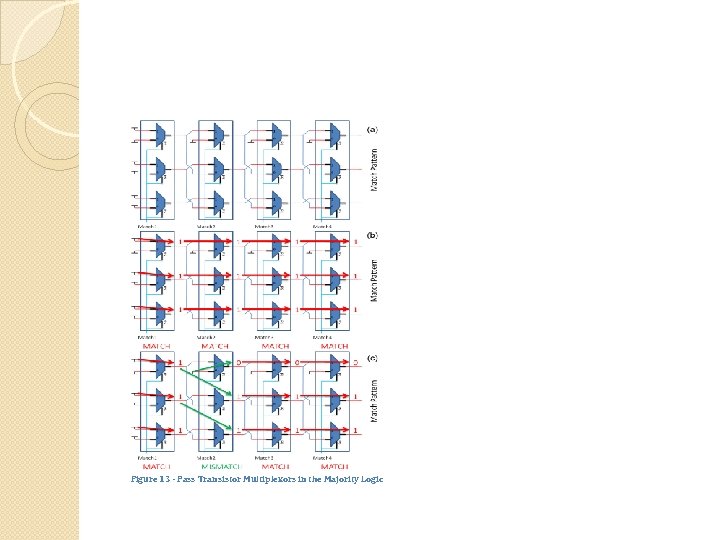

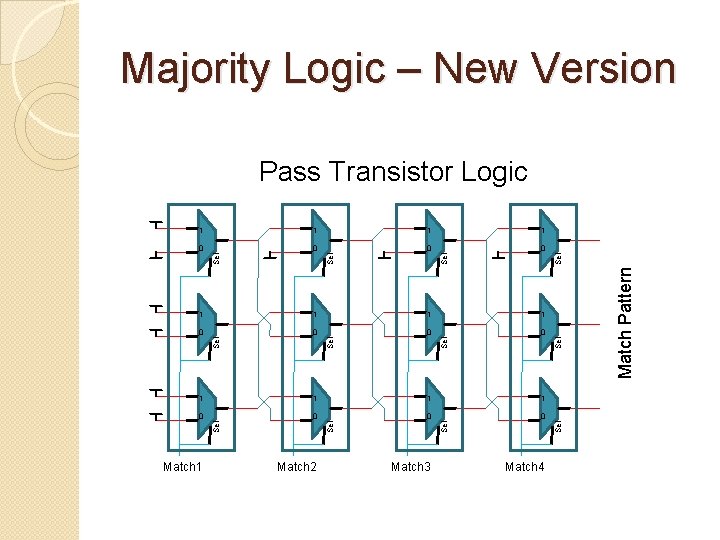

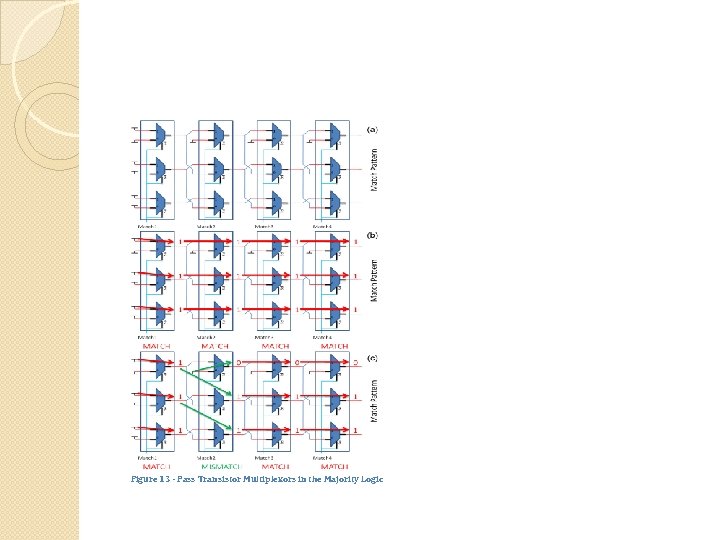

Majority Logic – New Version Pass Transistor Logic 1 0 0 1 1 0 0 Sel Sel 1 1 1 0 0 Match 1 Sel Match 2 Sel 1 Match 3 Match 4 Match Pattern Sel 1

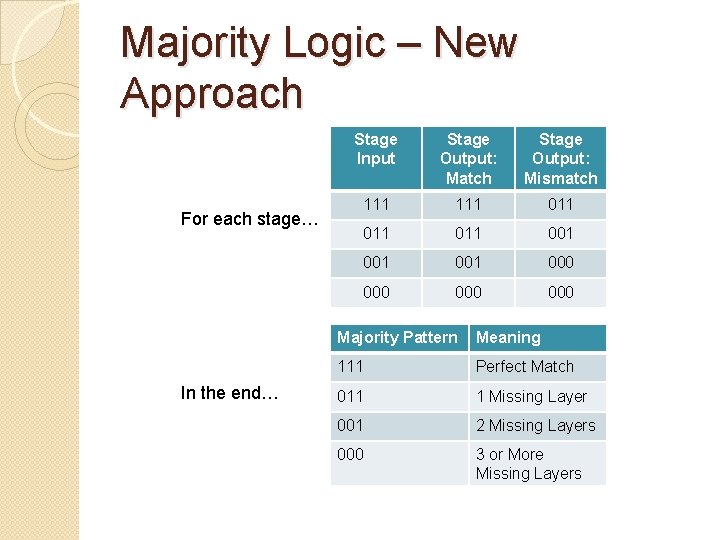

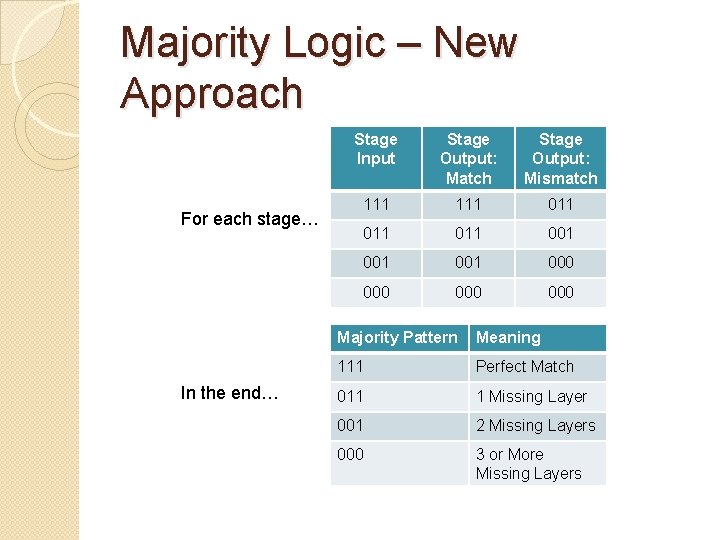

Majority Logic – New Approach For each stage… In the end… Stage Input Stage Output: Match Stage Output: Mismatch 111 011 011 001 000 000 000 Majority Pattern Meaning 111 Perfect Match 011 1 Missing Layer 001 2 Missing Layers 000 3 or More Missing Layers

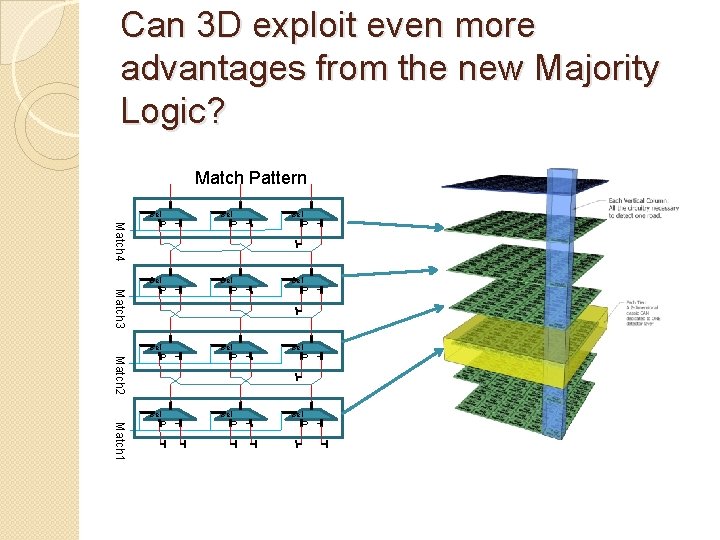

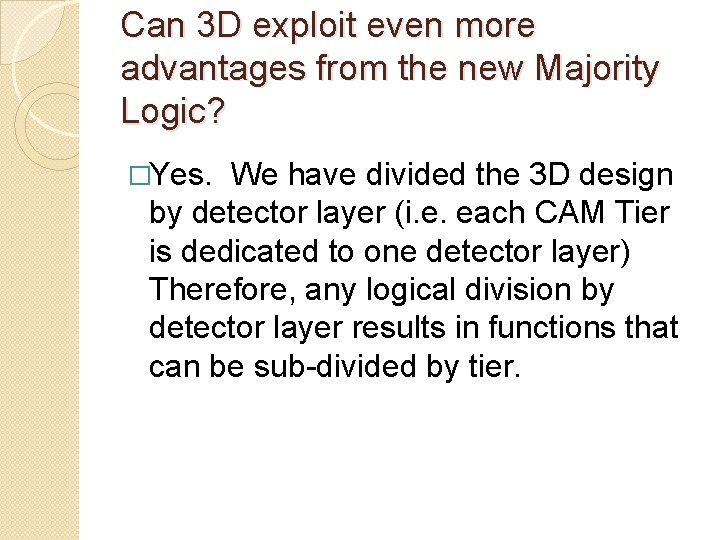

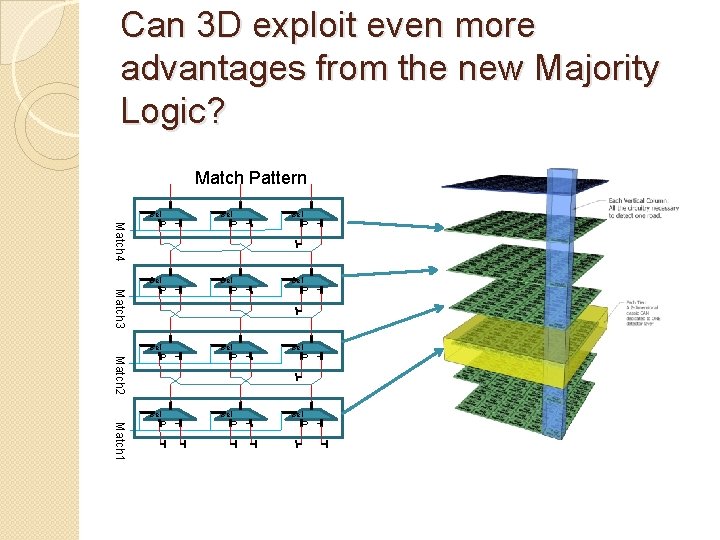

Can 3 D exploit even more advantages from the new Majority Logic? �Yes. We have divided the 3 D design by detector layer (i. e. each CAM Tier is dedicated to one detector layer) Therefore, any logical division by detector layer results in functions that can be sub-divided by tier.

Can 3 D exploit even more advantages from the new Majority Logic? Match Pattern Sel Sel 1 Sel 0 1 0 Match 2 Sel 1 Sel 0 1 0 Match 3 Sel 1 Sel 0 1 0 Match 4 Sel Sel 1 0 1 0 Match 1

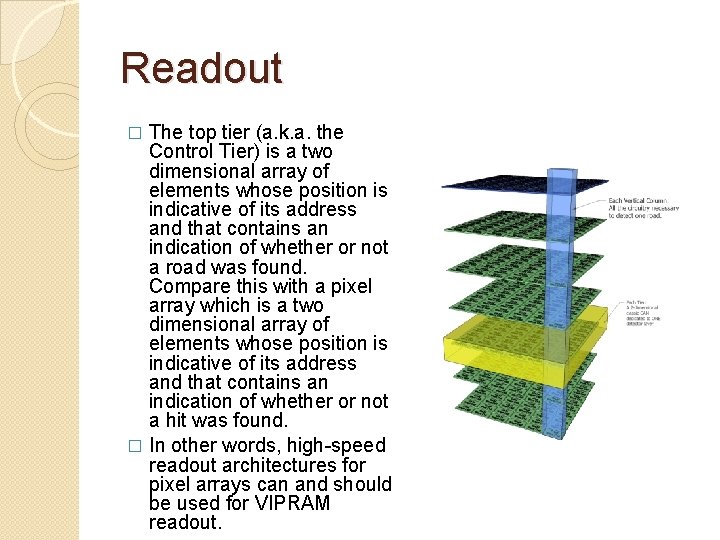

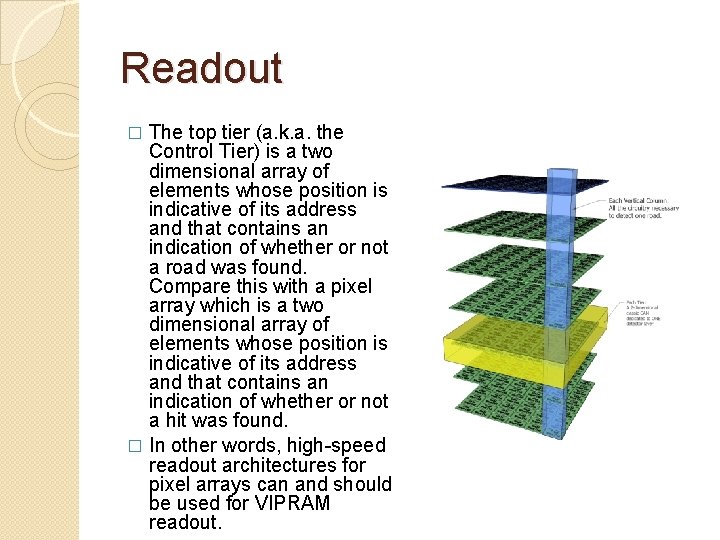

Readout The top tier (a. k. a. the Control Tier) is a two dimensional array of elements whose position is indicative of its address and that contains an indication of whether or not a road was found. Compare this with a pixel array which is a two dimensional array of elements whose position is indicative of its address and that contains an indication of whether or not a hit was found. � In other words, high-speed readout architectures for pixel arrays can and should be used for VIPRAM readout. �

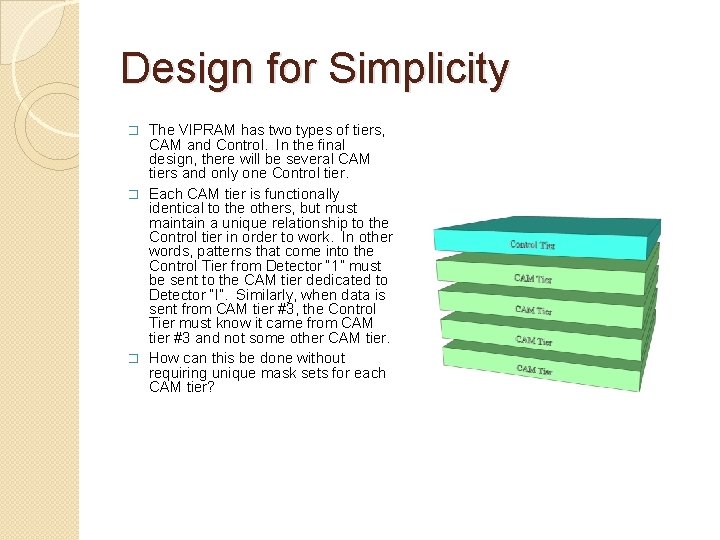

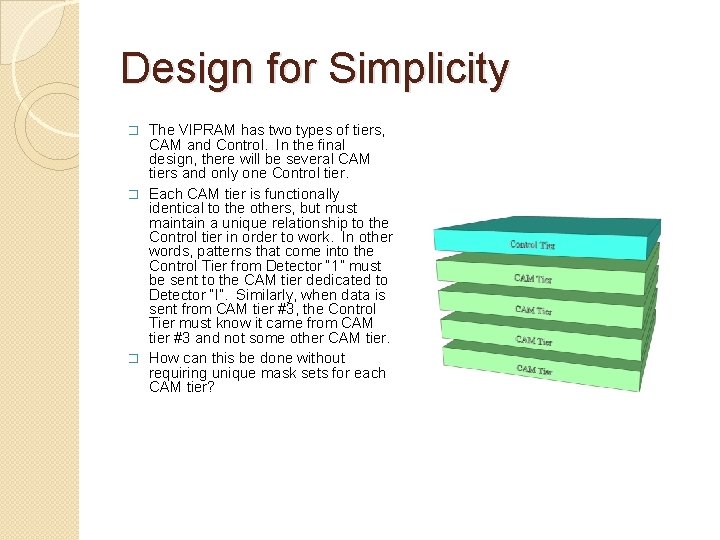

Design for Simplicity The VIPRAM has two types of tiers, CAM and Control. In the final design, there will be several CAM tiers and only one Control tier. � Each CAM tier is functionally identical to the others, but must maintain a unique relationship to the Control tier in order to work. In other words, patterns that come into the Control Tier from Detector “ 1” must be sent to the CAM tier dedicated to Detector “I”. Similarly, when data is sent from CAM tier #3, the Control Tier must know it came from CAM tier #3 and not some other CAM tier. � How can this be done without requiring unique mask sets for each CAM tier? �

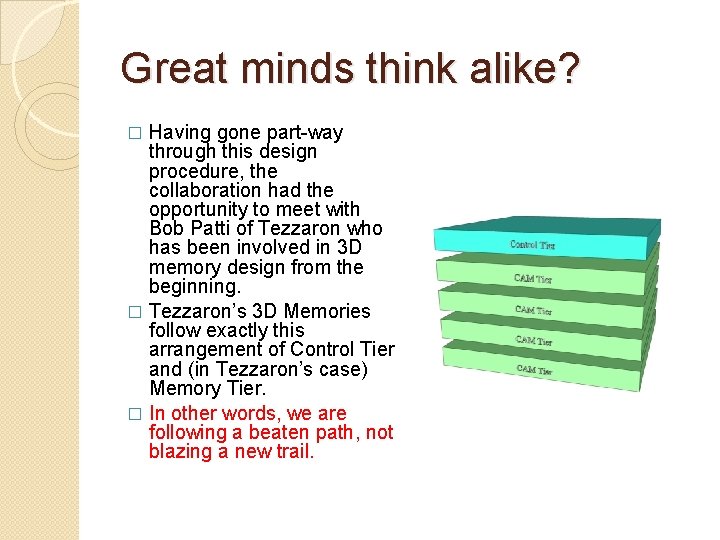

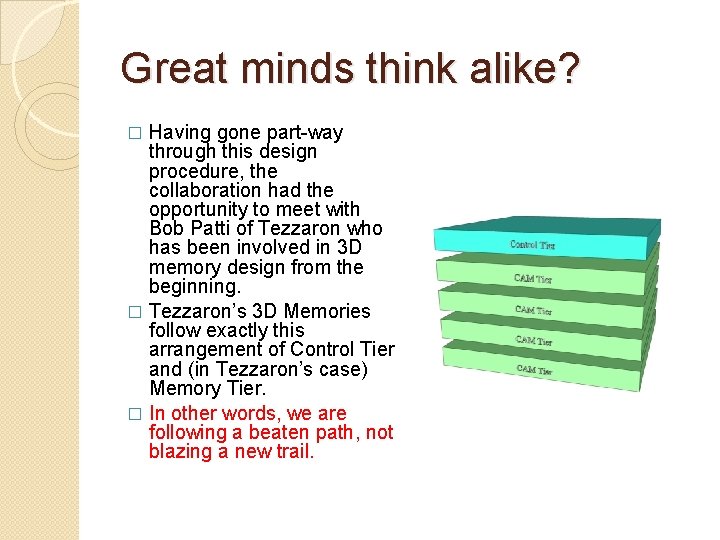

Great minds think alike? Having gone part-way through this design procedure, the collaboration had the opportunity to meet with Bob Patti of Tezzaron who has been involved in 3 D memory design from the beginning. � Tezzaron’s 3 D Memories follow exactly this arrangement of Control Tier and (in Tezzaron’s case) Memory Tier. � In other words, we are following a beaten path, not blazing a new trail. �

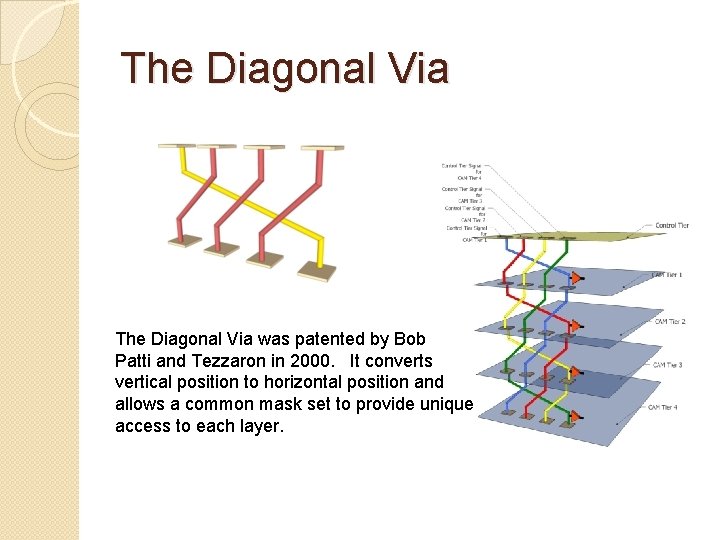

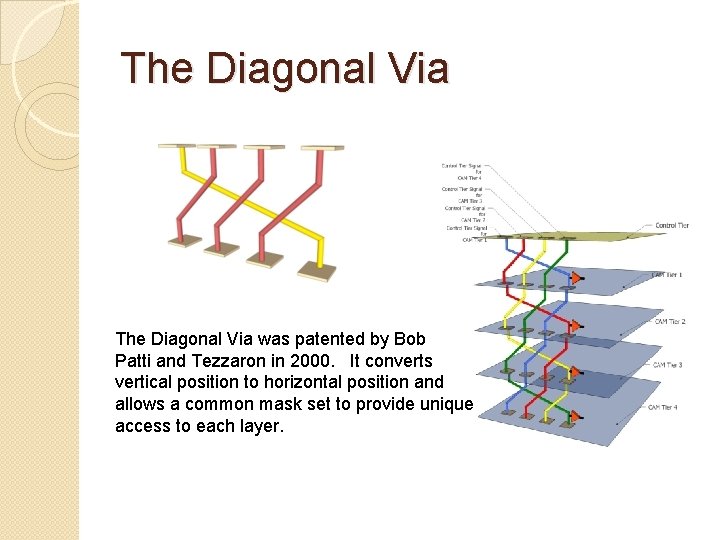

The Diagonal Via was patented by Bob Patti and Tezzaron in 2000. It converts vertical position to horizontal position and allows a common mask set to provide unique access to each layer.

Conclusions and Future Work �The VIPRAM is a new concept and now we are developing a collaboration with Fermilab, University of Chicago, INFN and Argonne. ◦ The immediate goal is a proof of principal ◦ The ultimate goal is a 3 order-of-magnitude increase in performance (density+speed). �At present, we are seeking funding for the VIPRAM development. �You will hear from us again at the next TIPP (please pick a nice place for my

Background

Figure 13 - Pass Transistor Multiplexors in the Majority Logic

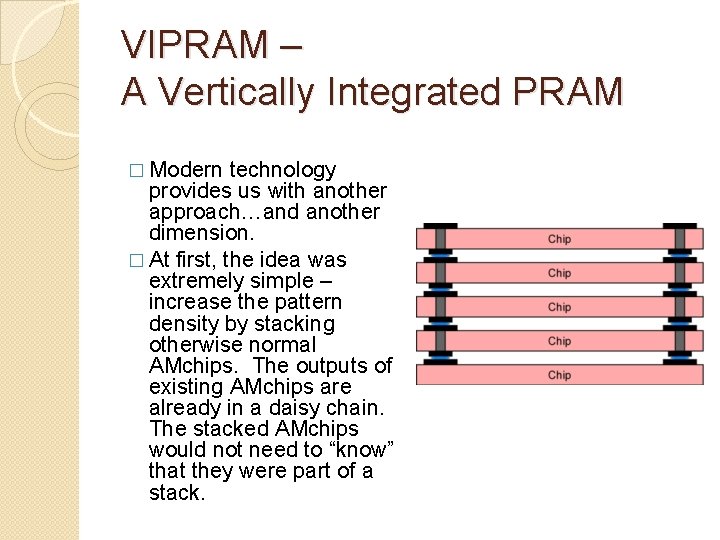

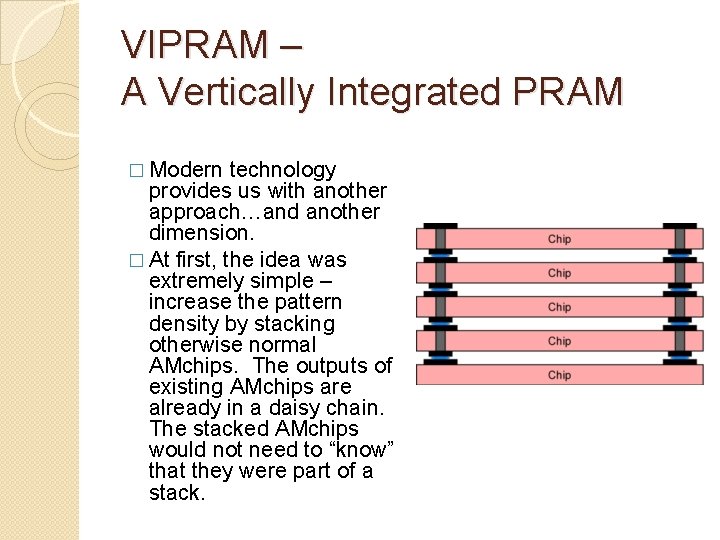

VIPRAM – A Vertically Integrated PRAM � Modern technology provides us with another approach…and another dimension. � At first, the idea was extremely simple – increase the pattern density by stacking otherwise normal AMchips. The outputs of existing AMchips are already in a daisy chain. The stacked AMchips would not need to “know” that they were part of a stack.

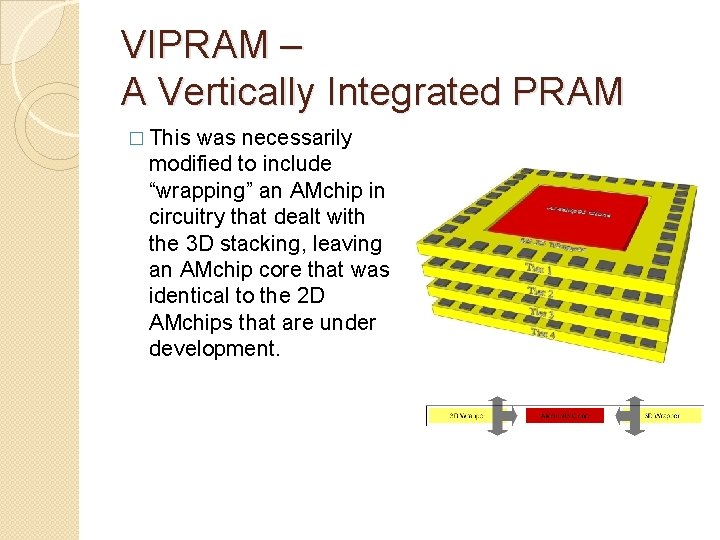

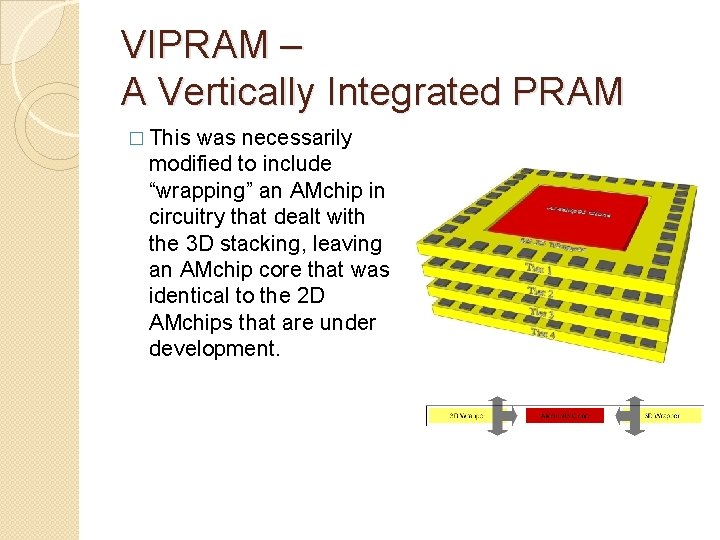

VIPRAM – A Vertically Integrated PRAM � This was necessarily modified to include “wrapping” an AMchip in circuitry that dealt with the 3 D stacking, leaving an AMchip core that was identical to the 2 D AMchips that are under development.

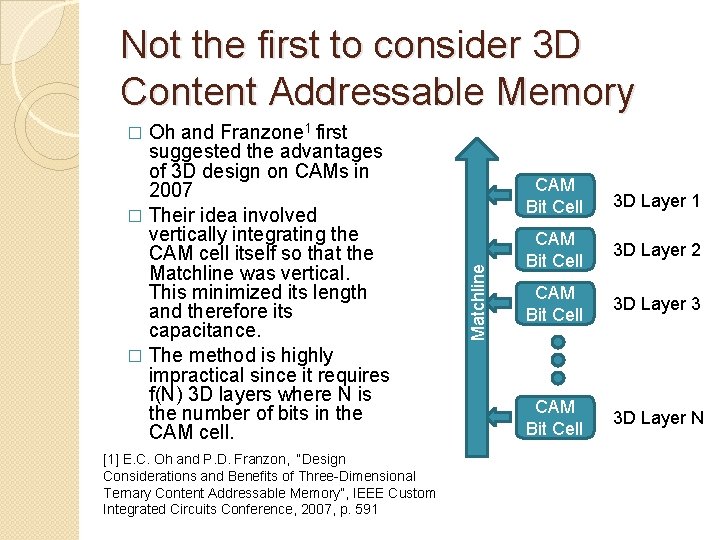

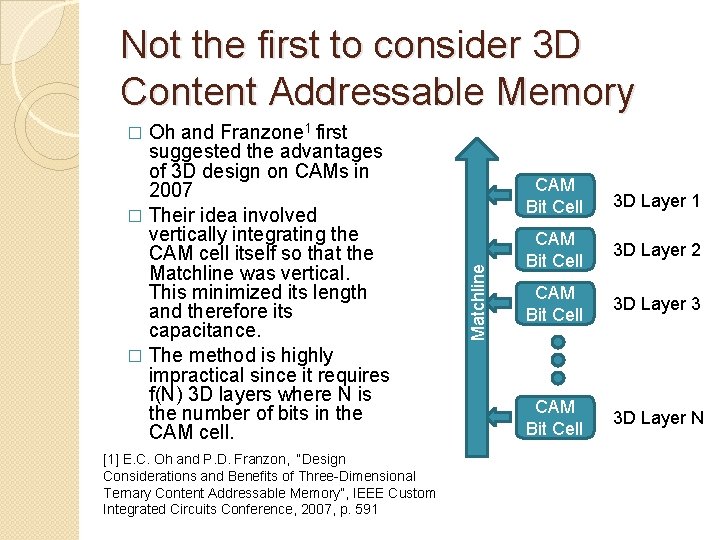

Not the first to consider 3 D Content Addressable Memory Oh and Franzone 1 first suggested the advantages of 3 D design on CAMs in 2007 � Their idea involved vertically integrating the CAM cell itself so that the Matchline was vertical. This minimized its length and therefore its capacitance. � The method is highly impractical since it requires f(N) 3 D layers where N is the number of bits in the CAM cell. [1] E. C. Oh and P. D. Franzon, “Design Considerations and Benefits of Three-Dimensional Ternary Content Addressable Memory”, IEEE Custom Integrated Circuits Conference, 2007, p. 591 Matchline � CAM Bit Cell 3 D Layer 1 CAM Bit Cell 3 D Layer 2 CAM Bit Cell 3 D Layer 3 CAM Bit Cell 3 D Layer N

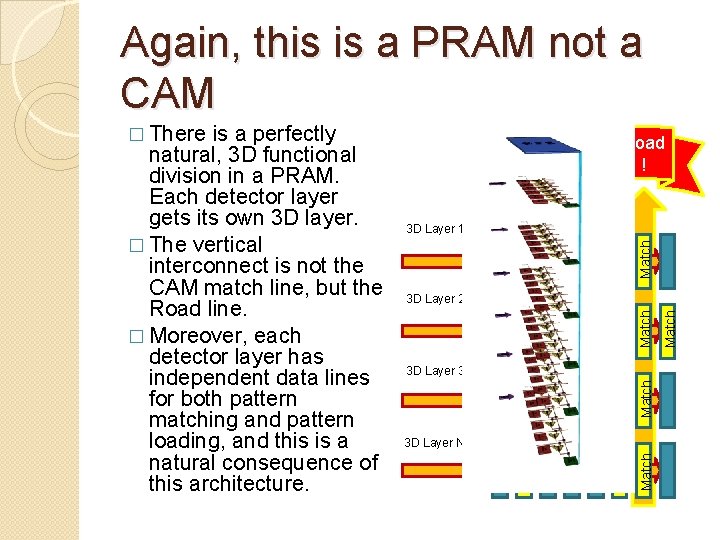

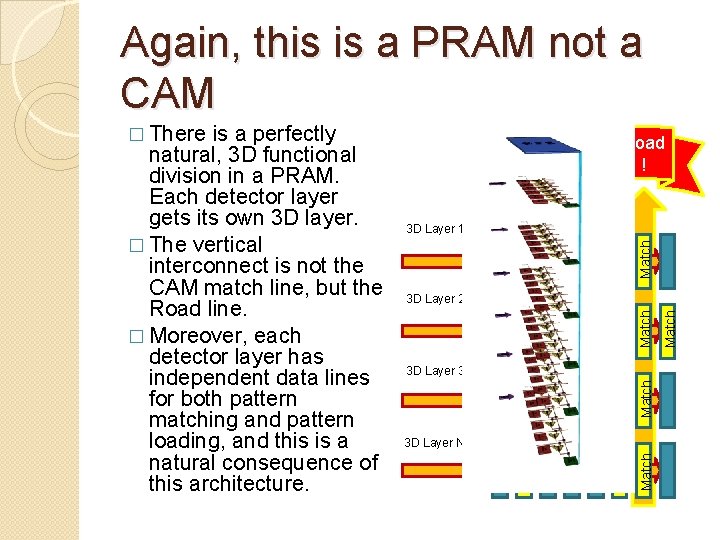

Again, this is a PRAM not a CAM � There Road ! Match 3 D Layer 1 Match Match 3 D Layer 3 Match 3 D Layer N Match 3 D Layer 2 Match is a perfectly natural, 3 D functional division in a PRAM. Each detector layer gets its own 3 D layer. � The vertical interconnect is not the CAM match line, but the Road line. � Moreover, each detector layer has independent data lines for both pattern matching and pattern loading, and this is a natural consequence of this architecture.

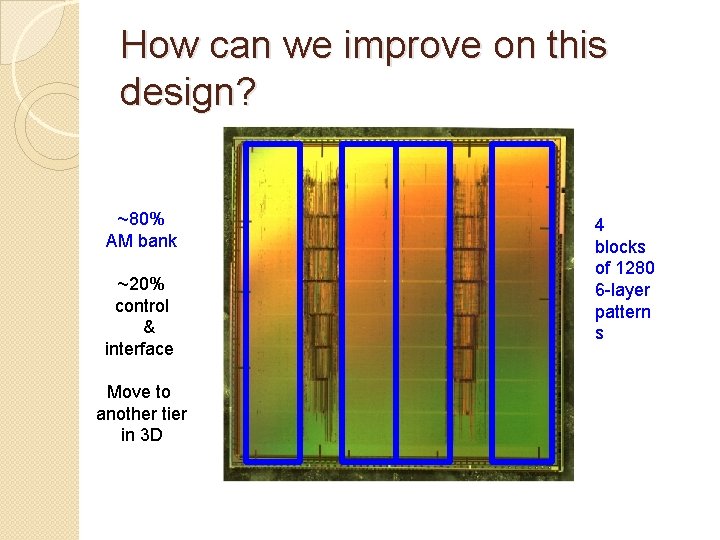

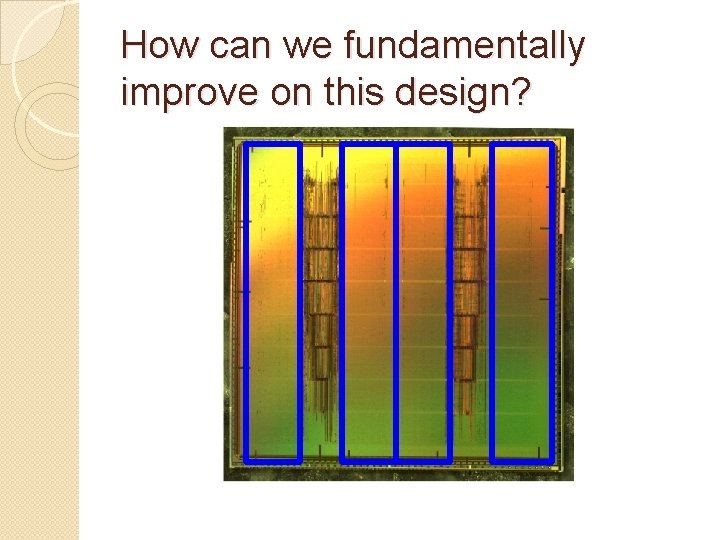

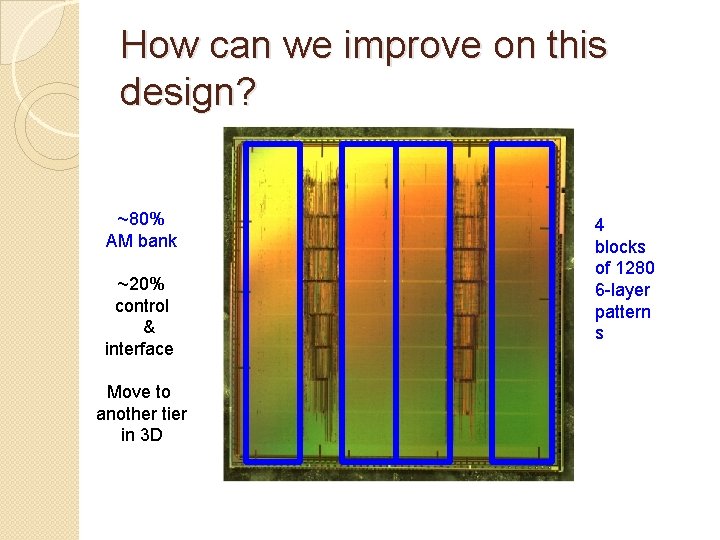

How can we improve on this design? ~80% AM bank ~20% control & interface Move to another tier in 3 D 4 blocks of 1280 6 -layer pattern s

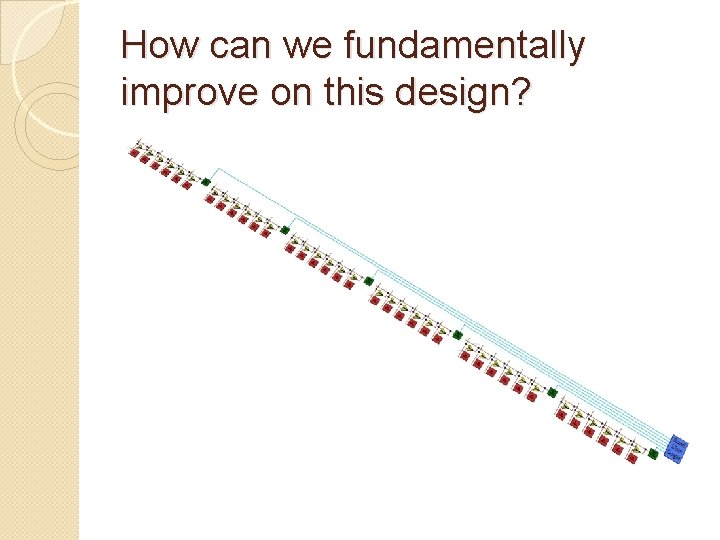

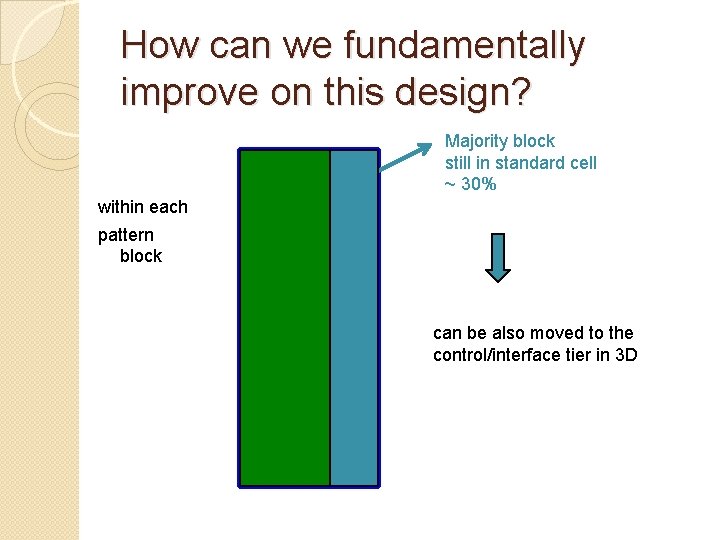

How can we fundamentally improve on this design?

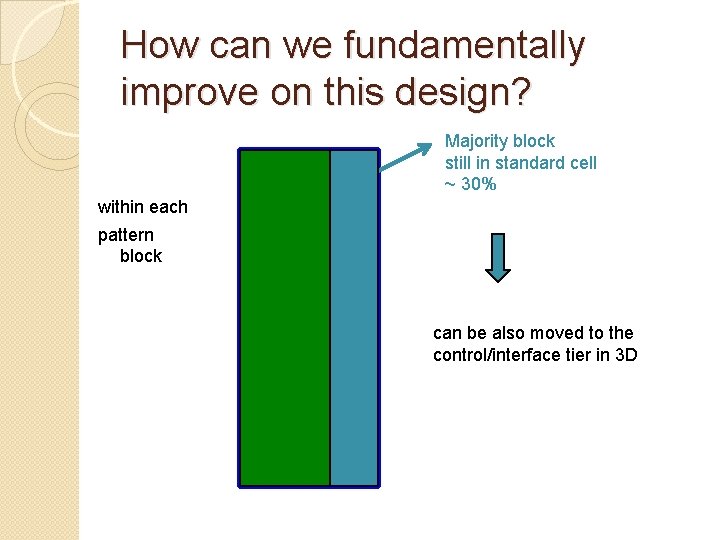

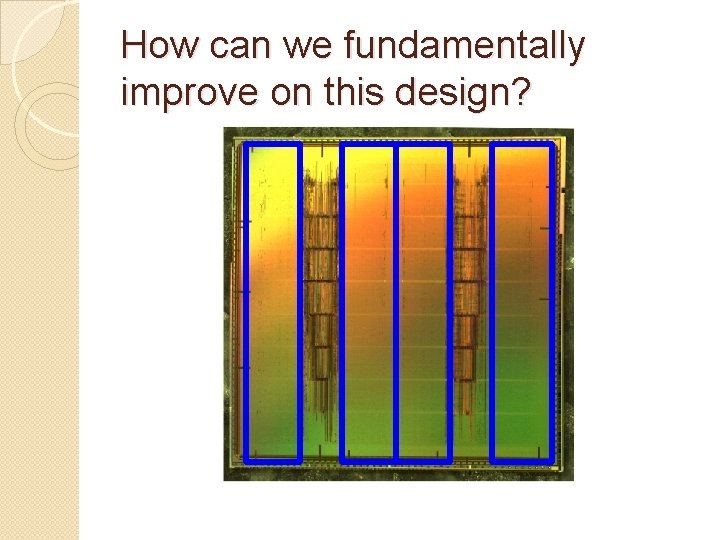

How can we fundamentally improve on this design?

How can we fundamentally improve on this design? Majority block still in standard cell ~ 30% within each pattern block can be also moved to the control/interface tier in 3 D

![Fischer Tree Mephisto Logic P Fischer introduced the Mephisto readout architecture 1 Fischer Tree (Mephisto Logic) � P. Fischer introduced the Mephisto readout architecture [1]. �](https://slidetodoc.com/presentation_image_h/065a20f32f8291753a301cce337c8fe9/image-35.jpg)

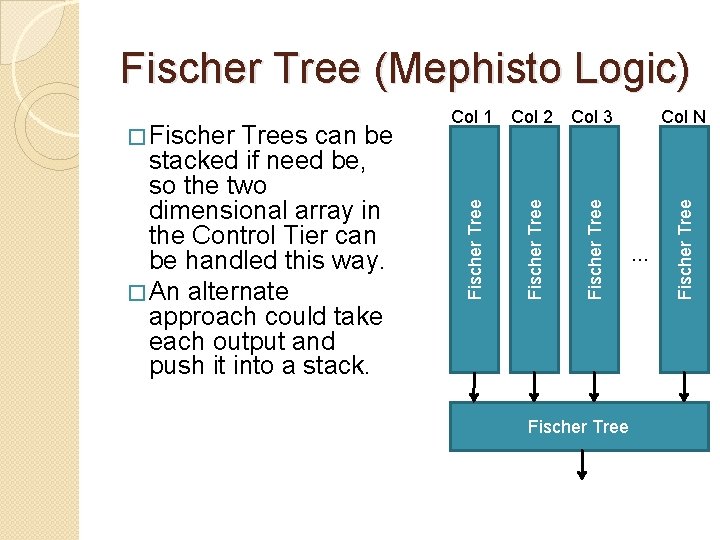

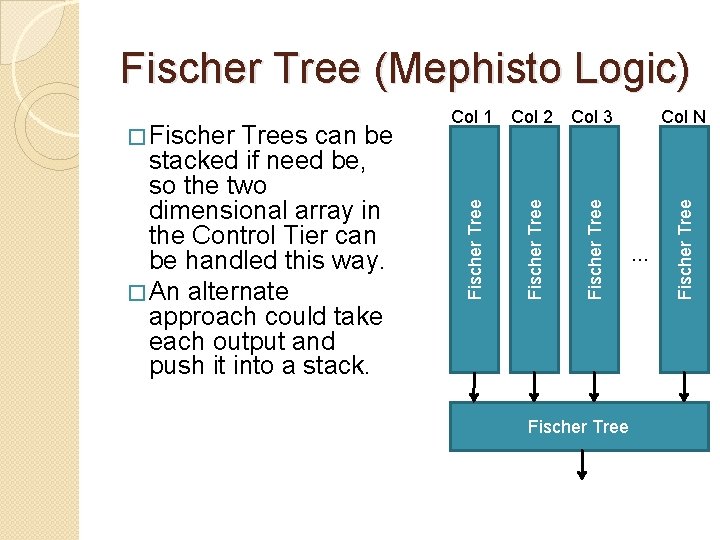

Fischer Tree (Mephisto Logic) � P. Fischer introduced the Mephisto readout architecture [1]. � We found “Fischer Tree” easier to say. � It is a self-selecting, self-addressing priority encoding architecture that performs the task in log[N] time. [1]“First implementation of the MEPHISTO binary readout architecture for strip detectors” Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment Volume 461, Issues 13, 1 April 2001, Pages 499 -504 8 th Pisa Meeting on Advanced Detectors

Fischer Tree Col N … Fischer Tree Col 3 Fischer Trees can be stacked if need be, so the two dimensional array in the Control Tier can be handled this way. � An alternate approach could take each output and push it into a stack. Col 2 Fischer Tree � Fischer Col 1 Fischer Tree (Mephisto Logic)