A MSP 430 Microcontroller with Custom Peripherals st

![Context [1] § Wireless body sensor nodes (BSN) often have microcontroller for processing § Context [1] § Wireless body sensor nodes (BSN) often have microcontroller for processing §](https://slidetodoc.com/presentation_image_h2/b6421cad674ba7a2aedd7d2752eb81d1/image-2.jpg)

![Architecture st Robu Low er Pow VLSI [2] § The most important file to Architecture st Robu Low er Pow VLSI [2] § The most important file to](https://slidetodoc.com/presentation_image_h2/b6421cad674ba7a2aedd7d2752eb81d1/image-4.jpg)

- Slides: 27

A MSP 430 Microcontroller with Custom Peripherals st Robu Low Robust er Pow LSI V Power VLSI Alicia Klinefelter Dept. of Electrical Engineering, University of Virginia May 08, 2012

![Context 1 Wireless body sensor nodes BSN often have microcontroller for processing Context [1] § Wireless body sensor nodes (BSN) often have microcontroller for processing §](https://slidetodoc.com/presentation_image_h2/b6421cad674ba7a2aedd7d2752eb81d1/image-2.jpg)

Context [1] § Wireless body sensor nodes (BSN) often have microcontroller for processing § Requires coding in custom ISA or assembly on finished chip st Robu Low er Pow VLSI § For flexible design available to C-level programmers, the MSP 430 is ideal § Problem: Accelerators not addressable! [2] 2

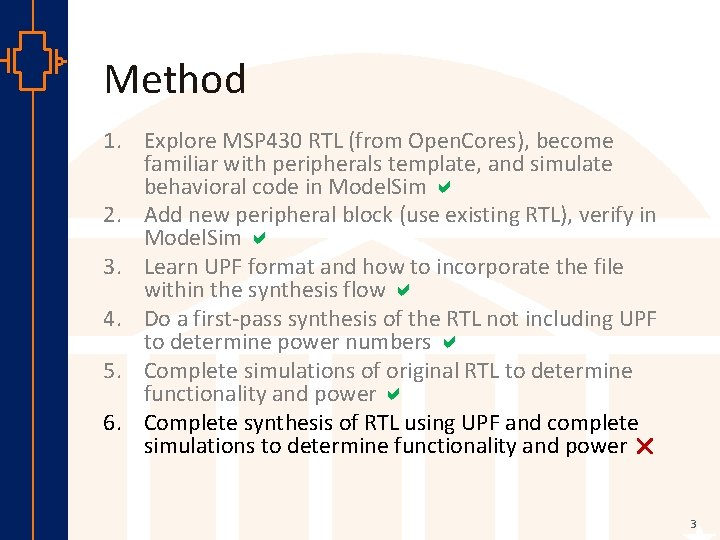

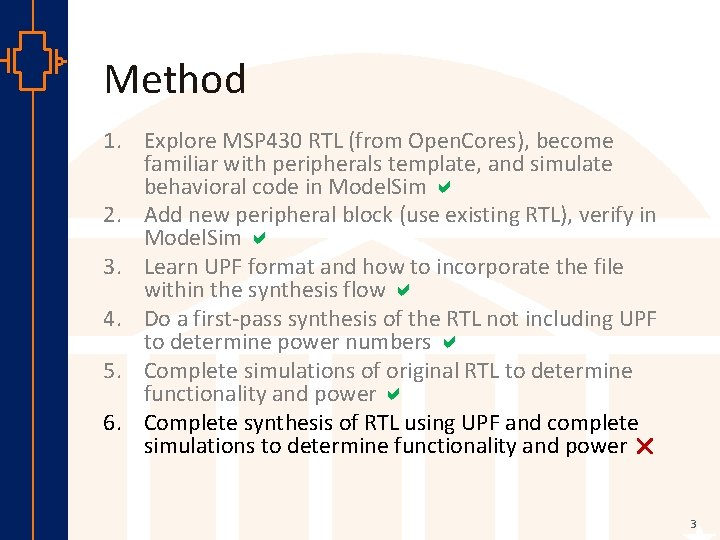

Method st Robu Low er Pow VLSI 1. Explore MSP 430 RTL (from Open. Cores), become familiar with peripherals template, and simulate behavioral code in Model. Sim a 2. Add new peripheral block (use existing RTL), verify in Model. Sim a 3. Learn UPF format and how to incorporate the file within the synthesis flow a 4. Do a first-pass synthesis of the RTL not including UPF to determine power numbers a 5. Complete simulations of original RTL to determine functionality and power a 6. Complete synthesis of RTL using UPF and complete simulations to determine functionality and power r 3

![Architecture st Robu Low er Pow VLSI 2 The most important file to Architecture st Robu Low er Pow VLSI [2] § The most important file to](https://slidetodoc.com/presentation_image_h2/b6421cad674ba7a2aedd7d2752eb81d1/image-4.jpg)

Architecture st Robu Low er Pow VLSI [2] § The most important file to edit is open. MSP 430_defines. v for setup information § The peripheral address space is assumed to be 512 B. § There are limitations to what peripherals (that are provided) can be used based on whether you plan to synthesize this for an § Within the open. MSP 430 directory taken from Open. Cores, there is a FPGA or as an ASIC. "/trunk/core/sim" directory for running behavioral simulations for § Program and data memory are all core instructions plus other test separate (can both be RAMs) features such as debugging, clocking, and peripherals. § § Run on Linux Download Icarus Verilog and GTK Wave Viewer 4

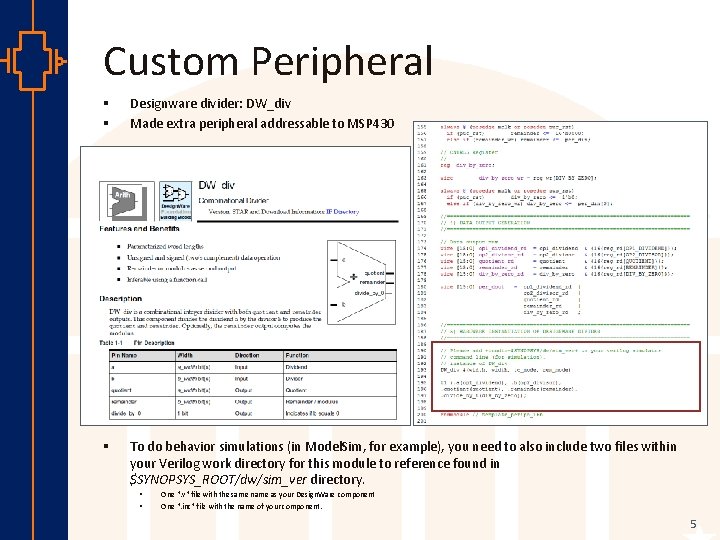

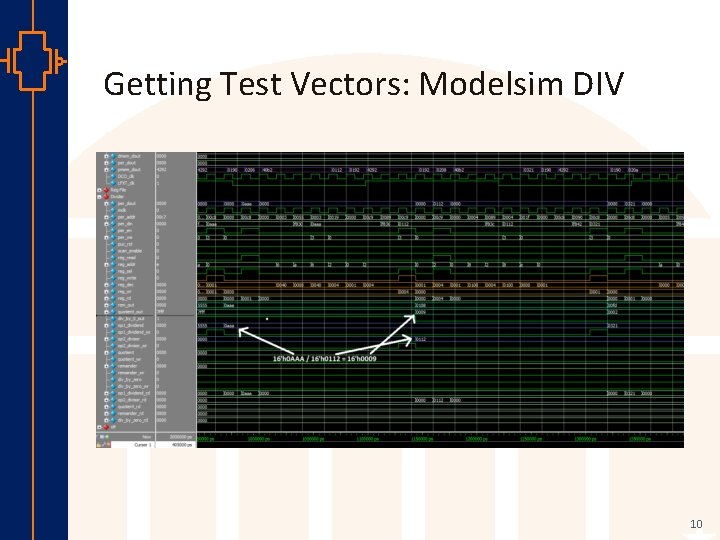

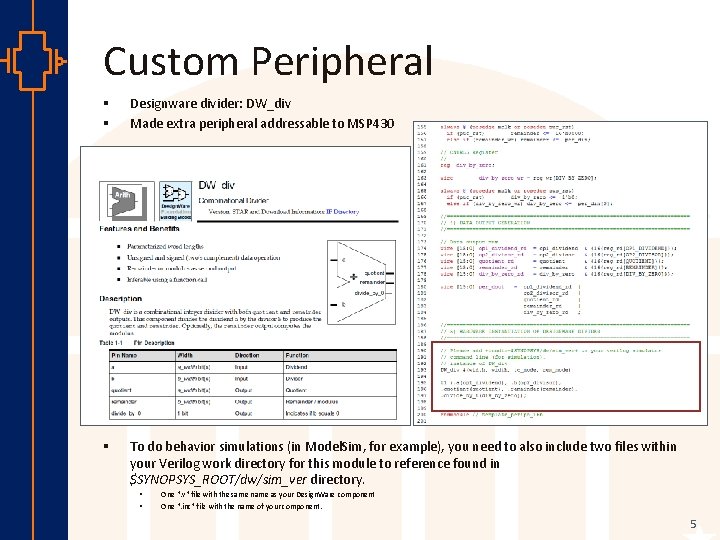

Custom Peripheral st Robu Low er Pow VLSI § § Designware divider: DW_div Made extra peripheral addressable to MSP 430 § To do behavior simulations (in Model. Sim, for example), you need to also include two files within your Verilog work directory for this module to reference found in $SYNOPSYS_ROOT/dw/sim_ver directory. § § One ". v" file with the same name as your Design. Ware component One ". inc" file with the name of your component. 5

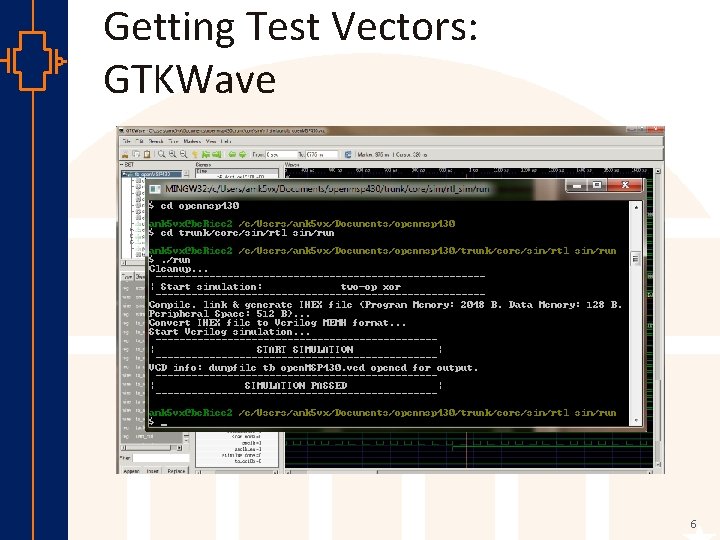

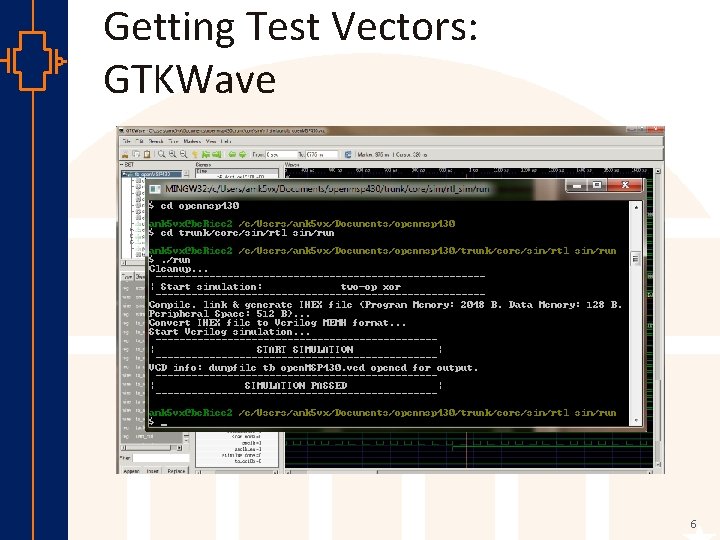

Getting Test Vectors: GTKWave st Robu Low er Pow VLSI 6

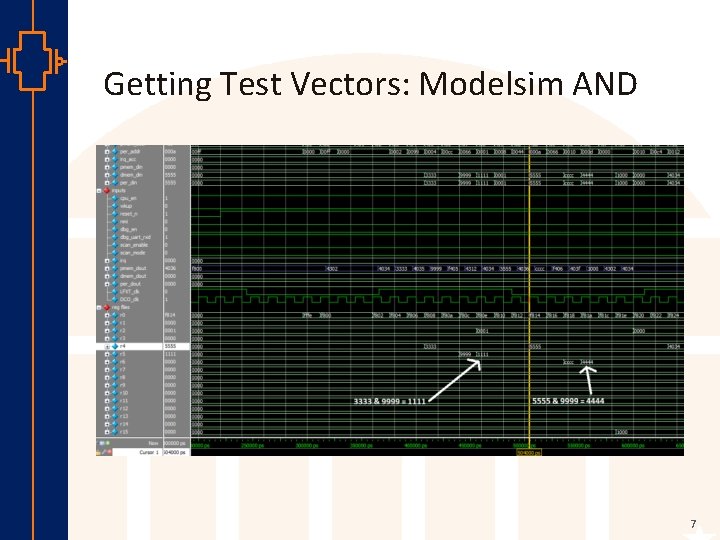

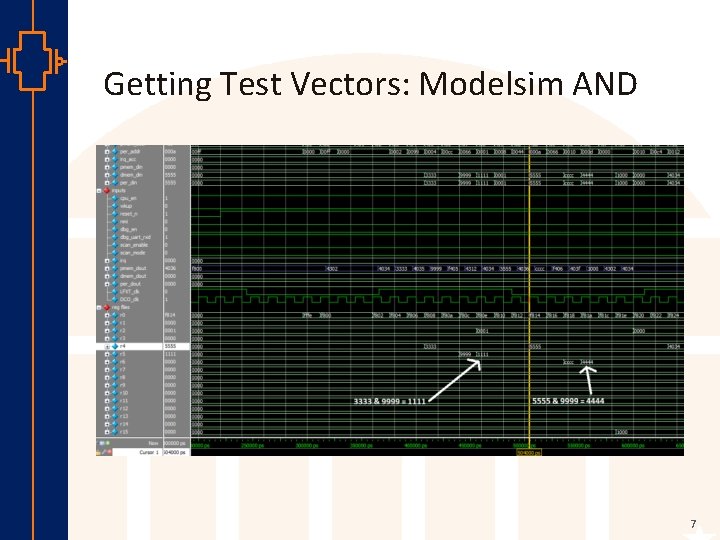

Getting Test Vectors: Modelsim AND st Robu Low er Pow VLSI 7

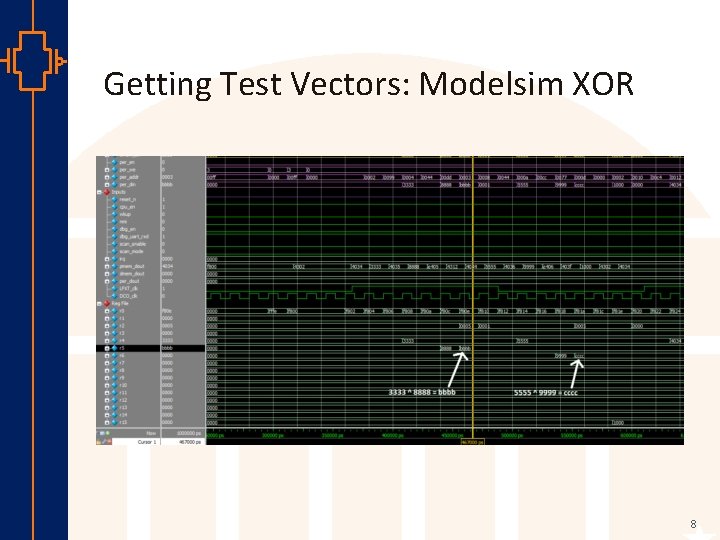

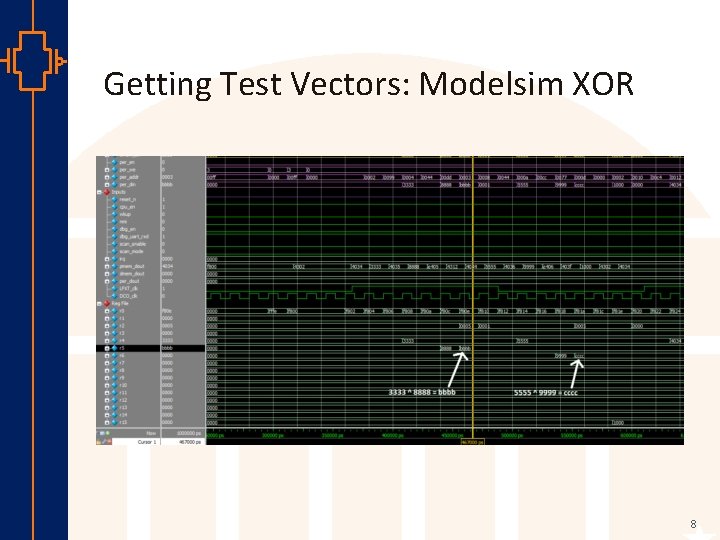

Getting Test Vectors: Modelsim XOR st Robu Low er Pow VLSI 8

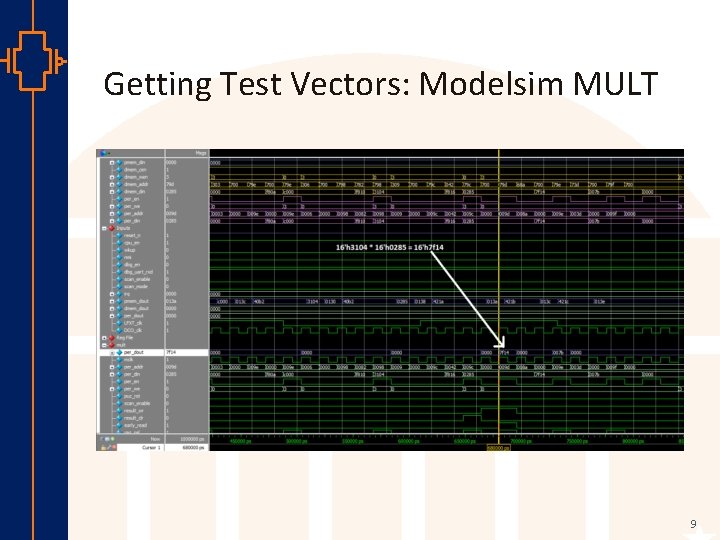

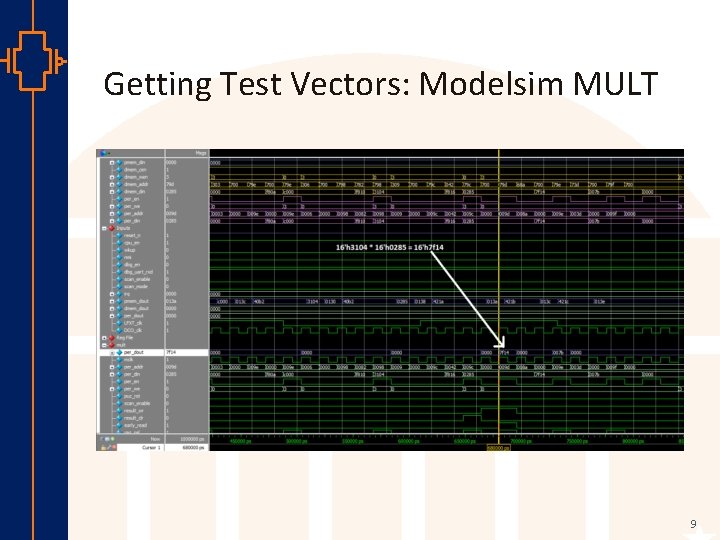

Getting Test Vectors: Modelsim MULT st Robu Low er Pow VLSI 9

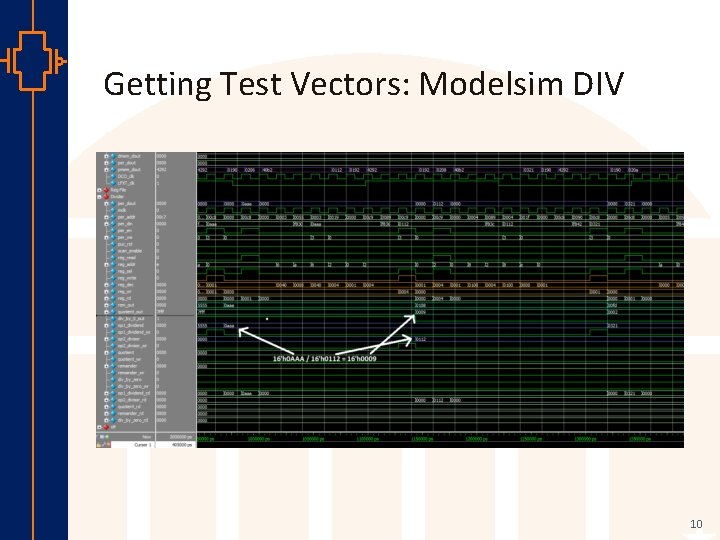

Getting Test Vectors: Modelsim DIV st Robu Low er Pow VLSI 10

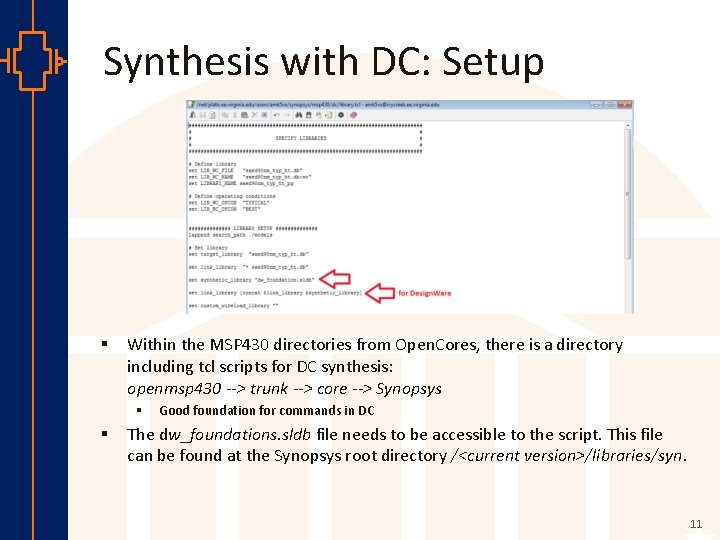

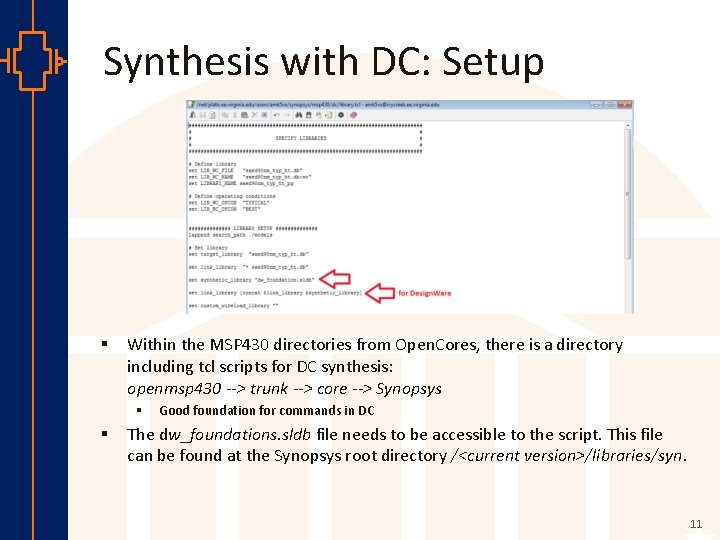

Synthesis with DC: Setup § st Robu Low er Pow VLSI Within the MSP 430 directories from Open. Cores, there is a directory including tcl scripts for DC synthesis: openmsp 430 --> trunk --> core --> Synopsys § § Good foundation for commands in DC The dw_foundations. sldb file needs to be accessible to the script. This file can be found at the Synopsys root directory /<current version>/libraries/syn. 11

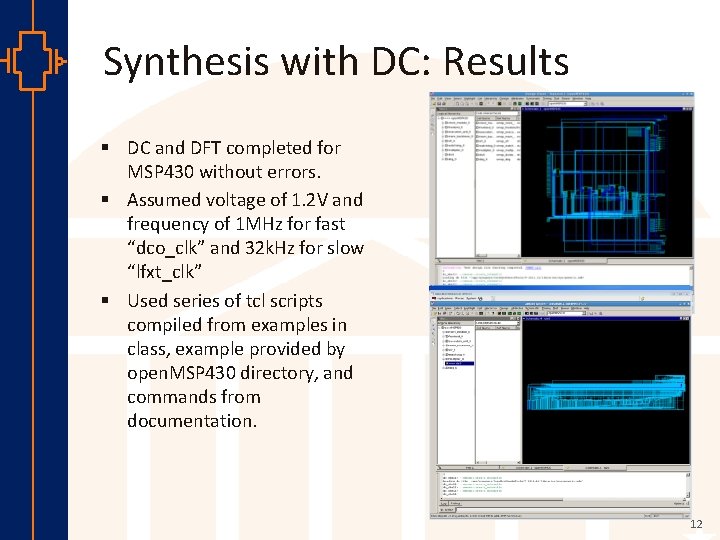

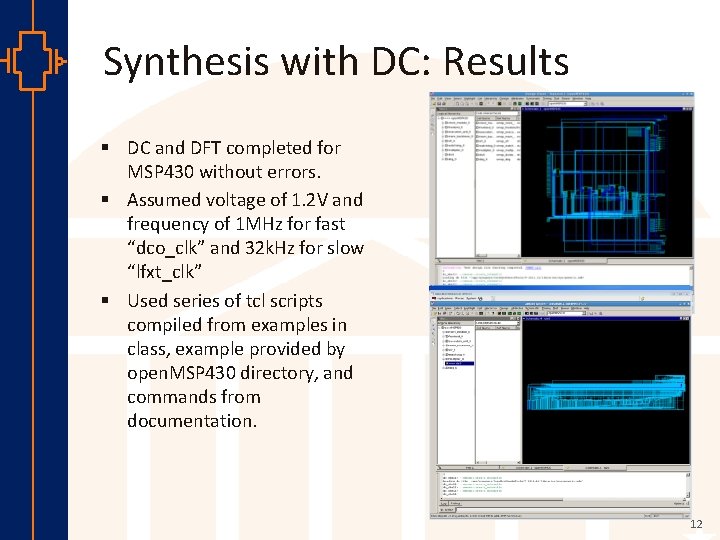

Synthesis with DC: Results st Robu Low er Pow VLSI § DC and DFT completed for MSP 430 without errors. § Assumed voltage of 1. 2 V and frequency of 1 MHz for fast “dco_clk” and 32 k. Hz for slow “lfxt_clk” § Used series of tcl scripts compiled from examples in class, example provided by open. MSP 430 directory, and commands from documentation. 12

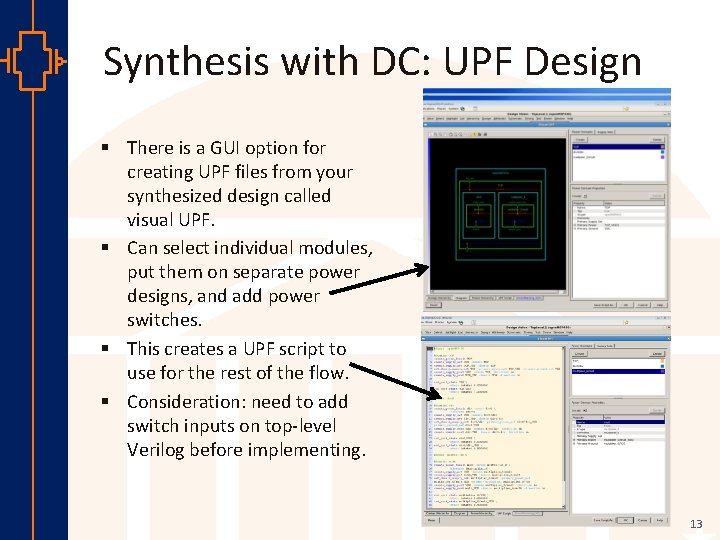

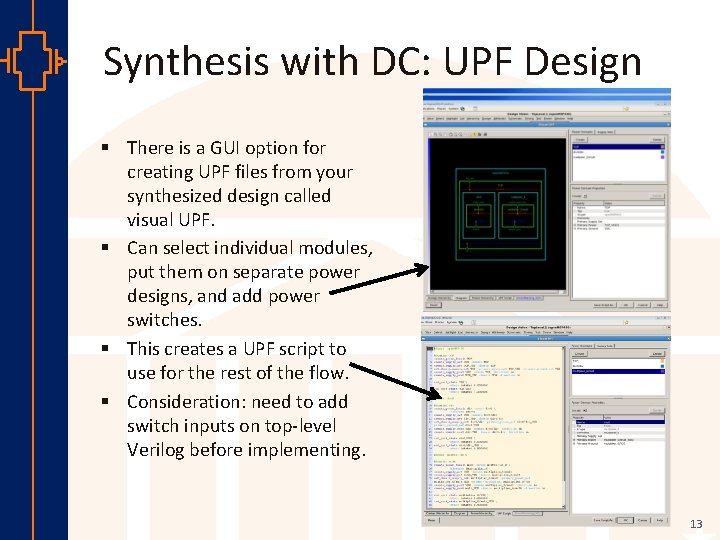

Synthesis with DC: UPF Design st Robu Low er Pow VLSI § There is a GUI option for creating UPF files from your synthesized design called visual UPF. § Can select individual modules, put them on separate power designs, and add power switches. § This creates a UPF script to use for the rest of the flow. § Consideration: need to add switch inputs on top-level Verilog before implementing. 13

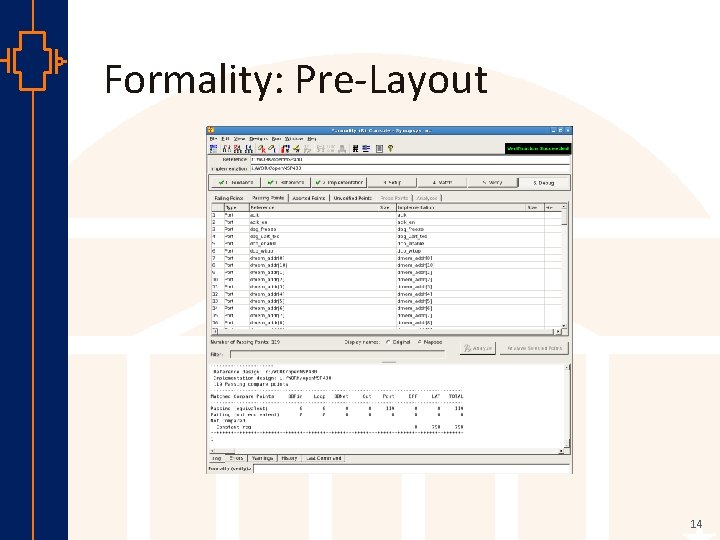

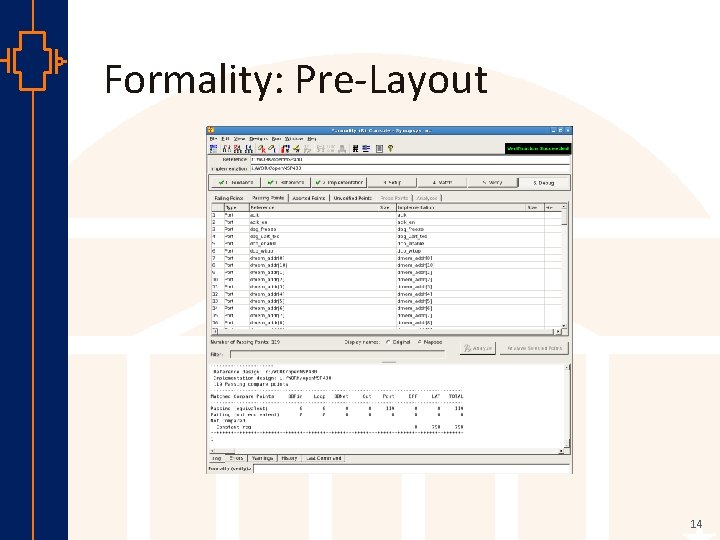

Formality: Pre-Layout st Robu Low er Pow VLSI 14

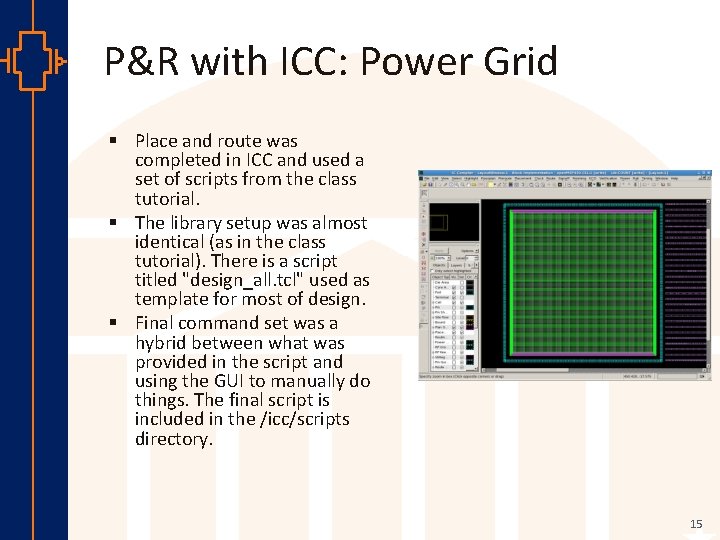

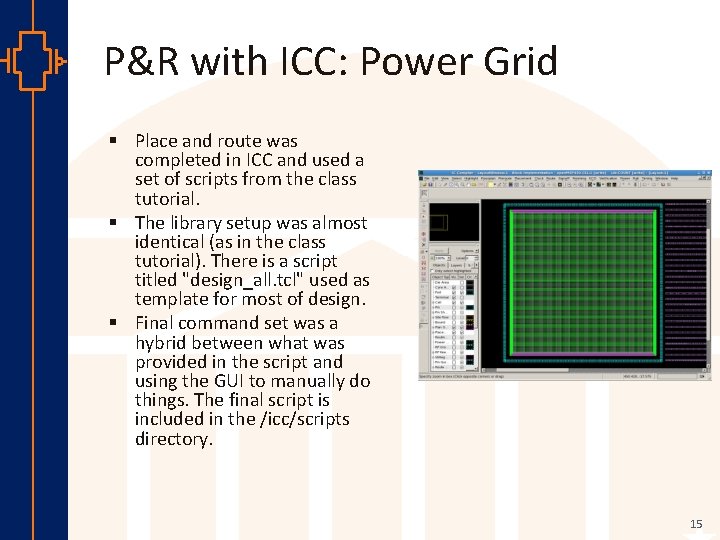

P&R with ICC: Power Grid st Robu Low er Pow VLSI § Place and route was completed in ICC and used a set of scripts from the class tutorial. § The library setup was almost identical (as in the class tutorial). There is a script titled "design_all. tcl" used as template for most of design. § Final command set was a hybrid between what was provided in the script and using the GUI to manually do things. The final script is included in the /icc/scripts directory. 15

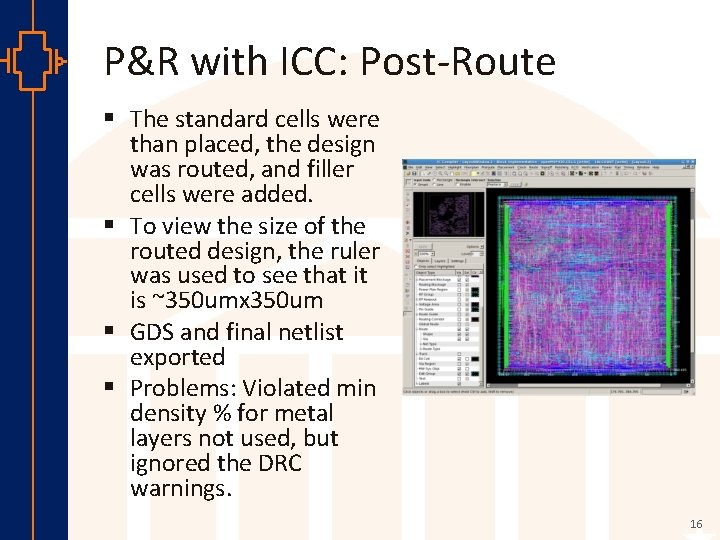

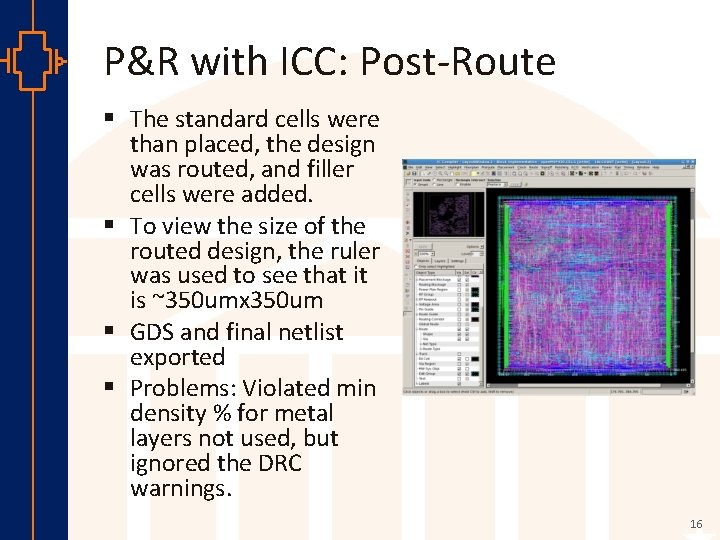

P&R with ICC: Post-Route st Robu Low er Pow VLSI § The standard cells were than placed, the design was routed, and filler cells were added. § To view the size of the routed design, the ruler was used to see that it is ~350 umx 350 um § GDS and final netlist exported § Problems: Violated min density % for metal layers not used, but ignored the DRC warnings. 16

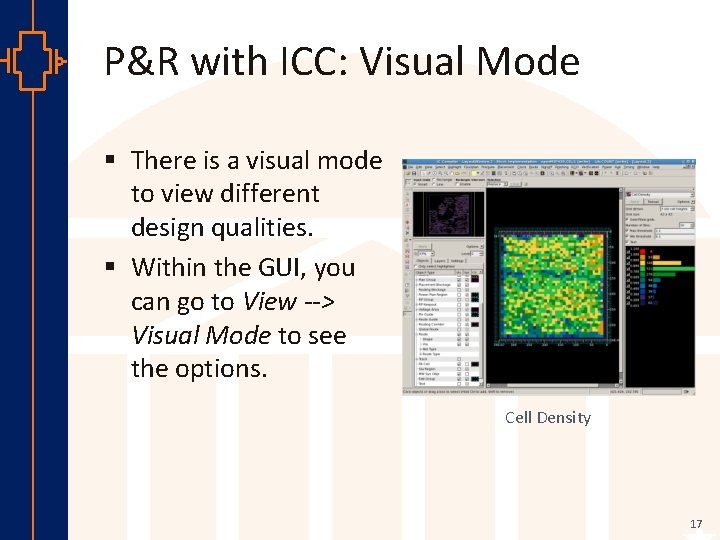

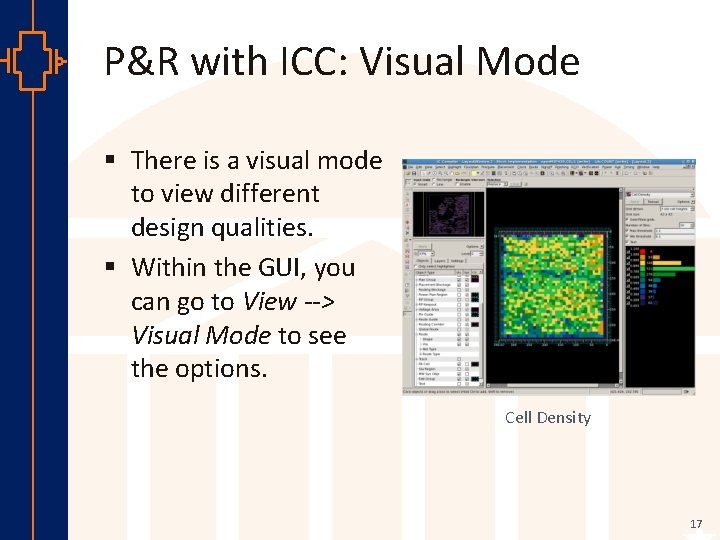

P&R with ICC: Visual Mode § There is a visual mode to view different design qualities. § Within the GUI, you can go to View --> Visual Mode to see the options. st Robu Low er Pow VLSI Cell Density 17

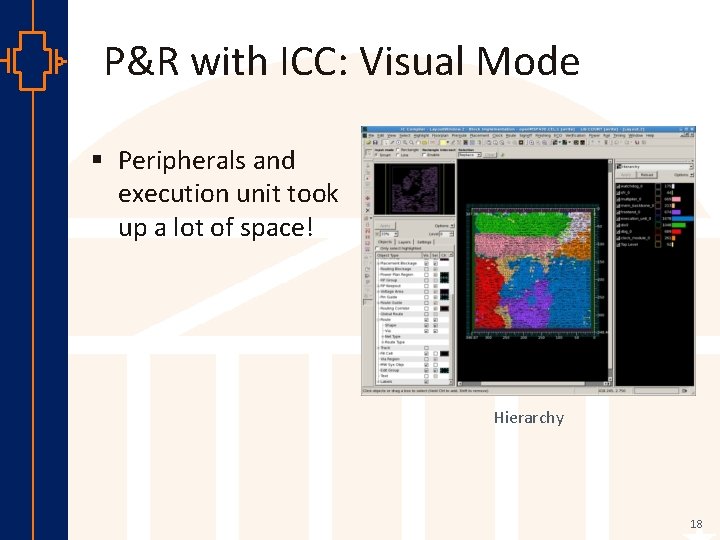

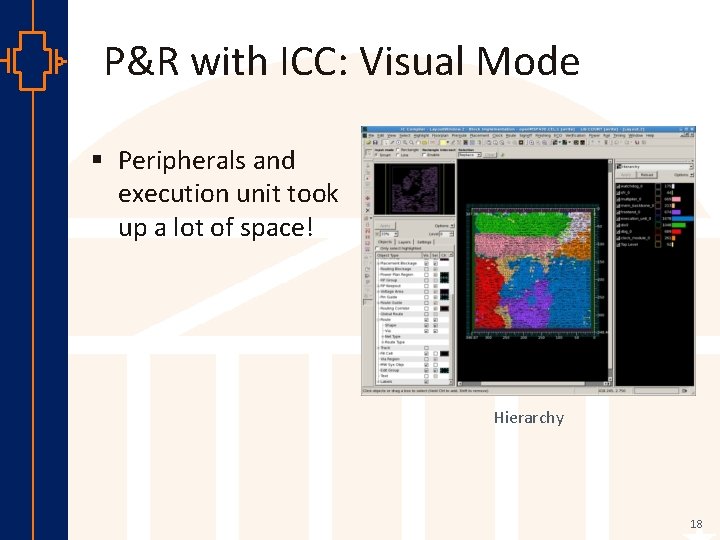

P&R with ICC: Visual Mode § Peripherals and execution unit took up a lot of space! st Robu Low er Pow VLSI Hierarchy 18

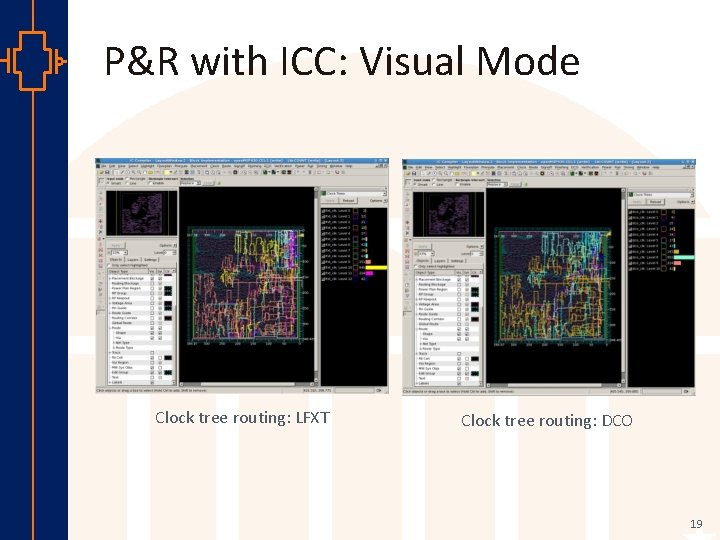

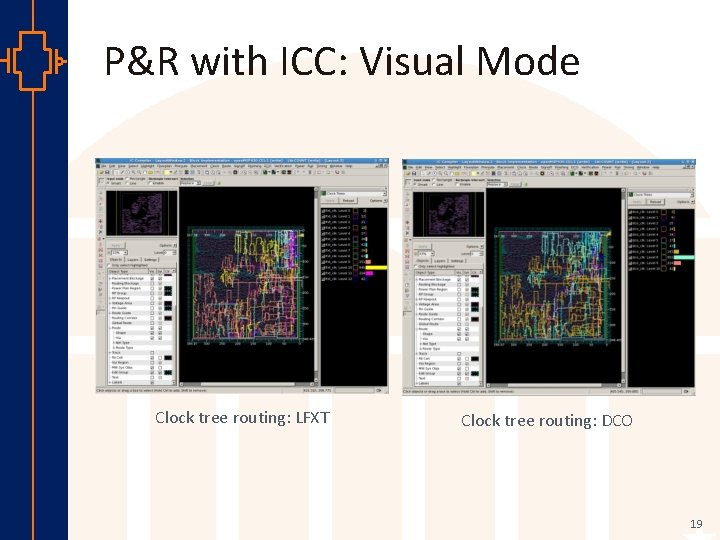

P&R with ICC: Visual Mode st Robu Low er Pow VLSI Clock tree routing: LFXT Clock tree routing: DCO 19

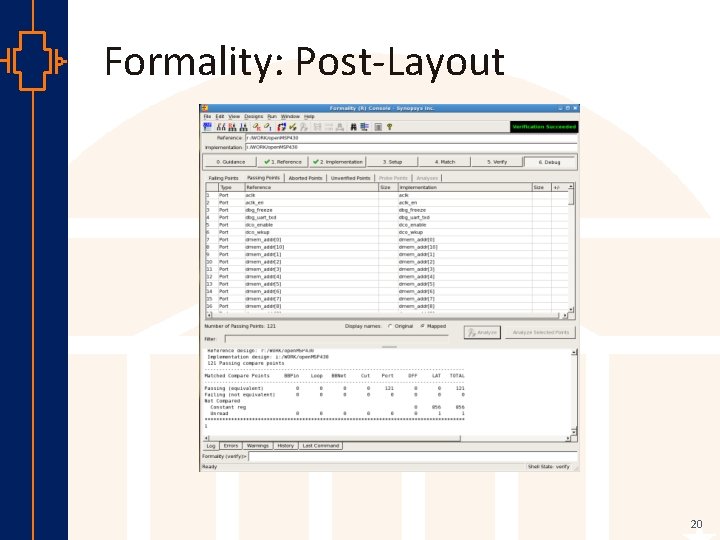

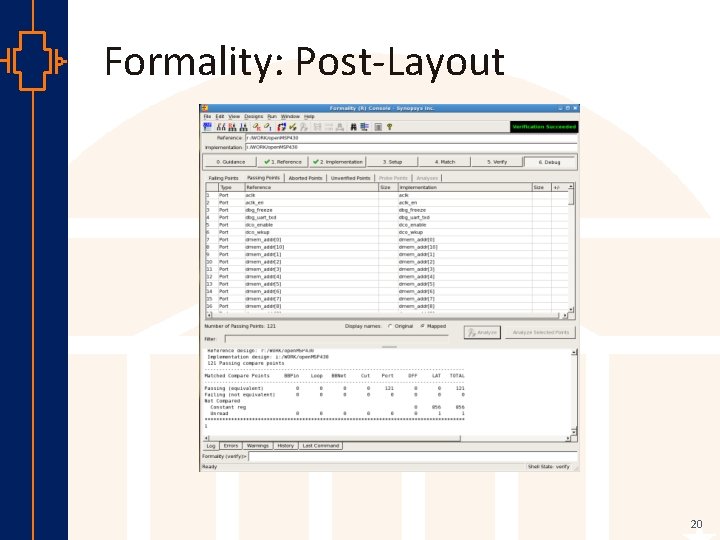

Formality: Post-Layout st Robu Low er Pow VLSI 20

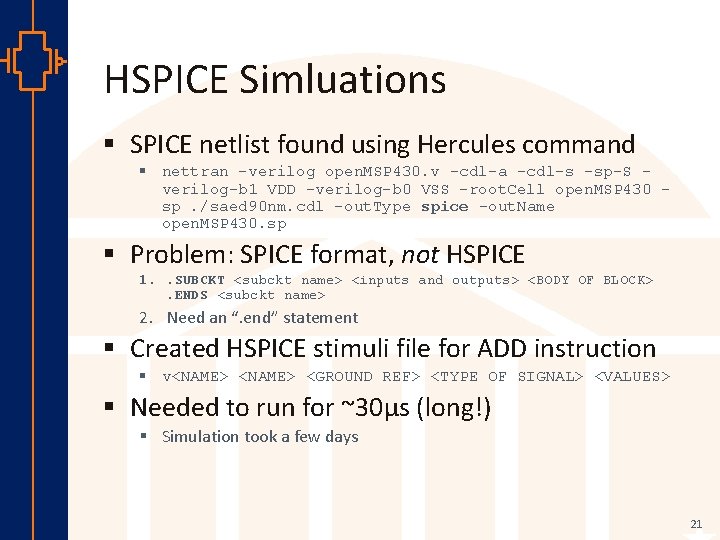

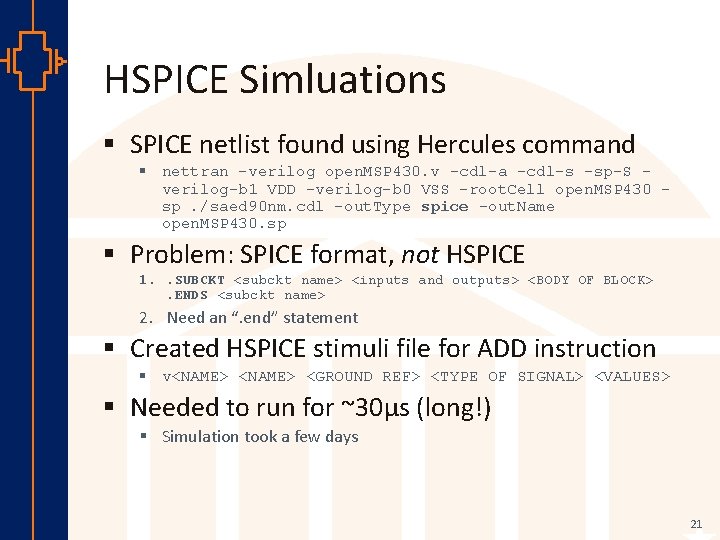

HSPICE Simluations § SPICE netlist found using Hercules command § nettran -verilog open. MSP 430. v -cdl-a -cdl-s -sp-S verilog-b 1 VDD -verilog-b 0 VSS -root. Cell open. MSP 430 sp. /saed 90 nm. cdl -out. Type spice -out. Name open. MSP 430. sp § Problem: SPICE format, not HSPICE 1. . SUBCKT <subckt name> <inputs and outputs> <BODY OF BLOCK>. ENDS <subckt name> 2. Need an “. end” statement § Created HSPICE stimuli file for ADD instruction § v<NAME> <GROUND REF> <TYPE OF SIGNAL> <VALUES> st Robu Low er Pow VLSI § Needed to run for ~30μs (long!) § Simulation took a few days 21

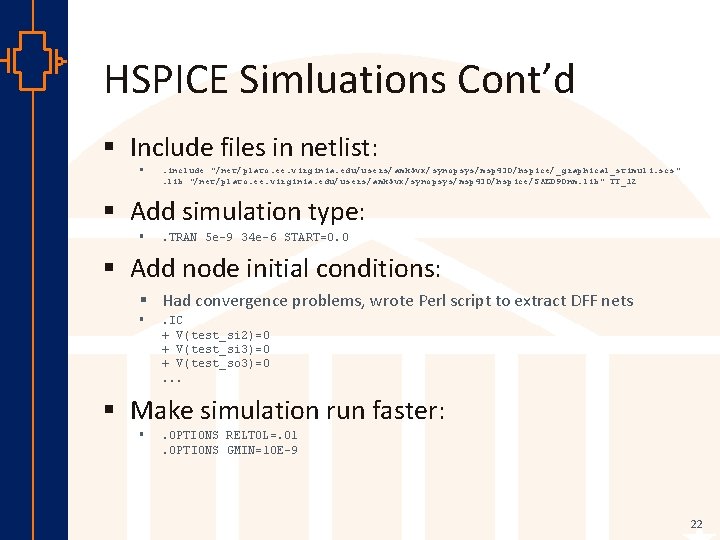

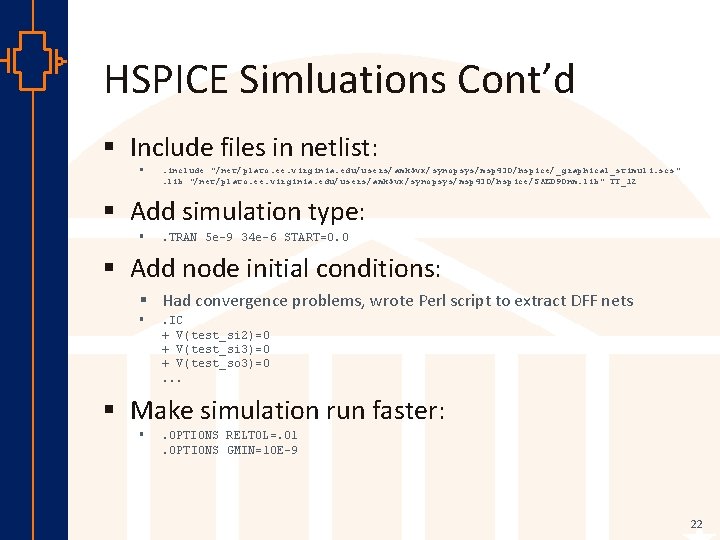

HSPICE Simluations Cont’d § Include files in netlist: § . include "/net/plato. ee. virginia. edu/users/amk 5 vx/synopsys/msp 430/hspice/_graphical_stimuli. scs". lib "/net/plato. ee. virginia. edu/users/amk 5 vx/synopsys/msp 430/hspice/SAED 90 nm. lib" TT_12 § Add simulation type: § . TRAN 5 e-9 34 e-6 START=0. 0 § Add node initial conditions: § Had convergence problems, wrote Perl script to extract DFF nets § st Robu Low er Pow VLSI . IC + V(test_si 2)=0 + V(test_si 3)=0 + V(test_so 3)=0. . . § Make simulation run faster: § . OPTIONS RELTOL=. 01. OPTIONS GMIN=10 E-9 22

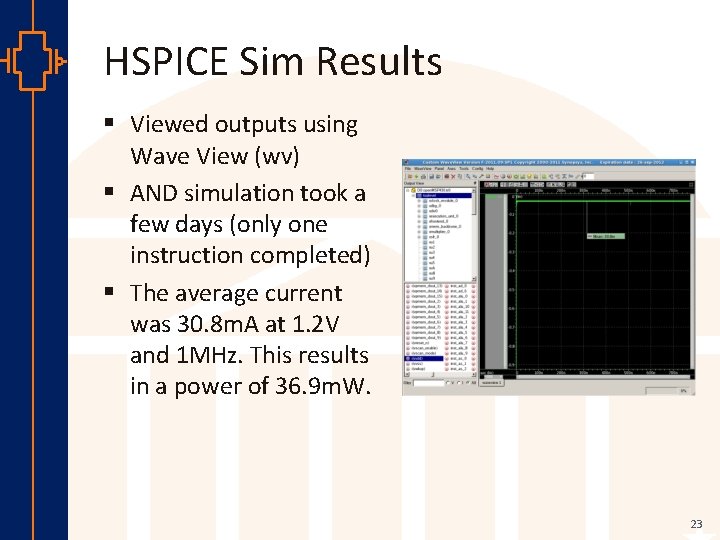

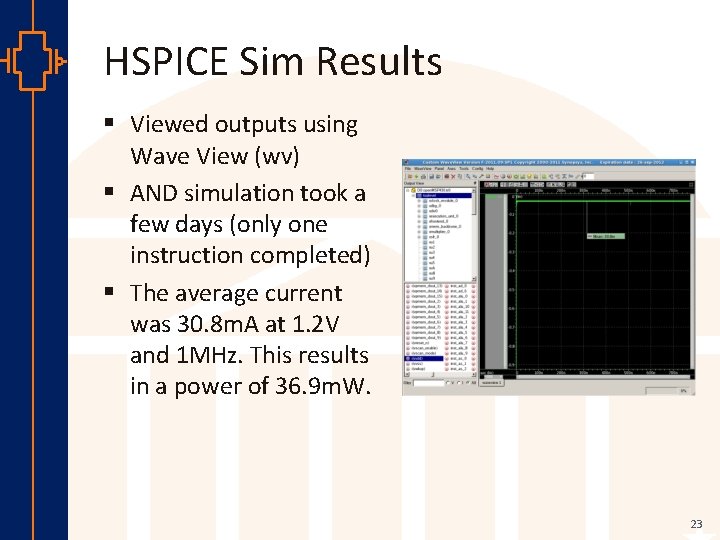

HSPICE Sim Results § Viewed outputs using Wave View (wv) § AND simulation took a few days (only one instruction completed) § The average current was 30. 8 m. A at 1. 2 V and 1 MHz. This results in a power of 36. 9 m. W. st Robu Low er Pow VLSI 23

Provided Results § Directory of files including the results. The description of each sub-directory is: § dc: Results, scripts, ref files, and original Verilog files of the design for DC synthesis. § formality: Formality of pre and post layout files. § hercules: Used for getting SPICE netlist from the results of ICC place and route. § hspice: directory containing HSPICE netlist, perl scripts for modifying SPICE netlist to turn into an HSPICE netlist, and stimuli file. § icc: Files and scripts used for place and route. § Other loose files in the directory st Robu Low er Pow VLSI § The data sheet for the Design. Ware divider that is being used (dw_div. pdf) § The "syn_setup" file that needs to be sourced before using all of the tools described above. 24

Future Work st Robu Low er Pow VLSI § Adding Design. Ware or custom memories for the program and data memories. The difficulty isn't adding them so much as using them to feed data to the MSP 430 including all of the scanning data into them and timing. § More simulations of other instructions would be good to truly know functionality across the instruction set. § Implementing power gating into the layout using UPF. 25

References 1. Fan Zhang; Yanqing Zhang; Silver, J. ; Shakhsheer, Y. ; Nagaraju, M. ; Klinefelter, A. ; Pandey, J. ; Boley, J. ; Carlson, E. ; Shrivastava, A. ; Otis, B. ; Calhoun, B. ; , "A batteryless 19μW MICS/ISM-band energy harvesting body area sensor node So. C, " Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2012 IEEE International , vol. , no. , pp. 298 -300, 19 -23 Feb. 2012. 2. http: //opencores. com/project, openmsp 430 st Robu Low er Pow VLSI 26

Questions? st Robu Low er Pow VLSI 27