A Hybrid DRAMPCM Buffer Cache Architecture for Smartphones

A Hybrid DRAM/PCM Buffer Cache Architecture for Smartphones with Qo. S Consideration ACM Transactions on Design Automation of Electronic Systems, Vol. 22, No. 2, Article 27, Pub. date: December 2016.

Outline • • • Introduction Background Design Evaluation Conclusion

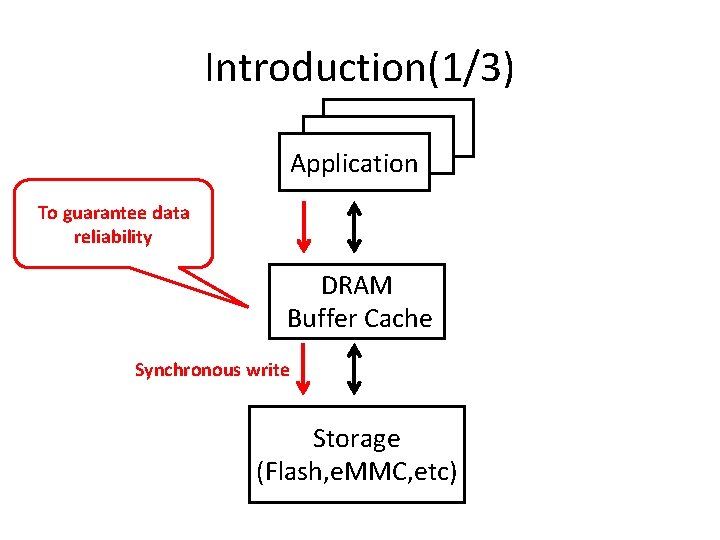

Introduction(1/3) Application To guarantee data reliability DRAM Buffer Cache Synchronous write Storage (Flash, e. MMC, etc)

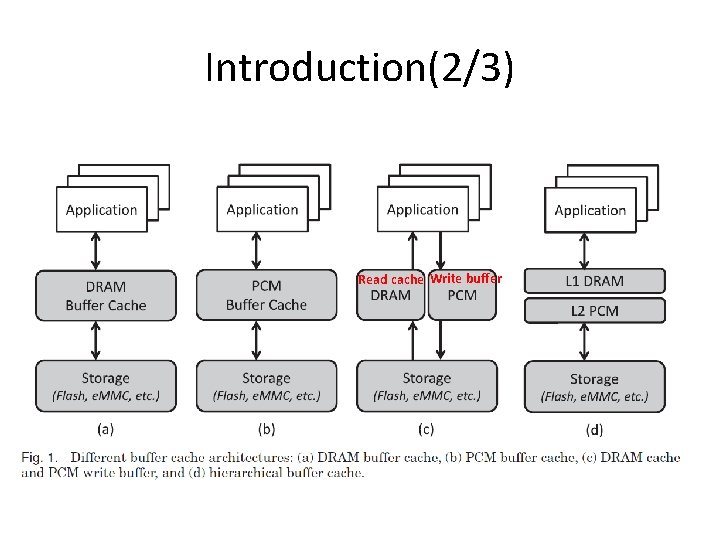

Introduction(2/3) Read cache Write buffer

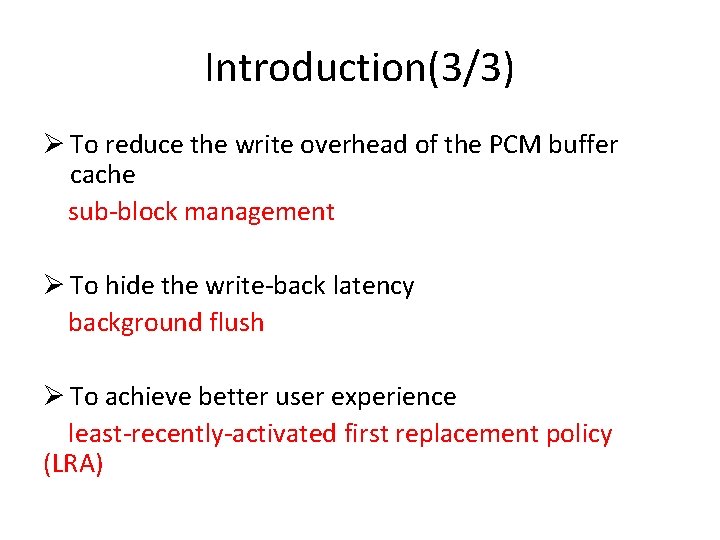

Introduction(3/3) Ø To reduce the write overhead of the PCM buffer cache sub-block management Ø To hide the write-back latency background flush Ø To achieve better user experience least-recently-activated first replacement policy (LRA)

Outline • • • Introduction Background Design Evaluation Conclusion

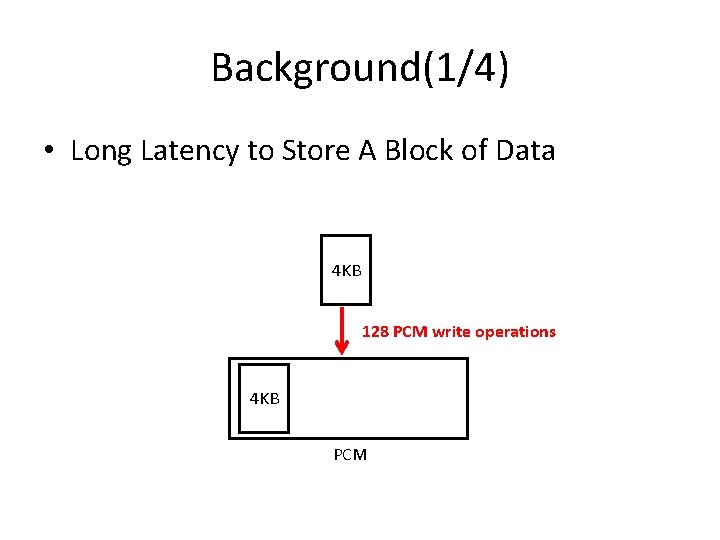

Background(1/4) • Long Latency to Store A Block of Data 4 KB 128 PCM write operations 4 KB PCM

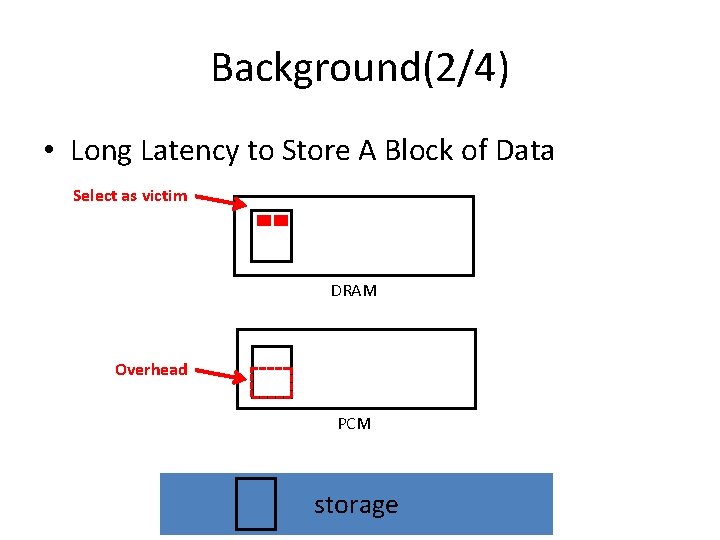

Background(2/4) • Long Latency to Store A Block of Data Select as victim DRAM Overhead PCM storage

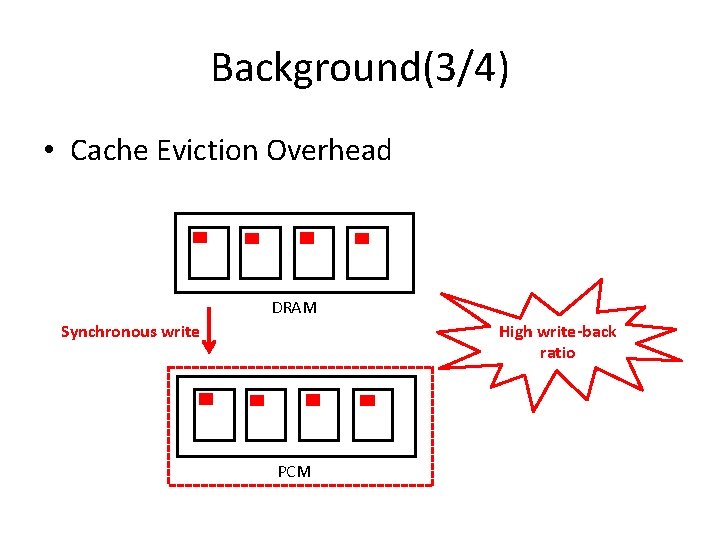

Background(3/4) • Cache Eviction Overhead DRAM High write-back ratio Synchronous write PCM

Background(4/4) • Buffer Cache Design for Qo. S Ø In smartphones, user experience is mainly dependent on the response time of the foreground application Ø Conventional buffer caches only optimize the average I/O response time without taking the user experience into account in the management scheme

Outline • • • Introduction Background Design Evaluation Conclusion

Design(1/6) Ø cache miss Ø write-back of the evicted blocks Ø synchronous write

Design(2/6) • Sub-Block Management Select as victim

Design(3/6) • Background Flush

Design(4/6) • Background Flush

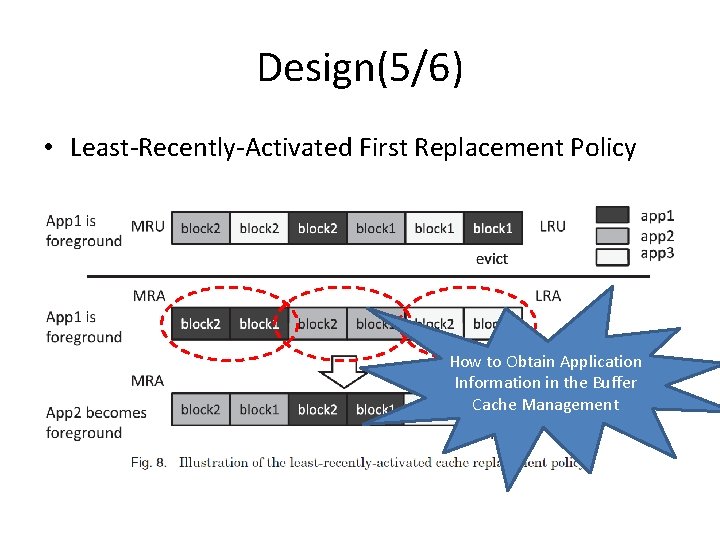

Design(5/6) • Least-Recently-Activated First Replacement Policy How to Obtain Application Information in the Buffer Cache Management

Design(6/6)

Outline • • • Introduction Background Design Evaluation Conclusion

Evaluation(1/3)

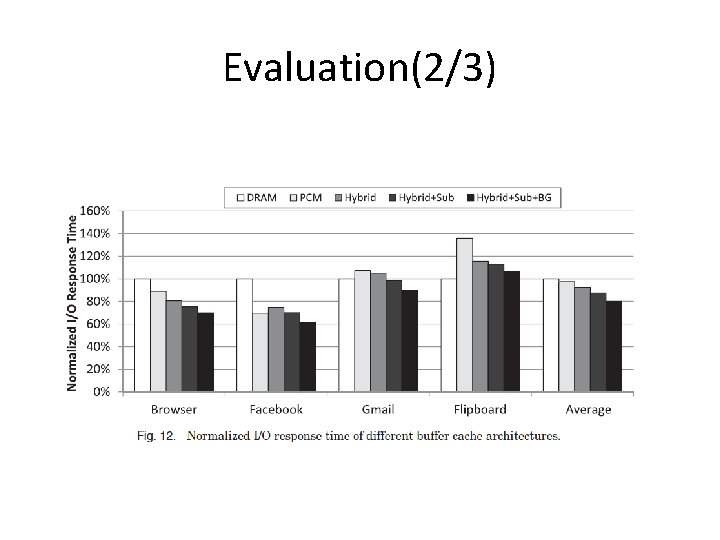

Evaluation(2/3)

Evaluation(3/3)

Outline • • • Introduction Background Design Evaluation Conclusion

Conclusion • To reduce the PCM write overhead in the buffer cache, we propose a sub-block management to reduce the redundant data being written to PCM. • To reduce the flush write-back overhead, we propose a background flush scheme to flush the dirty blocks in the PCM buffer cache in the background. • To achieve better user experience, we propose a Qo. S-aware LRA to avoid the foreground application blocks from being replaced by the background ones.

- Slides: 23