A DualLoop InjectionLocked PLL with AllDigital PVT Calibration

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 1 of 21 A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System Wei Deng, Ahmed Musa, Teerachot Siriburanon, Masaya Miyahara, Kenichi Okada, and Akira Matsuzawa Tokyo Institute of Technology, Japan © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 2 of 21 Outline • Introduction • Issues of Conventional Injection. Locked PLLs (IL-PLLs) • Proposed Dual-loop IL-PLL • PVT Tracking Capability by Replica Loop • Low Jitter by Main Loop • Measurement Results • Conclusion © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 3 of 21 Introduction • Why High Performance PLL – Clock generation/distribution • Key Specifications for So. C Clocking – Small area – Low power consumption – Low jitter – Scalable with technology advancement – Insensitive over environment variations © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 4 of 21 Injection-locking Technique © 2013 電子情報通信学会 総合大会 © 2013

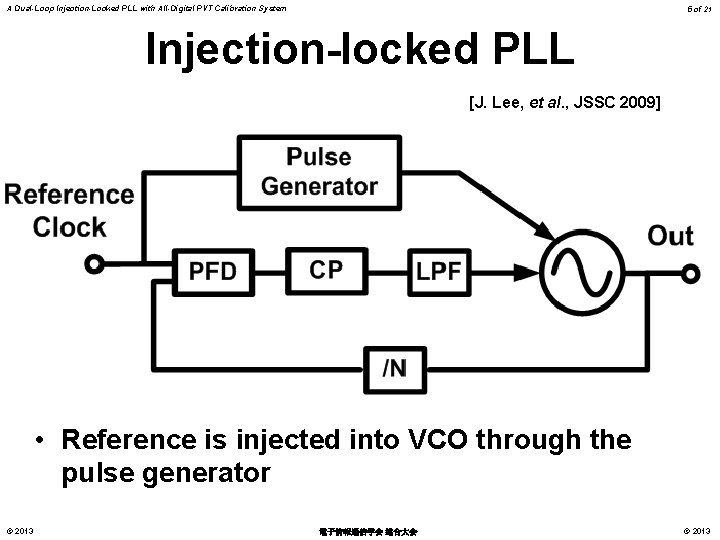

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 5 of 21 Injection-locked PLL [J. Lee, et al. , JSSC 2009] • Reference is injected into VCO through the pulse generator © 2013 電子情報通信学会 総合大会 © 2013

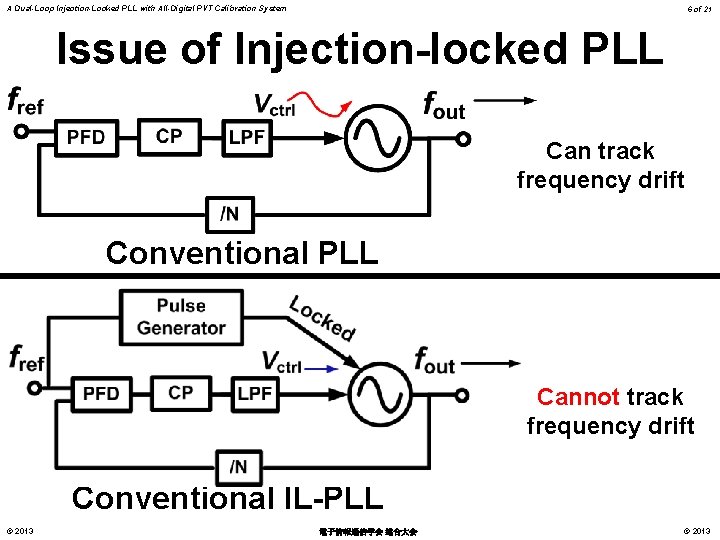

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 6 of 21 Issue of Injection-locked PLL Can track frequency drift Conventional PLL Cannot track frequency drift Conventional IL-PLL © 2013 電子情報通信学会 総合大会 © 2013

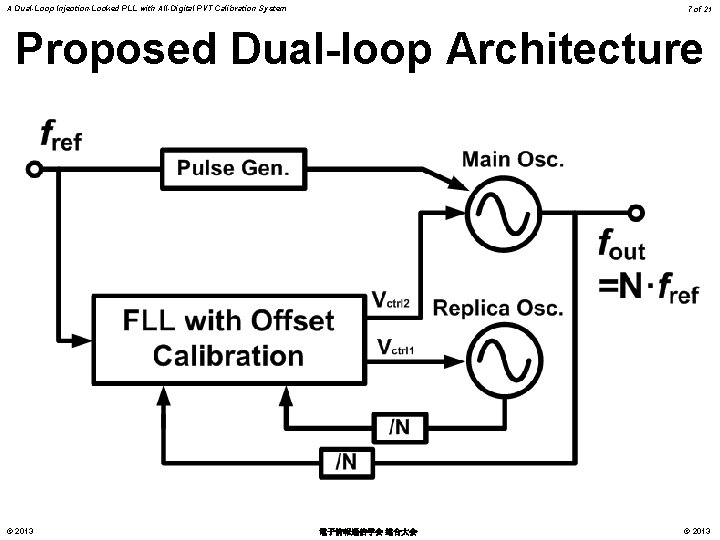

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 7 of 21 Proposed Dual-loop Architecture © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 8 of 21 Proposed Dual-loop IL-PLL FCW: Frequency Control Word © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 9 of 21 Calibration Algorithm © 2013 電子情報通信学会 総合大会 © 2013

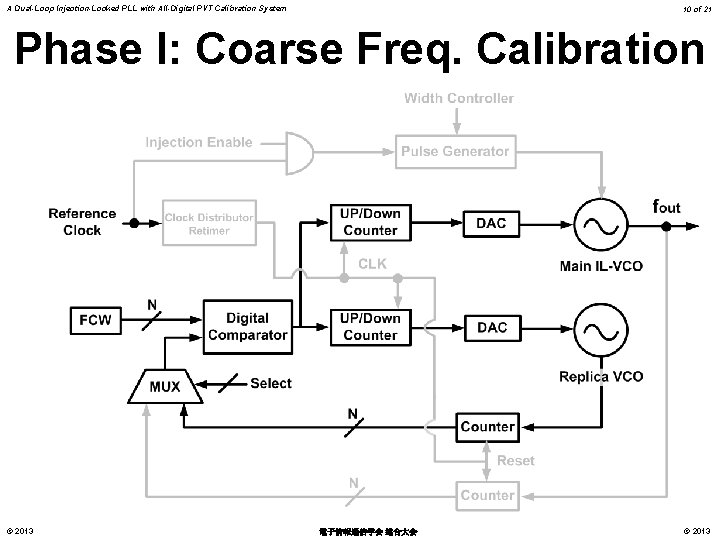

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 10 of 21 Phase I: Coarse Freq. Calibration © 2013 電子情報通信学会 総合大会 © 2013

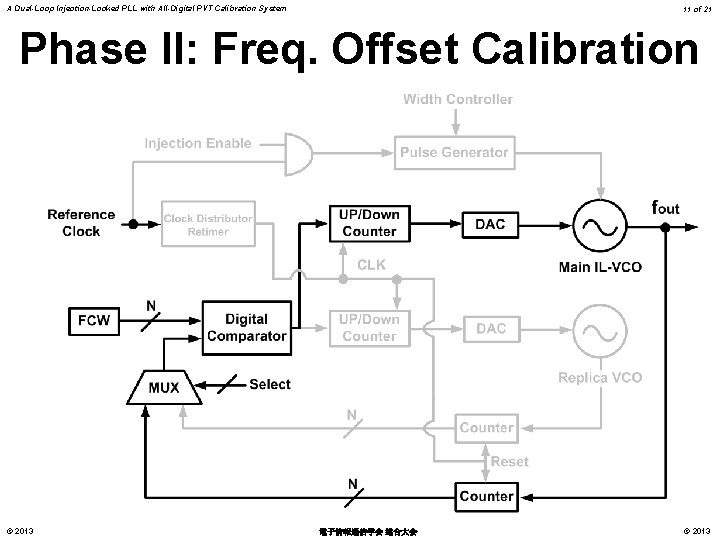

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 11 of 21 Phase II: Freq. Offset Calibration © 2013 電子情報通信学会 総合大会 © 2013

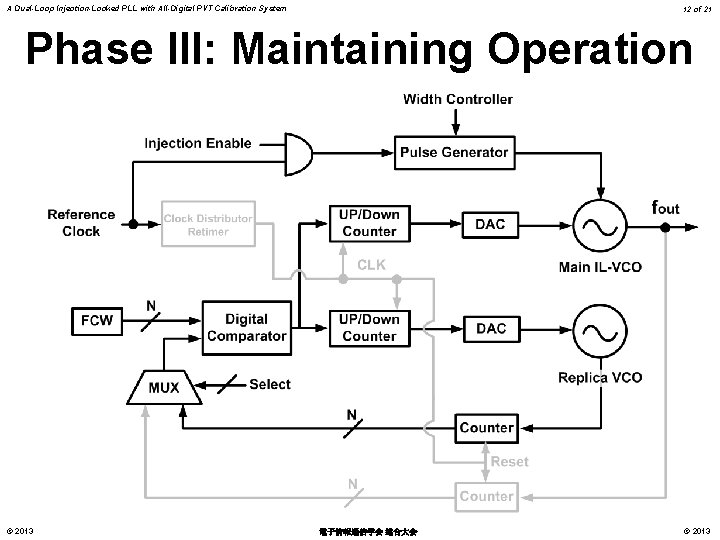

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 12 of 21 Phase III: Maintaining Operation © 2013 電子情報通信学会 総合大会 © 2013

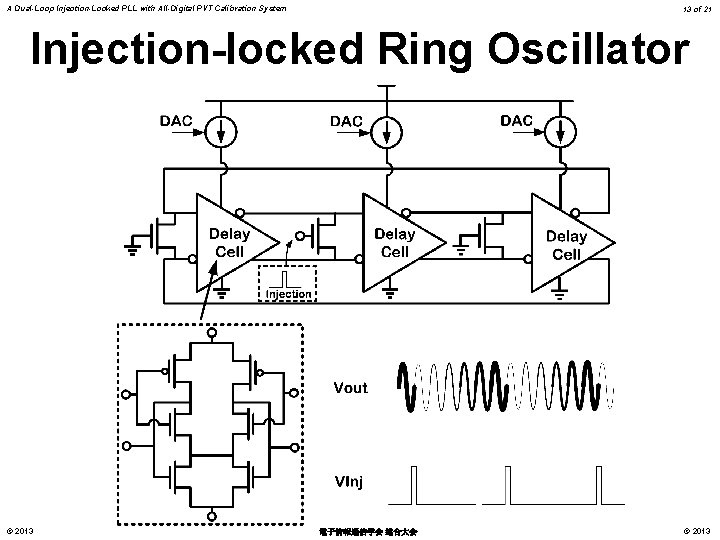

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 13 of 21 Injection-locked Ring Oscillator © 2013 電子情報通信学会 総合大会 © 2013

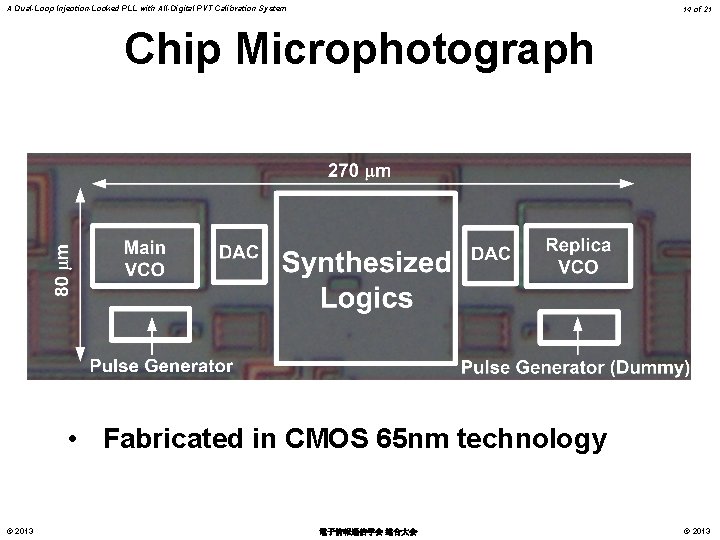

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 14 of 21 Chip Microphotograph • Fabricated in CMOS 65 nm technology © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 15 of 21 Phase Noise Ref. : 300 MHz (40 MHz-300 MHz) Freq. : 1. 2 GHz (0. 5 -1. 6 GHz) Integrated jitter: 0. 7 ps (10 k. Hz-40 MHz) Pdc: 0. 97 m. W (1. 2 GHz) © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 16 of 21 Measured Spectrum Locked Free-running 1. 08 GHz © 2013 1. 32 GHz 1. 199 GHz 電子情報通信学会 総合大会 1. 201 GHz © 2013

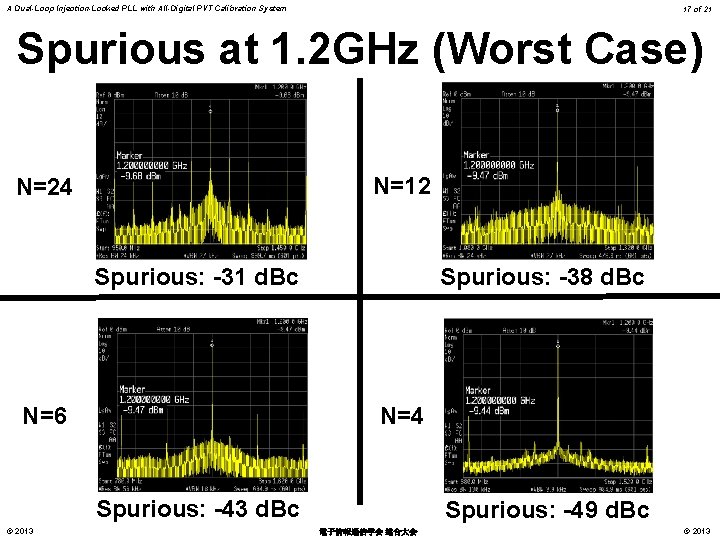

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 17 of 21 Spurious at 1. 2 GHz (Worst Case) N=12 N=24 Spurious: -38 d. Bc Spurious: -31 d. Bc N=6 N=4 Spurious: -43 d. Bc © 2013 Spurious: -49 d. Bc 電子情報通信学会 総合大会 © 2013

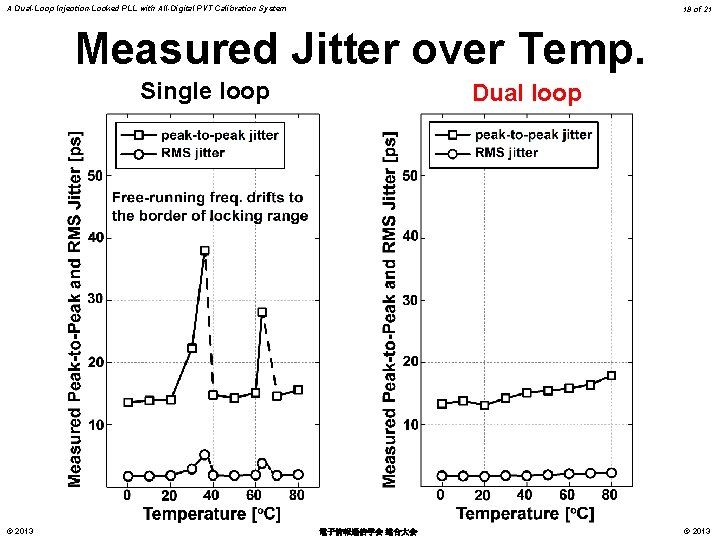

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 18 of 21 Measured Jitter over Temp. Single loop © 2013 Dual loop 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 19 of 21 Performance Summary This work IL-PLL 1. 2 Freq. [GHz] (0. 5 -1. 6) 300 Ref. [MHz] (40 -300) Power [m. W] 0. 97 Area [mm 2] 0. 022 Integ. Jitter [ps] 0. 7 Jitter RMS/PP 1. 81/19. 4 [ps] 10 M hits FOM [d. B] -243 CMOS Tech. 65 nm [1] [2] MDLL [5] IL-PLL 1. 6 0. 216 DMDLL 1. 5 (0. 8 -1. 8) DPLL 1. 5 (0. 8 -1. 8) 375 50 27 0. 89 0. 25 0. 4 0. 92/9. 2 5 M hits -248. 46 1. 35 0. 25 3. 2 4. 2/33 5 M hits -228. 59 12 0. 058 0. 68 0. 93/11. 1 30 M hits -233. 76 6. 9 0. 03 2. 4 -225 130 nm 55 nm N. A. [1] A. Elshazly, et al. , ISSCC 2012 [2] B. Helal, et al. , JSSC 2008 [5] C. Liang, et al. , ISSCC 2011 © 2013 電子情報通信学会 総合大会 © 2013

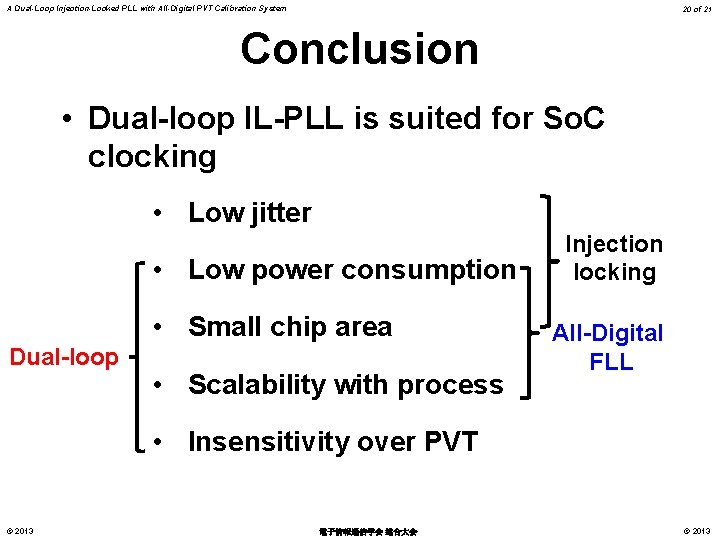

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 20 of 21 Conclusion • Dual-loop IL-PLL is suited for So. C clocking • Low jitter • Low power consumption • Small chip area Dual-loop • Scalability with process Injection locking All-Digital FLL • Insensitivity over PVT © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 21 of 21 Acknowledgement This work was partially supported by SCOPE, STARC, NEDO, MIC, MEXT, Canon Foundation, Huawei, and VDEC in collaboration with Cadence Design Systems, Inc. , and Agilent Technologies Japan, Ltd. © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System © 2013 22 of 21 電子情報通信学会 総合大会 © 2013

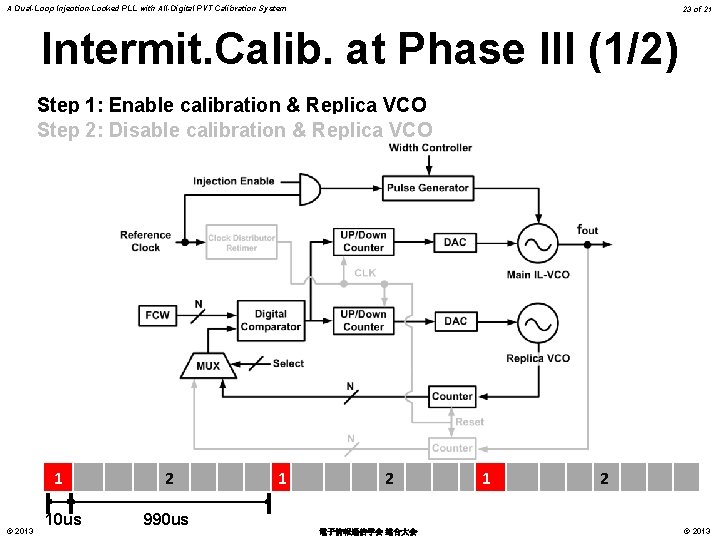

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 23 of 21 Intermit. Calib. at Phase III (1/2) Step 1: Enable calibration & Replica VCO Step 2: Disable calibration & Replica VCO 1 © 2013 10 us 2 990 us 1 2 電子情報通信学会 総合大会 1 2 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 24 of 21 Intermit. Calib. at Phase III (2/2) Step 1: Enable calibration & Replica VCO Step 2: Disable calibration & Replica VCO 1 © 2013 10 us 2 990 us 1 2 電子情報通信学会 総合大会 1 W/O Intermittent 1. 6 m. W W/ Intermittent 1 m. W 2 © 2013

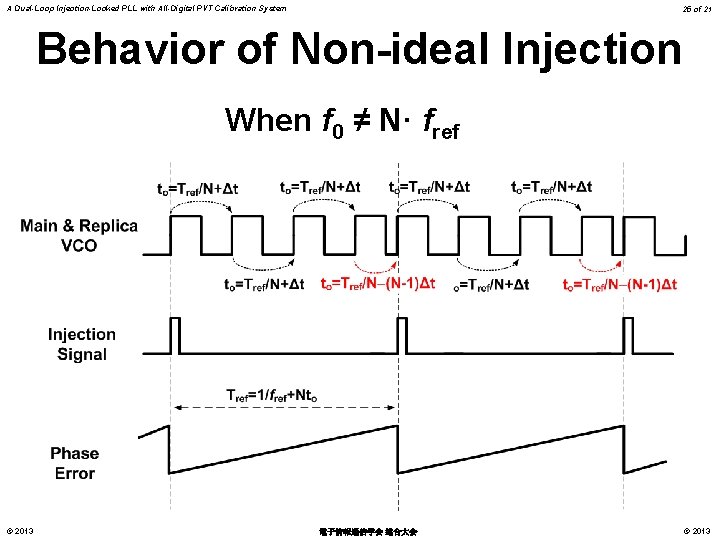

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 25 of 21 Behavior of Non-ideal Injection When f 0 ≠ N· fref © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 26 of 21 Spur Level Locked state: flocked=N · fref Free-running: ffree-running=(1+a) · flocked Spur power = -20 log 10((ffree-running- flocked)/(2 ·fref)) = -20 log 10(a ·N/2) e. g. N=20, a=0. 001 -60 d. Bc spur [R. B. Staszewski, et al. , All-Digital Frequency Synthesizer in Deep-Submicron CMOS, Wiley, 2006] © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 27 of 21 FOM over Area [1] A. Elshazly, et al. , ISSCC 2012 [2] B. Helal, et al. , JSSC 2008 [3] J. Lee, et al. , JSSC 2009 [4] G. Xiang, et al. , ISSCC 2009 [5] C. Liang, et al. , ISSCC 2011 © 2013 電子情報通信学会 総合大会 © 2013

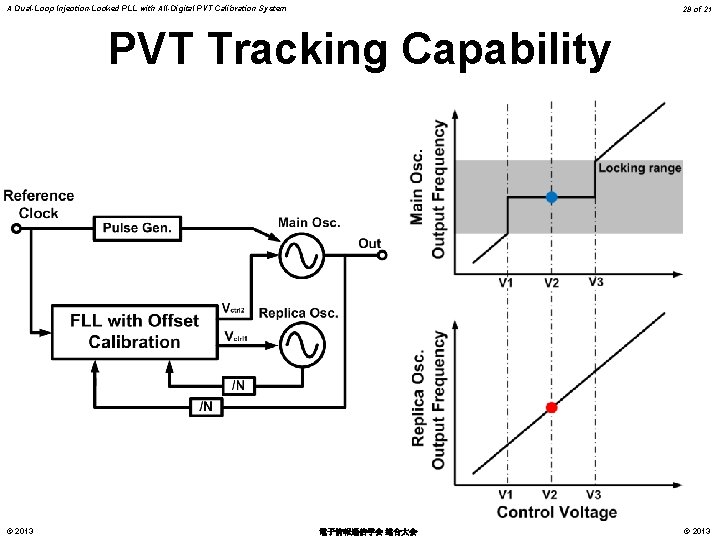

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 28 of 21 PVT Tracking Capability © 2013 電子情報通信学会 総合大会 © 2013

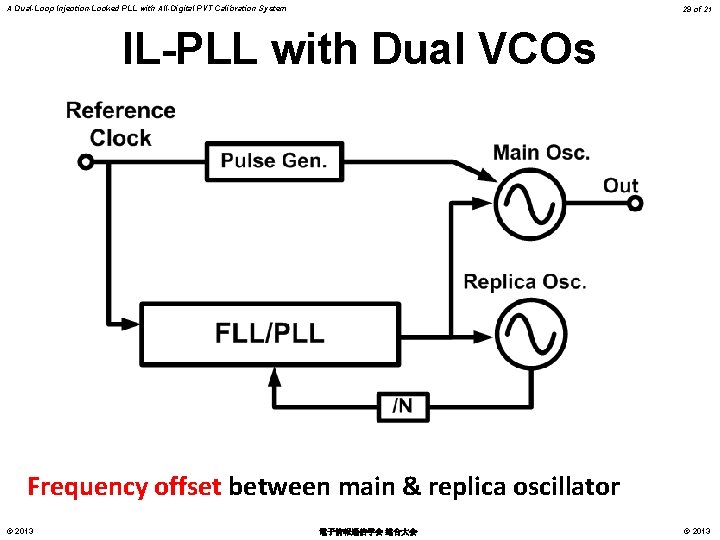

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 29 of 21 IL-PLL with Dual VCOs Frequency offset between main & replica oscillator © 2013 電子情報通信学会 総合大会 © 2013

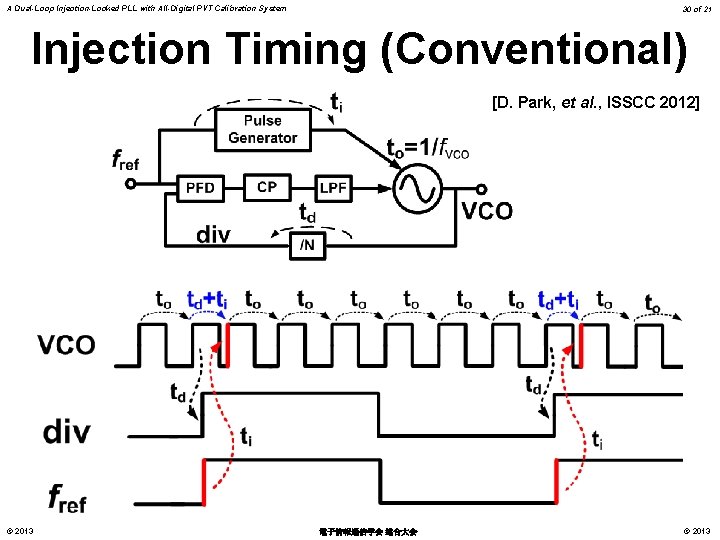

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 30 of 21 Injection Timing (Conventional) [D. Park, et al. , ISSCC 2012] © 2013 電子情報通信学会 総合大会 © 2013

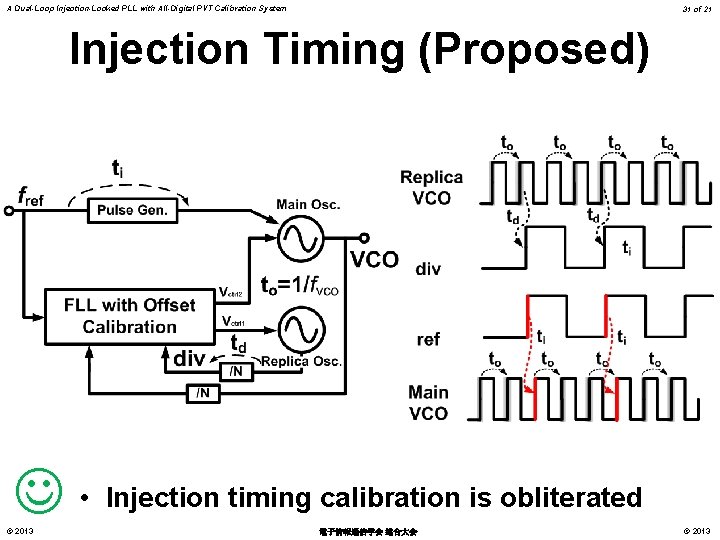

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 31 of 21 Injection Timing (Proposed) • Injection timing calibration is obliterated © 2013 電子情報通信学会 総合大会 © 2013

A Dual-Loop Injection-Locked PLL with All-Digital PVT Calibration System 32 of 21 Proposed Concept • Dual-loop Topology – PVT tracking capability – Compensate for main & replica VCO frequency offset – No calibration for injection timing required • Reduce area & power overhead • All-digital Frequency-locked Loop – Compact chip area – Low power consumption – Scalable with process advancement © 2013 電子情報通信学会 総合大会 © 2013

- Slides: 32