A Digital Circuit Toolbox Verilog Hierarchy Each design

A Digital Circuit Toolbox

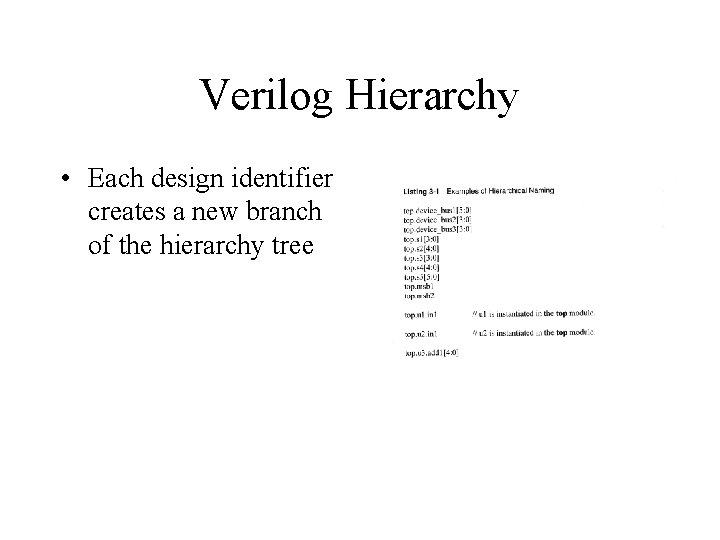

Verilog Hierarchy • Each design identifier creates a new branch of the hierarchy tree

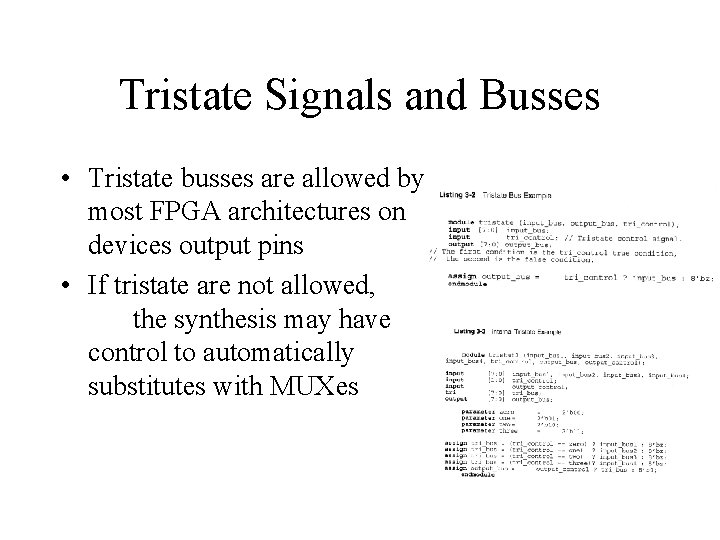

Tristate Signals and Busses • Tristate busses are allowed by most FPGA architectures on devices output pins • If tristate are not allowed, the synthesis may have control to automatically substitutes with MUXes

Schematics for Internal Tristate Buffer Design

MUX version of Tristate Buffer Design

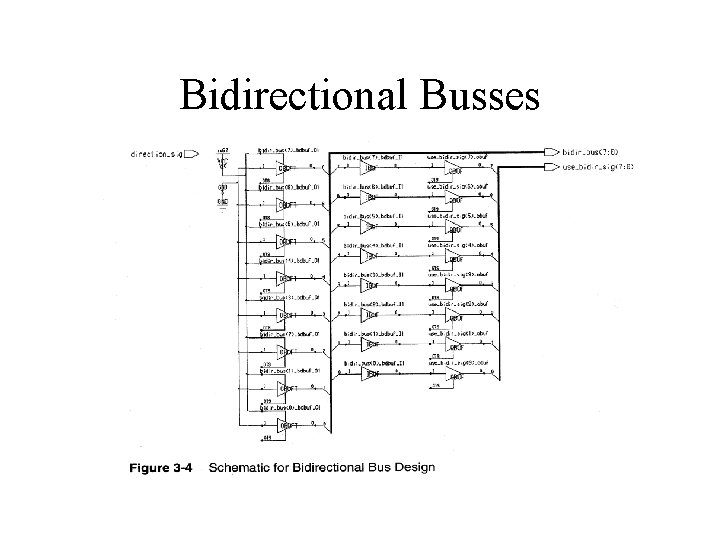

Bidirectional Busses • The signals is divided into two parts: the driver part input part • The two parts are then wired together

Bidirectional Busses

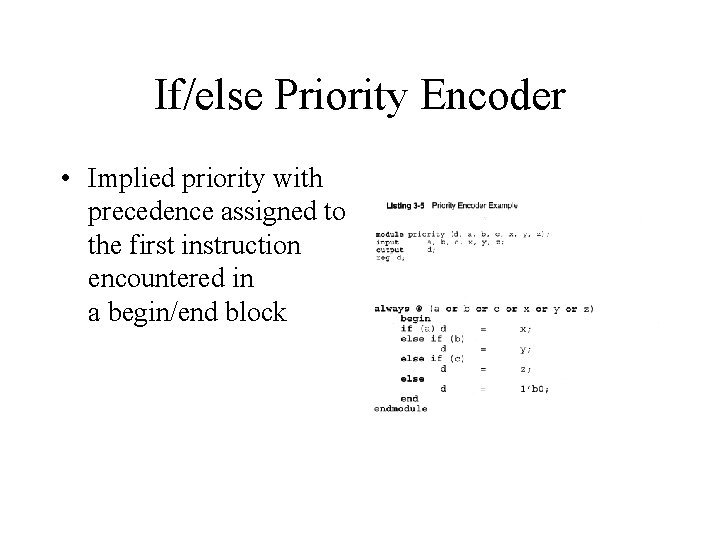

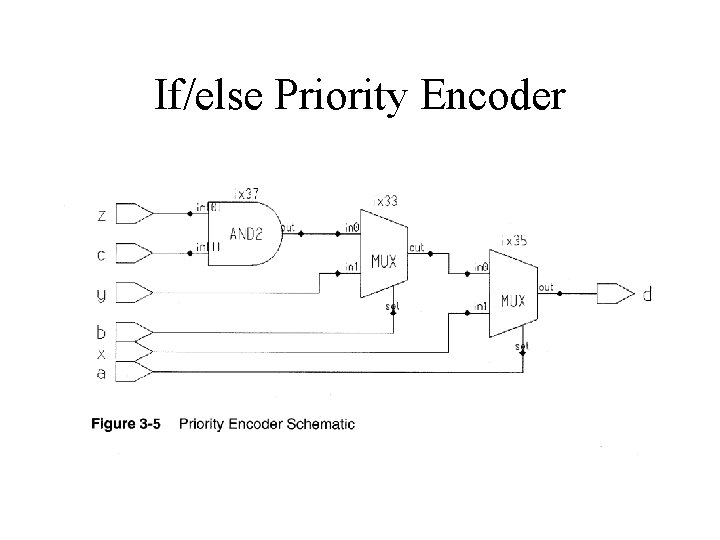

If/else Priority Encoder • Implied priority with precedence assigned to the first instruction encountered in a begin/end block

If/else Priority Encoder

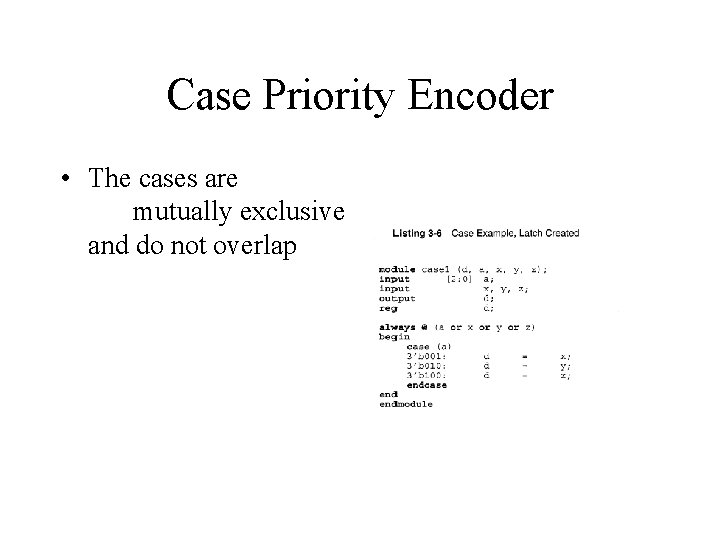

Case Priority Encoder • The cases are mutually exclusive and do not overlap

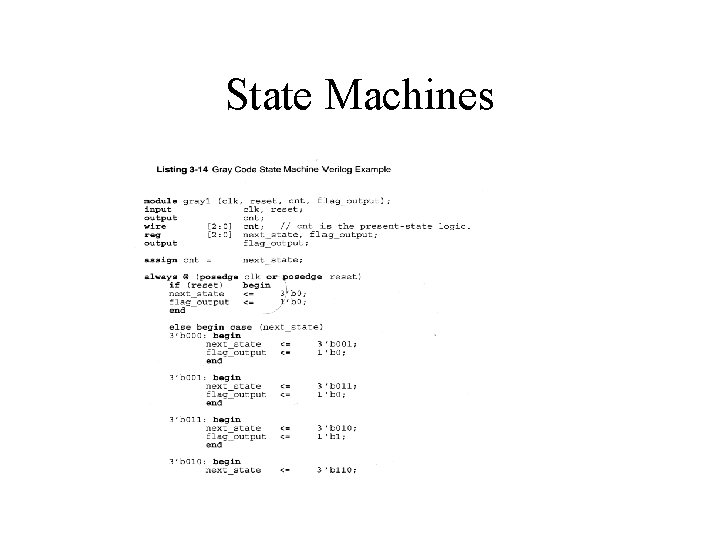

State Machines • Use a set of registers, to determine current machine state • Moore style: the output depends only on the state • Mealy style: the output depends on the state and some input signals

State Machines

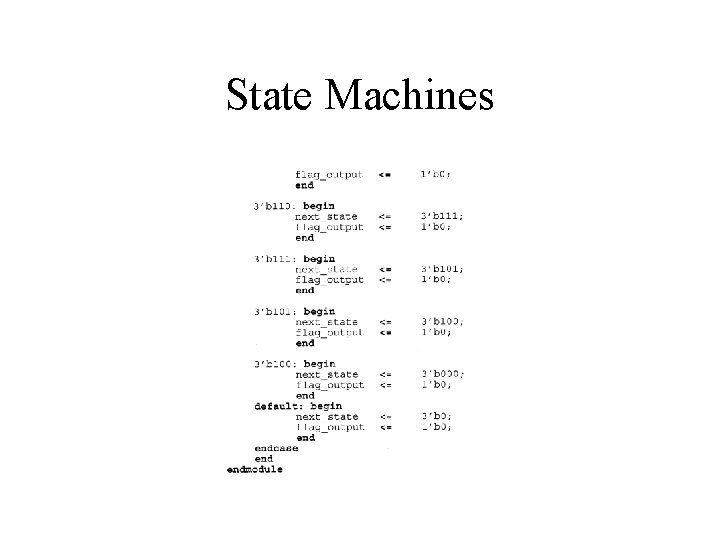

State Machines

Converting Binary to Gray Code

Converting Gray Code to Binary

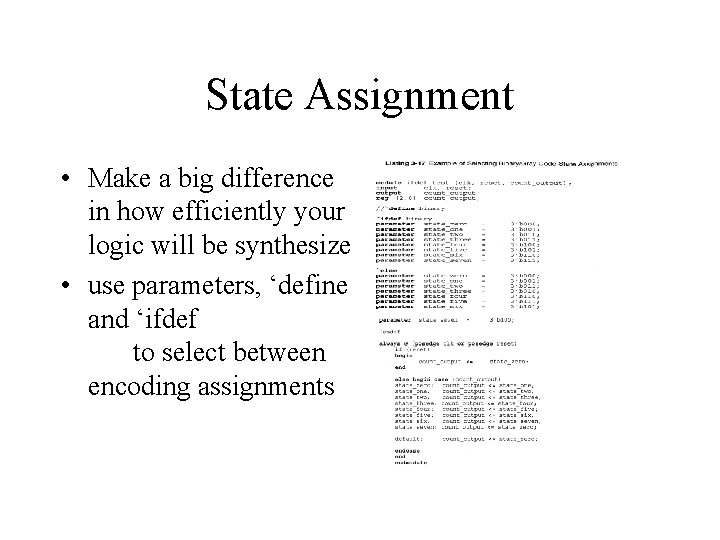

State Assignment • Make a big difference in how efficiently your logic will be synthesize • use parameters, ‘define and ‘ifdef to select between encoding assignments

State Assignment • One-hot state assignment means that each state is assigned a single state flip -flop which is active only in the assigned state • One-could state assignment means that a flip-flop is inactive only in the assigned state

Adders Half-Adder • The synthesis tool will examine each instance of the + operator and will try to implement the logic with a preoptimized module

Half-Adder

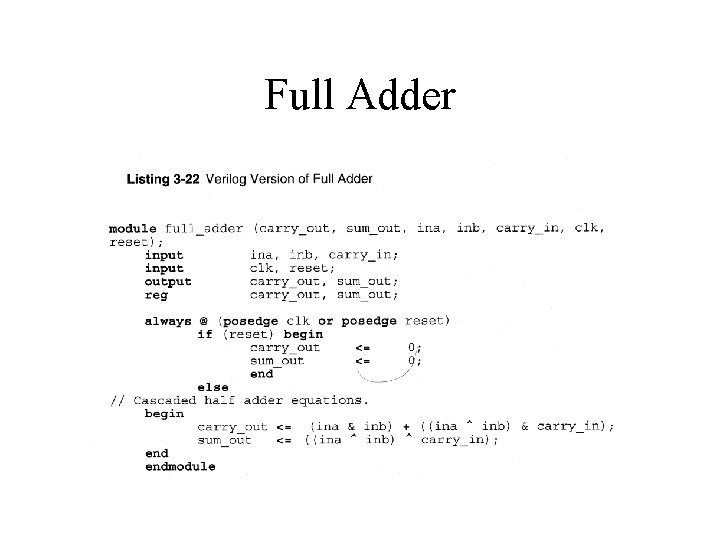

Full Adder • To turn the half adder into a full adder, we take the output of a half adder and connect it into another half adder

Full Adder

Full Adder

Full Adder

Subtractor • Similar to the adder

Full-Subtractor

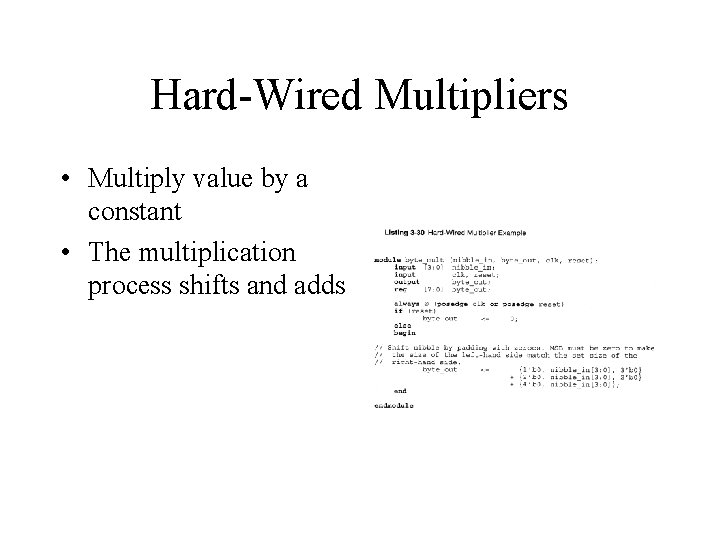

Hard-Wired Multipliers • Multiply value by a constant • The multiplication process shifts and adds

Generic Multipliers • We must create logic which allows all the shift and adds to be used

- Slides: 28