A basic ARM memory system 2000 Addison Wesley

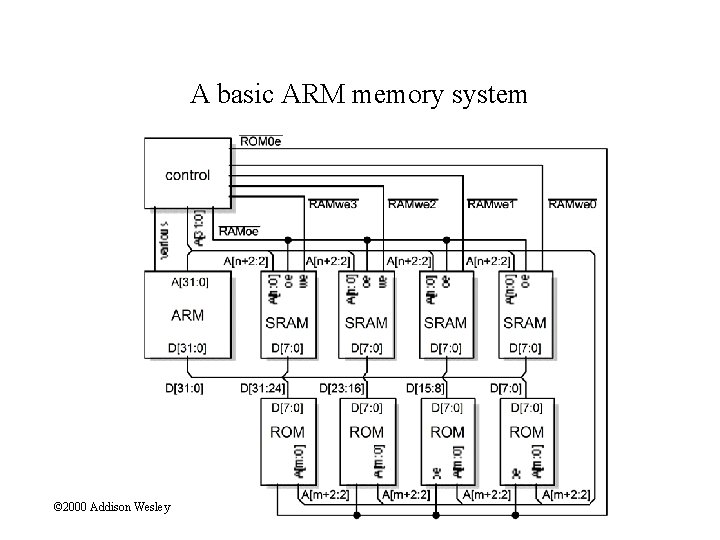

A basic ARM memory system © 2000 Addison Wesley

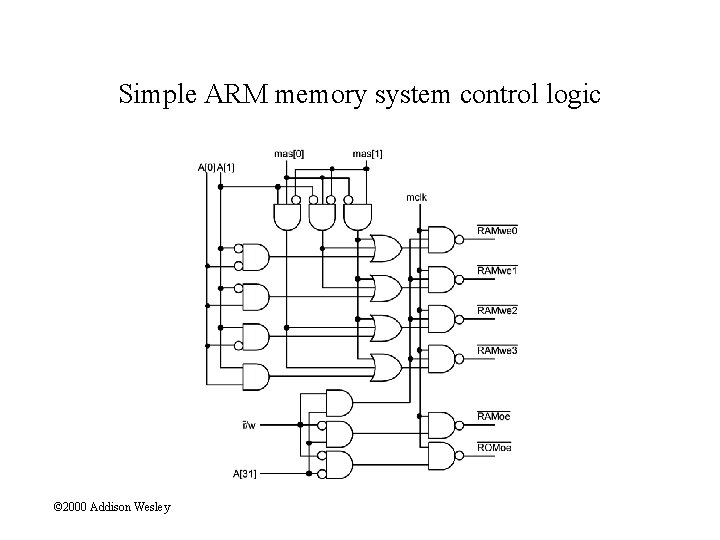

Simple ARM memory system control logic © 2000 Addison Wesley

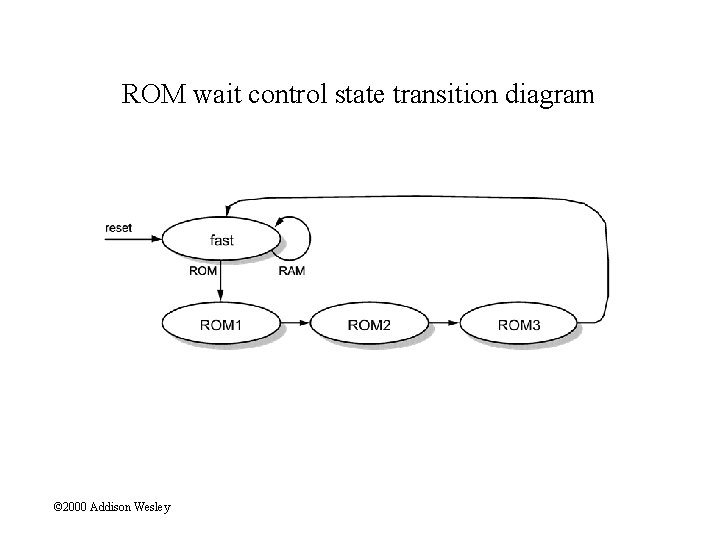

ROM wait control state transition diagram © 2000 Addison Wesley

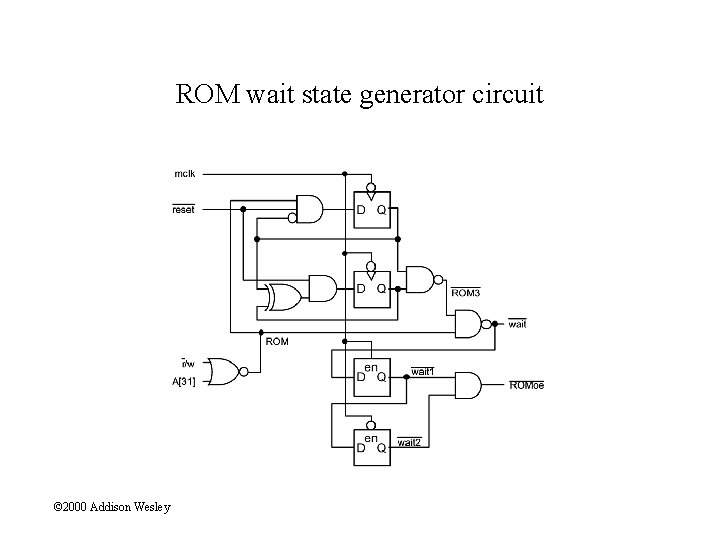

ROM wait state generator circuit © 2000 Addison Wesley

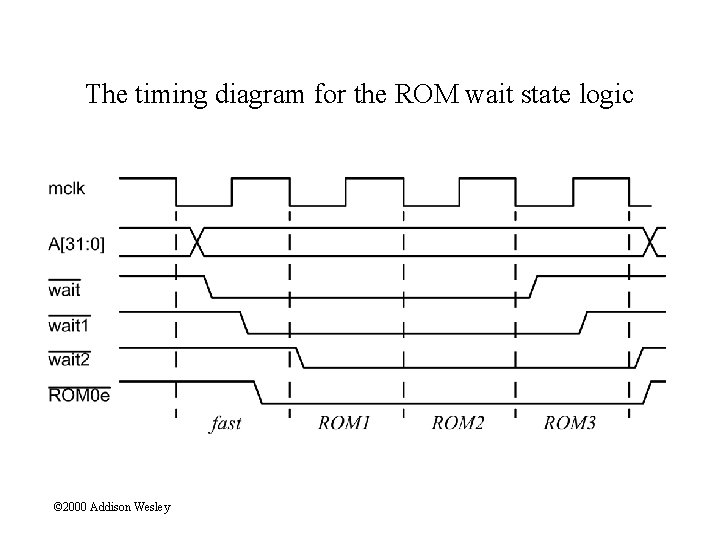

The timing diagram for the ROM wait state logic © 2000 Addison Wesley

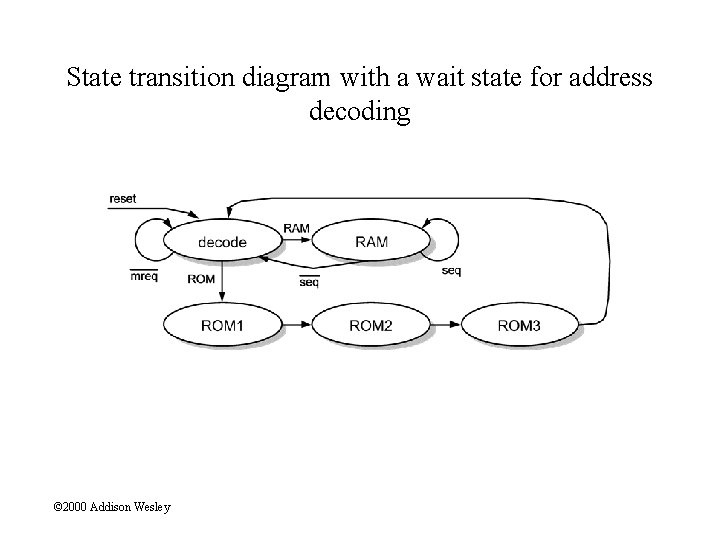

State transition diagram with a wait state for address decoding © 2000 Addison Wesley

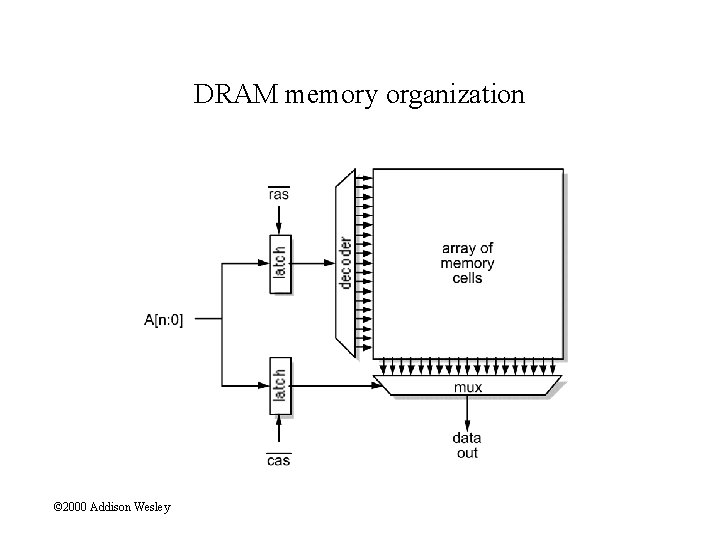

DRAM memory organization © 2000 Addison Wesley

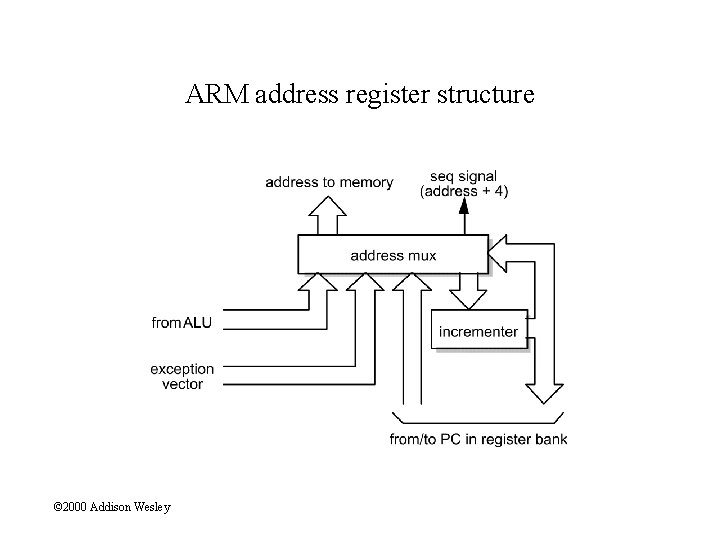

ARM address register structure © 2000 Addison Wesley

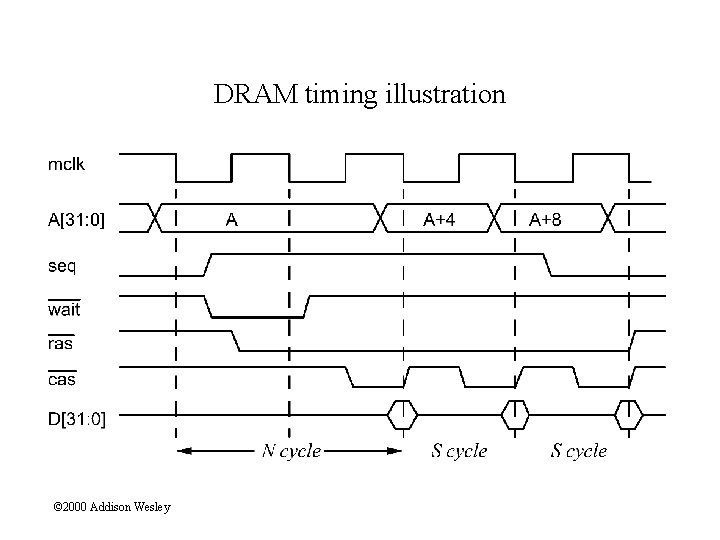

DRAM timing illustration © 2000 Addison Wesley

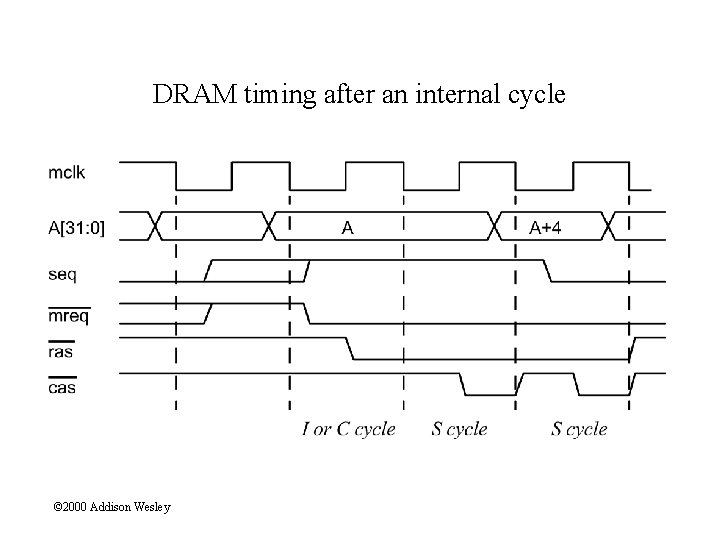

DRAM timing after an internal cycle © 2000 Addison Wesley

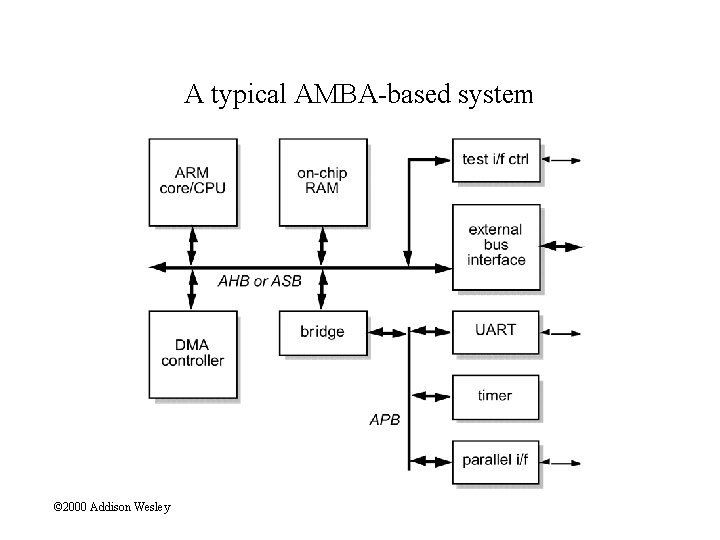

A typical AMBA-based system © 2000 Addison Wesley

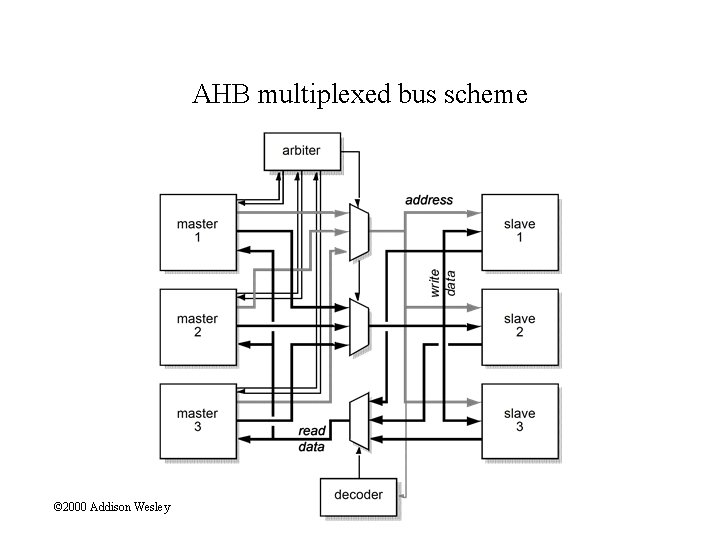

AHB multiplexed bus scheme © 2000 Addison Wesley

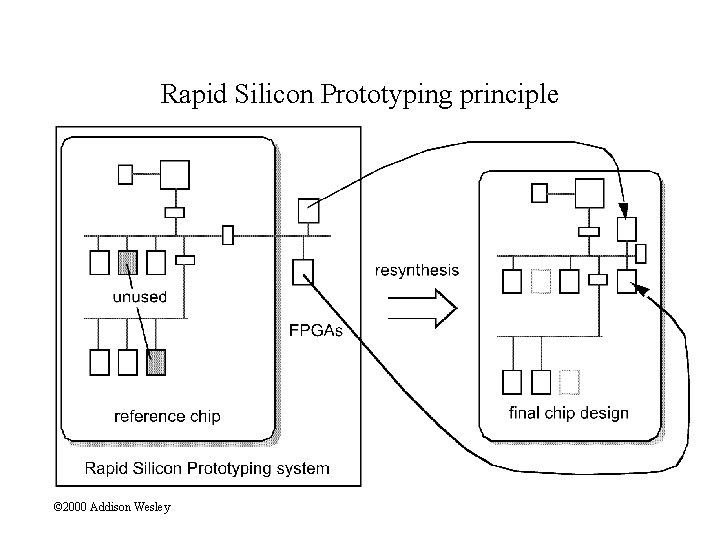

Rapid Silicon Prototyping principle © 2000 Addison Wesley

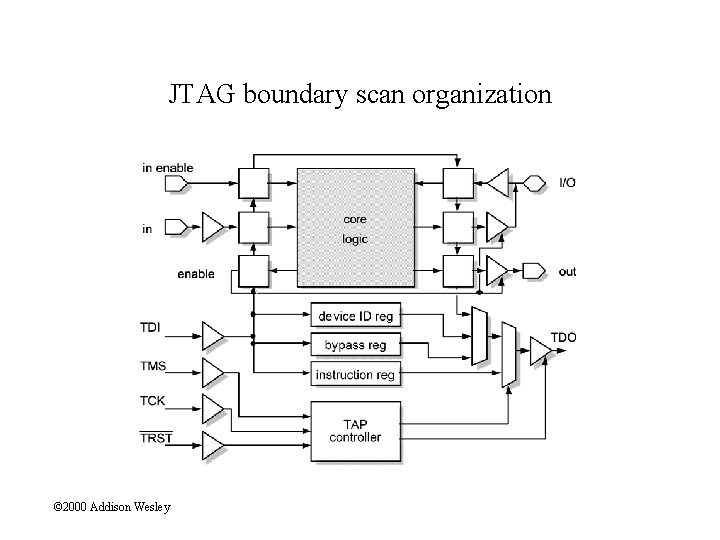

JTAG boundary scan organization © 2000 Addison Wesley

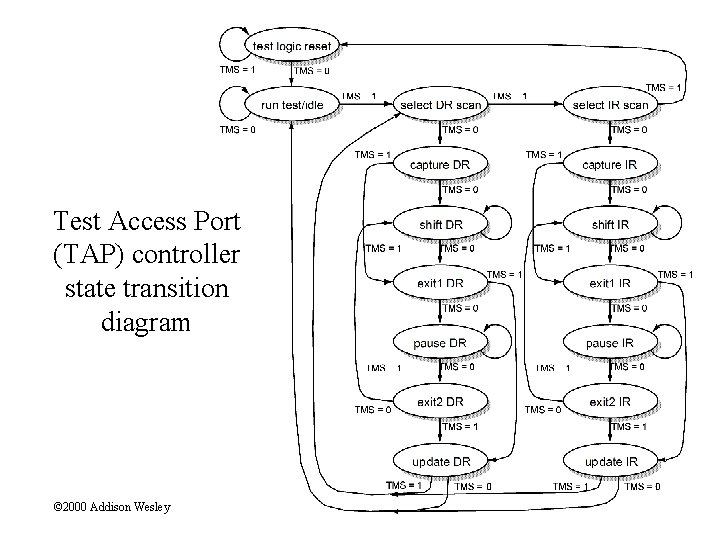

Test Access Port (TAP) controller state transition diagram © 2000 Addison Wesley

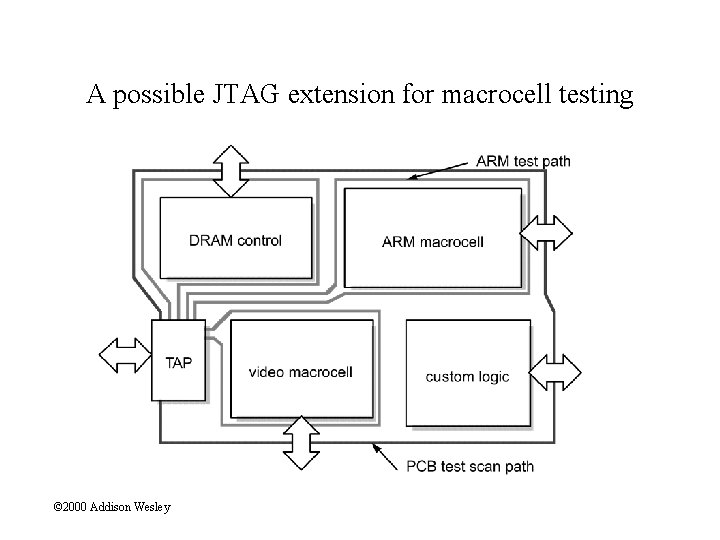

A possible JTAG extension for macrocell testing © 2000 Addison Wesley

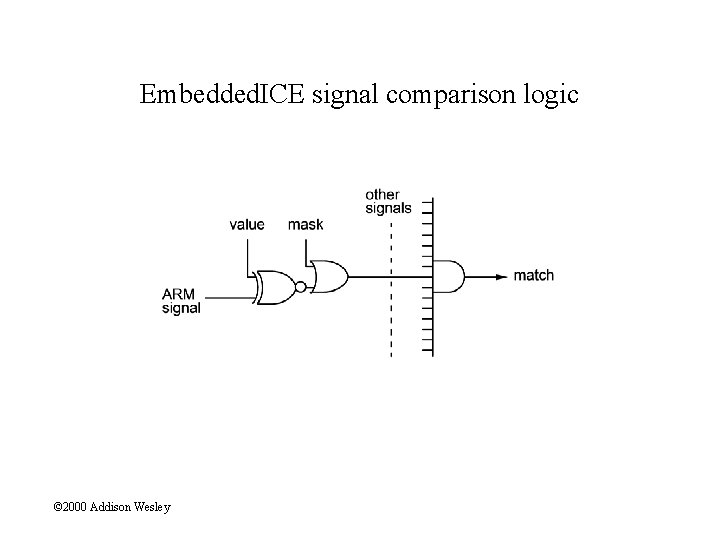

Embedded. ICE signal comparison logic © 2000 Addison Wesley

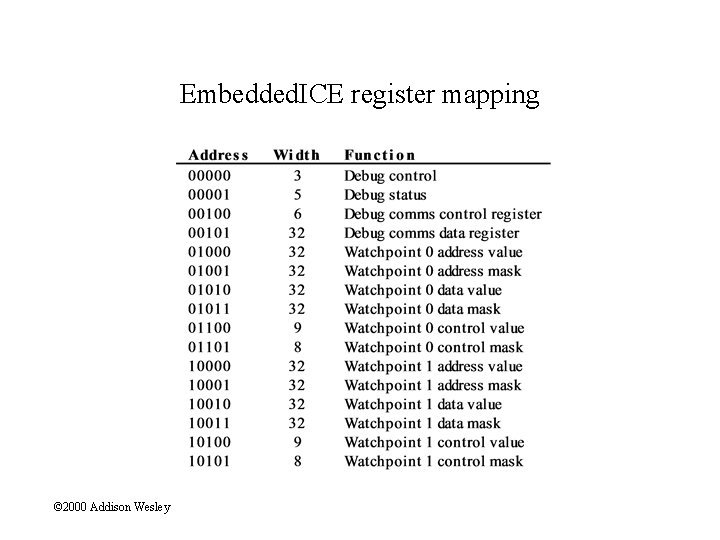

Embedded. ICE register mapping © 2000 Addison Wesley

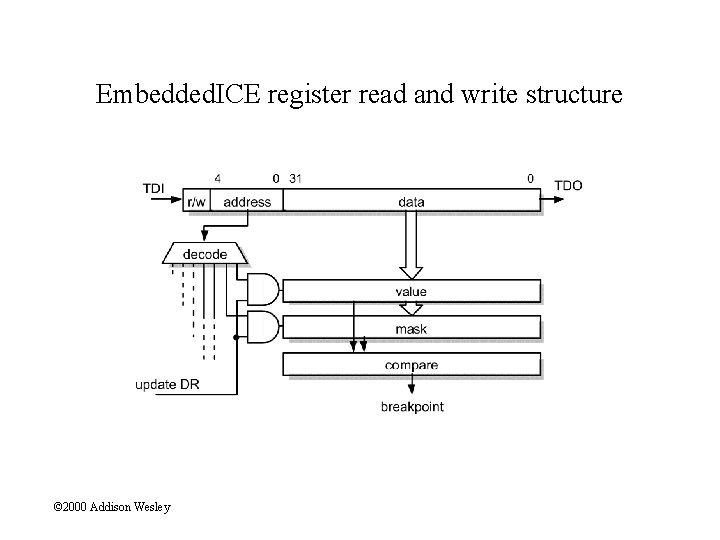

Embedded. ICE register read and write structure © 2000 Addison Wesley

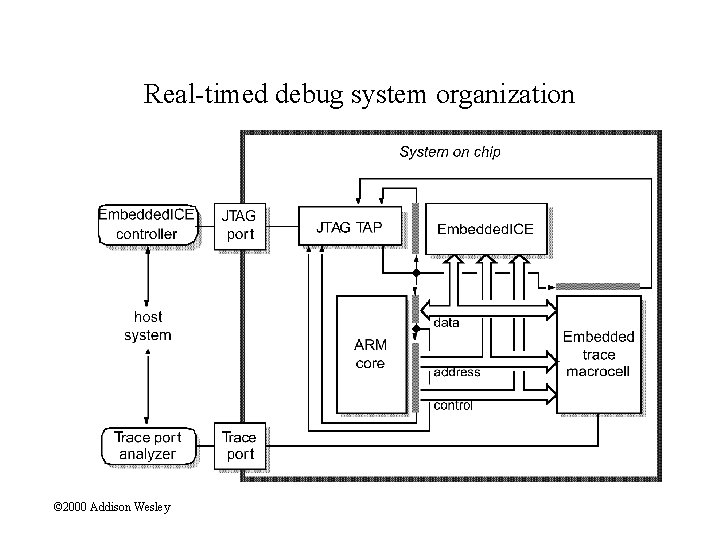

Real-timed debug system organization © 2000 Addison Wesley

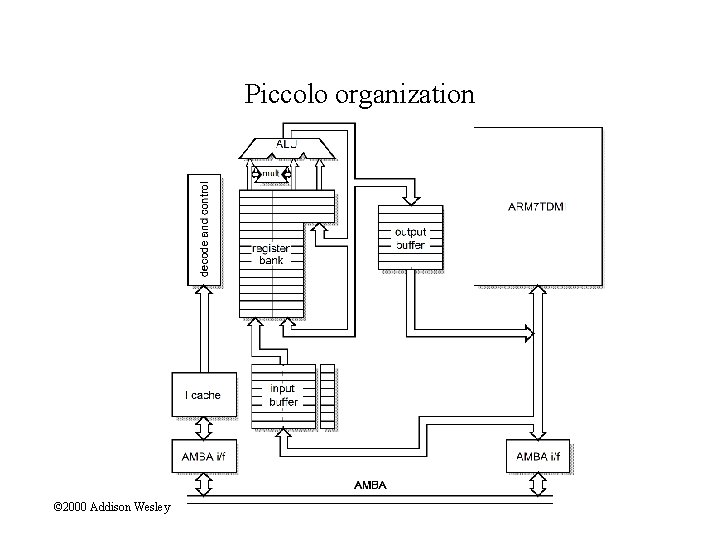

Piccolo organization © 2000 Addison Wesley

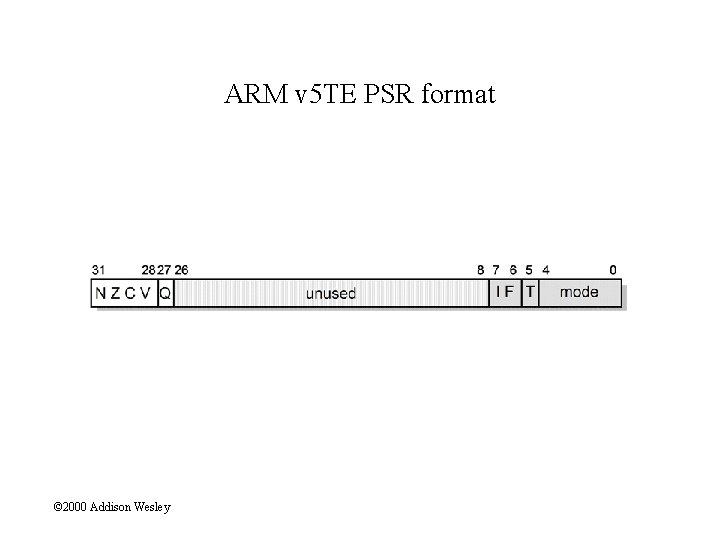

ARM v 5 TE PSR format © 2000 Addison Wesley

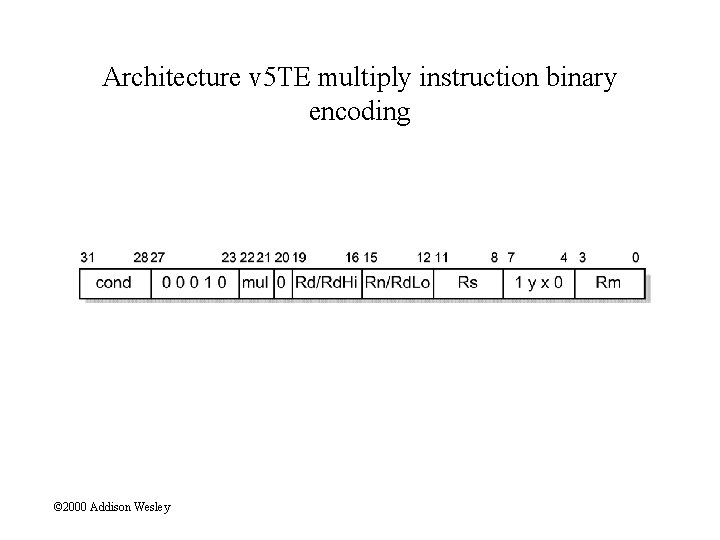

Architecture v 5 TE multiply instruction binary encoding © 2000 Addison Wesley

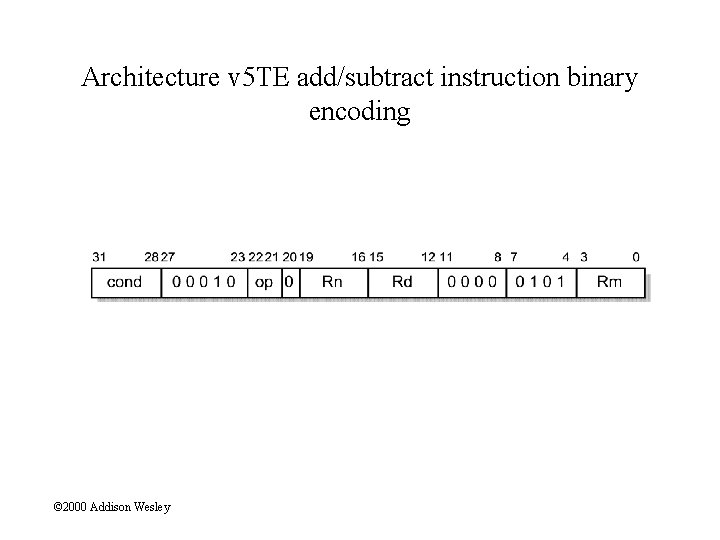

Architecture v 5 TE add/subtract instruction binary encoding © 2000 Addison Wesley

- Slides: 24