a b c Register version unsigned char a

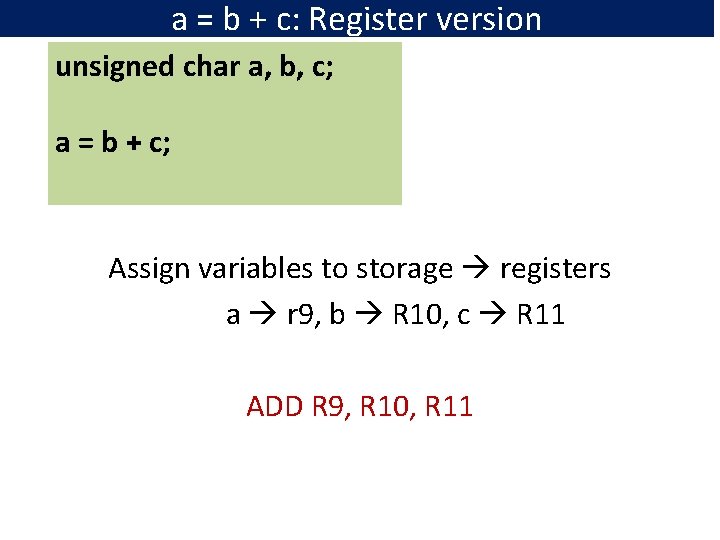

a = b + c: Register version unsigned char a, b, c; a = b + c; Assign variables to storage registers a r 9, b R 10, c R 11 ADD R 9, R 10, R 11

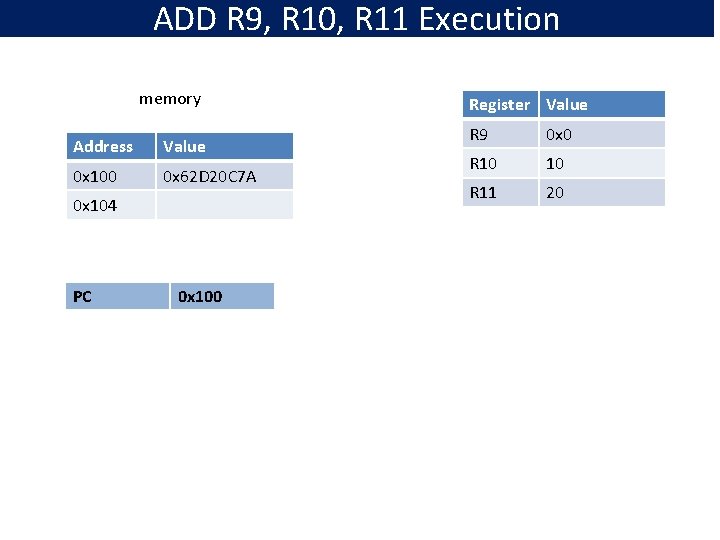

ADD R 9, R 10, R 11 Execution memory Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 PC 0 x 100 Register Value R 9 0 x 0 R 10 10 R 11 20

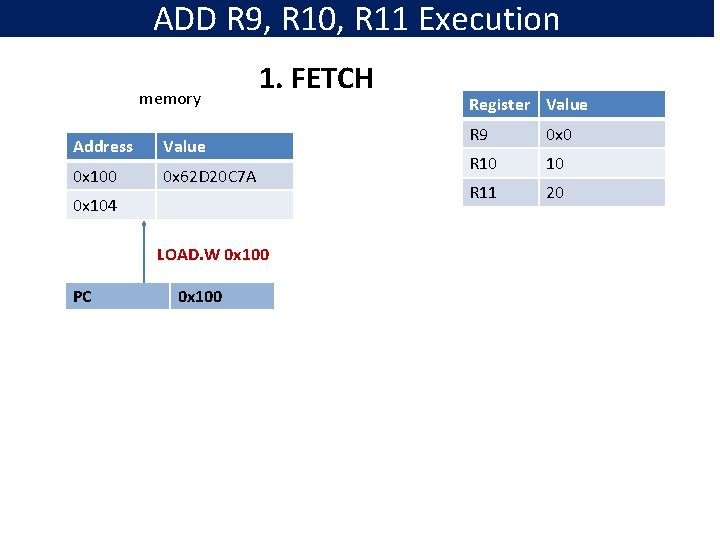

ADD R 9, R 10, R 11 Execution memory Address Value 0 x 100 0 x 62 D 20 C 7 A 1. FETCH 0 x 104 LOAD. W 0 x 100 PC 0 x 100 Register Value R 9 0 x 0 R 10 10 R 11 20

ADD R 9, R 10, R 11 Execution 1. FETCH memory Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 100 0 x 62 D 20 C 7 A Register Value R 9 0 x 0 R 10 10 R 11 20

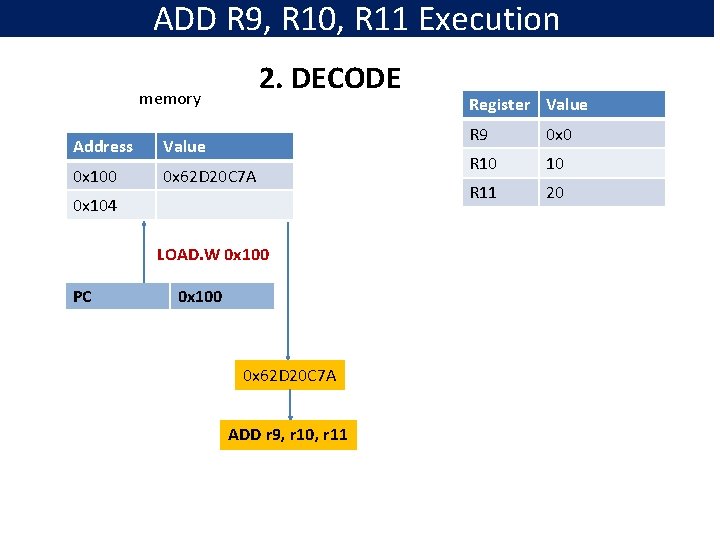

ADD R 9, R 10, R 11 Execution 2. DECODE memory Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 100 0 x 62 D 20 C 7 A ADD r 9, r 10, r 11 Register Value R 9 0 x 0 R 10 10 R 11 20

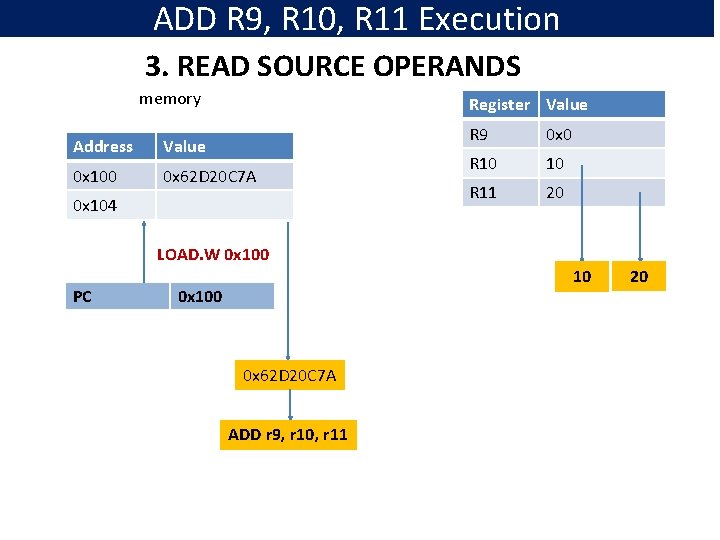

ADD R 9, R 10, R 11 Execution 3. READ SOURCE OPERANDS memory Register Value Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 100 0 x 62 D 20 C 7 A ADD r 9, r 10, r 11 R 9 0 x 0 R 10 10 R 11 20 10 20

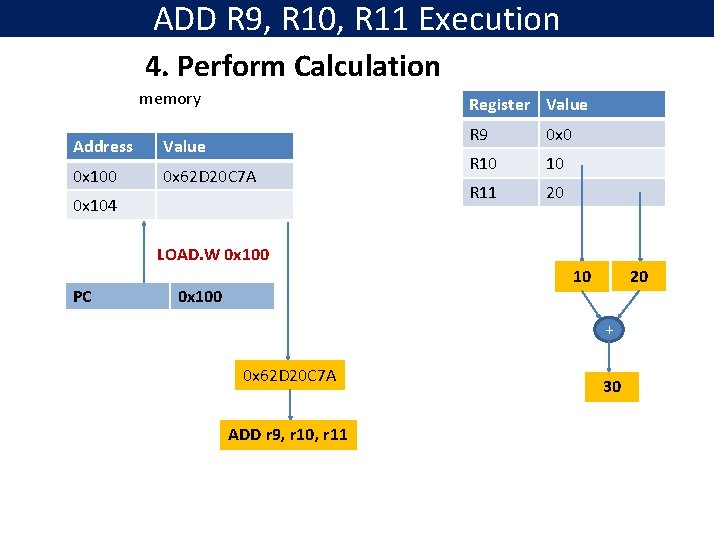

ADD R 9, R 10, R 11 Execution 4. Perform Calculation memory Register Value Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 100 R 9 0 x 0 R 10 10 R 11 20 20 10 + 0 x 62 D 20 C 7 A ADD r 9, r 10, r 11 30

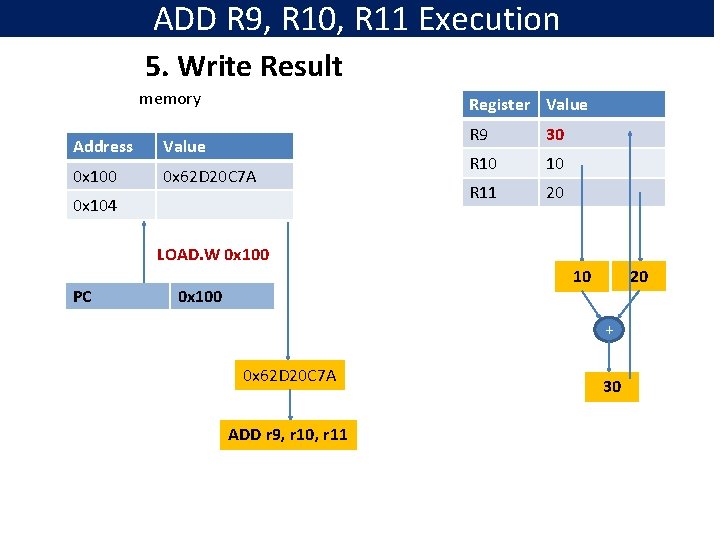

ADD R 9, R 10, R 11 Execution 5. Write Result memory Register Value Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 100 R 9 30 R 10 10 R 11 20 20 10 + 0 x 62 D 20 C 7 A ADD r 9, r 10, r 11 30

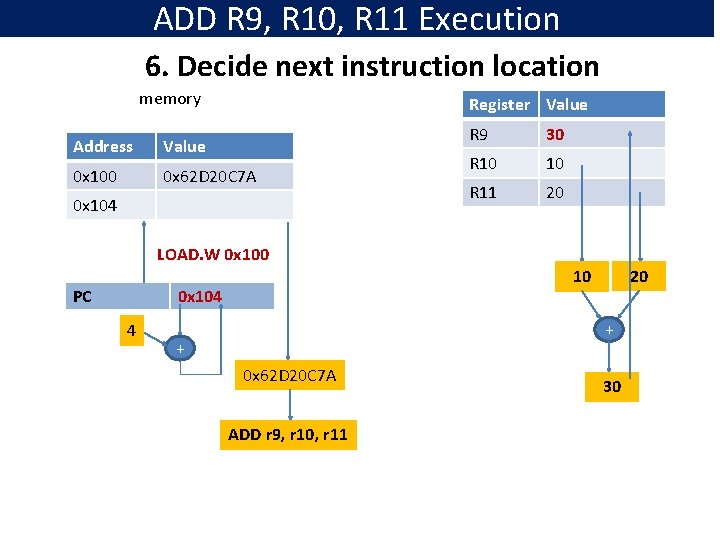

ADD R 9, R 10, R 11 Execution 6. Decide next instruction location memory Register Value Address Value 0 x 100 0 x 62 D 20 C 7 A 0 x 104 LOAD. W 0 x 100 PC 0 x 104 4 R 9 30 R 10 10 R 11 20 20 10 + + 0 x 62 D 20 C 7 A ADD r 9, r 10, r 11 30

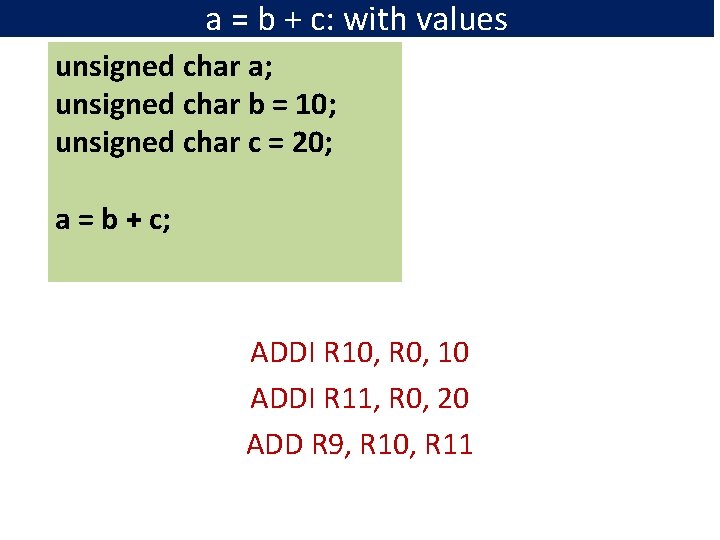

a = b + c: with values unsigned char a; unsigned char b = 10; unsigned char c = 20; a = b + c; ADDI R 10, R 0, 10 ADDI R 11, R 0, 20 ADD R 9, R 10, R 11

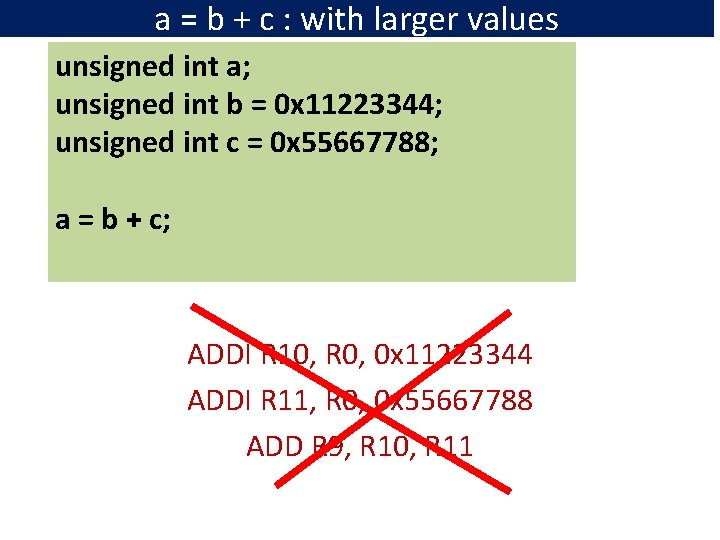

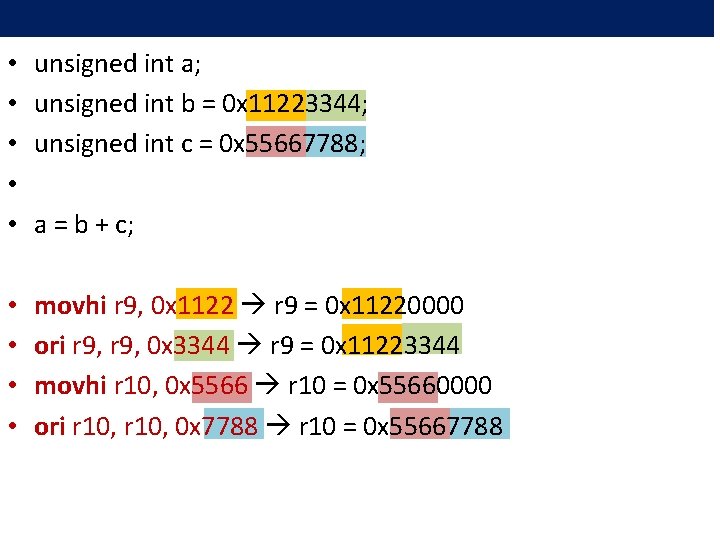

a = b + c : with larger values unsigned int a; unsigned int b = 0 x 11223344; unsigned int c = 0 x 55667788; a = b + c; ADDI R 10, R 0, 0 x 11223344 ADDI R 11, R 0, 0 x 55667788 ADD R 9, R 10, R 11

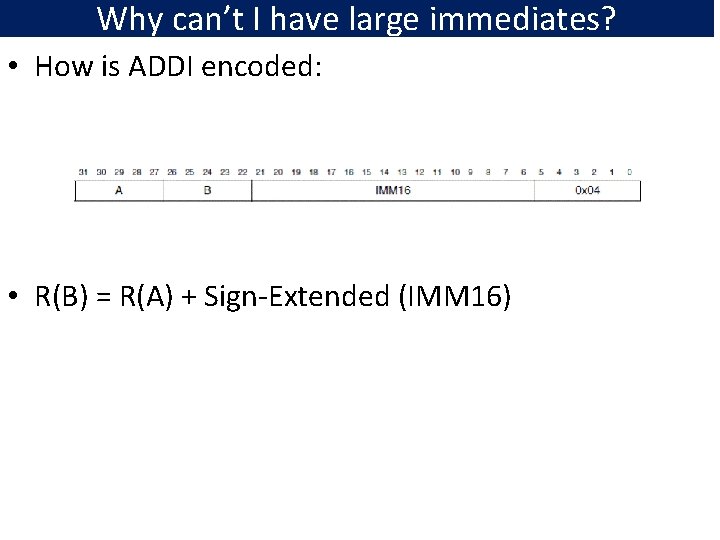

Why can’t I have large immediates? • How is ADDI encoded: • R(B) = R(A) + Sign-Extended (IMM 16)

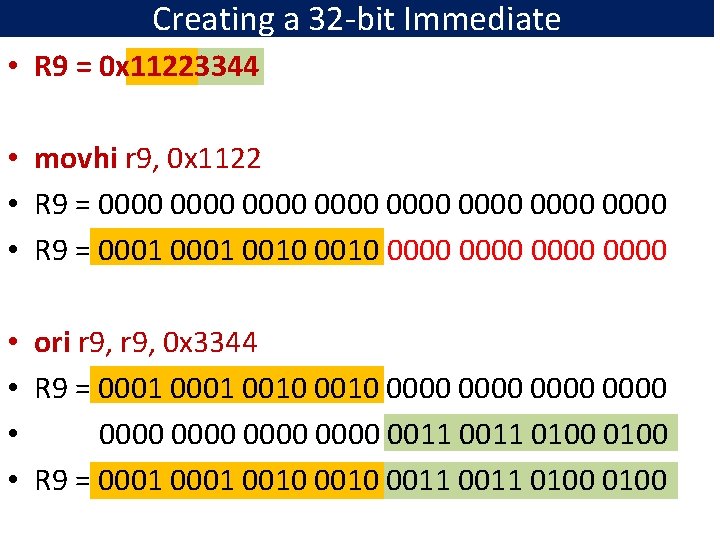

Creating a 32 -bit Immediate • R 9 = 0 x 11223344 • movhi r 9, 0 x 1122 • R 9 = 0000 0000 • R 9 = 0001 0010 0000 • ori r 9, 0 x 3344 • R 9 = 0001 0010 0000 • 0000 0011 0100 • R 9 = 0001 0010 0011 0100

• • • unsigned int a; unsigned int b = 0 x 11223344; unsigned int c = 0 x 55667788; • • movhi r 9, 0 x 1122 r 9 = 0 x 11220000 ori r 9, 0 x 3344 r 9 = 0 x 11223344 movhi r 10, 0 x 5566 r 10 = 0 x 55660000 ori r 10, 0 x 7788 r 10 = 0 x 55667788 a = b + c;

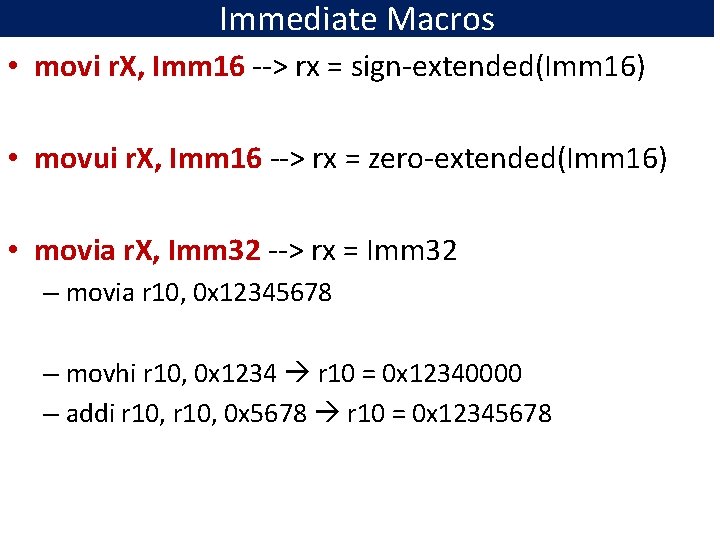

Immediate Macros • movi r. X, Imm 16 --> rx = sign-extended(Imm 16) • movui r. X, Imm 16 --> rx = zero-extended(Imm 16) • movia r. X, Imm 32 --> rx = Imm 32 – movia r 10, 0 x 12345678 – movhi r 10, 0 x 1234 r 10 = 0 x 12340000 – addi r 10, 0 x 5678 r 10 = 0 x 12345678

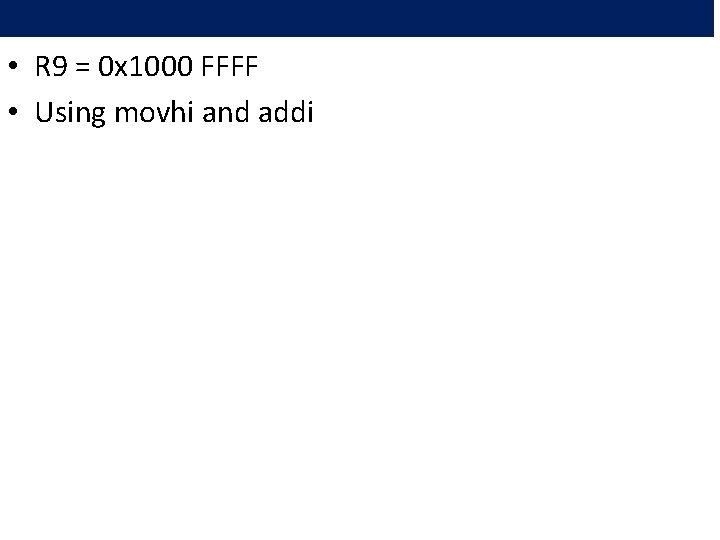

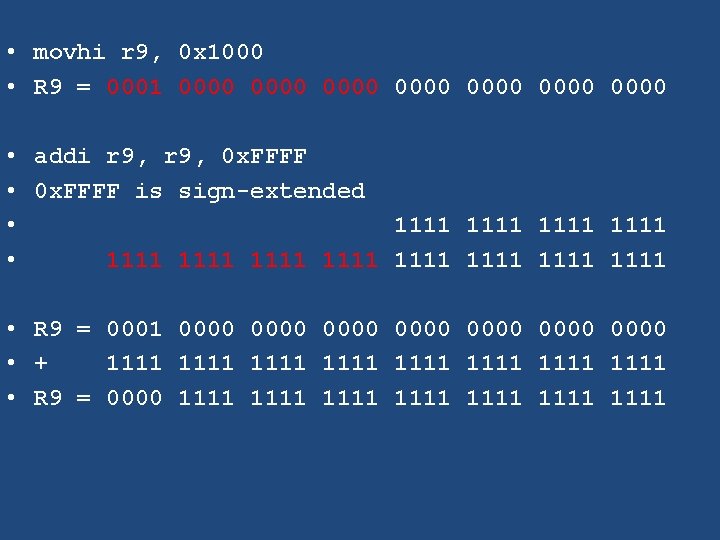

• R 9 = 0 x 1000 FFFF • Using movhi and addi

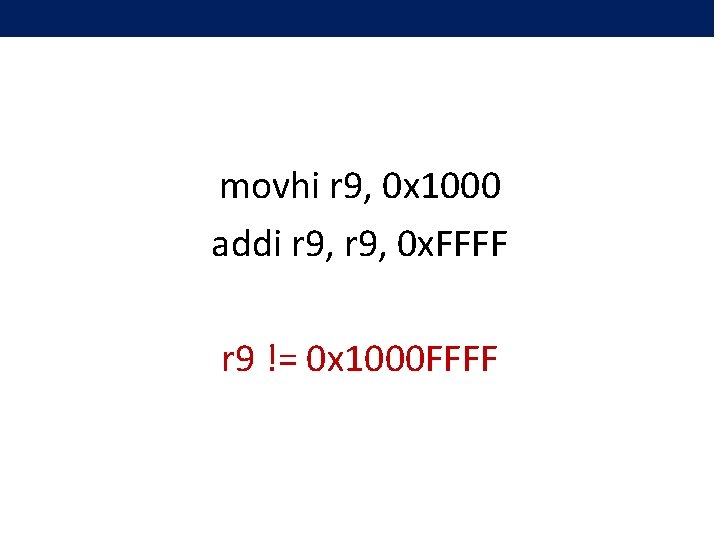

movhi r 9, 0 x 1000 addi r 9, 0 x. FFFF r 9 != 0 x 1000 FFFF

• movhi r 9, 0 x 1000 • R 9 = 0001 0000 0000 • addi r 9, 0 x. FFFF • 0 x. FFFF is sign-extended • 1111 1111 1111 • R 9 = 0001 0000 0000 • + 1111 1111 • R 9 = 0000 1111 1111

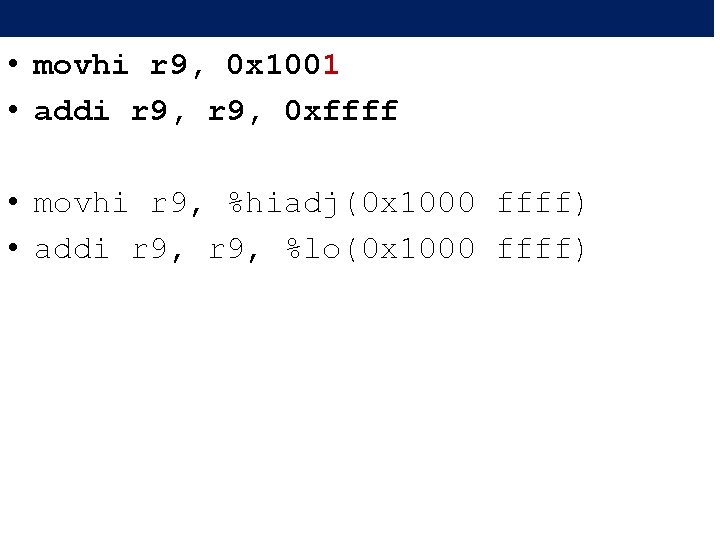

• movhi r 9, 0 x 1001 • addi r 9, 0 xffff • movhi r 9, %hiadj(0 x 1000 ffff) • addi r 9, %lo(0 x 1000 ffff)

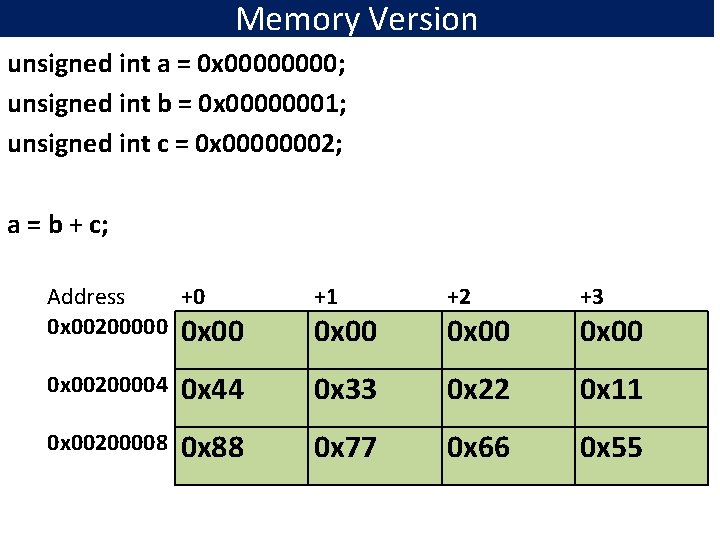

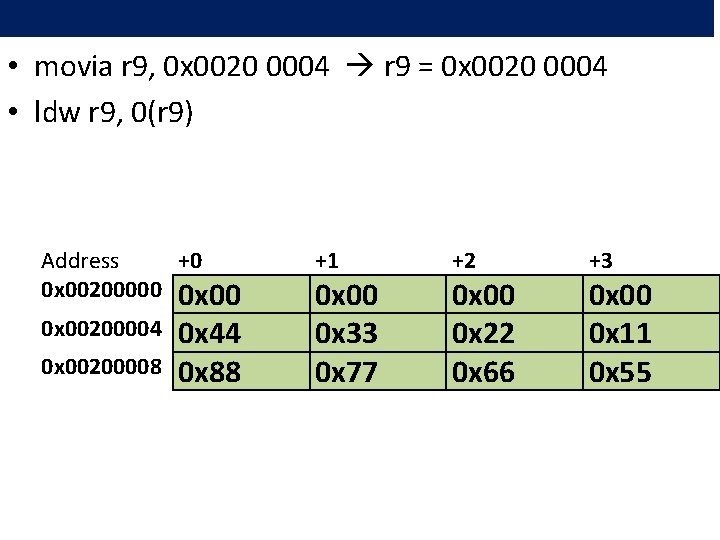

Memory Version unsigned int a = 0 x 0000; unsigned int b = 0 x 00000001; unsigned int c = 0 x 00000002; a = b + c; Address +0 0 x 00200000 0 x 00 +1 +2 +3 0 x 00200004 0 x 44 0 x 33 0 x 22 0 x 11 0 x 00200008 0 x 88 0 x 77 0 x 66 0 x 55

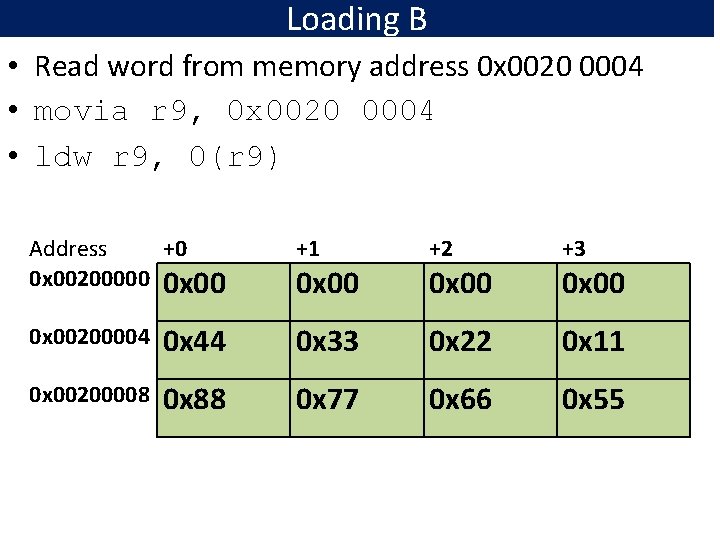

Loading B • Read word from memory address 0 x 0020 0004 • movia r 9, 0 x 0020 0004 • ldw r 9, 0(r 9) Address +0 0 x 00200000 0 x 00 +1 +2 +3 0 x 00200004 0 x 44 0 x 33 0 x 22 0 x 11 0 x 00200008 0 x 88 0 x 77 0 x 66 0 x 55

• movia r 9, 0 x 0020 0004 r 9 = 0 x 0020 0004 • ldw r 9, 0(r 9) Address +0 0 x 00200000 0 x 00200004 0 x 00200008 0 x 44 0 x 88 +1 0 x 00 0 x 33 0 x 77 +2 0 x 00 0 x 22 0 x 66 +3 0 x 00 0 x 11 0 x 55

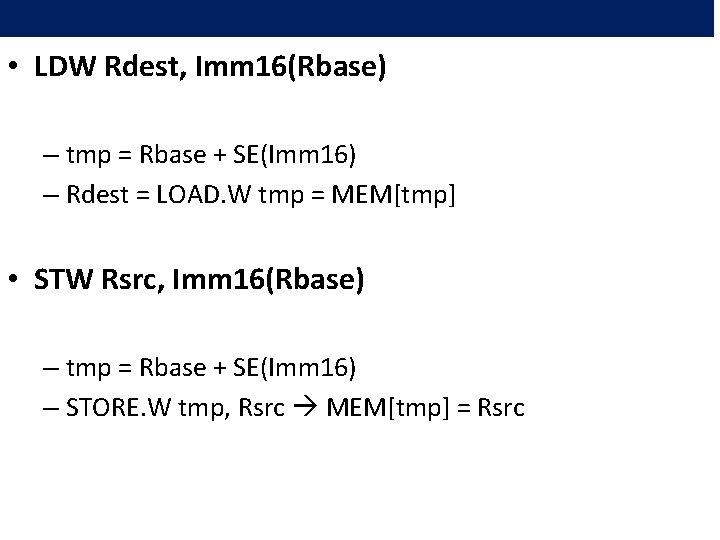

• LDW Rdest, Imm 16(Rbase) – tmp = Rbase + SE(Imm 16) – Rdest = LOAD. W tmp = MEM[tmp] • STW Rsrc, Imm 16(Rbase) – tmp = Rbase + SE(Imm 16) – STORE. W tmp, Rsrc MEM[tmp] = Rsrc

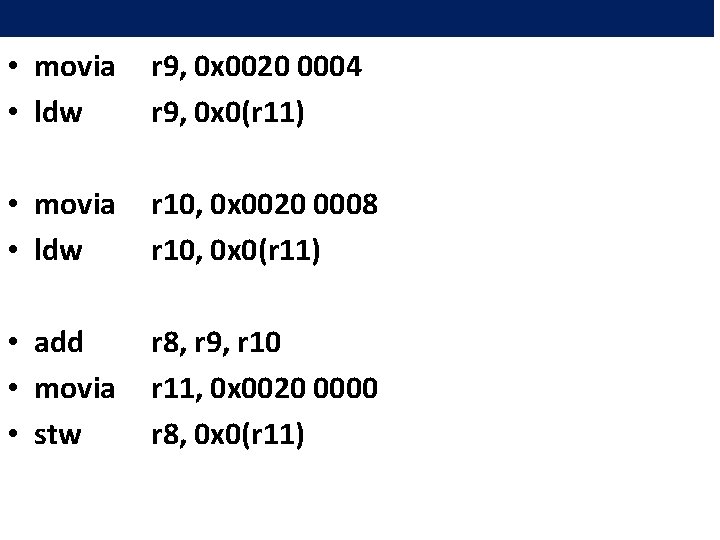

• movia • ldw r 9, 0 x 0020 0004 r 9, 0 x 0(r 11) • movia • ldw r 10, 0 x 0020 0008 r 10, 0 x 0(r 11) • add • movia • stw r 8, r 9, r 10 r 11, 0 x 0020 0000 r 8, 0 x 0(r 11)

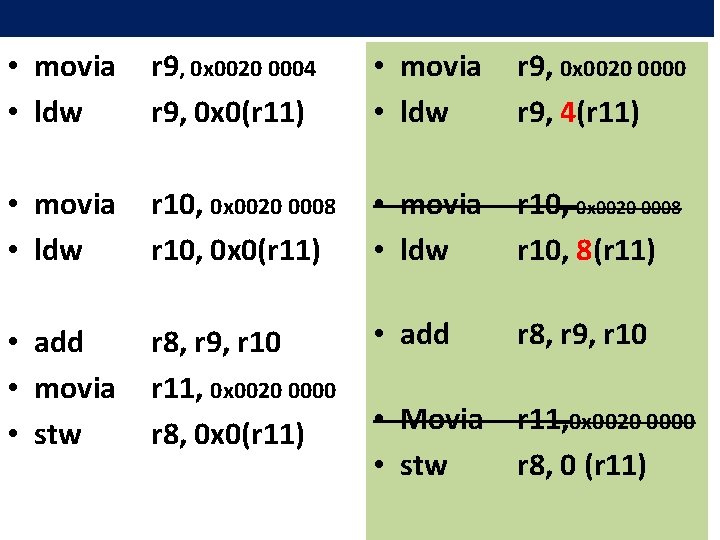

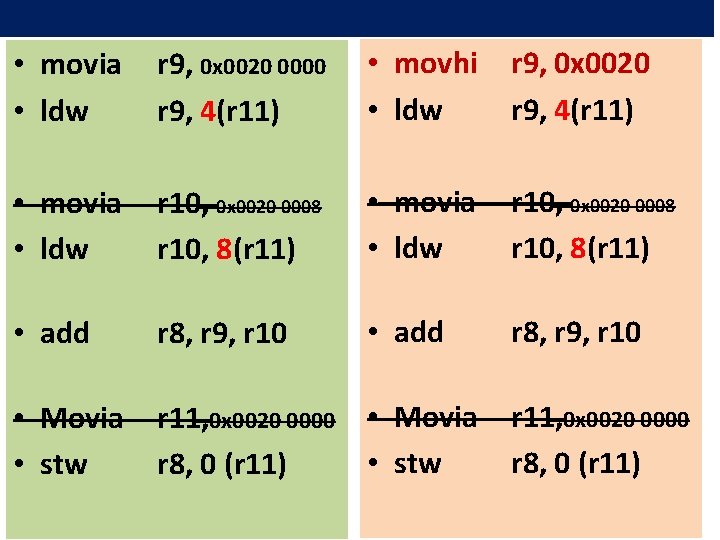

• movia • ldw r 9, 0 x 0020 0004 r 9, 0 x 0(r 11) • movia • ldw r 9, 0 x 0020 0000 r 9, 4(r 11) • movia • ldw r 10, 0 x 0020 0008 r 10, 0 x 0(r 11) • movia • ldw r 10, 0 x 0020 0008 r 10, 8(r 11) • add • movia • stw r 8, r 9, r 10 r 11, 0 x 0020 0000 r 8, 0 x 0(r 11) • add r 8, r 9, r 10 • Movia • stw r 11, 0 x 0020 0000 r 8, 0 (r 11)

• movia • ldw r 9, 0 x 0020 0000 r 9, 4(r 11) • movhi • ldw r 9, 0 x 0020 r 9, 4(r 11) • movia • ldw r 10, 0 x 0020 0008 r 10, 8(r 11) • add r 8, r 9, r 10 • Movia • stw r 11, 0 x 0020 0000 r 8, 0 (r 11)

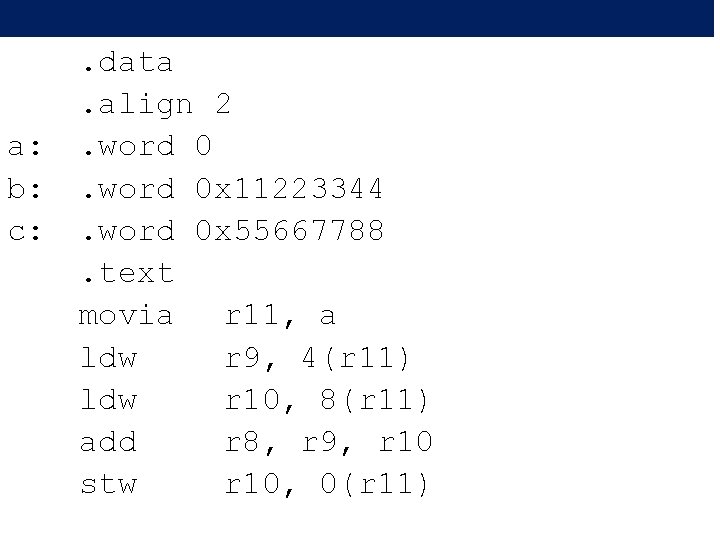

a: b: c: . data. align 2. word 0 x 11223344. word 0 x 55667788. text movia r 11, a ldw r 9, 4(r 11) ldw r 10, 8(r 11) add r 8, r 9, r 10 stw r 10, 0(r 11)

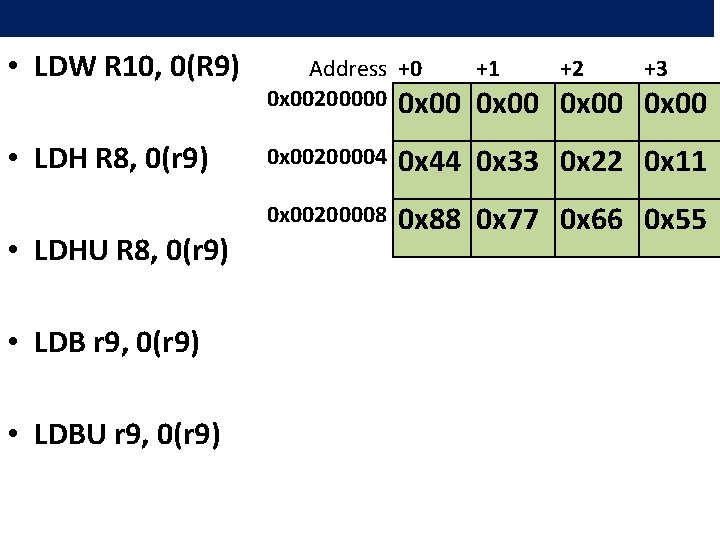

• LDW R 10, 0(R 9) Address +0 +1 +2 +3 0 x 00200000 0 x 00 • LDH R 8, 0(r 9) 0 x 00200004 0 x 44 0 x 33 0 x 22 0 x 11 0 x 00200008 0 x 88 0 x 77 0 x 66 0 x 55 • LDHU R 8, 0(r 9) • LDB r 9, 0(r 9) • LDBU r 9, 0(r 9)

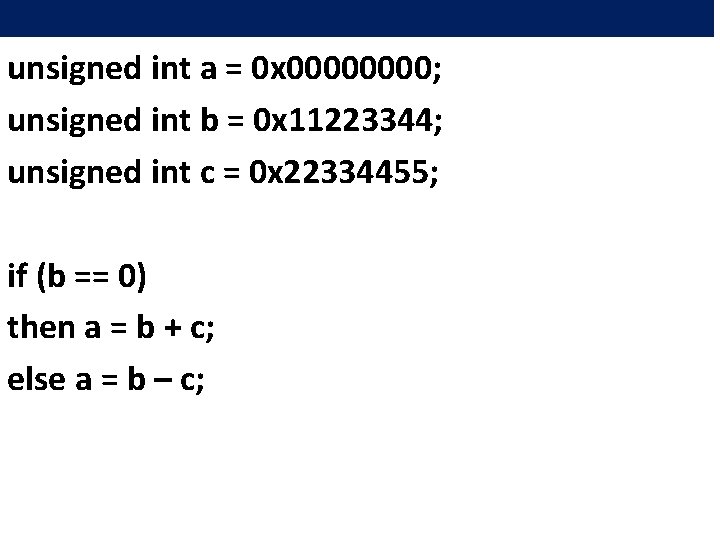

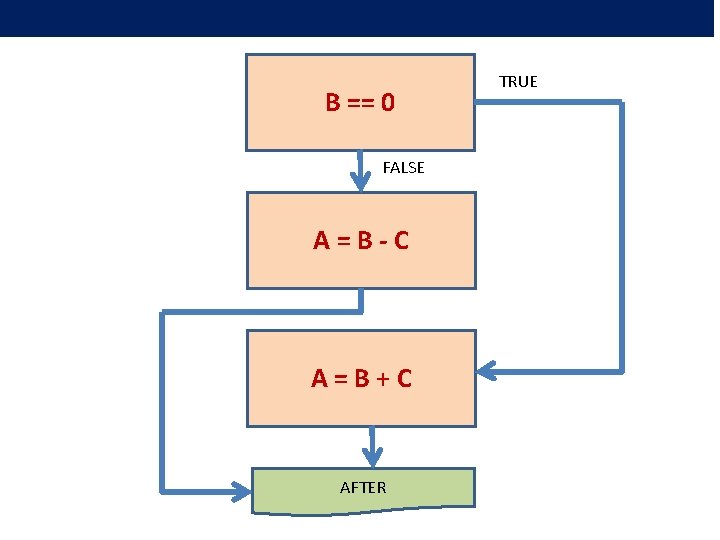

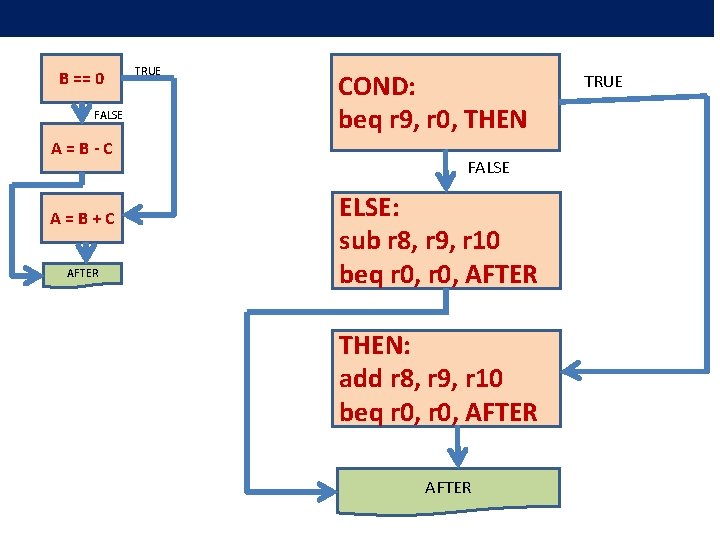

unsigned int a = 0 x 0000; unsigned int b = 0 x 11223344; unsigned int c = 0 x 22334455; if (b == 0) then a = b + c; else a = b – c;

B == 0 FALSE A=B-C A=B+C AFTER TRUE

B == 0 FALSE A=B-C A=B+C AFTER TRUE COND: beq r 9, r 0, THEN FALSE ELSE: sub r 8, r 9, r 10 beq r 0, AFTER THEN: add r 8, r 9, r 10 beq r 0, AFTER TRUE

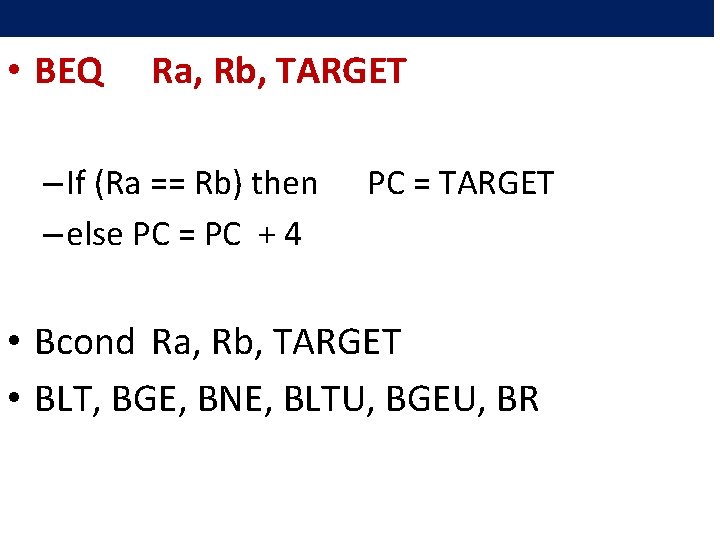

• BEQ Ra, Rb, TARGET – If (Ra == Rb) then – else PC = PC + 4 PC = TARGET • Bcond Ra, Rb, TARGET • BLT, BGE, BNE, BLTU, BGEU, BR

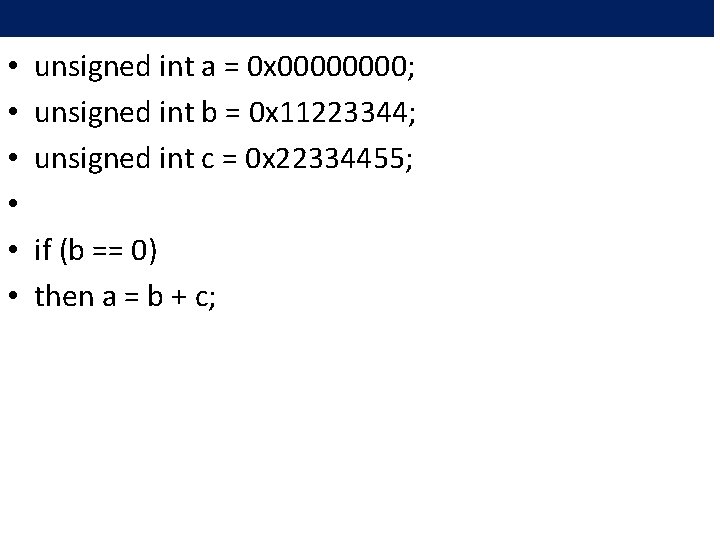

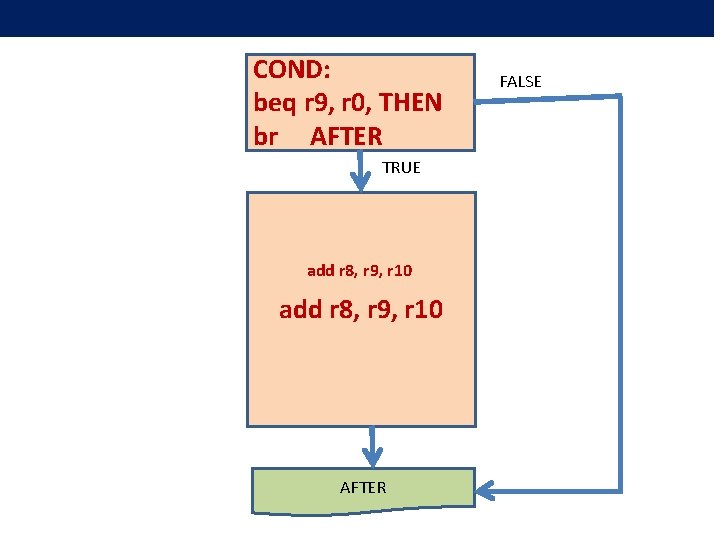

• • • unsigned int a = 0 x 0000; unsigned int b = 0 x 11223344; unsigned int c = 0 x 22334455; if (b == 0) then a = b + c;

COND: beq r 9, r 0, THEN br AFTER TRUE add r 8, r 9, r 10 AFTER FALSE

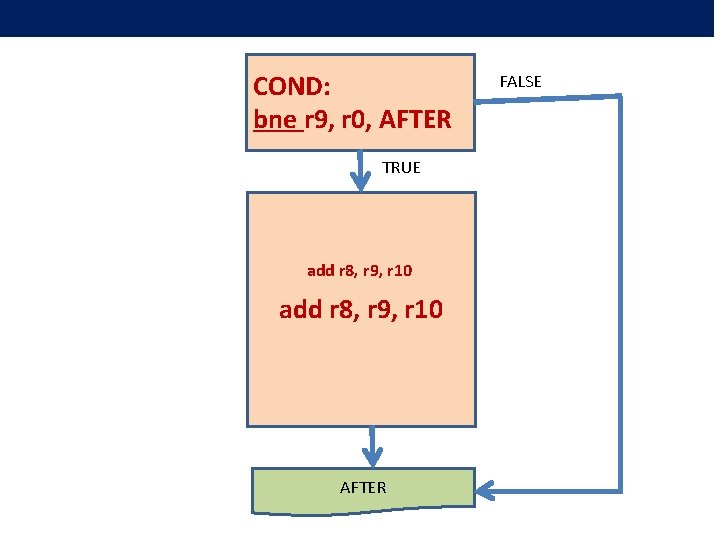

COND: bne r 9, r 0, AFTER TRUE add r 8, r 9, r 10 AFTER FALSE

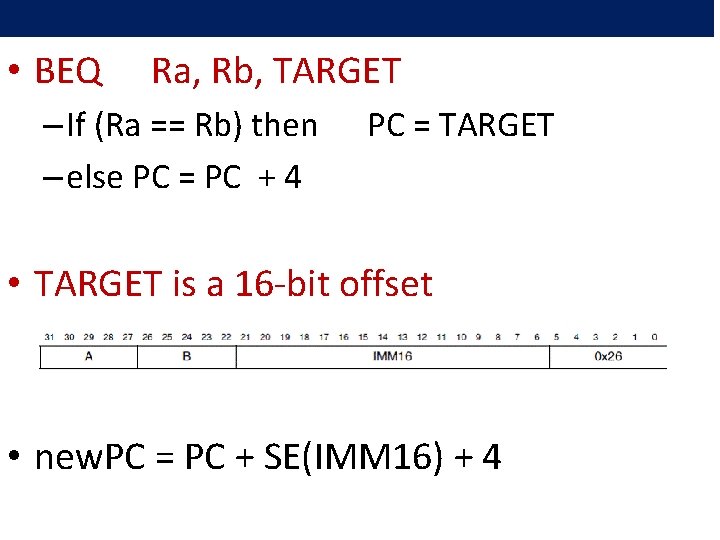

• BEQ Ra, Rb, TARGET – If (Ra == Rb) then – else PC = PC + 4 PC = TARGET • TARGET is a 16 -bit offset • new. PC = PC + SE(IMM 16) + 4

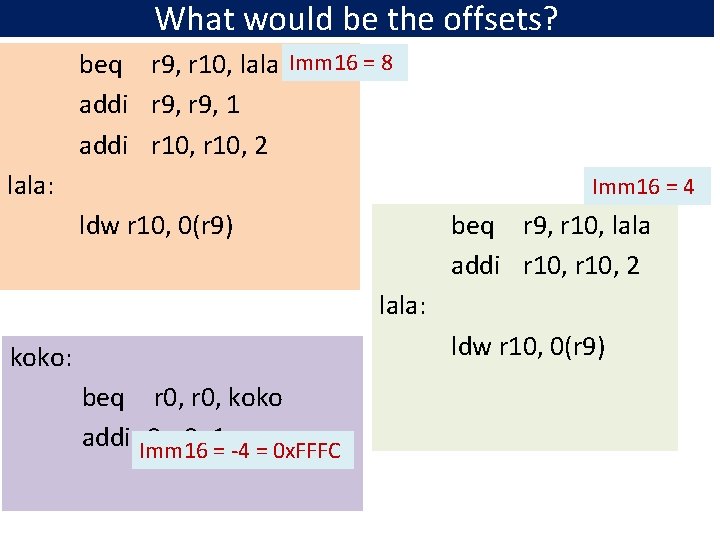

What would be the offsets? beq r 9, r 10, lala Imm 16 = 8 addi r 9, 1 addi r 10, 2 lala: Imm 16 = 4 beq r 9, r 10, lala addi r 10, 2 ldw r 10, 0(r 9) lala: ldw r 10, 0(r 9) koko: beq r 0, koko addi r 9, 1= -4 = 0 x. FFFC Imm 16

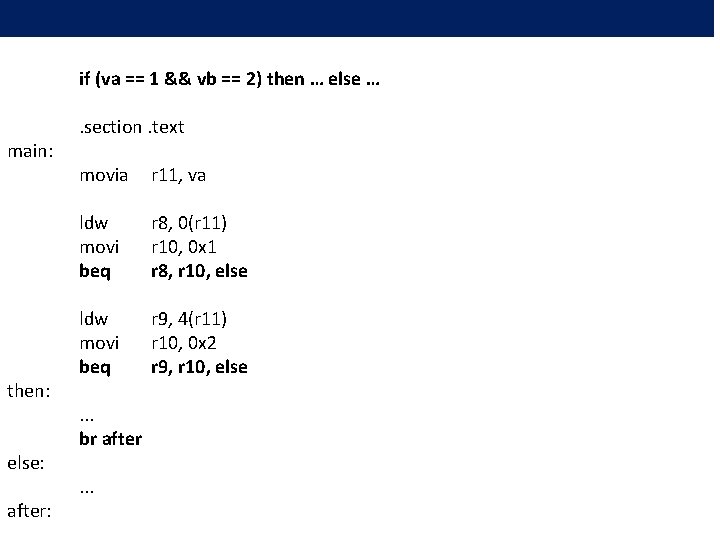

if (va == 1 && vb == 2) then … else … main: then: else: after: . section. text movia r 11, va ldw movi beq r 8, 0(r 11) r 10, 0 x 1 r 8, r 10, else ldw movi beq r 9, 4(r 11) r 10, 0 x 2 r 9, r 10, else . . . br after. . .

- Slides: 38