A 2 GHz Direct Sampling Tunable Receiver with

A 2 -GHz Direct Sampling ΔΣ Tunable Receiver with 40 -GHz Sampling Clock and on-chip PLL T. Chalvatzis 1, T. O. Dickson 1, 2 and S. P. Voinigescu 1 University of Toronto, CA 2 now with IBM T. J. Watson Research Center, NY, USA 1

Outline of Presentation • Motivation • Circuit design – Loop filter – PLL • Measurement results • Summary

Motivation • Direct sampling receiver for 2 -GHz radio with 60 MHz BW – CT BP ΔΣ ADC with SNDR of 55 d. B/60 MHz [Chalvatzis et al. , JSSC, May 2007] – Investigation of clock jitter impact with on-chip clock source

System Architecture • 2 -GHz Gm-LC BPF • Fourth order loop • 1 -bit quantizer as DFF with FCLK=40 GHz • RZ pulse DACs • 40 -GHz VCO/PLL

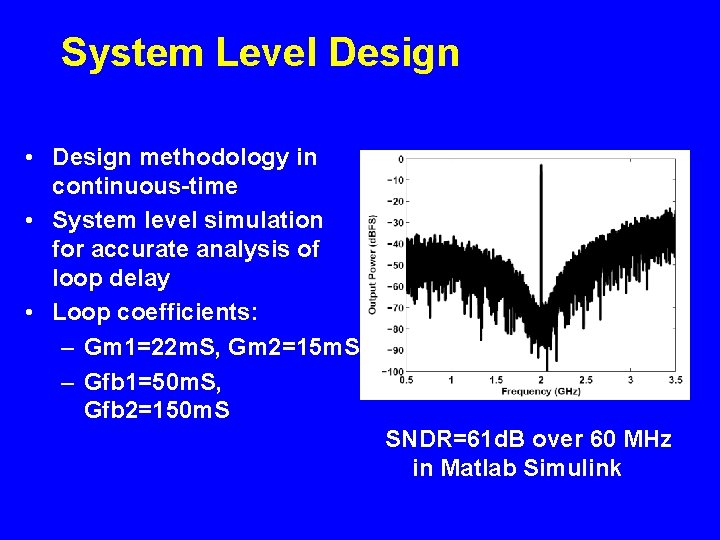

System Level Design • Design methodology in continuous-time • System level simulation for accurate analysis of loop delay • Loop coefficients: – Gm 1=22 m. S, Gm 2=15 m. S – Gfb 1=50 m. S, Gfb 2=150 m. S SNDR=61 d. B over 60 MHz in Matlab Simulink

![SNR vs clock jitter Δ: quantizer step [Ortmanns et al. , ISCAS 2003] • SNR vs clock jitter Δ: quantizer step [Ortmanns et al. , ISCAS 2003] •](http://slidetodoc.com/presentation_image_h2/4729ecfc716e0bbe16527eb3d667cd18/image-6.jpg)

SNR vs clock jitter Δ: quantizer step [Ortmanns et al. , ISCAS 2003] • Clock jitter effect simulated for FS=40 GHz, OSR=333 • PLL jitter < 1. 4 ps (rms) for 10 bits resolution

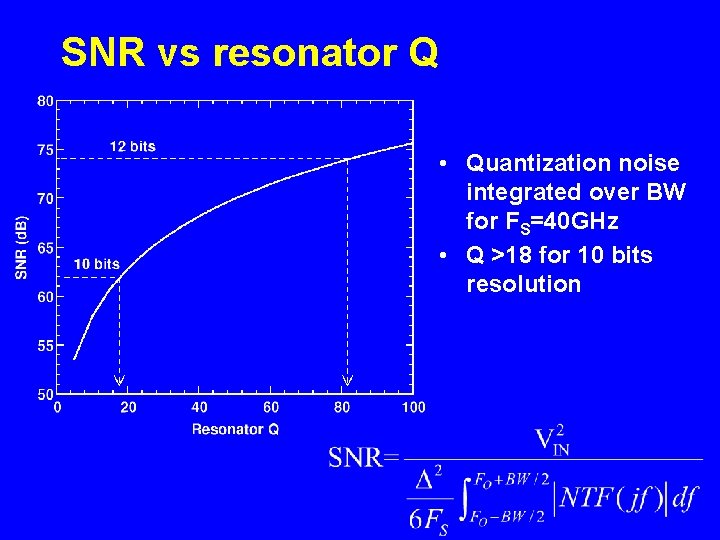

SNR vs resonator Q • Quantization noise integrated over BW for FS=40 GHz • Q >18 for 10 bits resolution

Loop Filter • MOS-HBT cascode for high linearity and low noise • EF limit voltage headroom, current source adds noise Loop filter with EF

Modified Loop Filter • MOS-HBT cascode for high linearity and low noise • EF limit voltage headroom, current source adds noise Modified Loop Filter

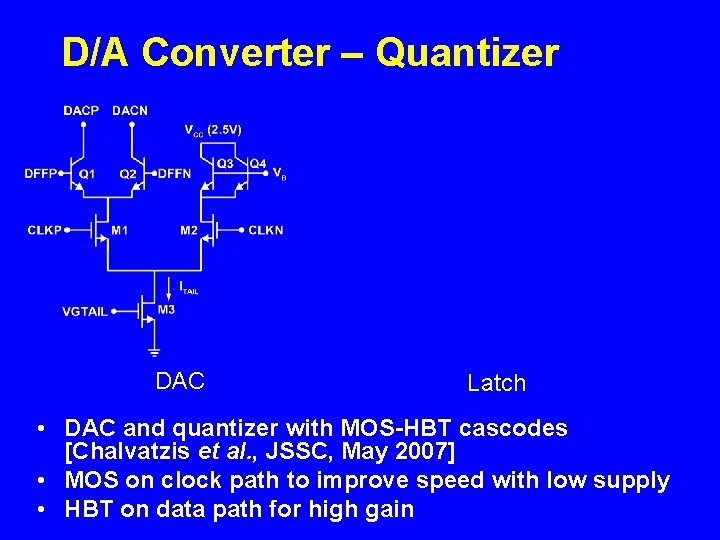

D/A Converter – Quantizer DAC Latch • DAC and quantizer with MOS-HBT cascodes [Chalvatzis et al. , JSSC, May 2007] • MOS on clock path to improve speed with low supply • HBT on data path for high gain

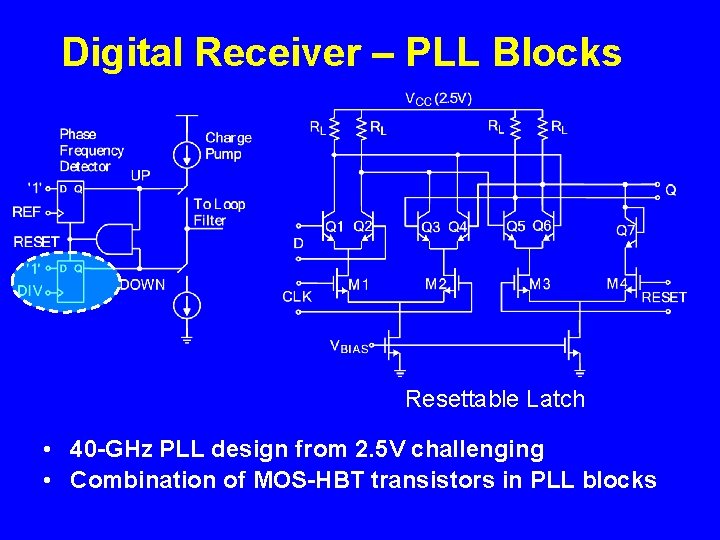

Digital Receiver – PLL Blocks Resettable Latch • 40 -GHz PLL design from 2. 5 V challenging • Combination of MOS-HBT transistors in PLL blocks

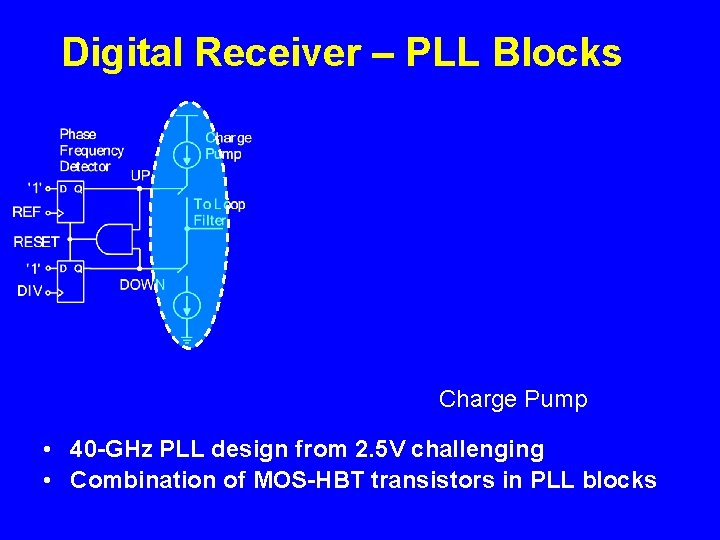

Digital Receiver – PLL Blocks Charge Pump • 40 -GHz PLL design from 2. 5 V challenging • Combination of MOS-HBT transistors in PLL blocks

![VCO • Colpitts VCO topology with HBT [Dickson et al. , CSICS 2006] • VCO • Colpitts VCO topology with HBT [Dickson et al. , CSICS 2006] •](http://slidetodoc.com/presentation_image_h2/4729ecfc716e0bbe16527eb3d667cd18/image-13.jpg)

VCO • Colpitts VCO topology with HBT [Dickson et al. , CSICS 2006] • VCO biased for minimum phase noise • Differential tuning with accumulation mode MOS varactors

Fabrication and characterization of digital receiver

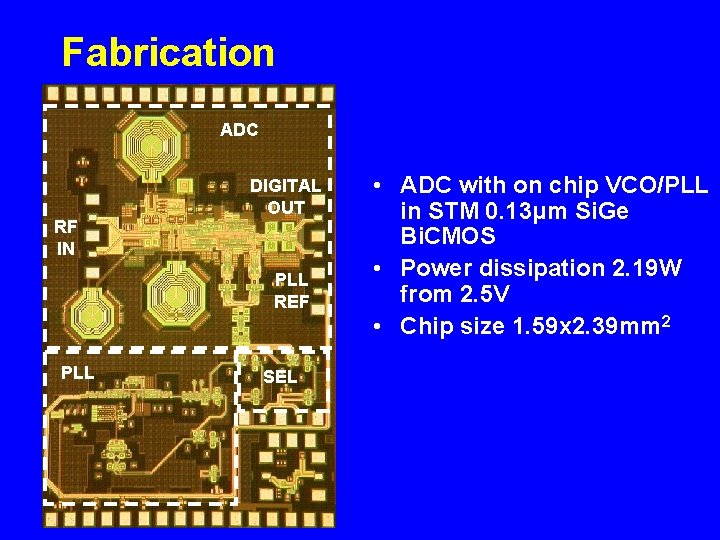

Fabrication ADC RF IN DIGITAL OUT PLL REF PLL SEL • ADC with on chip VCO/PLL in STM 0. 13μm Si. Ge Bi. CMOS • Power dissipation 2. 19 W from 2. 5 V • Chip size 1. 59 x 2. 39 mm 2

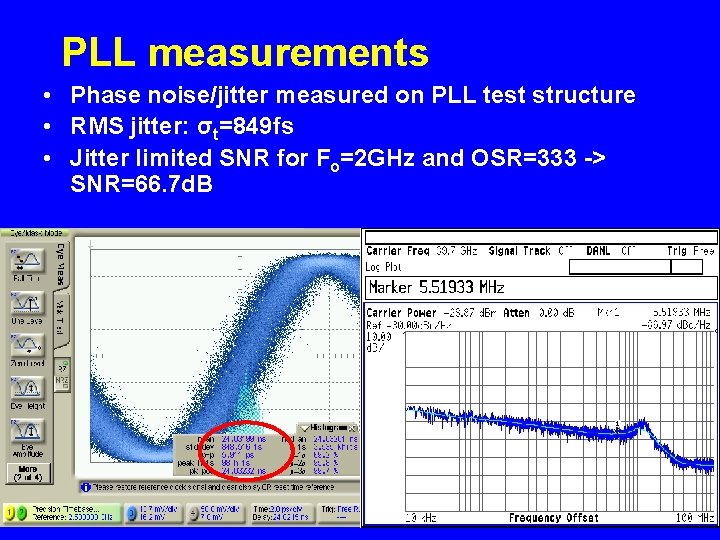

PLL measurements • Phase noise/jitter measured on PLL test structure • RMS jitter: σt=849 fs • Jitter limited SNR for Fo=2 GHz and OSR=333 -> SNR=66. 7 d. B

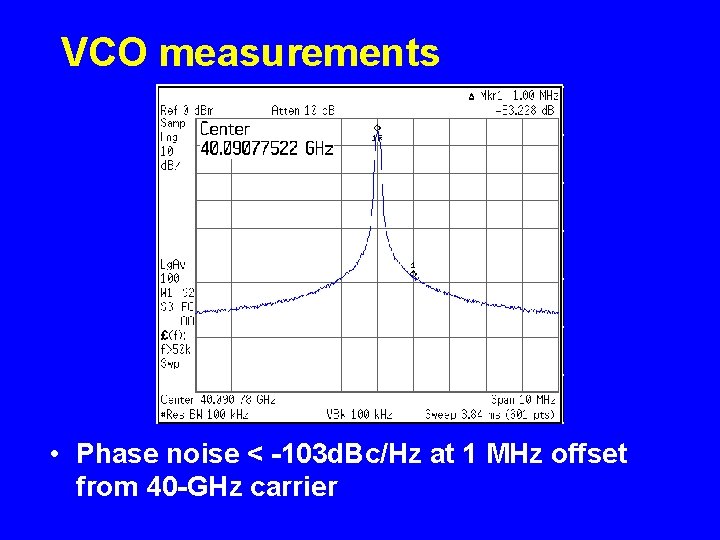

VCO measurements • Phase noise < -103 d. Bc/Hz at 1 MHz offset from 40 -GHz carrier

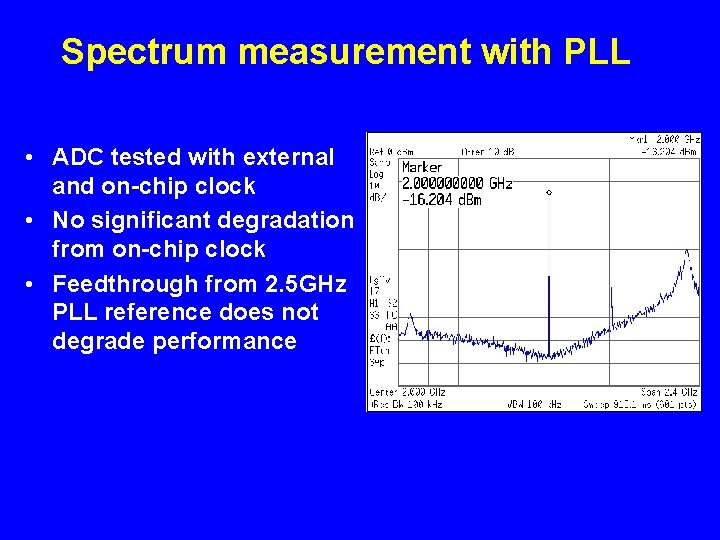

Spectrum measurement with PLL • ADC tested with external and on-chip clock • No significant degradation from on-chip clock • Feedthrough from 2. 5 GHz PLL reference does not degrade performance

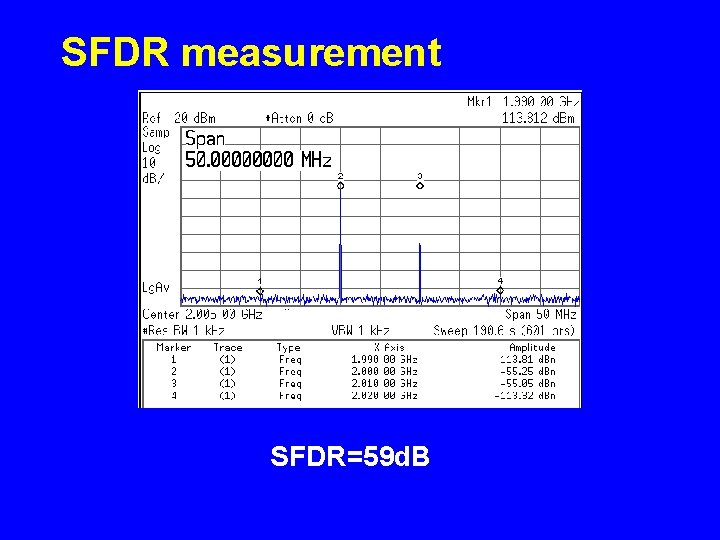

SFDR measurement SFDR=59 d. B

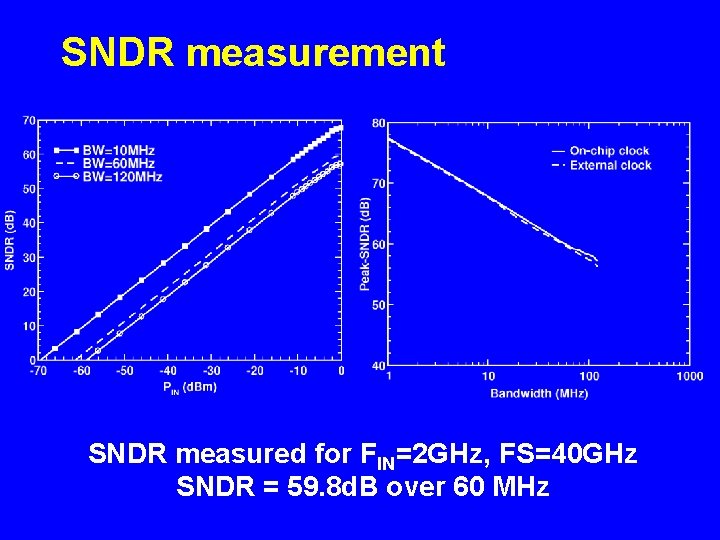

SNDR measurement SNDR measured for FIN=2 GHz, FS=40 GHz SNDR = 59. 8 d. B over 60 MHz

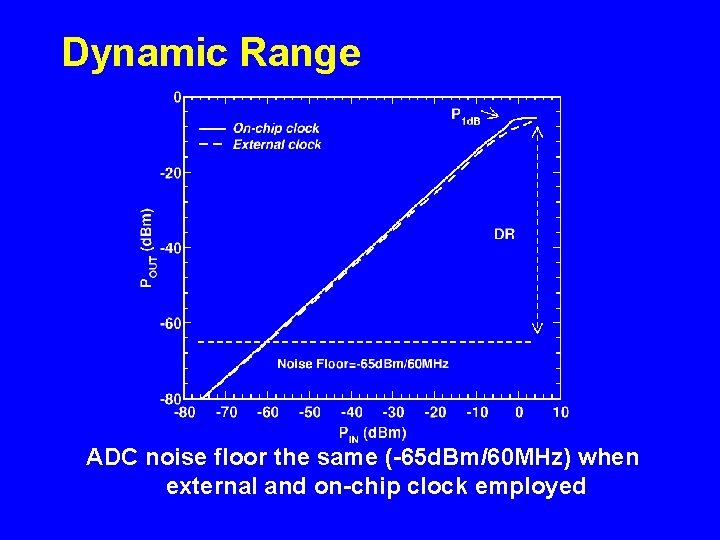

Dynamic Range ADC noise floor the same (-65 d. Bm/60 MHz) when external and on-chip clock employed

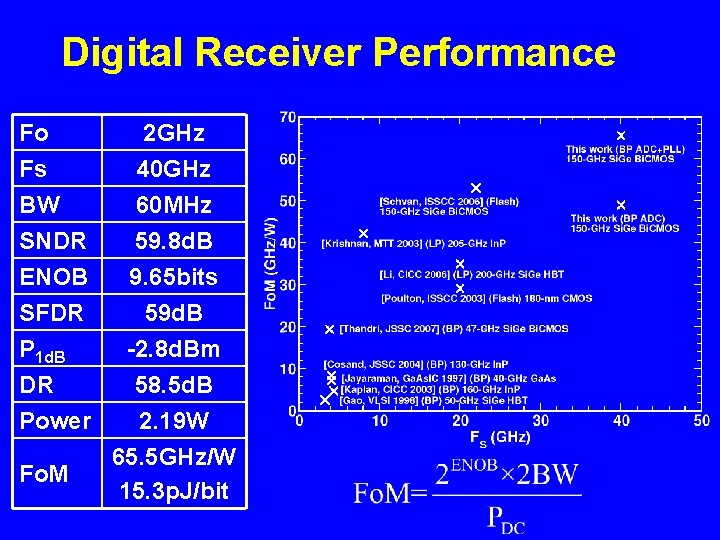

Digital Receiver Performance Fo Fs BW SNDR 2 GHz 40 GHz 60 MHz 59. 8 d. B ENOB SFDR P 1 d. B DR Power 9. 65 bits 59 d. B -2. 8 d. Bm 58. 5 d. B 2. 19 W 65. 5 GHz/W 15. 3 p. J/bit Fo. M

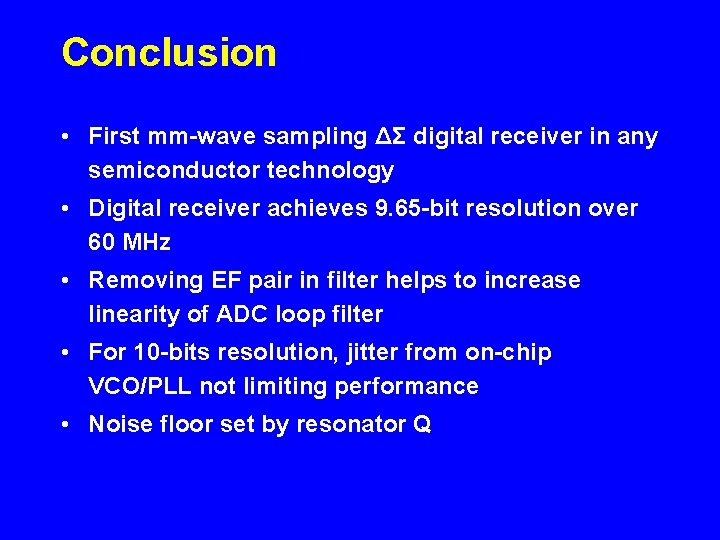

Conclusion • First mm-wave sampling ΔΣ digital receiver in any semiconductor technology • Digital receiver achieves 9. 65 -bit resolution over 60 MHz • Removing EF pair in filter helps to increase linearity of ADC loop filter • For 10 -bits resolution, jitter from on-chip VCO/PLL not limiting performance • Noise floor set by resonator Q

Acknowledgements • Nortel Networks for funding support • John Ilowski and Eric Gagnon for discussions • STMicroelectronics for chip fabrication • Prof Miles Copeland for advice on the manuscript • Ricardo Aroca for help with testing • CMC for CAD tools • Jaro Pristrupa for CAD support

- Slides: 24