A 12 bit 50 MSs Dual Channel Time

A 12 bit 50 MS/s Dual Channel Time Domain Two Step ADC Tibi Galambos, Vladimir Koifman, Anatoli Mordakhay Analog Value Ltd. May 13, 2019 May 1

Overview • • • ADC Architecture Sampling Voltage to Time Converter Sampling Latch Circuit ADC Layout Conclusions May 13, 2019 2

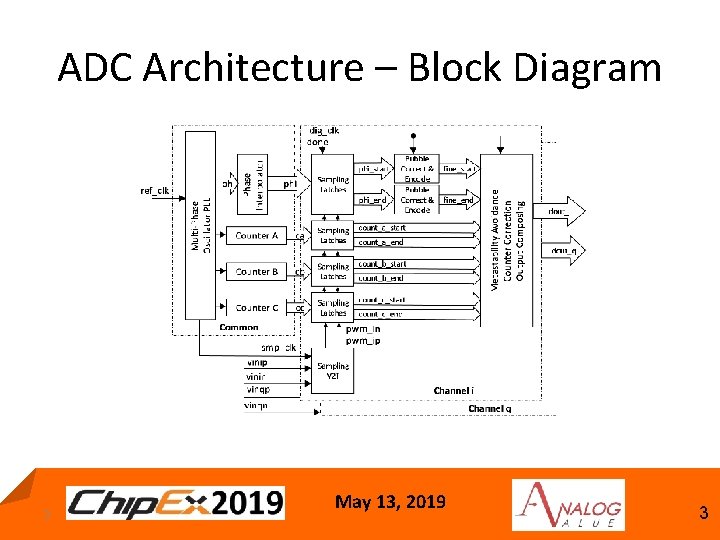

ADC Architecture – Block Diagram 3 May 13, 2019 3

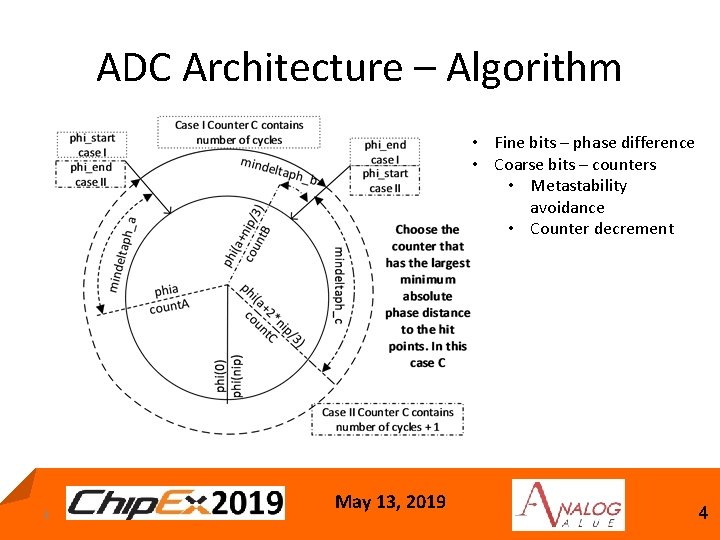

ADC Architecture – Algorithm • Fine bits – phase difference • Coarse bits – counters • Metastability avoidance • Counter decrement 4 May 13, 2019 4

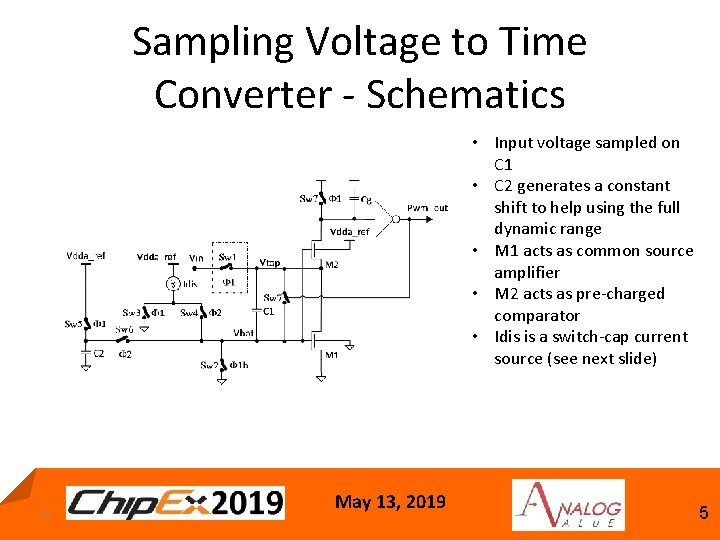

Sampling Voltage to Time Converter - Schematics • Input voltage sampled on C 1 • C 2 generates a constant shift to help using the full dynamic range • M 1 acts as common source amplifier • M 2 acts as pre-charged comparator • Idis is a switch-cap current source (see next slide) 5 May 13, 2019 5

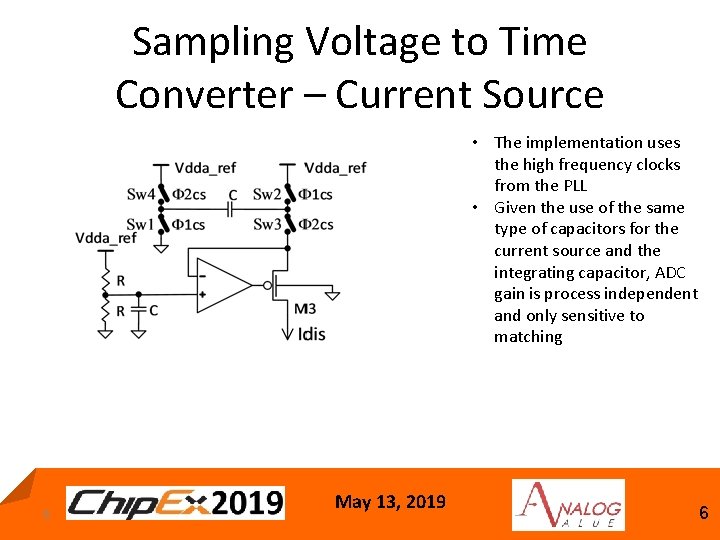

Sampling Voltage to Time Converter – Current Source • The implementation uses the high frequency clocks from the PLL • Given the use of the same type of capacitors for the current source and the integrating capacitor, ADC gain is process independent and only sensitive to matching 6 May 13, 2019 6

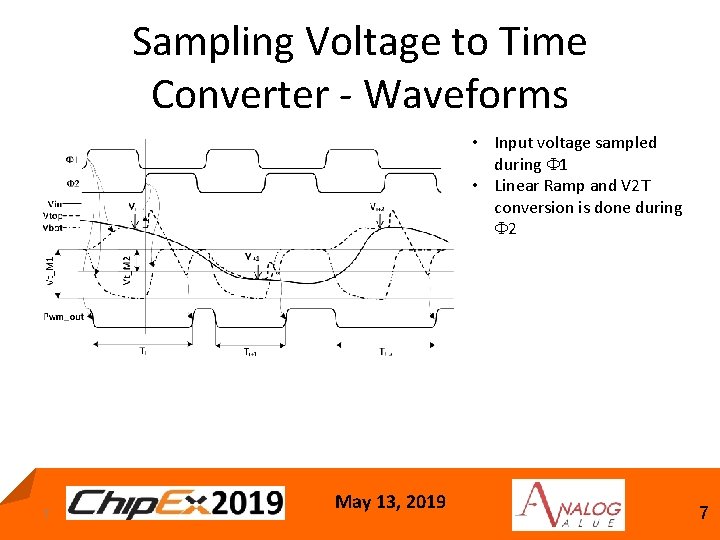

Sampling Voltage to Time Converter - Waveforms • Input voltage sampled during F 1 • Linear Ramp and V 2 T conversion is done during F 2 7 May 13, 2019 7

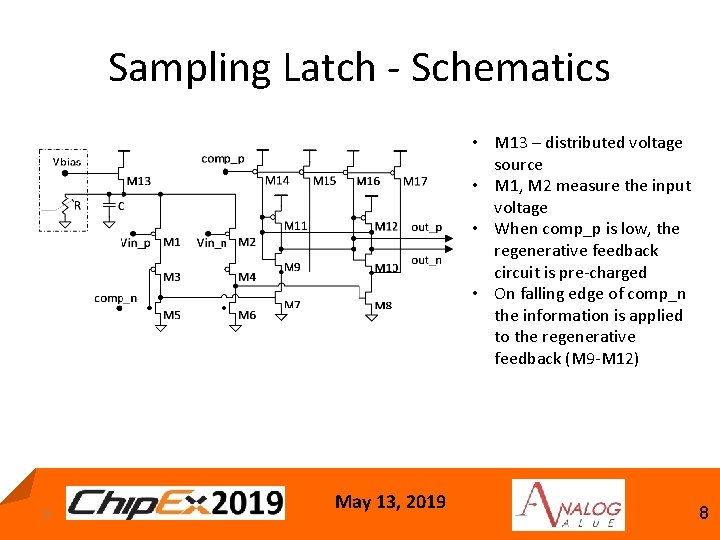

Sampling Latch - Schematics • M 13 – distributed voltage source • M 1, M 2 measure the input voltage • When comp_p is low, the regenerative feedback circuit is pre-charged • On falling edge of comp_n the information is applied to the regenerative feedback (M 9 -M 12) 8 May 13, 2019 8

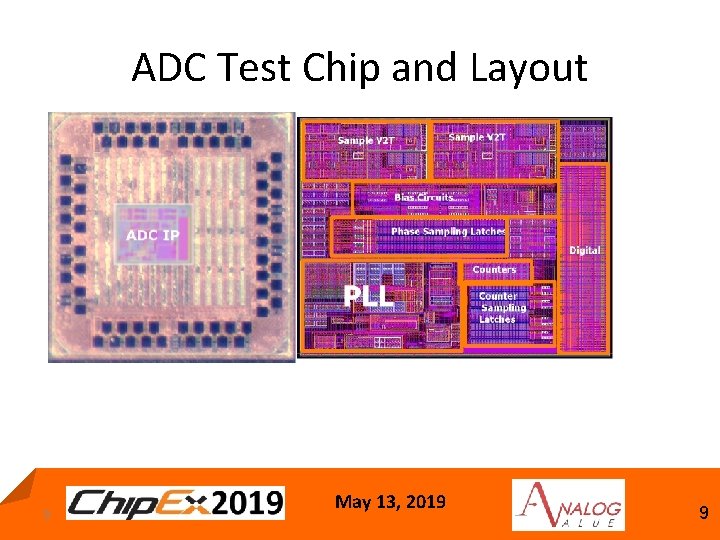

ADC Test Chip and Layout 9 May 13, 2019 9

Conclusion • A novel 12 bit ADC was designed and fabricated in GF 22 nm FDSOI technology • Power consumption (for 2 channels) is 4 m. W • Silicon area 0. 05 mm 2 • Measured an ENOB of 10. 5 May 13, 2019 10

Thanks for your attention 11 May 13, 2019 11

- Slides: 11