A 1 Tap 40 Gbps Decision Feedback Equalizer

A 1 -Tap 40 -Gbps Decision Feedback Equalizer in a 0. 18 -mm Si. Ge Bi. CMOS Technology Adesh Garg, Anthony Chan Carusone and Sorin P. Voinigescu University of Toronto October 31 st, 2005 CSICS Presentation 1

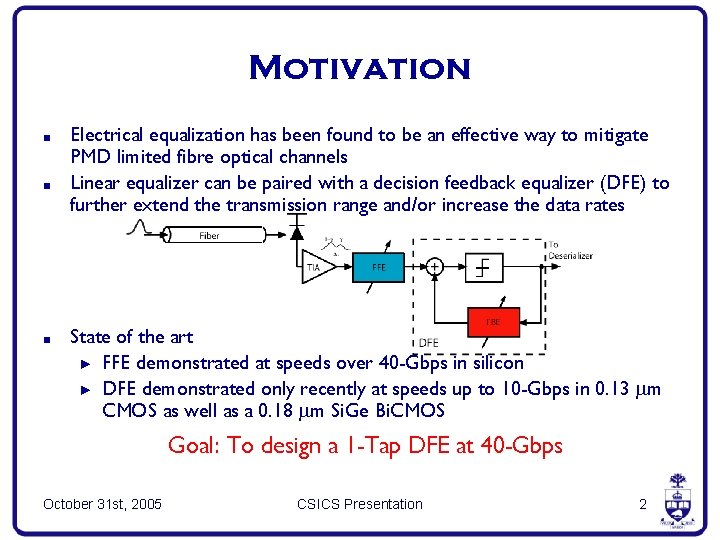

Motivation ■ ■ ■ Electrical equalization has been found to be an effective way to mitigate PMD limited fibre optical channels Linear equalizer can be paired with a decision feedback equalizer (DFE) to further extend the transmission range and/or increase the data rates State of the art ► FFE demonstrated at speeds over 40 -Gbps in silicon ► DFE demonstrated only recently at speeds up to 10 -Gbps in 0. 13 mm CMOS as well as a 0. 18 mm Si. Ge Bi. CMOS Goal: To design a 1 -Tap DFE at 40 -Gbps October 31 st, 2005 CSICS Presentation 2

Architecture ■ Direct Feedback – filter processing in feedback path ► ● Look-ahead – parallel computation of filter ► Disadvantages: ● ■ Advantages: Multiple processing stages in feedback path Additional loading at summing node October 31 st, 2005 CSICS Presentation ● ● Parallelism employed to remove processing in feedback path Limits loading on summing node 3

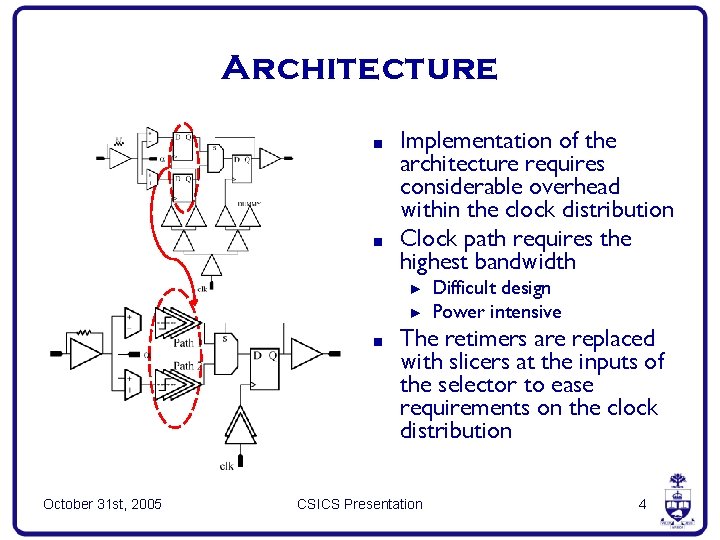

Architecture ■ ■ Implementation of the architecture requires considerable overhead within the clock distribution Clock path requires the highest bandwidth ► ► ■ October 31 st, 2005 Difficult design Power intensive The retimers are replaced with slicers at the inputs of the selector to ease requirements on the clock distribution CSICS Presentation 4

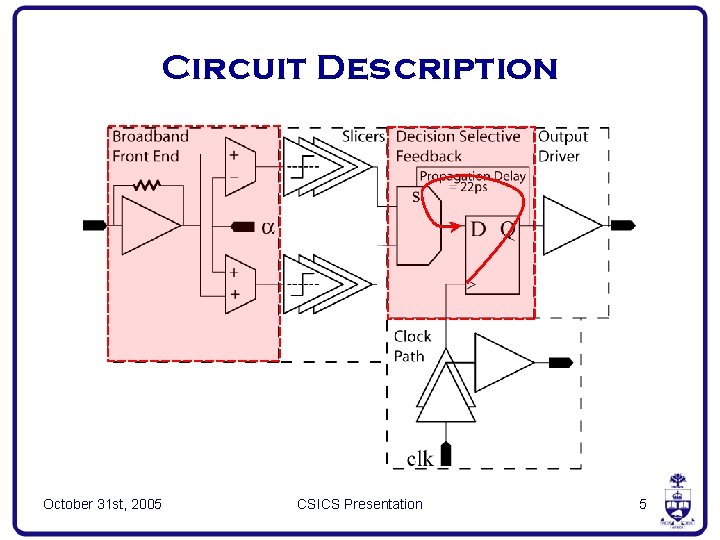

Circuit Description October 31 st, 2005 CSICS Presentation 5

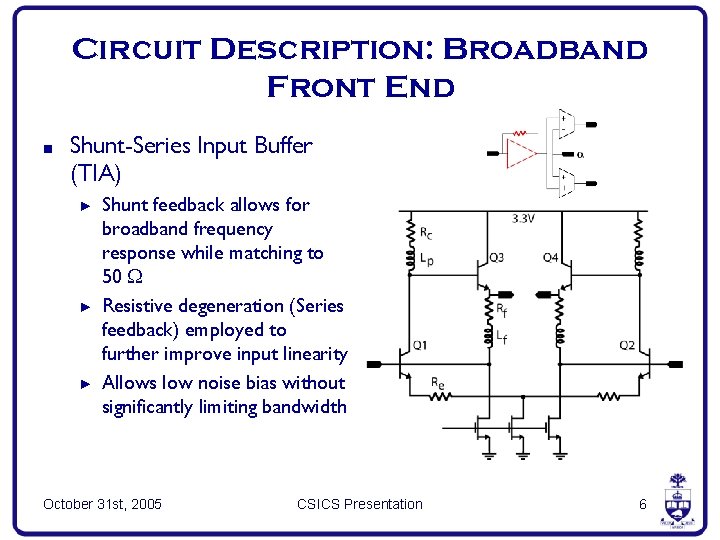

Circuit Description: Broadband Front End ■ Shunt-Series Input Buffer (TIA) ► ► ► Shunt feedback allows for broadband frequency response while matching to 50 W Resistive degeneration (Series feedback) employed to further improve input linearity Allows low noise bias without significantly limiting bandwidth October 31 st, 2005 CSICS Presentation 6

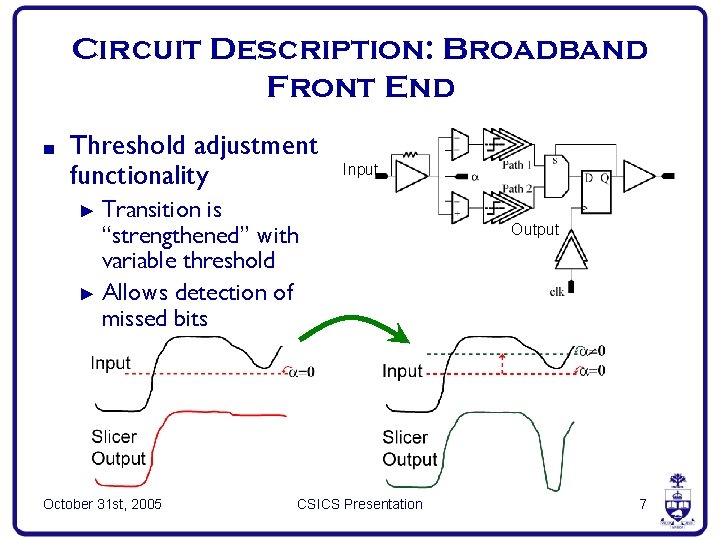

Circuit Description: Broadband Front End ■ Threshold adjustment functionality Input Transition is “strengthened” with variable threshold ► Allows detection of missed bits ► October 31 st, 2005 CSICS Presentation Output 7

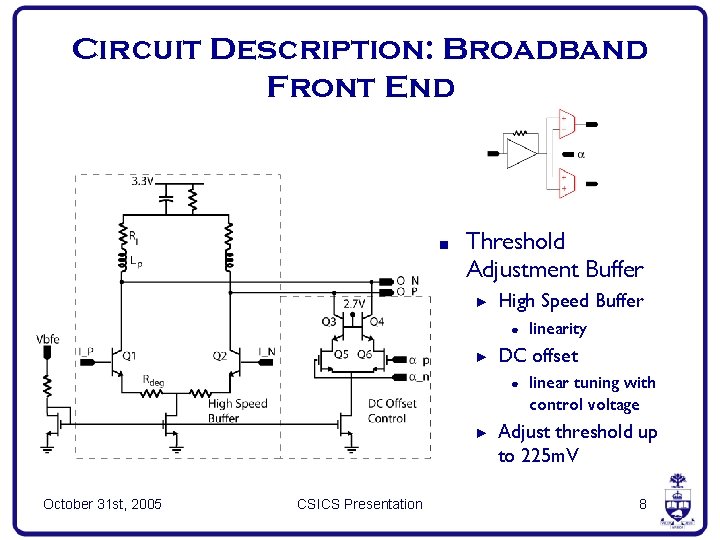

Circuit Description: Broadband Front End ■ Threshold Adjustment Buffer ► High Speed Buffer ● ► DC offset ● ► October 31 st, 2005 CSICS Presentation linearity linear tuning with control voltage Adjust threshold up to 225 m. V 8

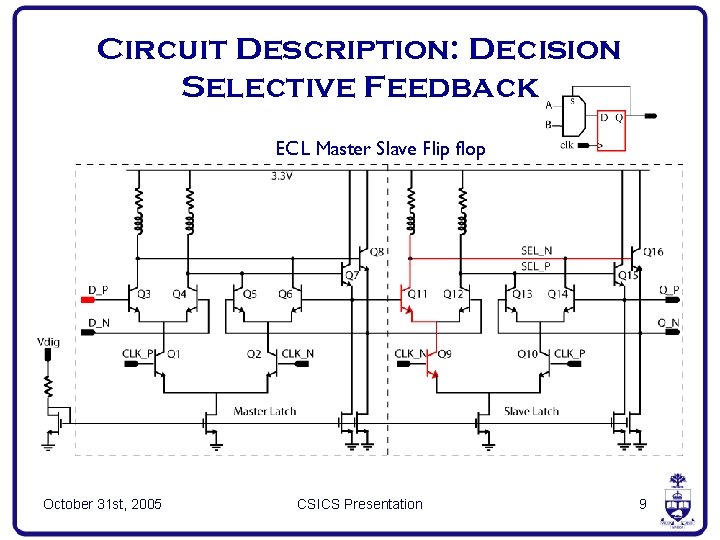

Circuit Description: Decision Selective Feedback ECL Master Slave Flip flop October 31 st, 2005 CSICS Presentation 9

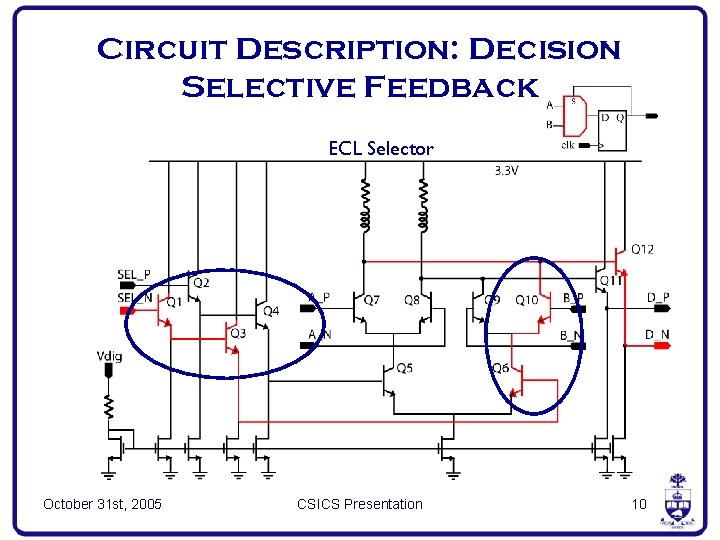

Circuit Description: Decision Selective Feedback ECL Selector October 31 st, 2005 CSICS Presentation 10

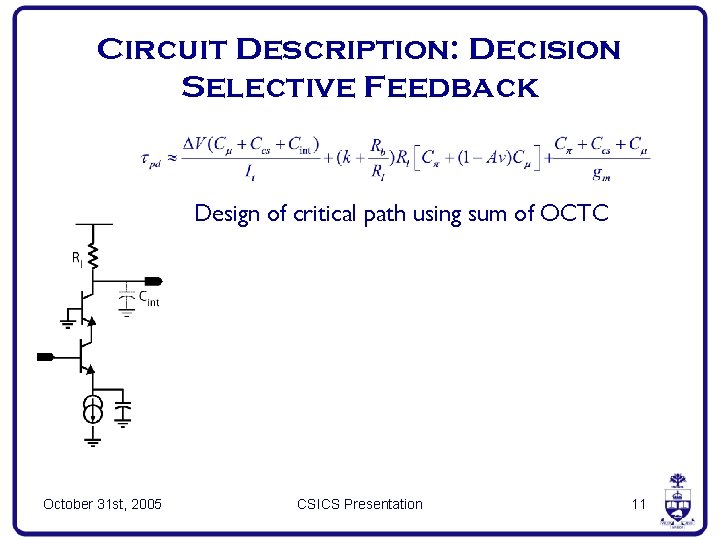

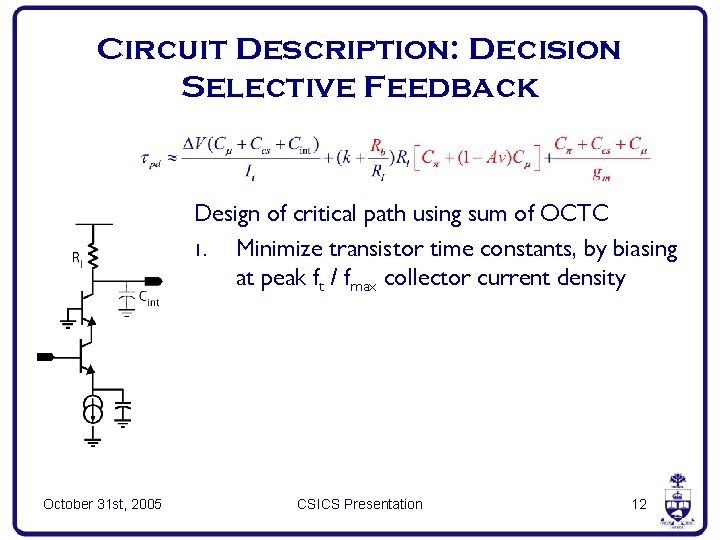

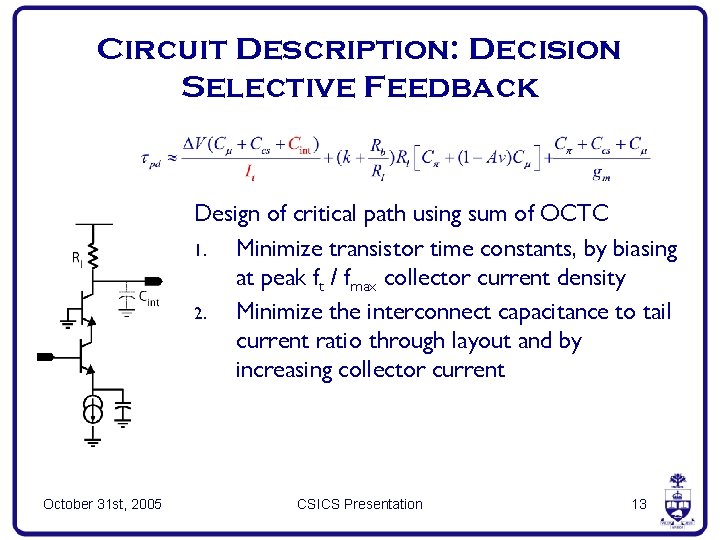

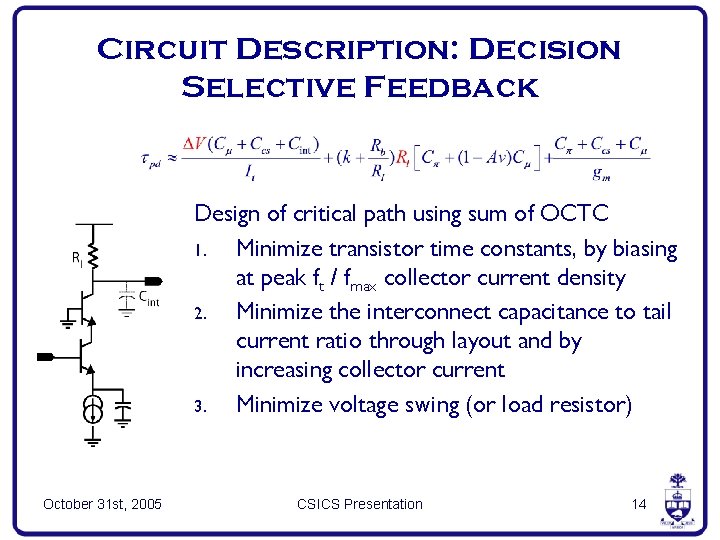

Circuit Description: Decision Selective Feedback Design of critical path using sum of OCTC October 31 st, 2005 CSICS Presentation 11

Circuit Description: Decision Selective Feedback Design of critical path using sum of OCTC 1. Minimize transistor time constants, by biasing at peak ft / fmax collector current density October 31 st, 2005 CSICS Presentation 12

Circuit Description: Decision Selective Feedback Design of critical path using sum of OCTC 1. Minimize transistor time constants, by biasing at peak ft / fmax collector current density 2. Minimize the interconnect capacitance to tail current ratio through layout and by increasing collector current October 31 st, 2005 CSICS Presentation 13

Circuit Description: Decision Selective Feedback Design of critical path using sum of OCTC 1. Minimize transistor time constants, by biasing at peak ft / fmax collector current density 2. Minimize the interconnect capacitance to tail current ratio through layout and by increasing collector current 3. Minimize voltage swing (or load resistor) October 31 st, 2005 CSICS Presentation 14

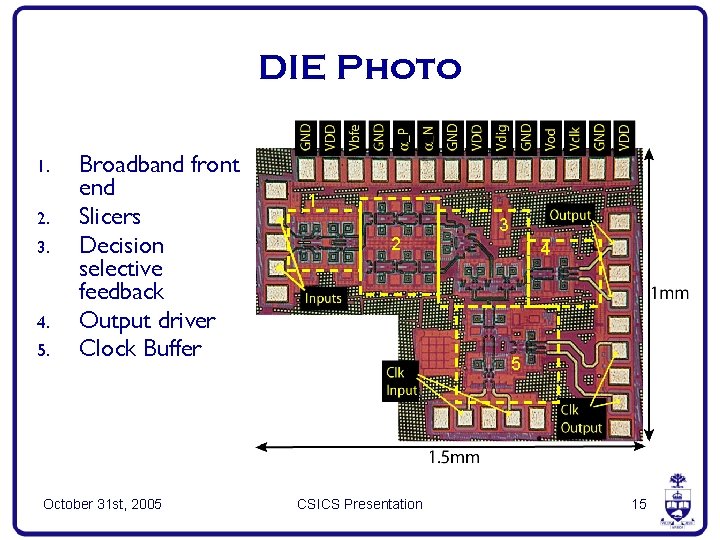

DIE Photo 1. 2. 3. 4. 5. Broadband front end Slicers Decision selective feedback Output driver Clock Buffer October 31 st, 2005 1 2 3 4 5 CSICS Presentation 15

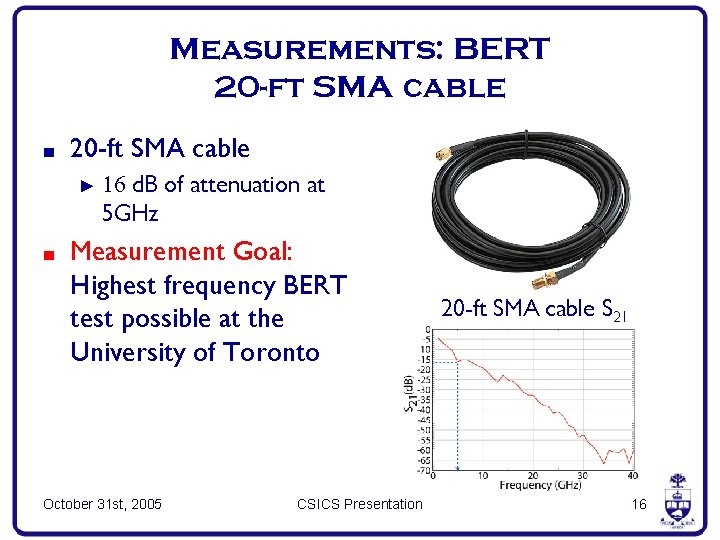

Measurements: BERT 20 -ft SMA cable ■ 20 -ft SMA cable ► ■ 16 d. B of attenuation at 5 GHz Measurement Goal: Highest frequency BERT test possible at the University of Toronto October 31 st, 2005 CSICS Presentation 20 -ft SMA cable S 21 16

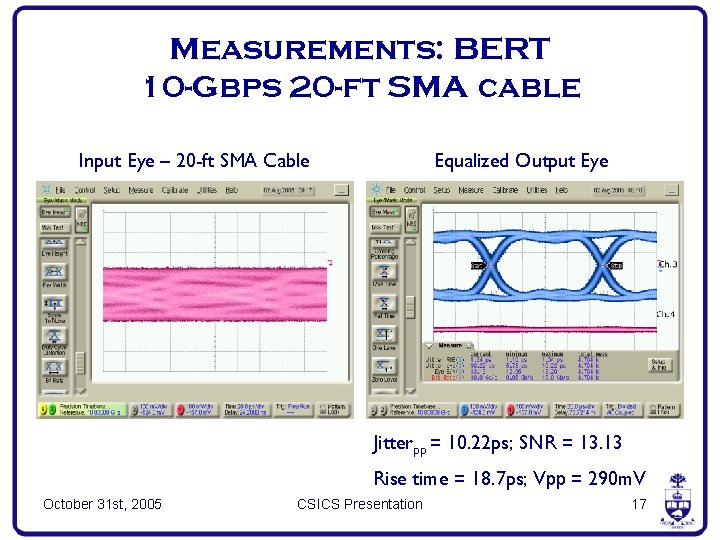

Measurements: BERT 10 -Gbps 20 -ft SMA cable Input Eye – 20 -ft SMA Cable Equalized Output Eye Jitterpp = 10. 22 ps; SNR = 13. 13 Rise time = 18. 7 ps; Vpp = 290 m. V October 31 st, 2005 CSICS Presentation 17

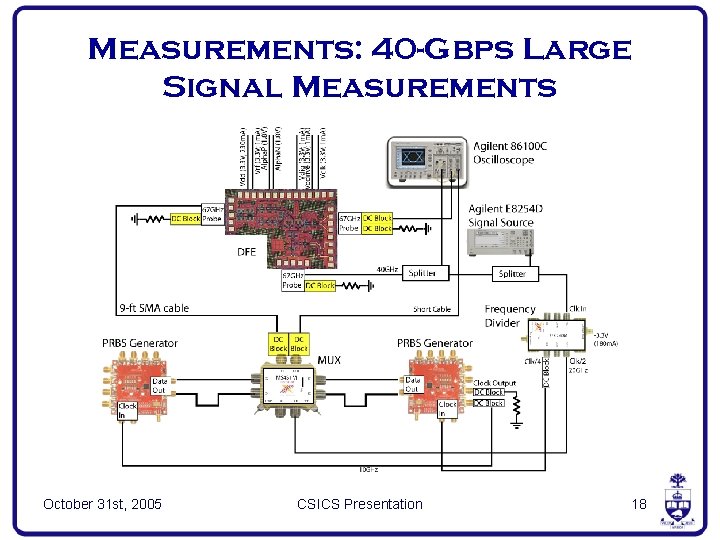

Measurements: 40 -Gbps Large Signal Measurements October 31 st, 2005 CSICS Presentation 18

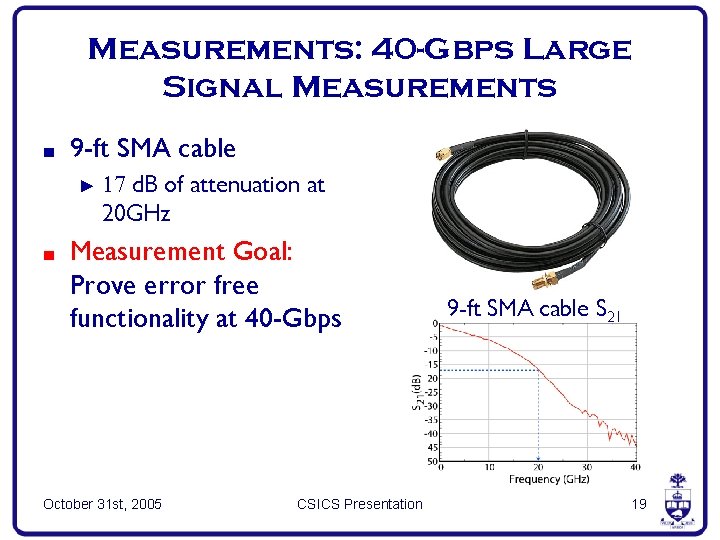

Measurements: 40 -Gbps Large Signal Measurements ■ 9 -ft SMA cable ► ■ 17 d. B of attenuation at 20 GHz Measurement Goal: Prove error free functionality at 40 -Gbps October 31 st, 2005 CSICS Presentation 9 -ft SMA cable S 21 19

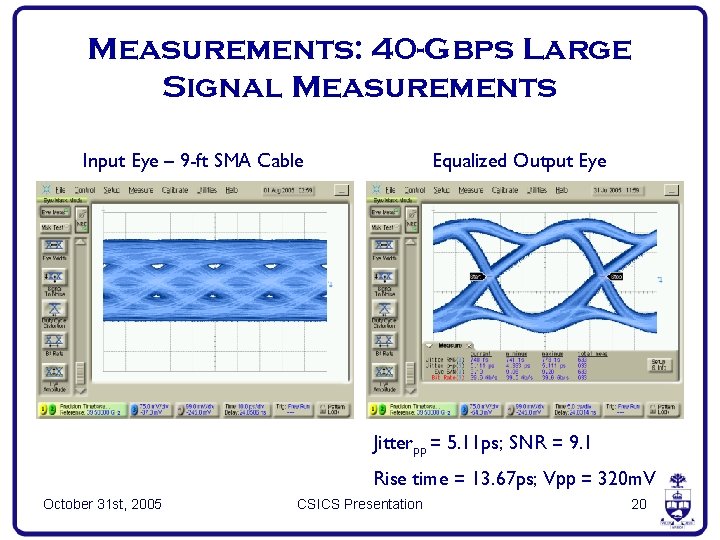

Measurements: 40 -Gbps Large Signal Measurements Input Eye – 9 -ft SMA Cable Equalized Output Eye Jitterpp = 5. 11 ps; SNR = 9. 1 Rise time = 13. 67 ps; Vpp = 320 m. V October 31 st, 2005 CSICS Presentation 20

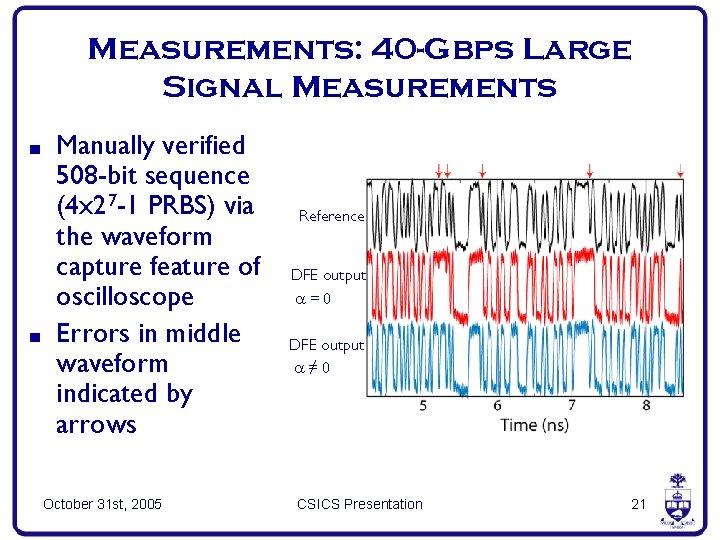

Measurements: 40 -Gbps Large Signal Measurements ■ ■ Manually verified 508 -bit sequence (4 x 27 -1 PRBS) via the waveform capture feature of oscilloscope Errors in middle waveform indicated by arrows October 31 st, 2005 Reference DFE output a=0 DFE output a≠ 0 CSICS Presentation 21

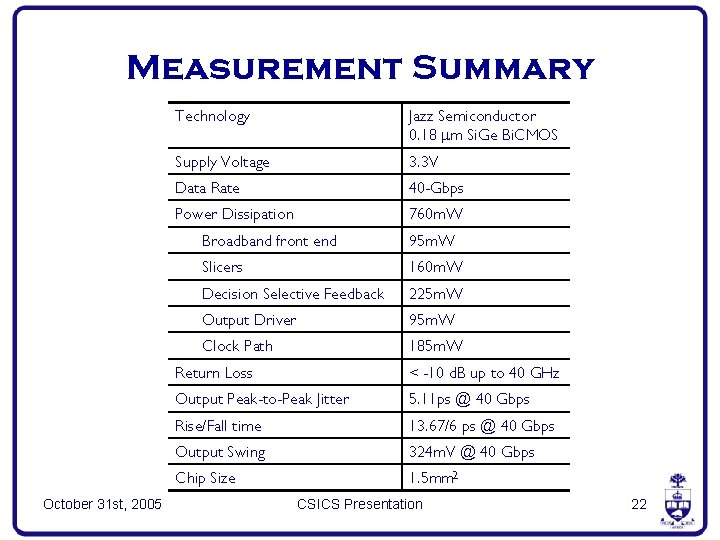

Measurement Summary October 31 st, 2005 Technology Jazz Semiconductor 0. 18 mm Si. Ge Bi. CMOS Supply Voltage 3. 3 V Data Rate 40 -Gbps Power Dissipation 760 m. W Broadband front end 95 m. W Slicers 160 m. W Decision Selective Feedback 225 m. W Output Driver 95 m. W Clock Path 185 m. W Return Loss < -10 d. B up to 40 GHz Output Peak-to-Peak Jitter 5. 11 ps @ 40 Gbps Rise/Fall time 13. 67/6 ps @ 40 Gbps Output Swing 324 m. V @ 40 Gbps Chip Size 1. 5 mm 2 CSICS Presentation 22

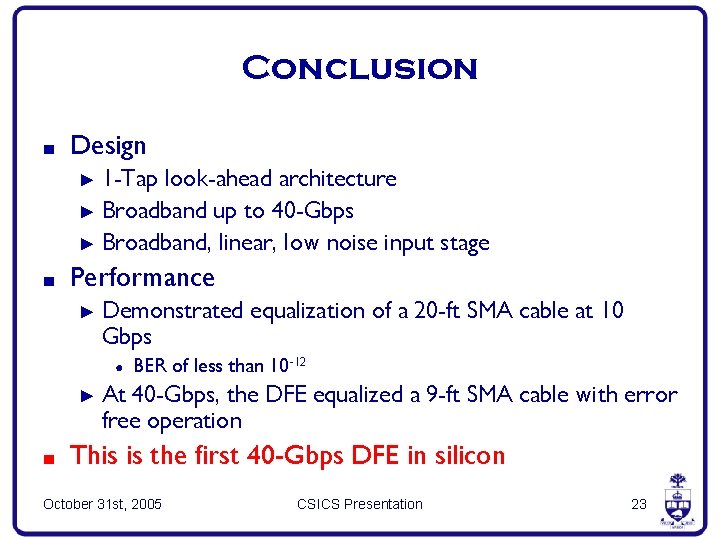

Conclusion ■ Design 1 -Tap look-ahead architecture ► Broadband up to 40 -Gbps ► Broadband, linear, low noise input stage ► ■ Performance ► Demonstrated equalization of a 20 -ft SMA cable at 10 Gbps ● ► ■ BER of less than 10 -12 At 40 -Gbps, the DFE equalized a 9 -ft SMA cable with error free operation This is the first 40 -Gbps DFE in silicon October 31 st, 2005 CSICS Presentation 23

Acknowledgements ■ ■ NIT, OIT, CFI for test equipment NSERC, Gennum and Micronet for financial support Jazz Semiconductor for technology access CAD tools by the Canadian Microelectronics. Corportation (CMC) October 31 st, 2005 CSICS Presentation 24

Questions? October 31 st, 2005 CSICS Presentation 25

Backup October 31 st, 2005 CSICS Presentation 26

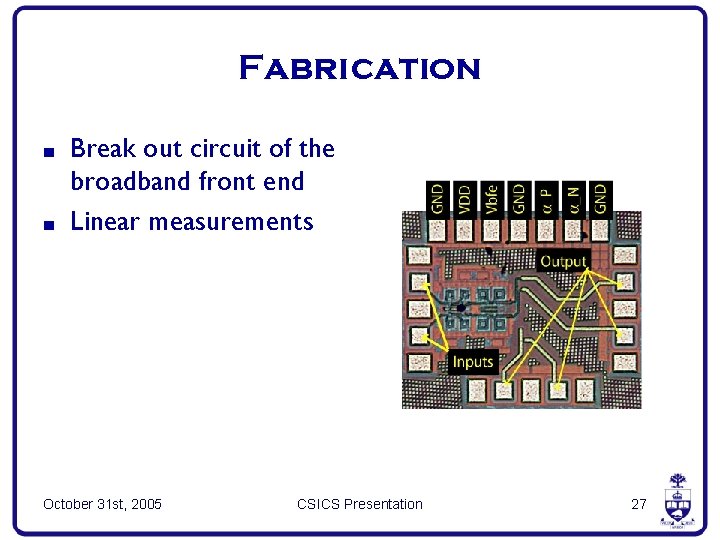

Fabrication ■ ■ Break out circuit of the broadband front end Linear measurements October 31 st, 2005 CSICS Presentation 27

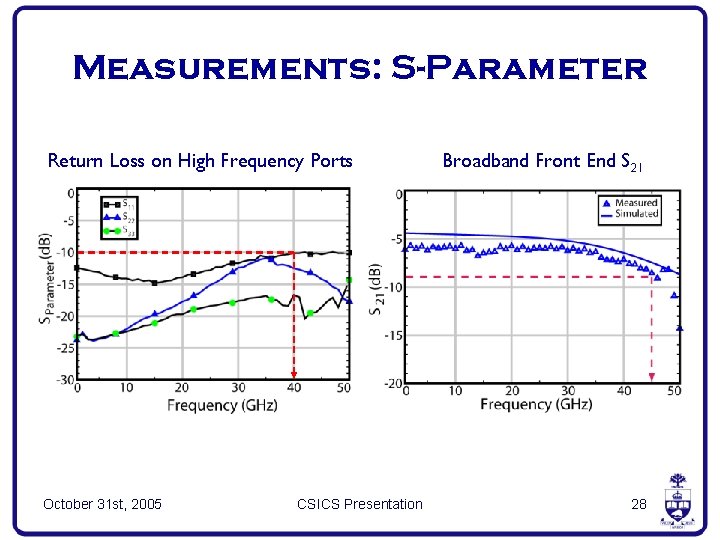

Measurements: S-Parameter Return Loss on High Frequency Ports October 31 st, 2005 CSICS Presentation Broadband Front End S 21 28

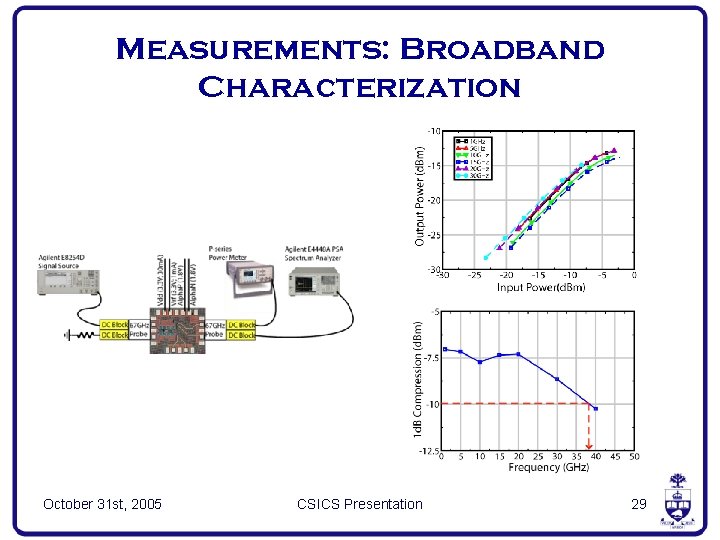

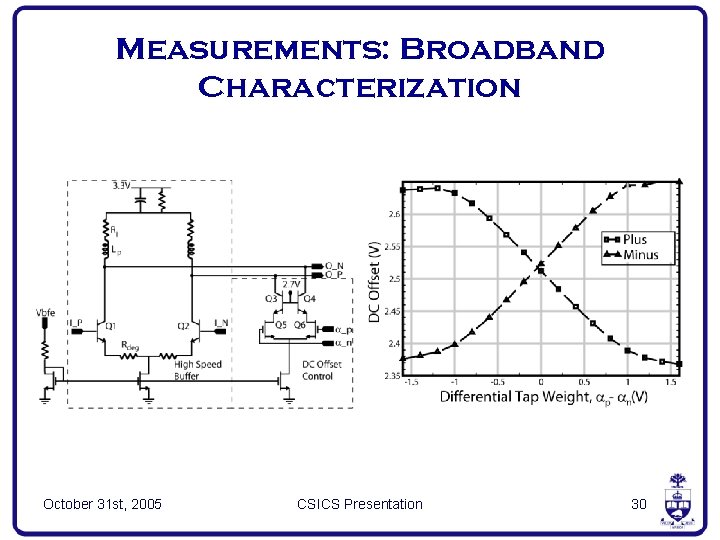

Measurements: Broadband Characterization October 31 st, 2005 CSICS Presentation 29

Measurements: Broadband Characterization October 31 st, 2005 CSICS Presentation 30

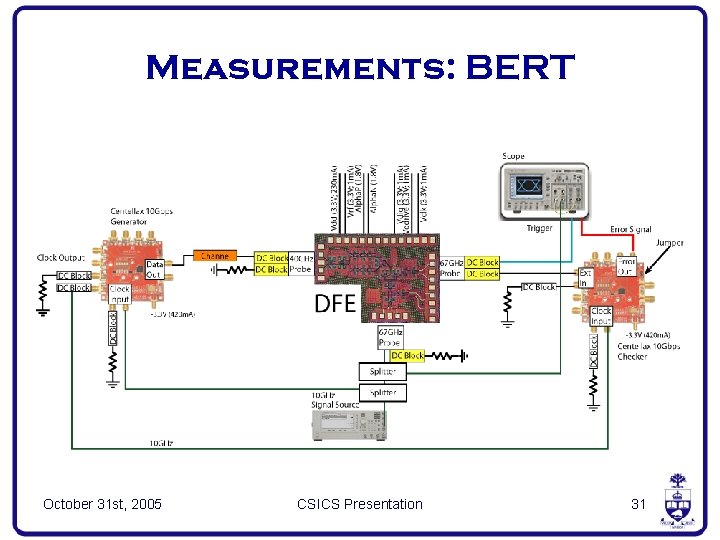

Measurements: BERT October 31 st, 2005 CSICS Presentation 31

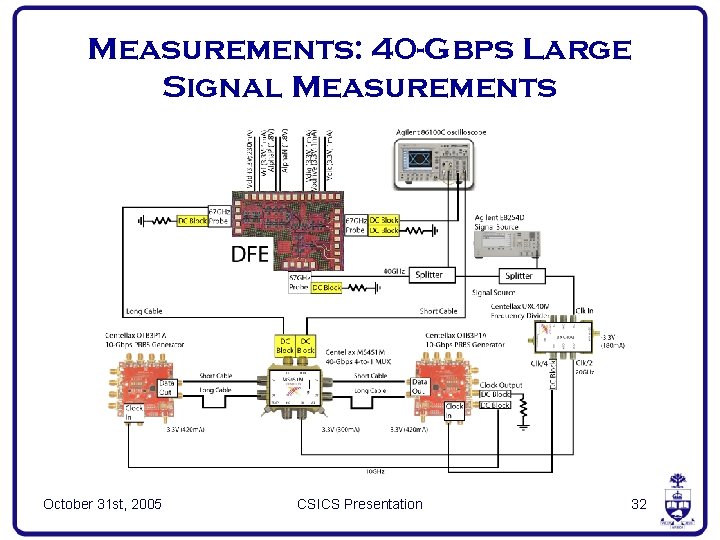

Measurements: 40 -Gbps Large Signal Measurements October 31 st, 2005 CSICS Presentation 32

- Slides: 32