90 nm MOS MetalOxideSemiconductor devices fabrication flow Wafer

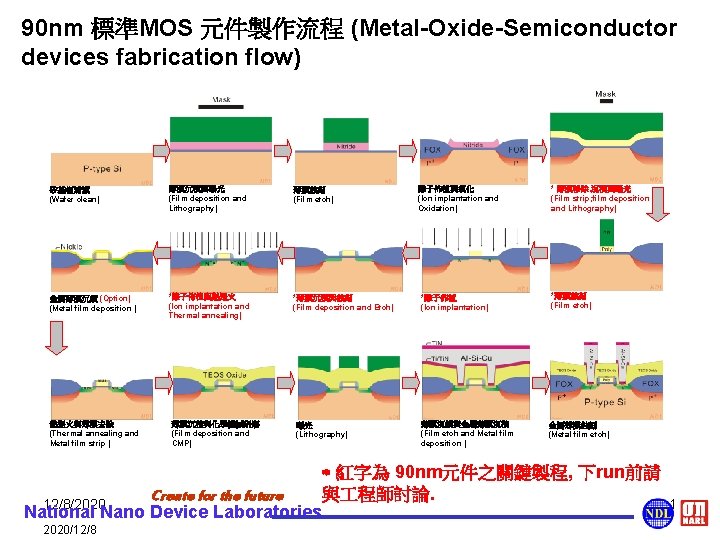

90 nm 標準MOS 元件製作流程 (Metal-Oxide-Semiconductor devices fabrication flow) 矽基板清潔 (Wafer clean) 薄膜沉積與曝光 (Film deposition and Lithography) 薄膜蝕刻 (Film etch) 金屬薄膜沉績 (Option) (Metal film deposition ) *離子佈植與熱退火 (Ion implantation and Thermal annealing) *薄膜沉積與蝕刻 (Film deposition and Etch) 熱退火與薄膜去除 (Thermal annealing and Metal film strip ) 薄膜沉積與化學機械研磨 (Film deposition and CMP) 曝光 (Lithography) 離子佈植與氧化 (Ion implantation and Oxidation) *離子佈植 (Ion implantation) 薄膜沉績與金屬薄膜沉積 (Film etch and Metal film deposition ) * 薄膜移除, 沉積與曝光 (Film strip; film deposition and Lithography) *薄膜蝕刻 (Film etch) 金屬薄膜蝕刻 (Metal film etch) 紅字為 90 nm元件之關鍵製程, 下run前請 與 程師討論. Create for the future 12/8/2020 National Nano Device Laboratories 2020/12/8 1

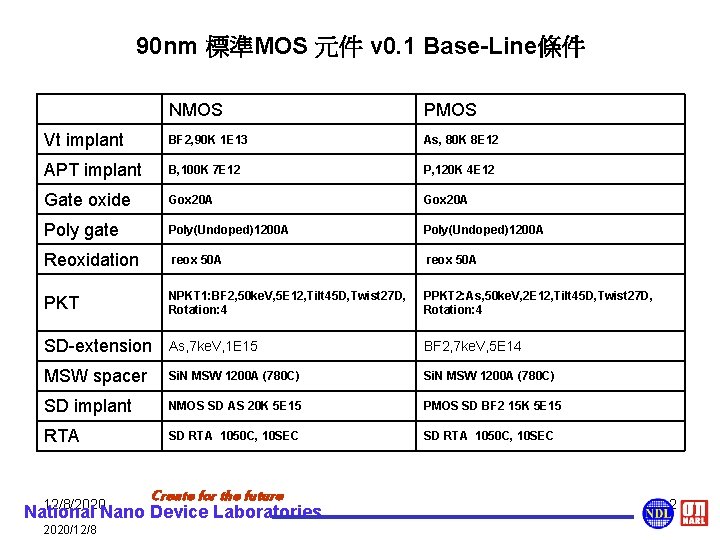

90 nm 標準MOS 元件 v 0. 1 Base-Line條件 NMOS PMOS Vt implant BF 2, 90 K 1 E 13 As, 80 K 8 E 12 APT implant B, 100 K 7 E 12 P, 120 K 4 E 12 Gate oxide Gox 20 A Poly gate Poly(Undoped)1200 A Reoxidation reox 50 A PKT NPKT 1: BF 2, 50 ke. V, 5 E 12, Tilt 45 D, Twist 27 D, Rotation: 4 PPKT 2: As, 50 ke. V, 2 E 12, Tilt 45 D, Twist 27 D, Rotation: 4 SD-extension As, 7 ke. V, 1 E 15 BF 2, 7 ke. V, 5 E 14 MSW spacer Si. N MSW 1200 A (780 C) SD implant NMOS SD AS 20 K 5 E 15 PMOS SD BF 2 15 K 5 E 15 RTA SD RTA 1050 C, 10 SEC 12/8/2020 Create for the future National Nano Device Laboratories 2020/12/8 2

- Slides: 2