9 6 The Control Word The selection variables

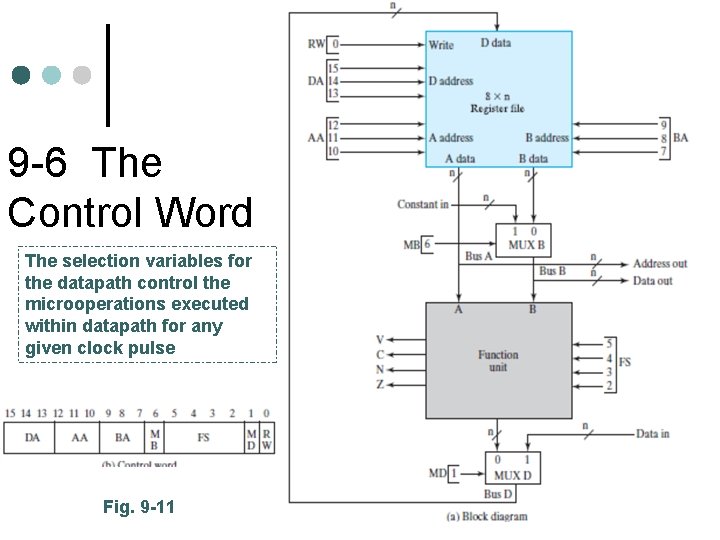

9 -6 The Control Word The selection variables for the datapath control the microoperations executed within datapath for any given clock pulse Fig. 9 -11

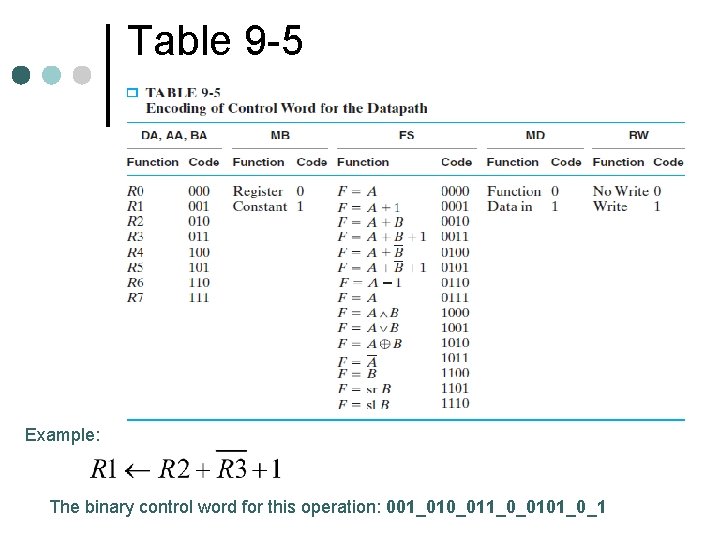

Table 9 -5 Example: The binary control word for this operation: 001_010_011_0_0101_0_1

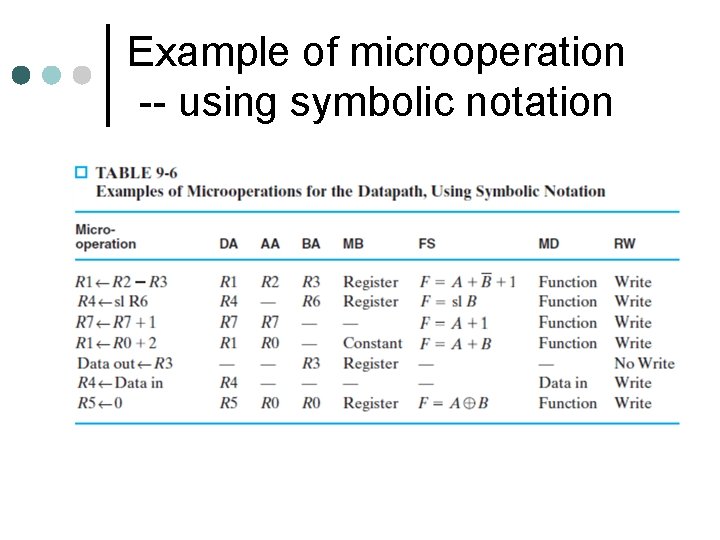

Example of microoperation -- using symbolic notation

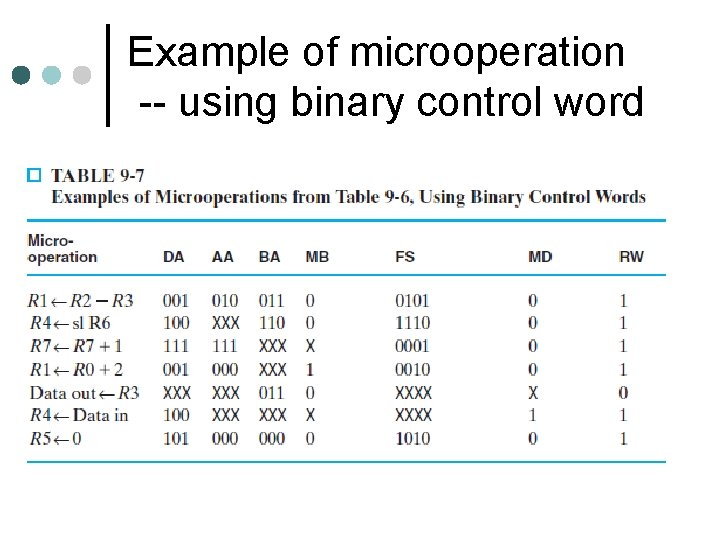

Example of microoperation -- using binary control word

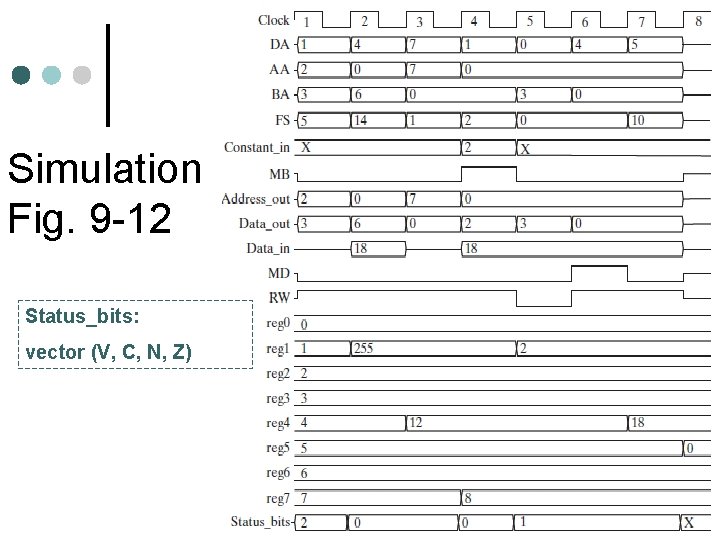

Simulation Fig. 9 -12 Status_bits: vector (V, C, N, Z)

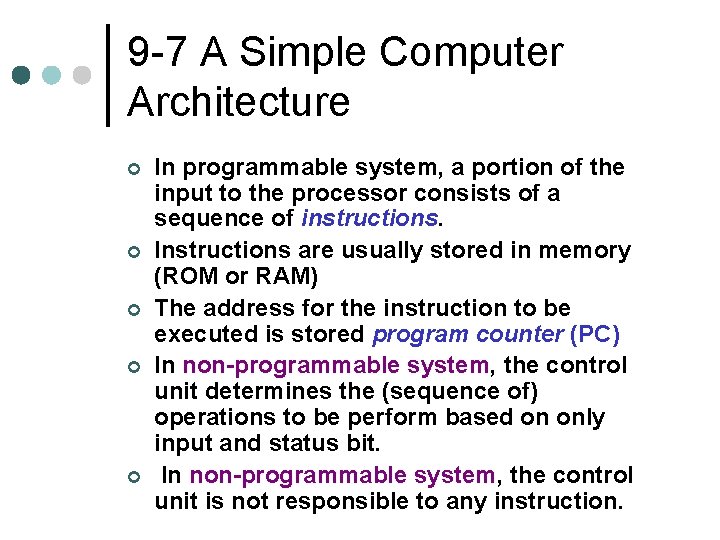

9 -7 A Simple Computer Architecture ¢ ¢ ¢ In programmable system, a portion of the input to the processor consists of a sequence of instructions. Instructions are usually stored in memory (ROM or RAM) The address for the instruction to be executed is stored program counter (PC) In non-programmable system, the control unit determines the (sequence of) operations to be perform based on only input and status bit. In non-programmable system, the control unit is not responsible to any instruction.

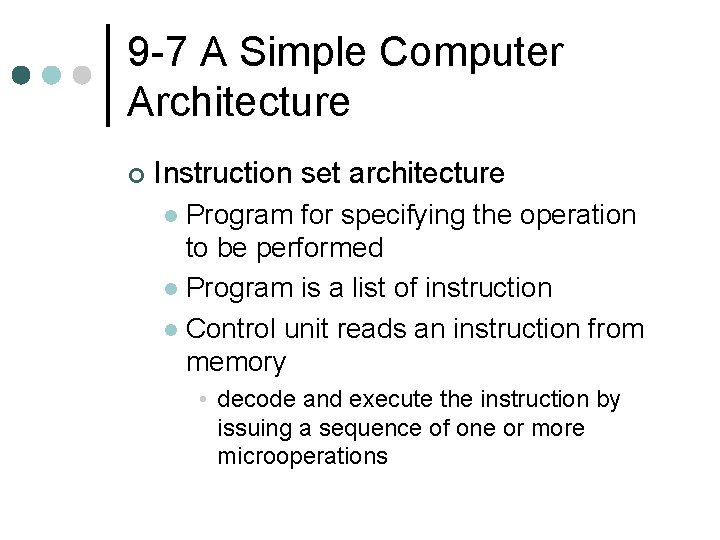

9 -7 A Simple Computer Architecture ¢ Instruction set architecture Program for specifying the operation to be performed l Program is a list of instruction l Control unit reads an instruction from memory l • decode and execute the instruction by issuing a sequence of one or more microoperations

Instruction set architecture Instruction set: a collection of instructions l Instruction set architecture (ISA): a thorough description of instruction set l Three major components: l • Storage resource • Instruction formats • Instruction specifications

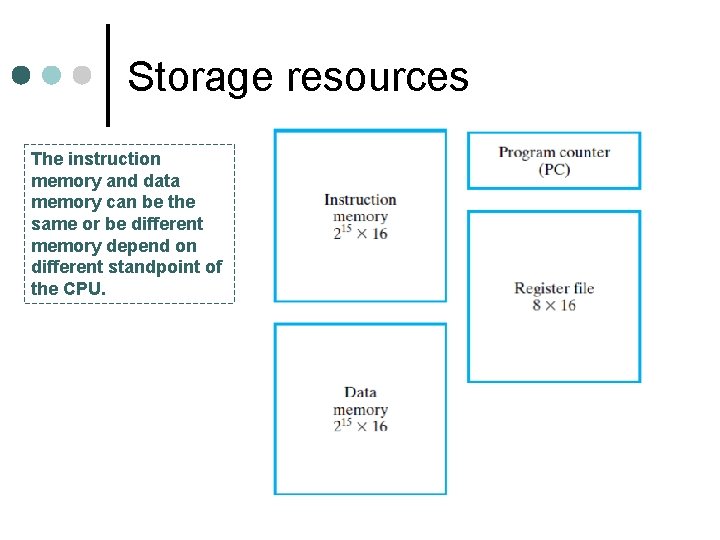

Storage resources The instruction memory and data memory can be the same or be different memory depend on different standpoint of the CPU.

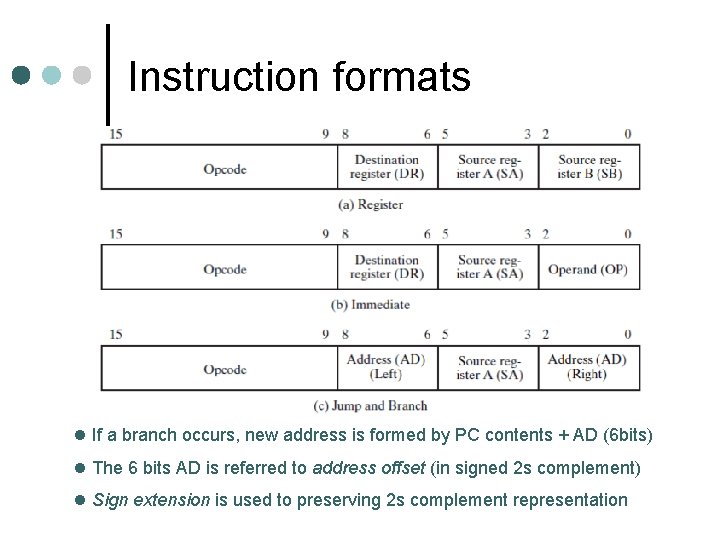

Instruction formats l If a branch occurs, new address is formed by PC contents + AD (6 bits) l The 6 bits AD is referred to address offset (in signed 2 s complement) l Sign extension is used to preserving 2 s complement representation

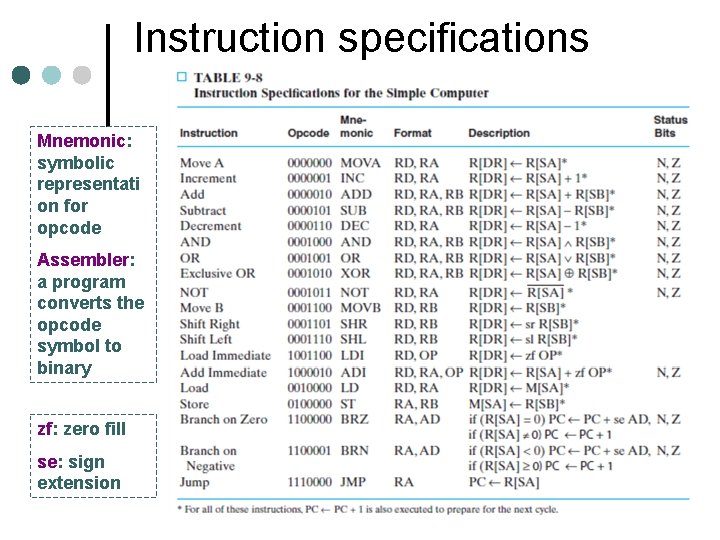

Instruction specifications Mnemonic: symbolic representati on for opcode Assembler: a program converts the opcode symbol to binary zf: zero fill se: sign extension

In memory Suppose R 4 contains 70 and R 5 contains 80 Why PC <- PC – 20 in address 55?

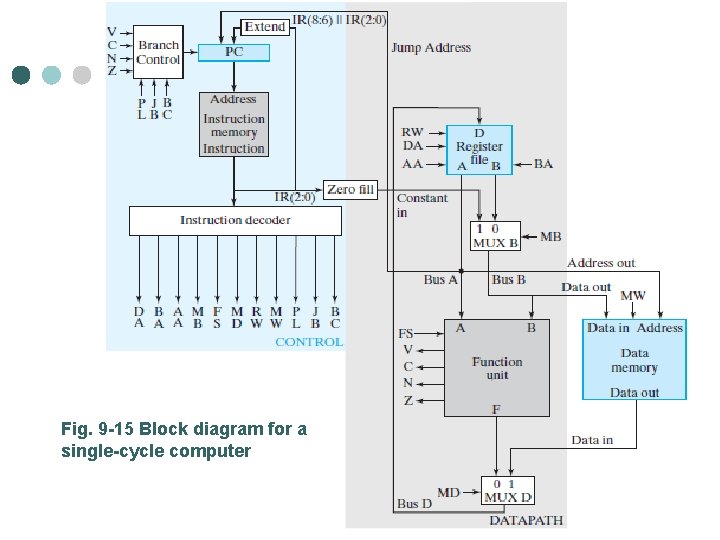

9 -8 Single-Cycle Hardwired Control ØA control unit that fetches and executes an instruction in a single clock cycle. ØWe refer to this computer as the single-cycle computer.

Fig. 9 -15 Block diagram for a single-cycle computer

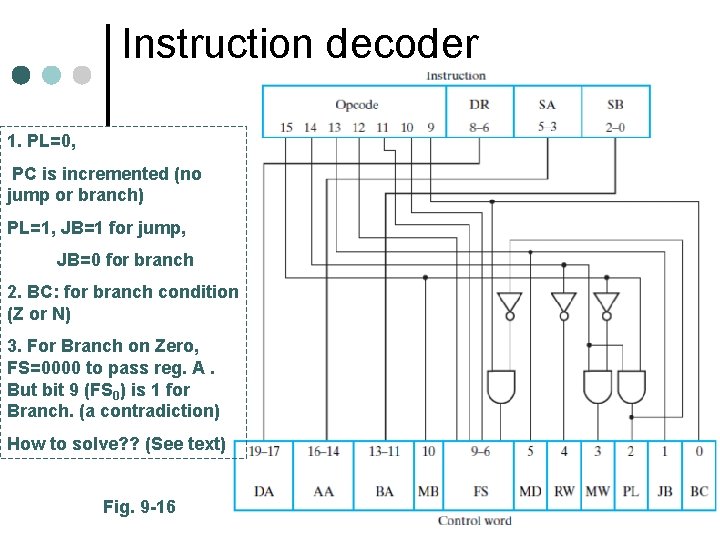

Instruction decoder 1. PL=0, PC is incremented (no jump or branch) PL=1, JB=1 for jump, JB=0 for branch 2. BC: for branch condition (Z or N) 3. For Branch on Zero, FS=0000 to pass reg. A. But bit 9 (FS 0) is 1 for Branch. (a contradiction) How to solve? ? (See text) Fig. 9 -16

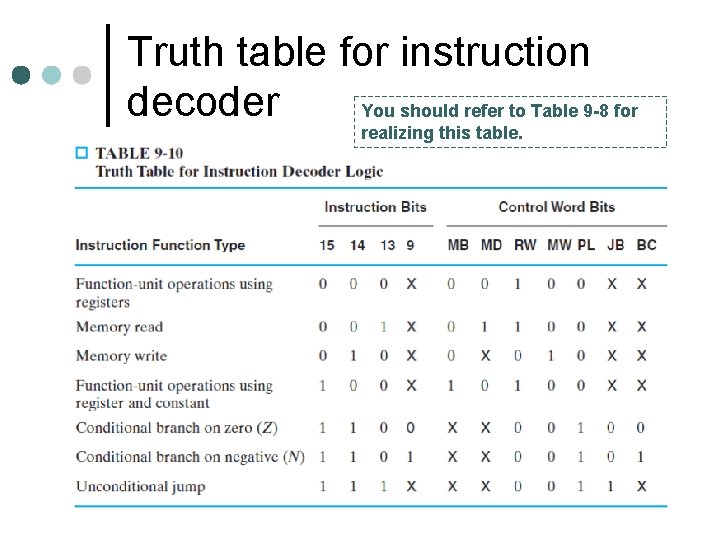

Truth table for instruction decoder You should refer to Table 9 -8 for realizing this table.

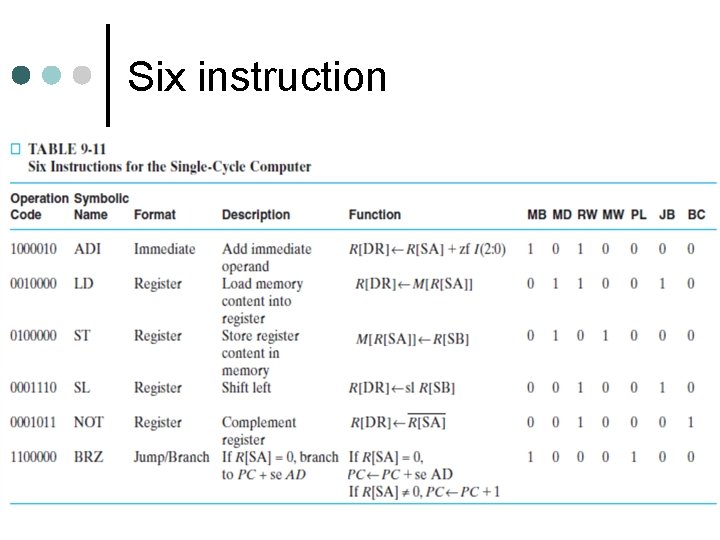

Six instruction

A program for 83 -(2+3) ¢ Suppose R 3 contains 248 l Memory in location 248 contains 2 l Memory in location 249 contains 83 l The result will be placed in location 249 l

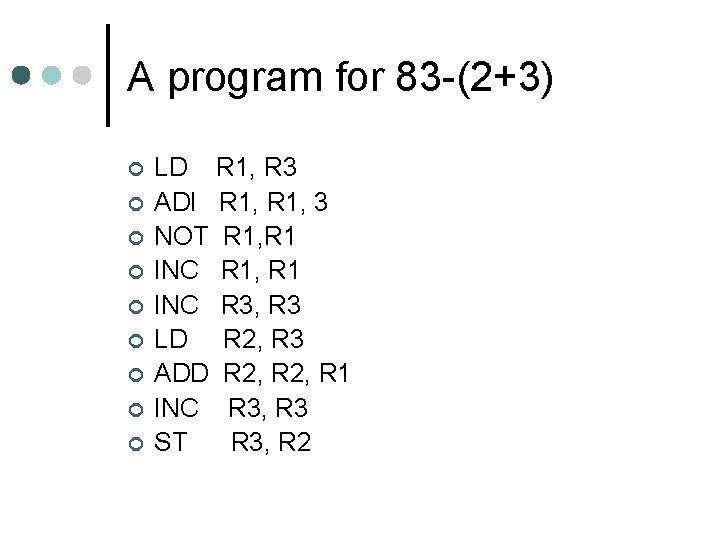

A program for 83 -(2+3) ¢ ¢ ¢ ¢ ¢ LD R 1, R 3 ADI R 1, 3 NOT R 1, R 1 INC R 3, R 3 LD R 2, R 3 ADD R 2, R 1 INC R 3, R 3 ST R 3, R 2

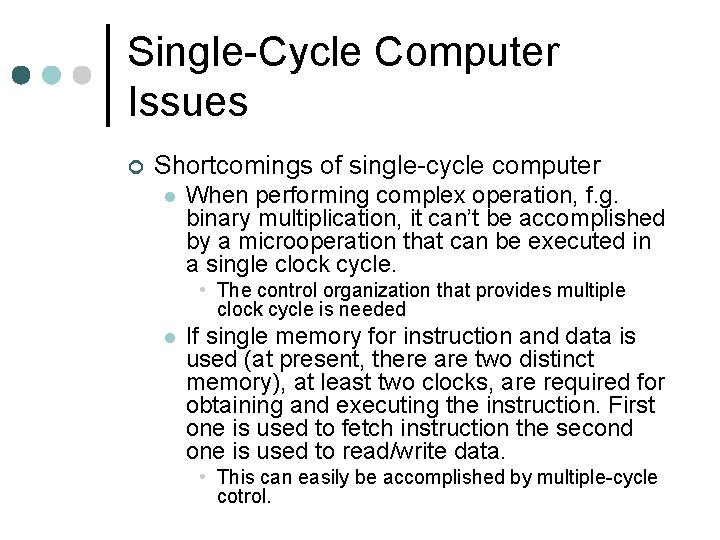

Single-Cycle Computer Issues ¢ Shortcomings of single-cycle computer l When performing complex operation, f. g. binary multiplication, it can’t be accomplished by a microoperation that can be executed in a single clock cycle. • The control organization that provides multiple clock cycle is needed l If single memory for instruction and data is used (at present, there are two distinct memory), at least two clocks, are required for obtaining and executing the instruction. First one is used to fetch instruction the second one is used to read/write data. • This can easily be accomplished by multiple-cycle cotrol.

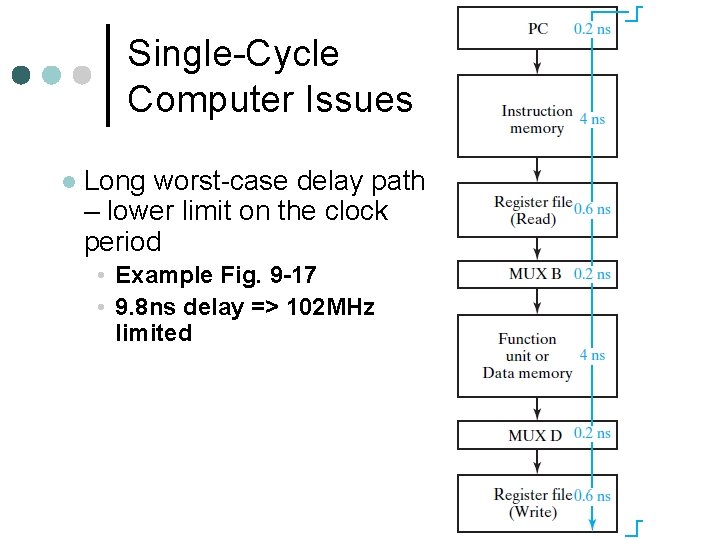

Single-Cycle Computer Issues l Long worst-case delay path – lower limit on the clock period • Example Fig. 9 -17 • 9. 8 ns delay => 102 MHz limited

End this lecture ¢ We neglect the section 9 -9 multiplecycle hardwired control due to less of time.

- Slides: 22