8259 Chip The Intel 8259 is a family

- Slides: 14

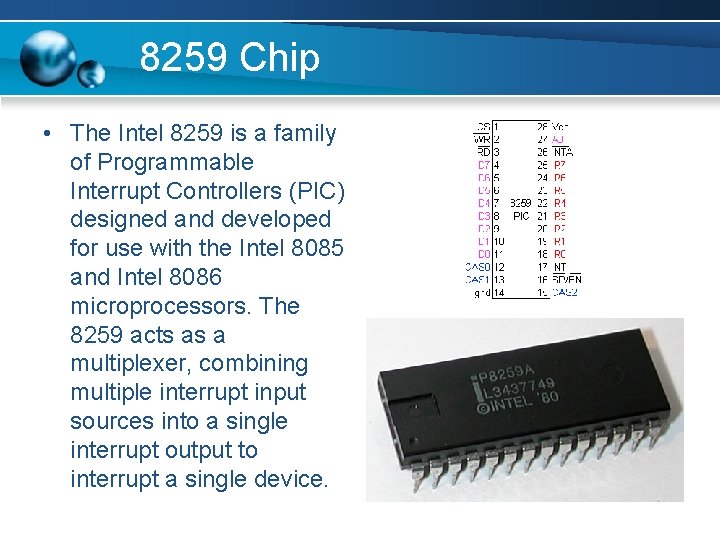

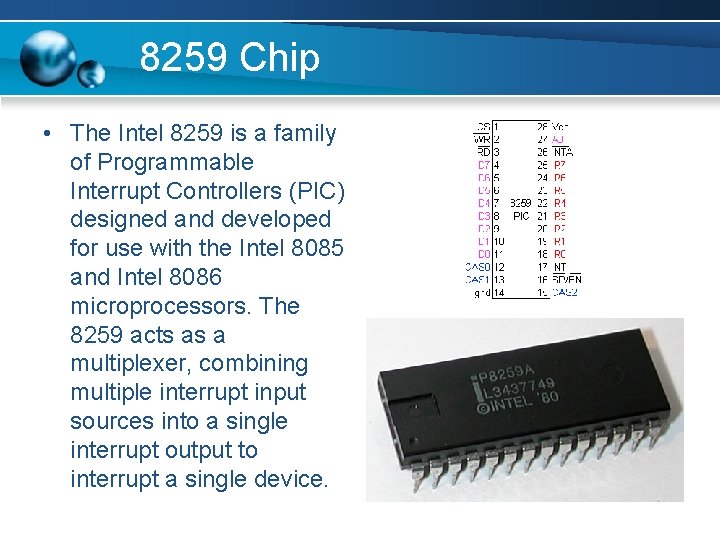

8259 Chip • The Intel 8259 is a family of Programmable Interrupt Controllers (PIC) designed and developed for use with the Intel 8085 and Intel 8086 microprocessors. The 8259 acts as a multiplexer, combining multiple interrupt input sources into a single interrupt output to interrupt a single device.

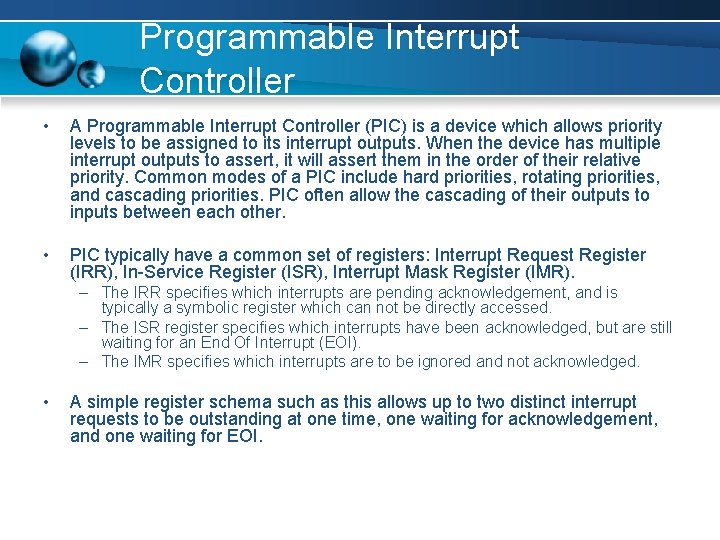

Programmable Interrupt Controller • A Programmable Interrupt Controller (PIC) is a device which allows priority levels to be assigned to its interrupt outputs. When the device has multiple interrupt outputs to assert, it will assert them in the order of their relative priority. Common modes of a PIC include hard priorities, rotating priorities, and cascading priorities. PIC often allow the cascading of their outputs to inputs between each other. • PIC typically have a common set of registers: Interrupt Request Register (IRR), In-Service Register (ISR), Interrupt Mask Register (IMR). – The IRR specifies which interrupts are pending acknowledgement, and is typically a symbolic register which can not be directly accessed. – The ISR register specifies which interrupts have been acknowledged, but are still waiting for an End Of Interrupt (EOI). – The IMR specifies which interrupts are to be ignored and not acknowledged. • A simple register schema such as this allows up to two distinct interrupt requests to be outstanding at one time, one waiting for acknowledgement, and one waiting for EOI.

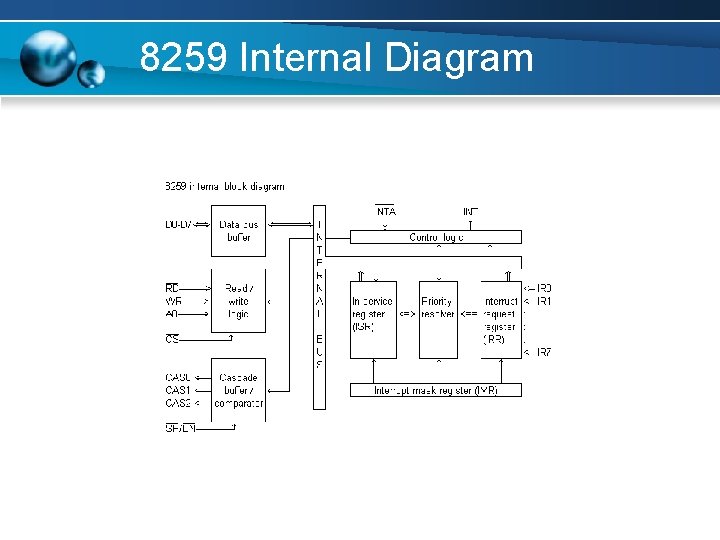

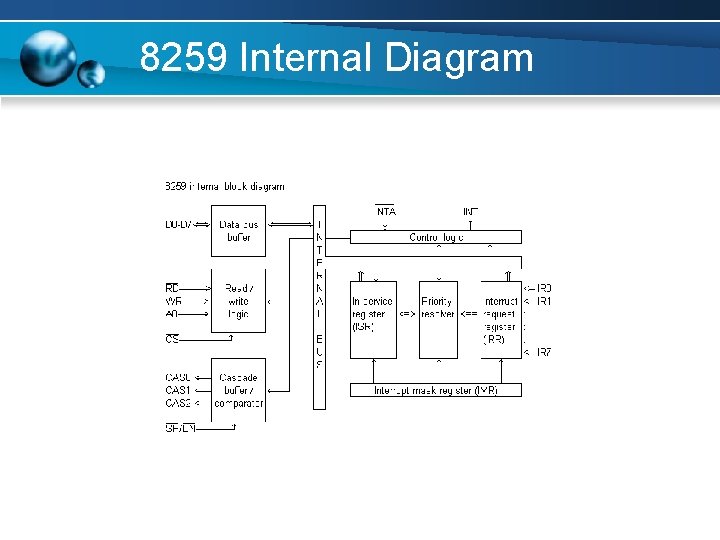

8259 Internal Diagram

Basic Interrupt Event • External device sends an interrupt signal, to one of the Interrupt Request (IR) pin, or an internal interrupt occurs. • The 8259 Chip signal to the CPU the interrupt via the INT pin. • The CPU finishes the present instruction and sends Interrupt Acknowledge (INTA). • The interrupt type is sent to the CPU via the Data bus. • The contents of the flag registers are pushed onto the stack. • Both the interrupt and flags are cleared. This disables the IR pin. • The contents of the code segment register (CS) are pushed onto the Stack. • The contents of the instruction pointer (IP) are pushed onto the Stack. • The interrupt vector contents are fetched, from and then placed into the IP and into the CS so that the next instruction executes at the Interrupt Service Routine (ISR) addressed by the interrupt vector. • While returning from the interrupt-service routine by the Interrupt Return (IRET) instruction, the IP, CS and Flag registers are popped from the Stack and return to their state prior to the interrupt.

Initialization Command Words

Initialization Command Words • Whenever a command is issued with A 0 = 0 and D 4 = 1, this is interpreted as Initialization Command Word 1 (ICW 1). ICW 1 starts the initialization sequence during which the following automatically occur: – The edge sense circuit is reset, which means that following initialization, an interrupt request (IR) input must make a low-tohigh transition to generate an interrupt. – The Interrupt Mask Register is cleared. – IR 7 input is assigned priority 7. – The slave mode address is set to 7. – Special Mask Mode is cleared and Status Read is set to IRR. – If IC 4 = 0, then all functions selected in ICW 4 are set to zero.

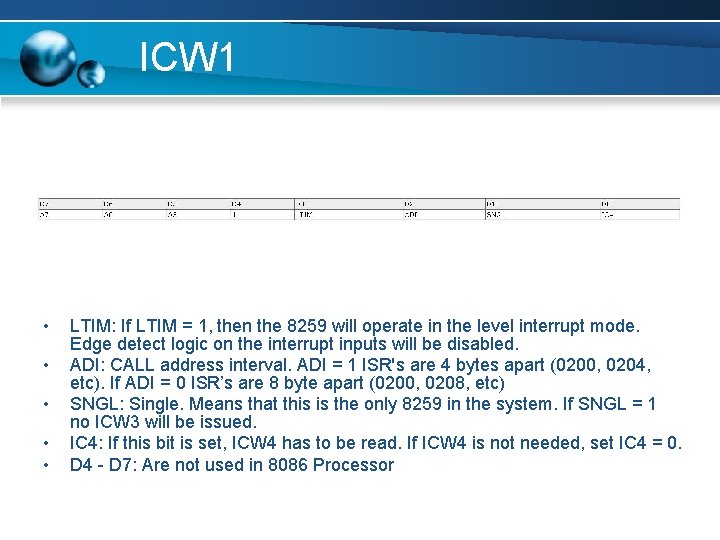

ICW 1 • • • LTIM: If LTIM = 1, then the 8259 will operate in the level interrupt mode. Edge detect logic on the interrupt inputs will be disabled. ADI: CALL address interval. ADI = 1 ISR's are 4 bytes apart (0200, 0204, etc). If ADI = 0 ISR’s are 8 byte apart (0200, 0208, etc) SNGL: Single. Means that this is the only 8259 in the system. If SNGL = 1 no ICW 3 will be issued. IC 4: If this bit is set, ICW 4 has to be read. If ICW 4 is not needed, set IC 4 = 0. D 4 - D 7: Are not used in 8086 Processor

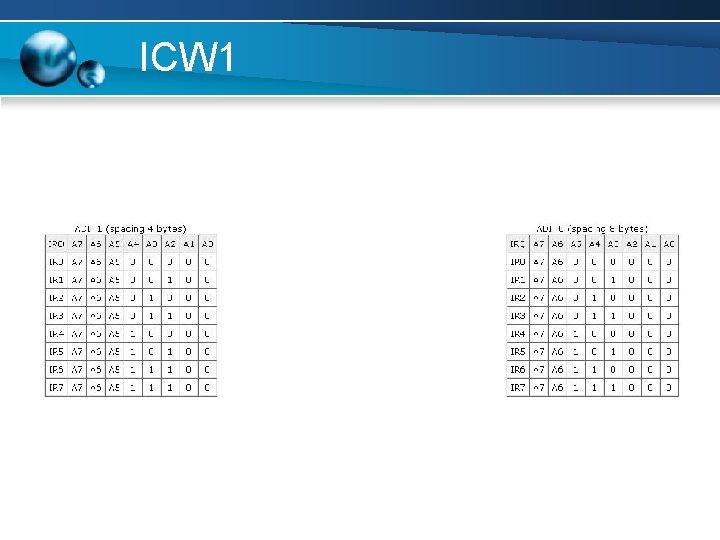

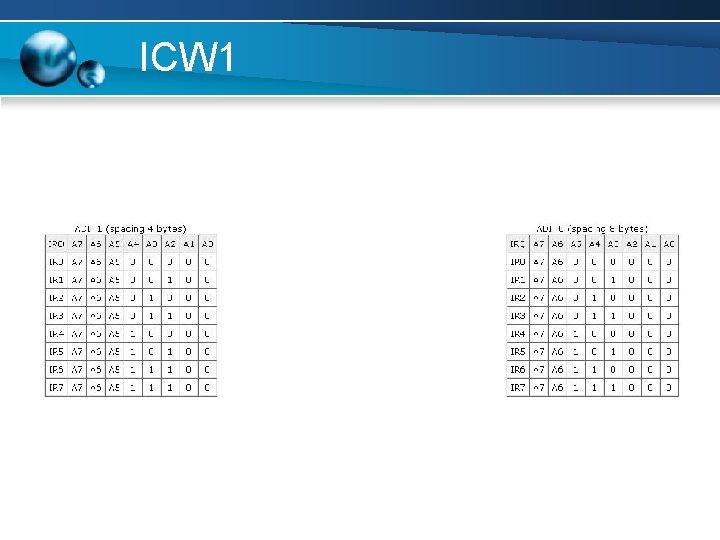

ICW 1

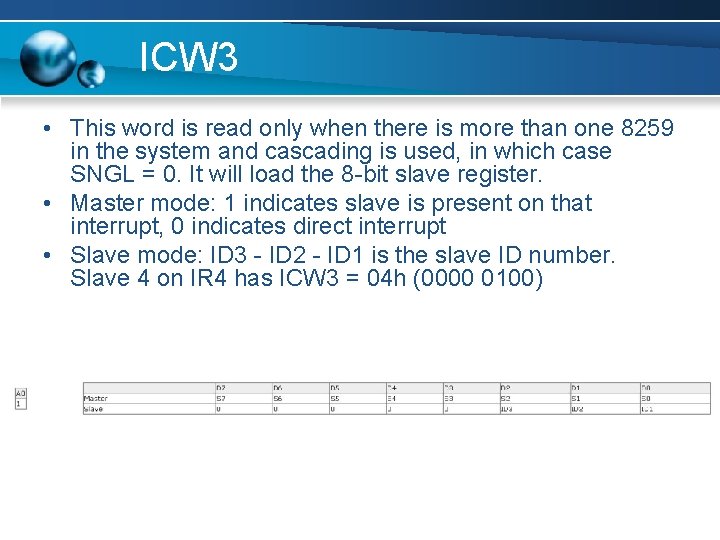

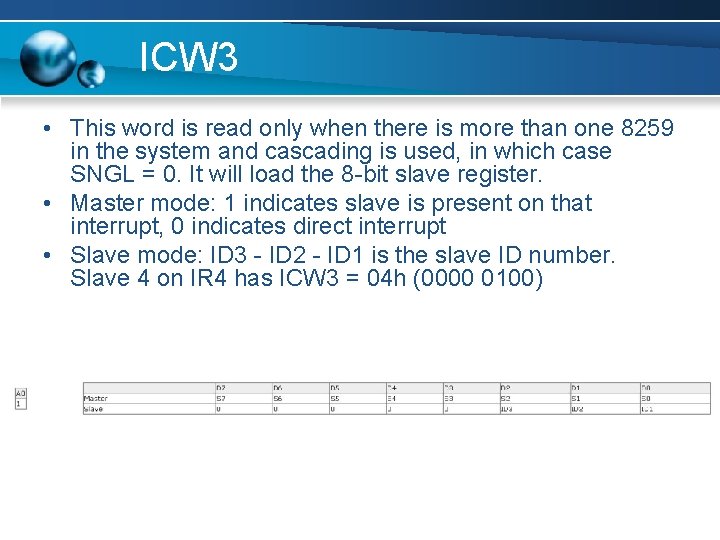

ICW 3 • This word is read only when there is more than one 8259 in the system and cascading is used, in which case SNGL = 0. It will load the 8 -bit slave register. • Master mode: 1 indicates slave is present on that interrupt, 0 indicates direct interrupt • Slave mode: ID 3 - ID 2 - ID 1 is the slave ID number. Slave 4 on IR 4 has ICW 3 = 04 h (0000 0100)

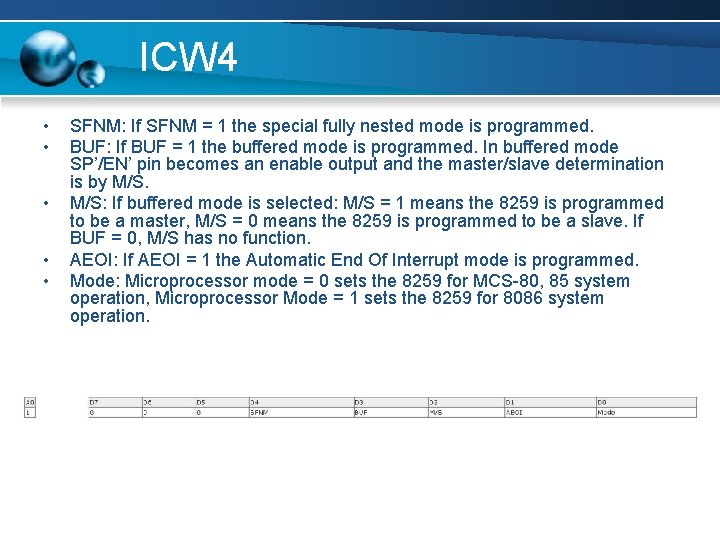

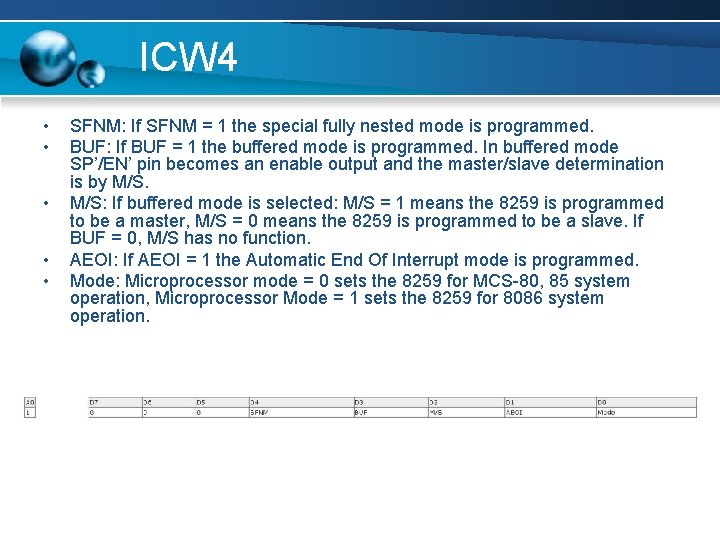

ICW 4 • • • SFNM: If SFNM = 1 the special fully nested mode is programmed. BUF: If BUF = 1 the buffered mode is programmed. In buffered mode SP’/EN’ pin becomes an enable output and the master/slave determination is by M/S: If buffered mode is selected: M/S = 1 means the 8259 is programmed to be a master, M/S = 0 means the 8259 is programmed to be a slave. If BUF = 0, M/S has no function. AEOI: If AEOI = 1 the Automatic End Of Interrupt mode is programmed. Mode: Microprocessor mode = 0 sets the 8259 for MCS-80, 85 system operation, Microprocessor Mode = 1 sets the 8259 for 8086 system operation.

Operational Command Words

Operation Command Words • After the Initialization Command Words (ICWs) are programmed into the 8259, the chip is ready to accept interrupt requests at its input lines. However, during the 8259 operation, a selection of algorithms can command the 8259 to operate in various modes through the Operation Command Words.

OCW 1 • OCW 1 sets and clears the mask bits in the Interrupt Mask Register (IMR). M 7 - M 0 represent the eight mask bits. M = 1 indicates the channel is masked, M = 0 indicates the channel is enabled.

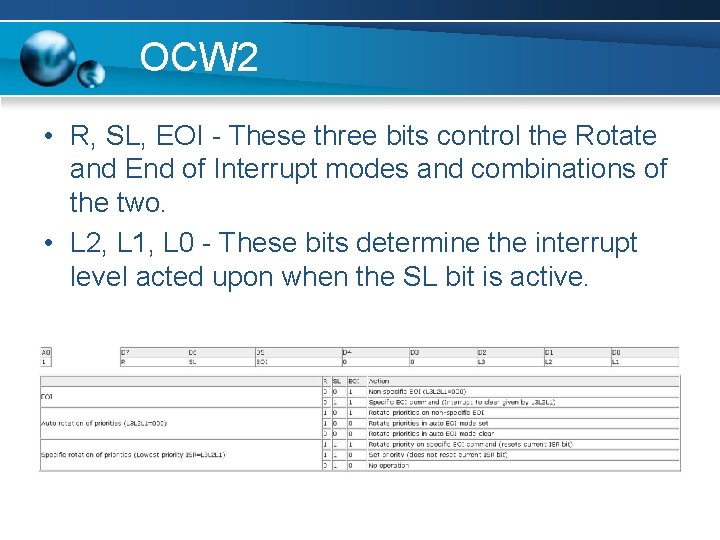

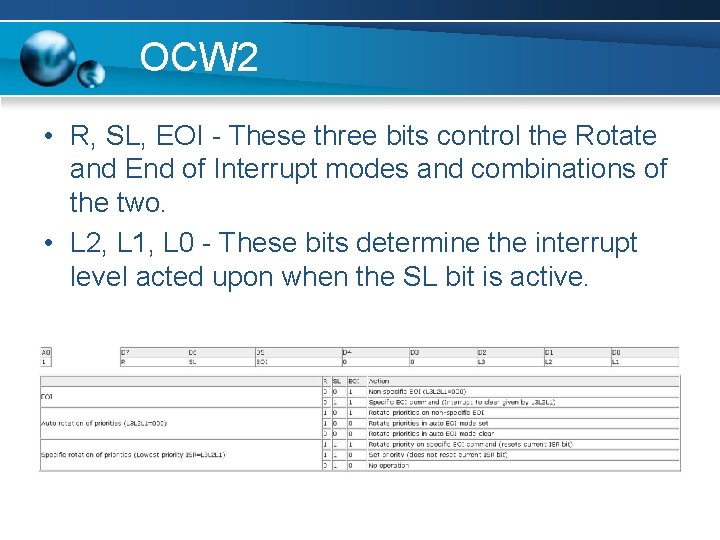

OCW 2 • R, SL, EOI - These three bits control the Rotate and End of Interrupt modes and combinations of the two. • L 2, L 1, L 0 - These bits determine the interrupt level acted upon when the SL bit is active.