8255 Programmable Peripheral Interface By Dr RN Rajotiya

8255 Programmable Peripheral Interface By Dr. RN Rajotiya

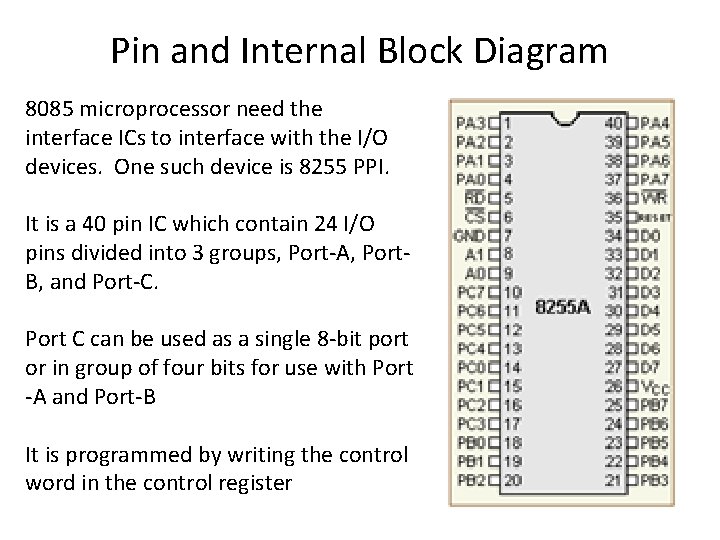

Pin and Internal Block Diagram 8085 microprocessor need the interface ICs to interface with the I/O devices. One such device is 8255 PPI. It is a 40 pin IC which contain 24 I/O pins divided into 3 groups, Port-A, Port. B, and Port-C. Port C can be used as a single 8 -bit port or in group of four bits for use with Port -A and Port-B It is programmed by writing the control word in the control register

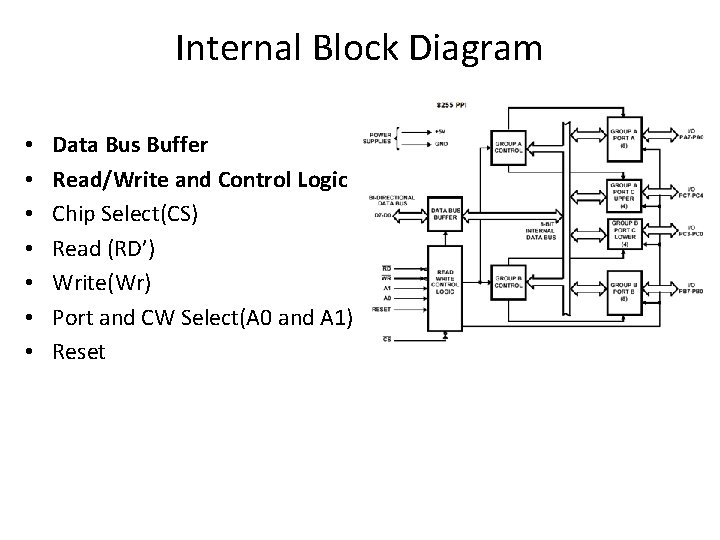

Internal Block Diagram • • Data Bus Buffer Read/Write and Control Logic Chip Select(CS) Read (RD’) Write(Wr) Port and CW Select(A 0 and A 1) Reset

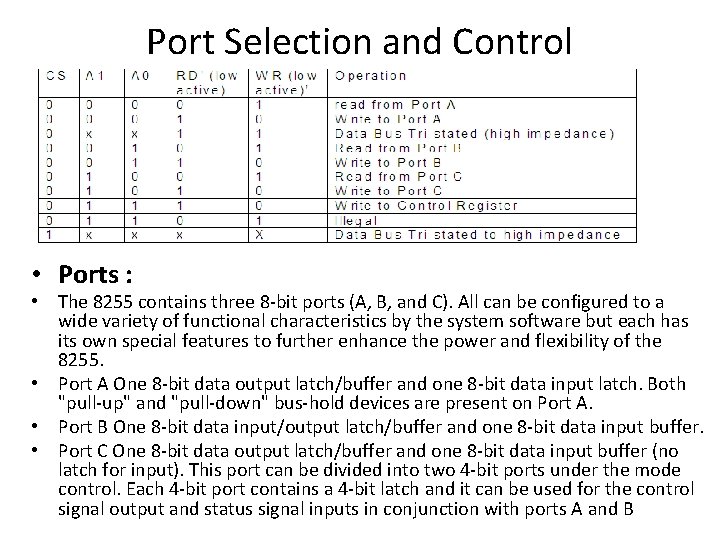

Port Selection and Control • Ports : • The 8255 contains three 8 -bit ports (A, B, and C). All can be configured to a wide variety of functional characteristics by the system software but each has its own special features to further enhance the power and flexibility of the 8255. • Port A One 8 -bit data output latch/buffer and one 8 -bit data input latch. Both "pull-up" and "pull-down" bus-hold devices are present on Port A. • Port B One 8 -bit data input/output latch/buffer and one 8 -bit data input buffer. • Port C One 8 -bit data output latch/buffer and one 8 -bit data input buffer (no latch for input). This port can be divided into two 4 -bit ports under the mode control. Each 4 -bit port contains a 4 -bit latch and it can be used for the control signal output and status signal inputs in conjunction with ports A and B

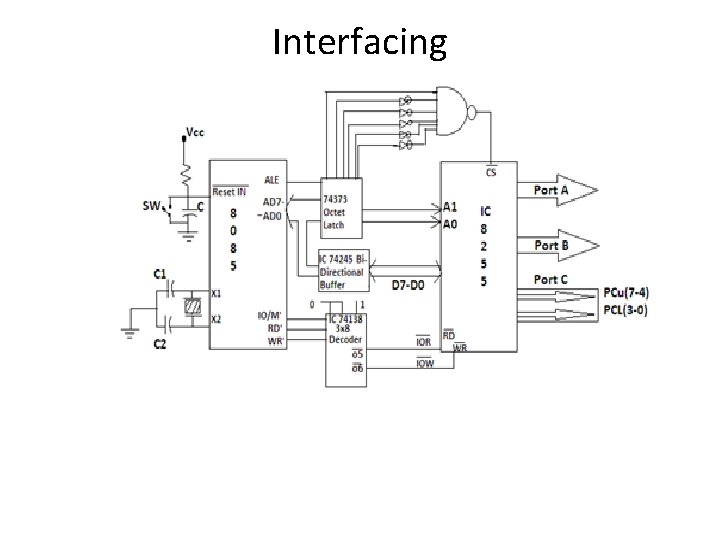

Interfacing

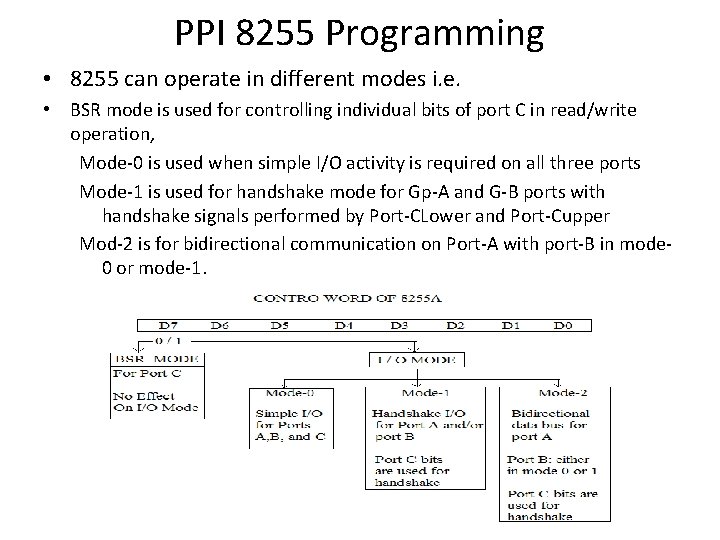

PPI 8255 Programming • 8255 can operate in different modes i. e. • BSR mode is used for controlling individual bits of port C in read/write operation, Mode-0 is used when simple I/O activity is required on all three ports Mode-1 is used for handshake mode for Gp-A and G-B ports with handshake signals performed by Port-CLower and Port-Cupper Mod-2 is for bidirectional communication on Port-A with port-B in mode 0 or mode-1.

- Slides: 6