8051 timercounter MNokhodchian yahoo com Microprocessors 1 1

- Slides: 29

8051 timer/counter M_Nokhodchian @ yahoo. com Microprocessors 1 -1

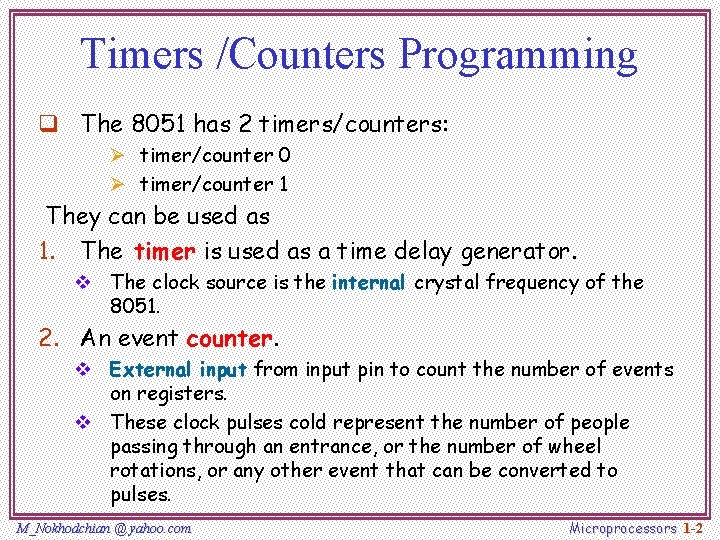

Timers /Counters Programming q The 8051 has 2 timers/counters: Ø timer/counter 0 Ø timer/counter 1 They can be used as 1. The timer is used as a time delay generator. v The clock source is the internal crystal frequency of the 8051. 2. An event counter. v External input from input pin to count the number of events on registers. v These clock pulses cold represent the number of people passing through an entrance, or the number of wheel rotations, or any other event that can be converted to pulses. M_Nokhodchian @ yahoo. com Microprocessors 1 -2

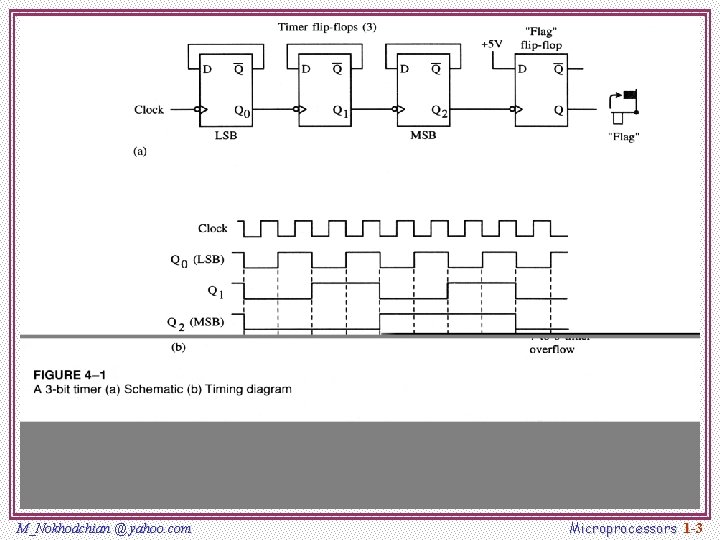

M_Nokhodchian @ yahoo. com Microprocessors 1 -3

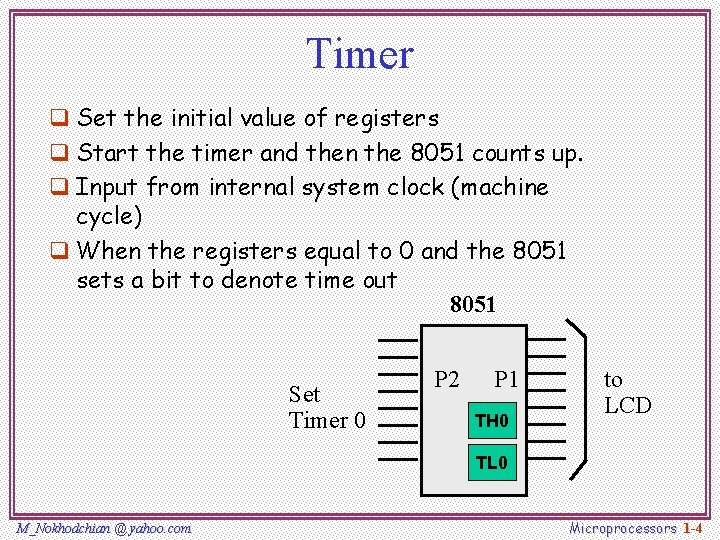

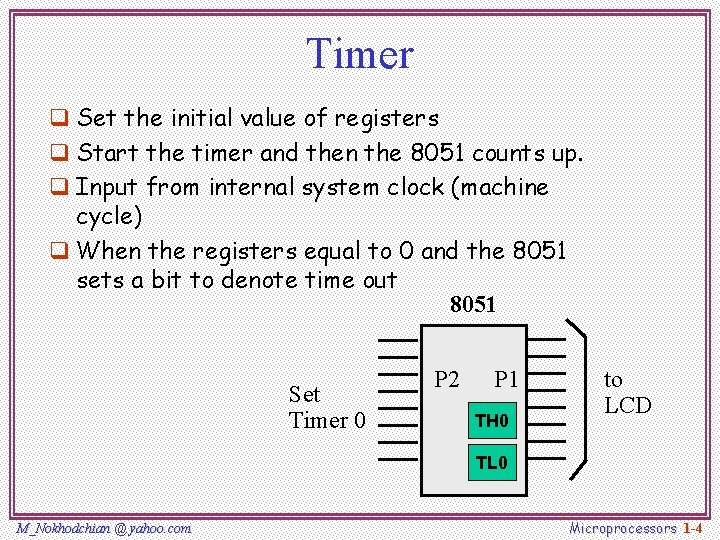

Timer q Set the initial value of registers q Start the timer and then the 8051 counts up. q Input from internal system clock (machine cycle) q When the registers equal to 0 and the 8051 sets a bit to denote time out 8051 Set Timer 0 P 2 P 1 TH 0 to LCD TL 0 M_Nokhodchian @ yahoo. com Microprocessors 1 -4

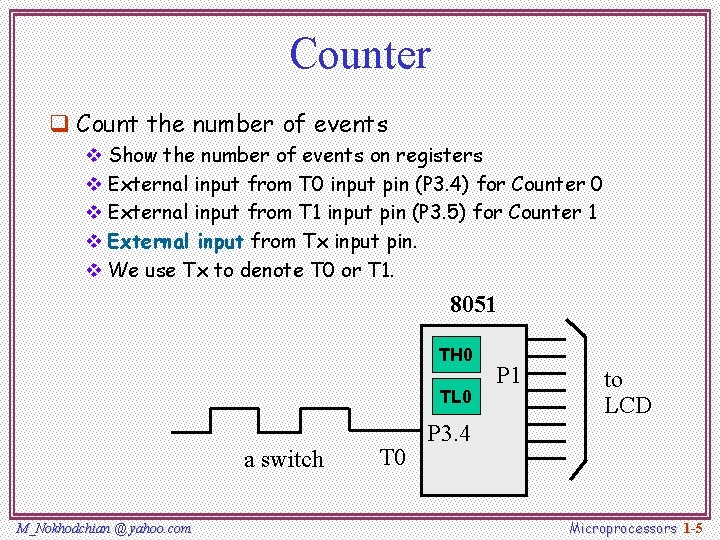

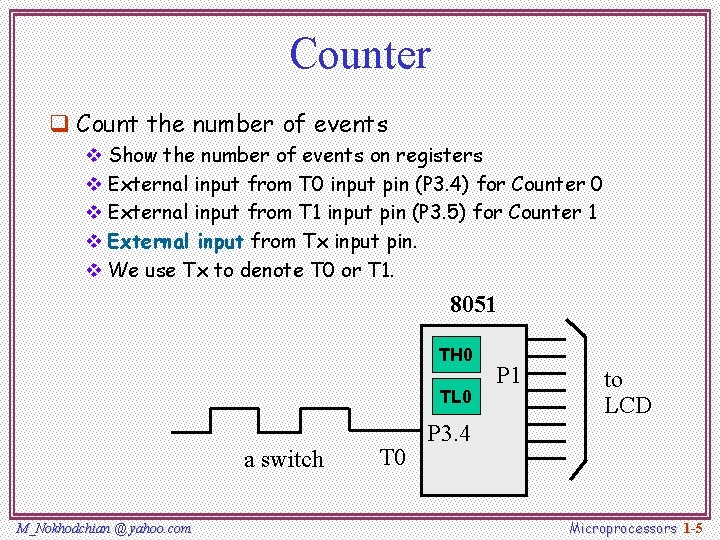

Counter q Count the number of events v Show the number of events on registers v External input from T 0 input pin (P 3. 4) for Counter 0 v External input from T 1 input pin (P 3. 5) for Counter 1 v External input from Tx input pin. v We use Tx to denote T 0 or T 1. 8051 TH 0 TL 0 a switch M_Nokhodchian @ yahoo. com T 0 P 1 to LCD P 3. 4 Microprocessors 1 -5

Registers Used in Timer/Counter q TH 0, TL 0, TH 1, TL 1 q TMOD (Timer mode register) q TCON (Timer control register) M_Nokhodchian @ yahoo. com Microprocessors 1 -6

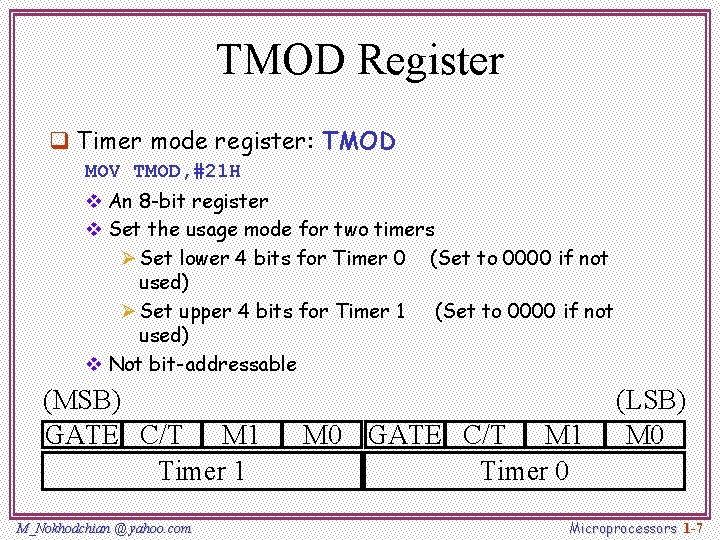

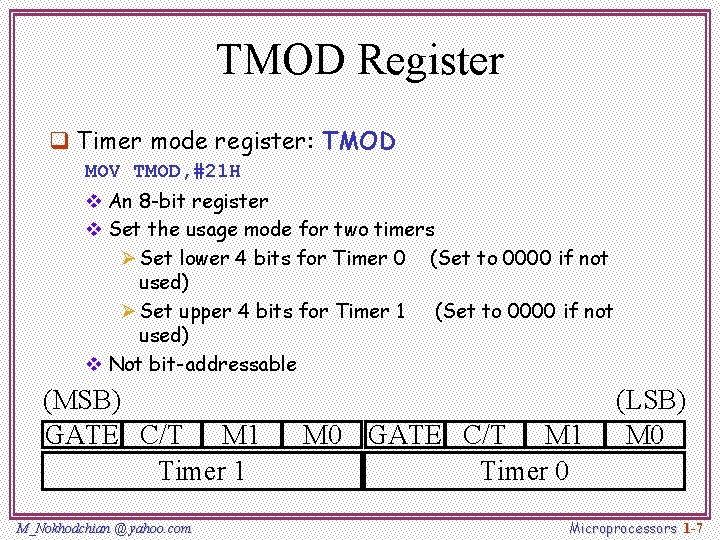

TMOD Register q Timer mode register: TMOD MOV TMOD, #21 H v An 8 -bit register v Set the usage mode for two timers Ø Set lower 4 bits for Timer 0 (Set to 0000 if not used) Ø Set upper 4 bits for Timer 1 (Set to 0000 if not used) v Not bit-addressable (MSB) GATE C/T M 1 Timer 1 M_Nokhodchian @ yahoo. com M 0 GATE C/T M 1 Timer 0 (LSB) M 0 Microprocessors 1 -7

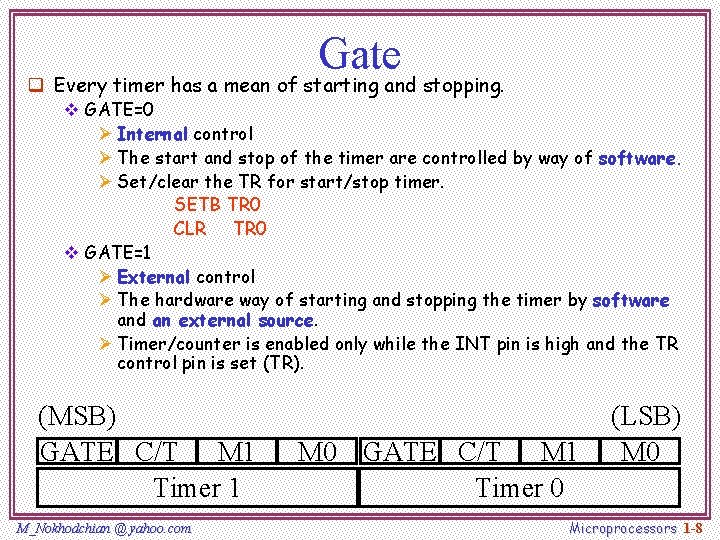

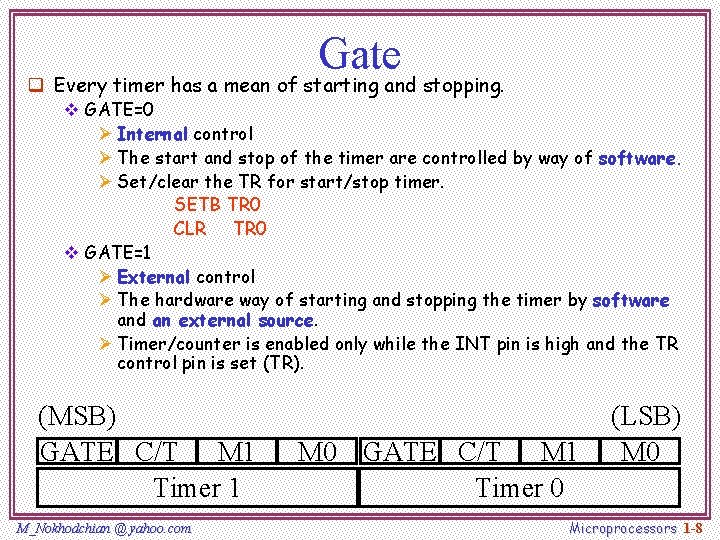

Gate q Every timer has a mean of starting and stopping. v GATE=0 Ø Internal control Ø The start and stop of the timer are controlled by way of software. Ø Set/clear the TR for start/stop timer. SETB TR 0 CLR TR 0 v GATE=1 Ø External control Ø The hardware way of starting and stopping the timer by software and an external source. Ø Timer/counter is enabled only while the INT pin is high and the TR control pin is set (TR). (MSB) GATE C/T M 1 Timer 1 M_Nokhodchian @ yahoo. com M 0 GATE C/T M 1 Timer 0 (LSB) M 0 Microprocessors 1 -8

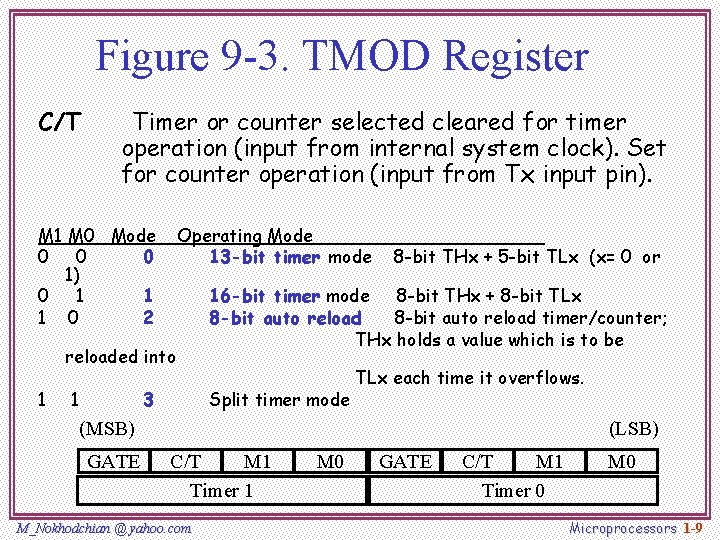

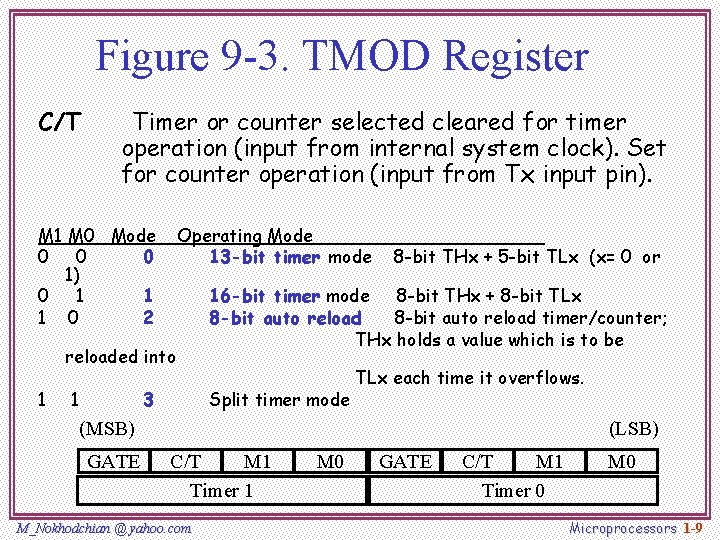

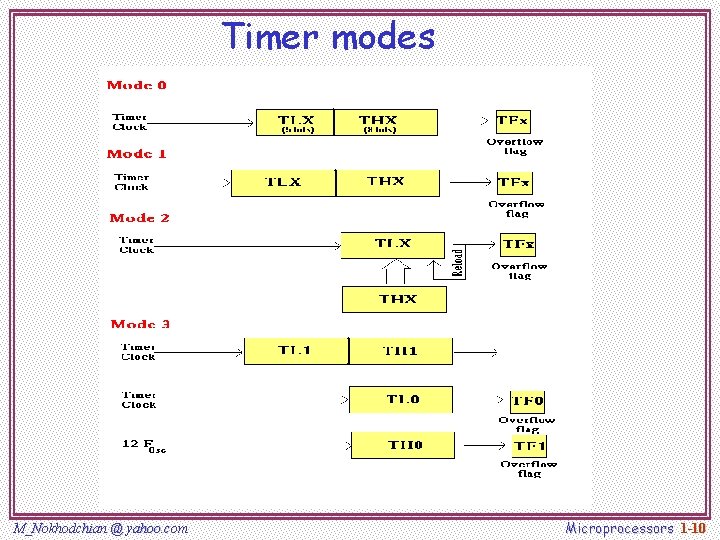

Figure 9 -3. TMOD Register C/T Timer or counter selected cleared for timer operation (input from internal system clock). Set for counter operation (input from Tx input pin). M 1 M 0 Mode 0 0 0 1) 0 1 1 1 0 2 Operating Mode 13 -bit timer mode reloaded into 1 1 3 8 -bit THx + 5 -bit TLx (x= 0 or 16 -bit timer mode 8 -bit THx + 8 -bit TLx 8 -bit auto reload timer/counter; THx holds a value which is to be Split timer mode TLx each time it overflows. (MSB) GATE (LSB) C/T M 1 Timer 1 M_Nokhodchian @ yahoo. com M 0 GATE C/T M 1 Timer 0 Microprocessors 1 -9

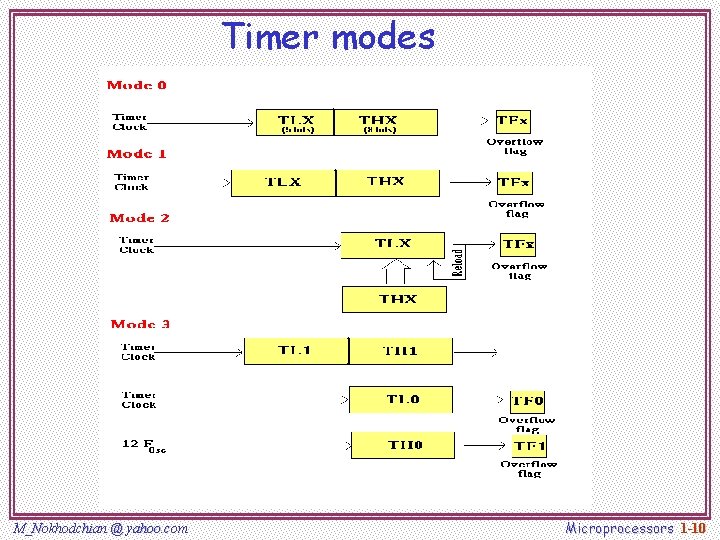

Timer modes M_Nokhodchian @ yahoo. com Microprocessors 1 -10

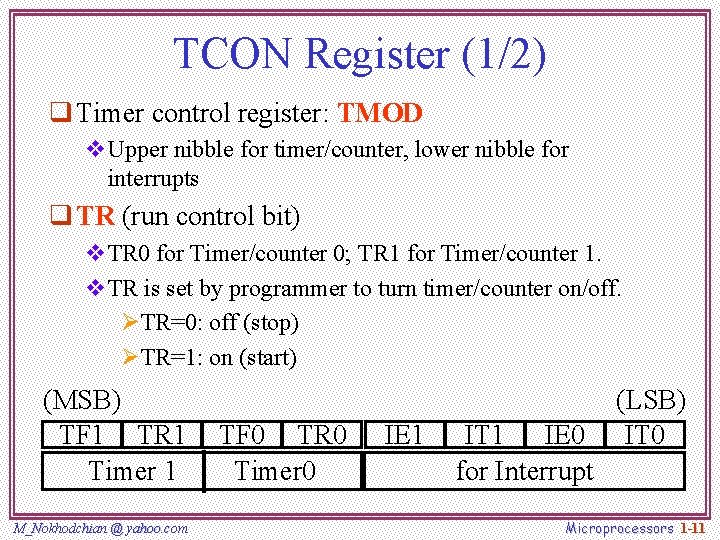

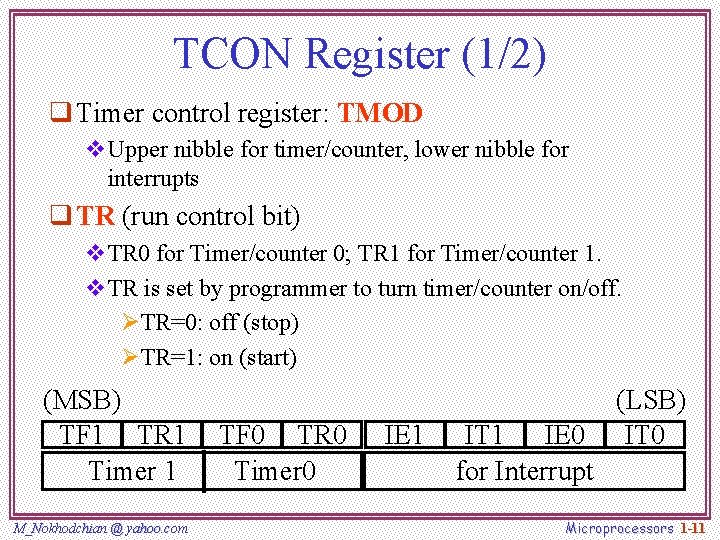

TCON Register (1/2) q Timer control register: TMOD v. Upper nibble for timer/counter, lower nibble for interrupts q TR (run control bit) v. TR 0 for Timer/counter 0; TR 1 for Timer/counter 1. v. TR is set by programmer to turn timer/counter on/off. ØTR=0: off (stop) ØTR=1: on (start) (MSB) TF 1 TR 1 Timer 1 M_Nokhodchian @ yahoo. com TF 0 TR 0 Timer 0 IE 1 IT 1 IE 0 for Interrupt (LSB) IT 0 Microprocessors 1 -11

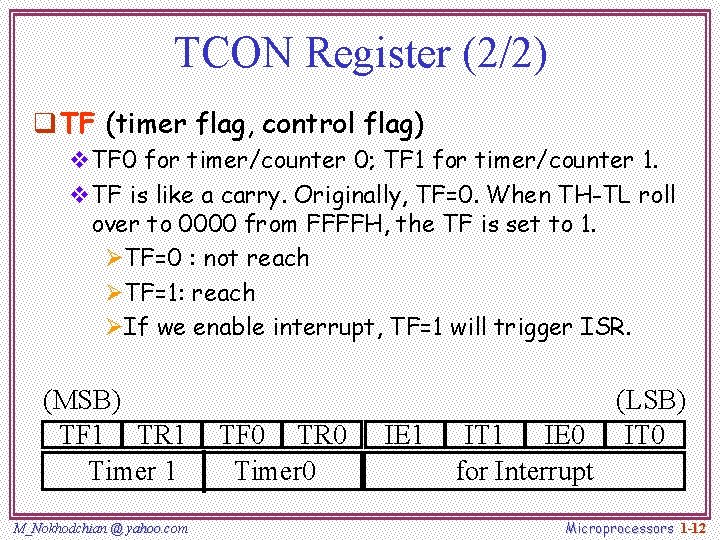

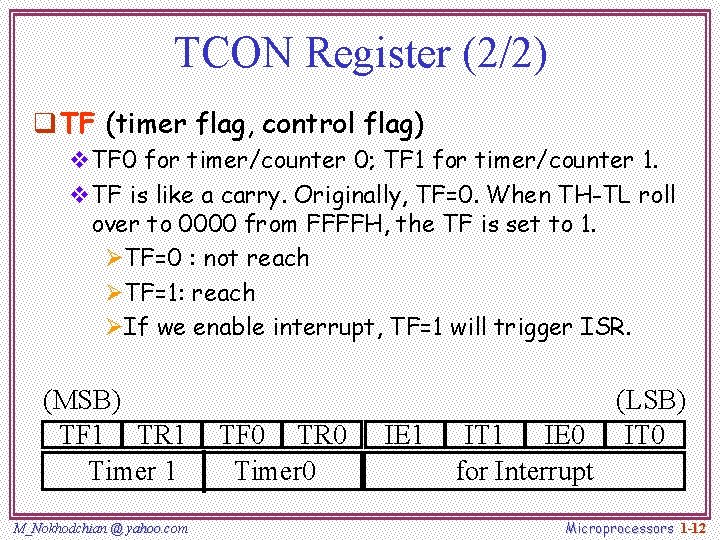

TCON Register (2/2) q TF (timer flag, control flag) v. TF 0 for timer/counter 0; TF 1 for timer/counter 1. v. TF is like a carry. Originally, TF=0. When TH-TL roll over to 0000 from FFFFH, the TF is set to 1. ØTF=0 : not reach ØTF=1: reach ØIf we enable interrupt, TF=1 will trigger ISR. (MSB) TF 1 TR 1 Timer 1 M_Nokhodchian @ yahoo. com TF 0 TR 0 Timer 0 IE 1 IT 1 IE 0 for Interrupt (LSB) IT 0 Microprocessors 1 -12

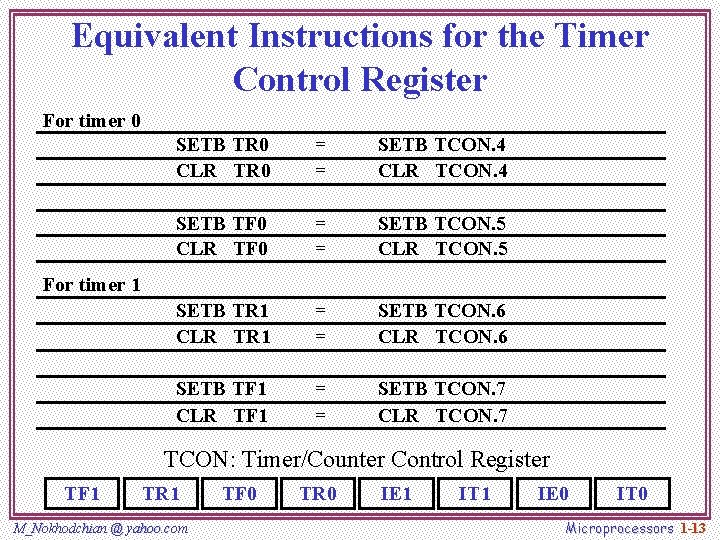

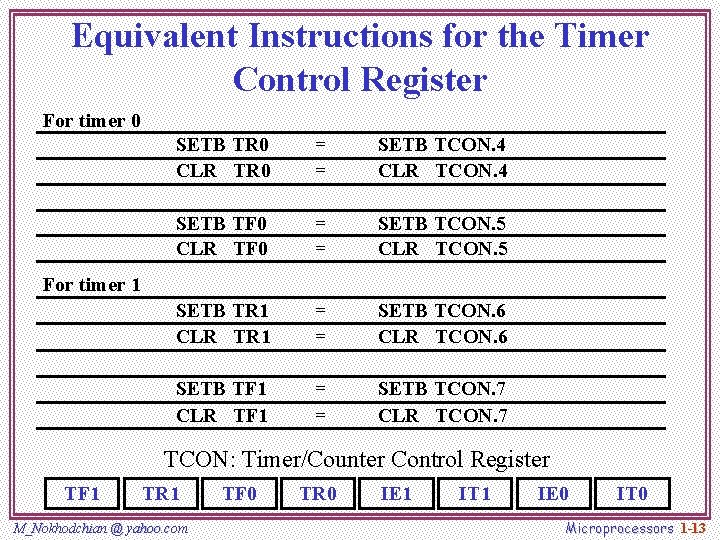

Equivalent Instructions for the Timer Control Register For timer 0 SETB TR 0 CLR TR 0 = = SETB TCON. 4 CLR TCON. 4 SETB TF 0 CLR TF 0 = = SETB TCON. 5 CLR TCON. 5 SETB TR 1 CLR TR 1 = = SETB TCON. 6 CLR TCON. 6 SETB TF 1 CLR TF 1 = = SETB TCON. 7 CLR TCON. 7 For timer 1 TCON: Timer/Counter Control Register TF 1 TR 1 M_Nokhodchian @ yahoo. com TF 0 TR 0 IE 1 IT 1 IE 0 IT 0 Microprocessors 1 -13

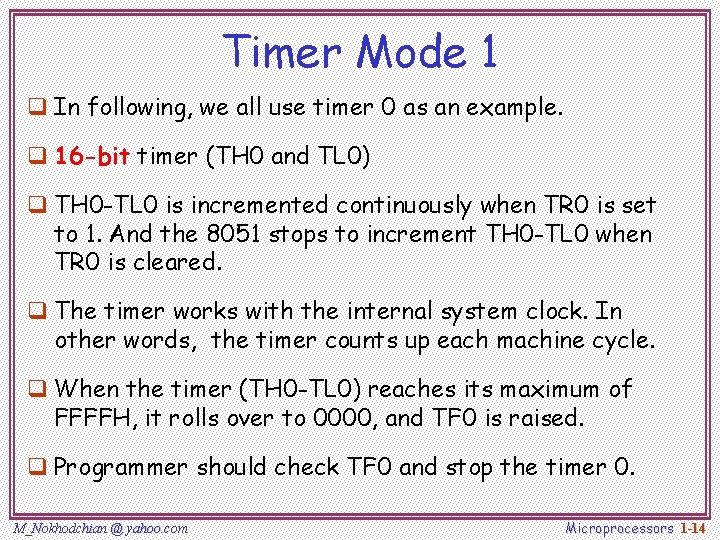

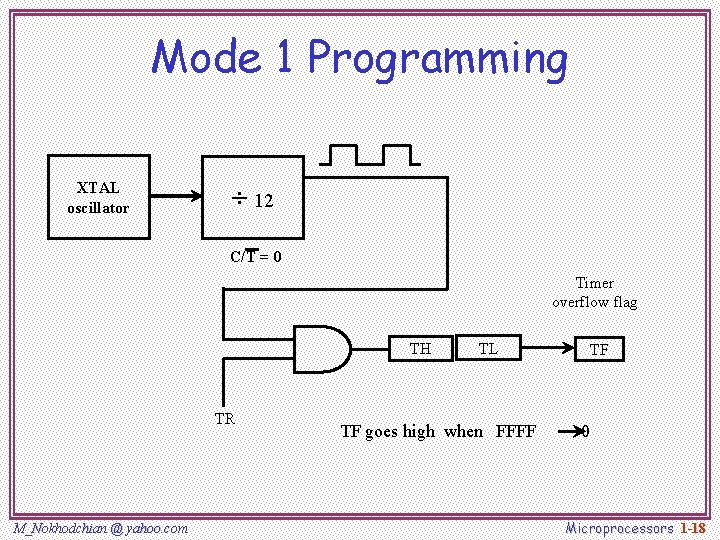

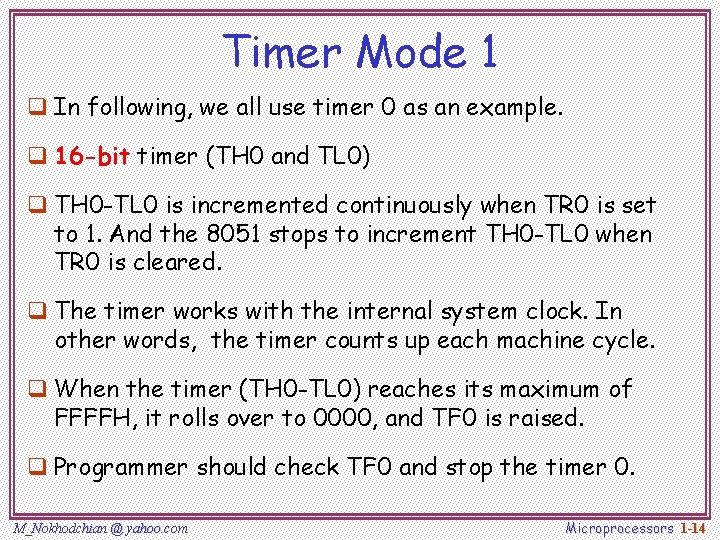

Timer Mode 1 q In following, we all use timer 0 as an example. q 16 -bit timer (TH 0 and TL 0) q TH 0 -TL 0 is incremented continuously when TR 0 is set to 1. And the 8051 stops to increment TH 0 -TL 0 when TR 0 is cleared. q The timer works with the internal system clock. In other words, the timer counts up each machine cycle. q When the timer (TH 0 -TL 0) reaches its maximum of FFFFH, it rolls over to 0000, and TF 0 is raised. q Programmer should check TF 0 and stop the timer 0. M_Nokhodchian @ yahoo. com Microprocessors 1 -14

Steps of Mode 1 (1/3) 1. Choose mode 1 timer 0 v MOV TMOD, #01 H 2. Set the original value to TH 0 and TL 0. v MOV TH 0, #FFH v MOV TL 0, #FCH 3. You had better to clear the flag to monitor: TF 0=0. v CLR TF 0 4. Start the timer. v SETB TR 0 M_Nokhodchian @ yahoo. com Microprocessors 1 -15

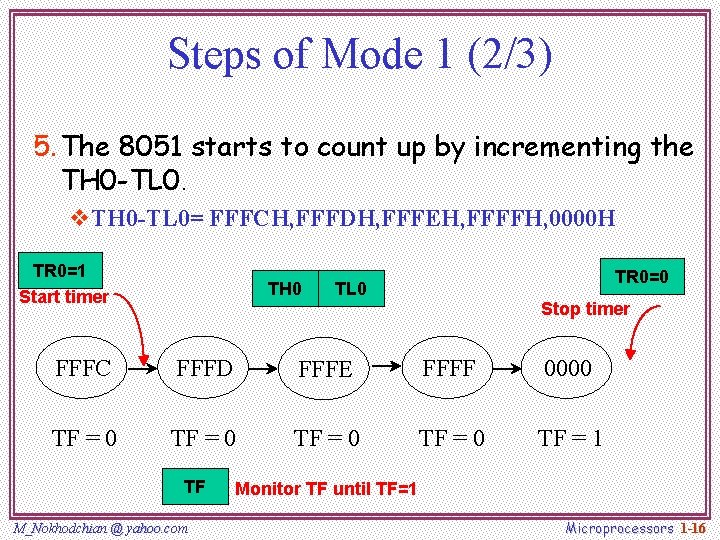

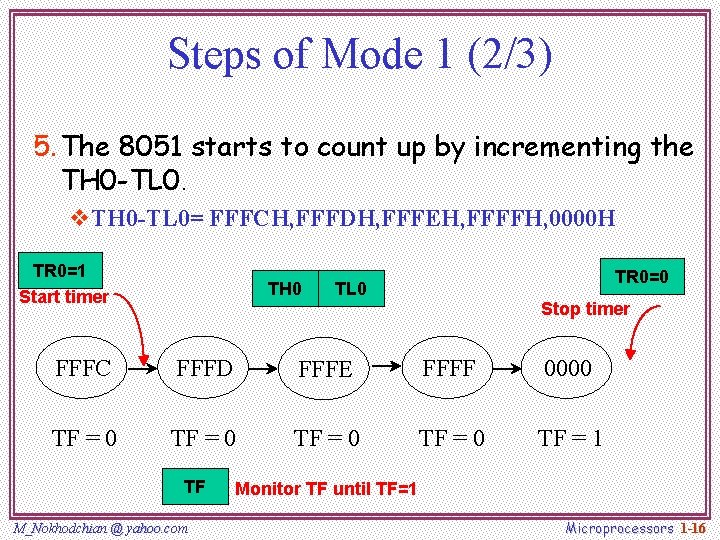

Steps of Mode 1 (2/3) 5. The 8051 starts to count up by incrementing the TH 0 -TL 0. v. TH 0 -TL 0= FFFCH, FFFDH, FFFEH, FFFFH, 0000 H TR 0=1 Start timer TH 0 TR 0=0 TL 0 Stop timer FFFC FFFD FFFE FFFF 0000 TF = 0 TF = 1 TF M_Nokhodchian @ yahoo. com Monitor TF until TF=1 Microprocessors 1 -16

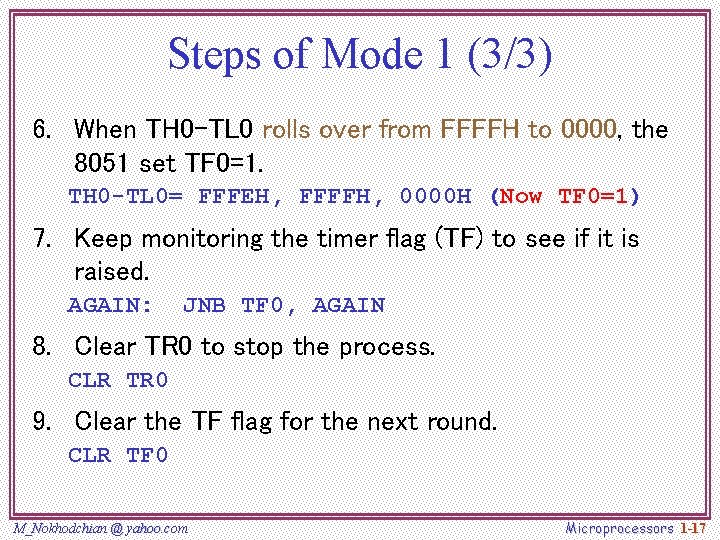

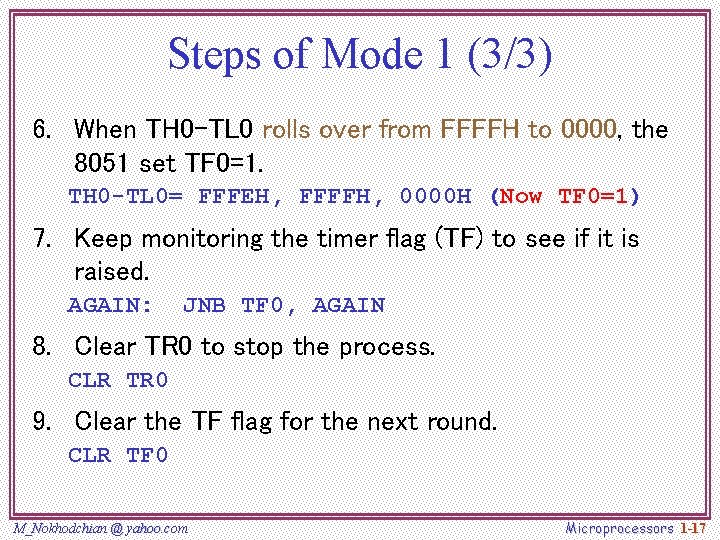

Steps of Mode 1 (3/3) 6. When TH 0 -TL 0 rolls over from FFFFH to 0000, the 8051 set TF 0=1. TH 0 -TL 0= FFFEH, FFFFH, 0000 H (Now TF 0=1) 7. Keep monitoring the timer flag (TF) to see if it is raised. AGAIN: JNB TF 0, AGAIN 8. Clear TR 0 to stop the process. CLR TR 0 9. Clear the TF flag for the next round. CLR TF 0 M_Nokhodchian @ yahoo. com Microprocessors 1 -17

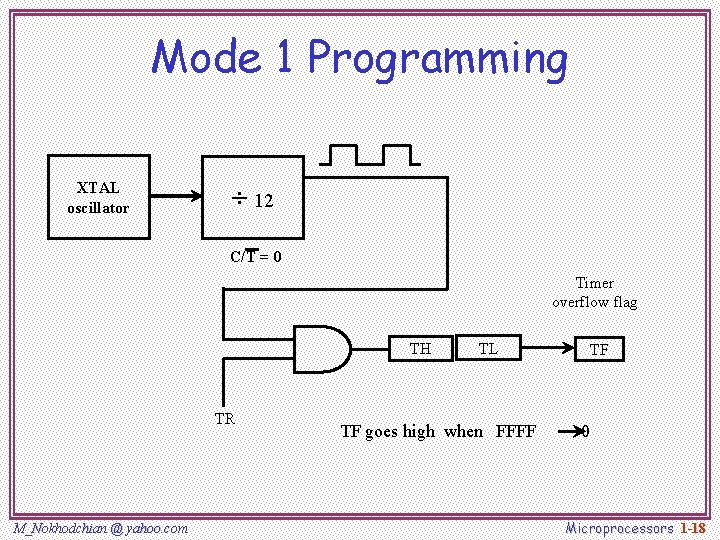

Mode 1 Programming XTAL oscillator ÷ 12 C/T = 0 Timer overflow flag TH TR M_Nokhodchian @ yahoo. com TL TF goes high when FFFF TF 0 Microprocessors 1 -18

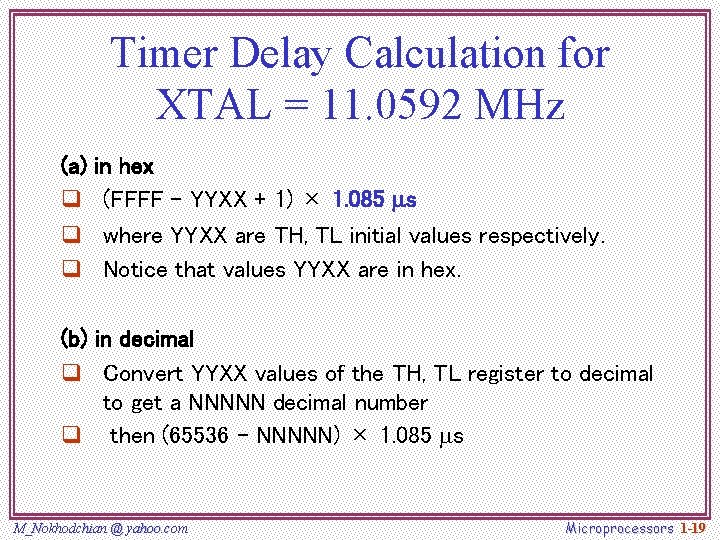

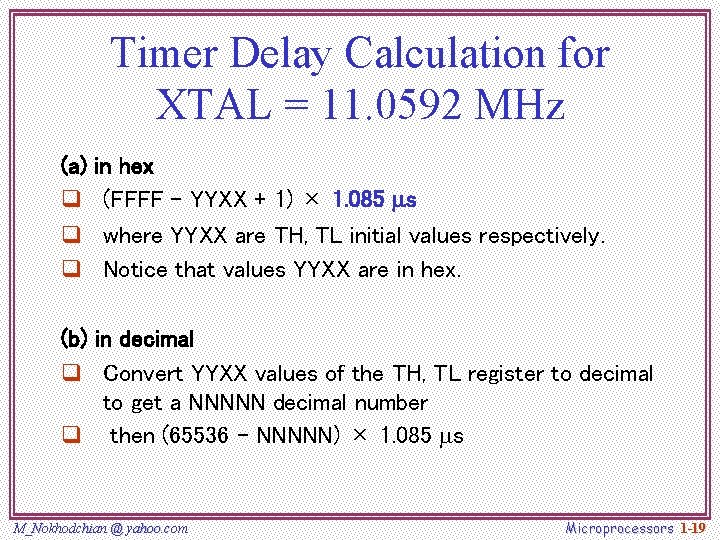

Timer Delay Calculation for XTAL = 11. 0592 MHz (a) q q q in hex (FFFF – YYXX + 1) × 1. 085 s where YYXX are TH, TL initial values respectively. Notice that values YYXX are in hex. (b) in decimal q Convert YYXX values of the TH, TL register to decimal to get a NNNNN decimal number q then (65536 – NNNNN) × 1. 085 s M_Nokhodchian @ yahoo. com Microprocessors 1 -19

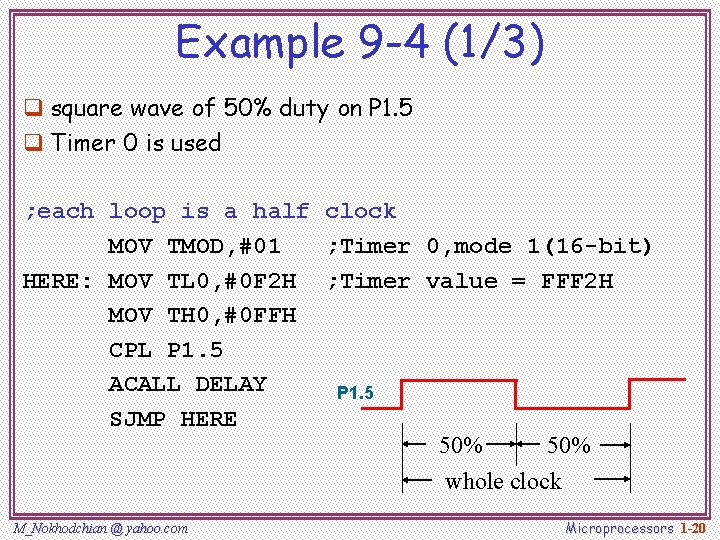

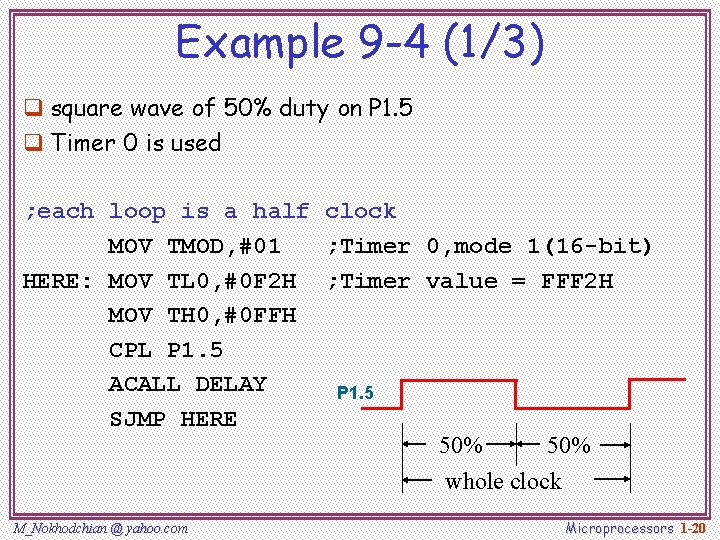

Example 9 -4 (1/3) q square wave of 50% duty on P 1. 5 q Timer 0 is used ; each loop is a half clock MOV TMOD, #01 ; Timer 0, mode 1(16 -bit) HERE: MOV TL 0, #0 F 2 H ; Timer value = FFF 2 H MOV TH 0, #0 FFH CPL P 1. 5 ACALL DELAY P 1. 5 SJMP HERE 50% whole clock M_Nokhodchian @ yahoo. com Microprocessors 1 -20

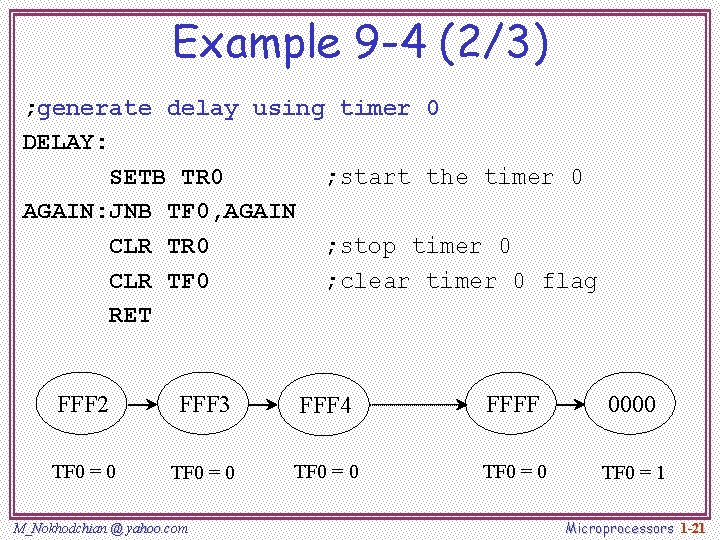

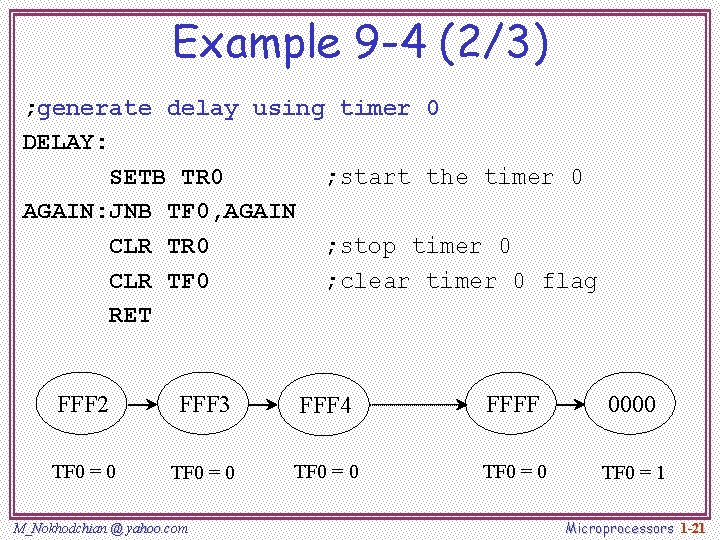

Example 9 -4 (2/3) ; generate delay using timer 0 DELAY: SETB TR 0 ; start the timer 0 AGAIN: JNB TF 0, AGAIN CLR TR 0 ; stop timer 0 CLR TF 0 ; clear timer 0 flag RET FFF 2 FFF 3 FFF 4 FFFF 0000 TF 0 = 0 TF 0 = 1 M_Nokhodchian @ yahoo. com Microprocessors 1 -21

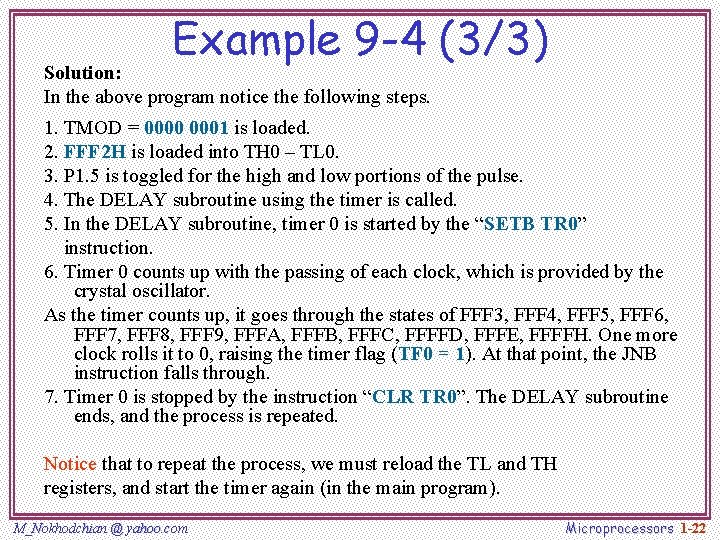

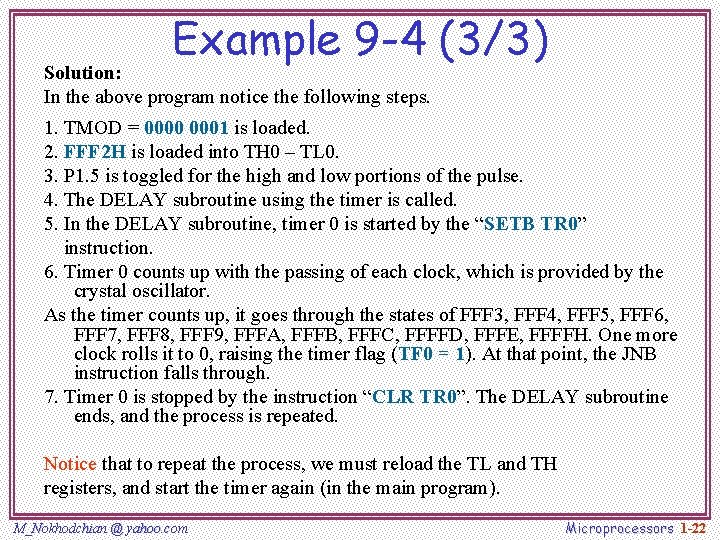

Example 9 -4 (3/3) Solution: In the above program notice the following steps. 1. TMOD = 0000 0001 is loaded. 2. FFF 2 H is loaded into TH 0 – TL 0. 3. P 1. 5 is toggled for the high and low portions of the pulse. 4. The DELAY subroutine using the timer is called. 5. In the DELAY subroutine, timer 0 is started by the “SETB TR 0” instruction. 6. Timer 0 counts up with the passing of each clock, which is provided by the crystal oscillator. As the timer counts up, it goes through the states of FFF 3, FFF 4, FFF 5, FFF 6, FFF 7, FFF 8, FFF 9, FFFA, FFFB, FFFC, FFFFD, FFFE, FFFFH. One more clock rolls it to 0, raising the timer flag (TF 0 = 1). At that point, the JNB instruction falls through. 7. Timer 0 is stopped by the instruction “CLR TR 0”. The DELAY subroutine ends, and the process is repeated. Notice that to repeat the process, we must reload the TL and TH registers, and start the timer again (in the main program). M_Nokhodchian @ yahoo. com Microprocessors 1 -22

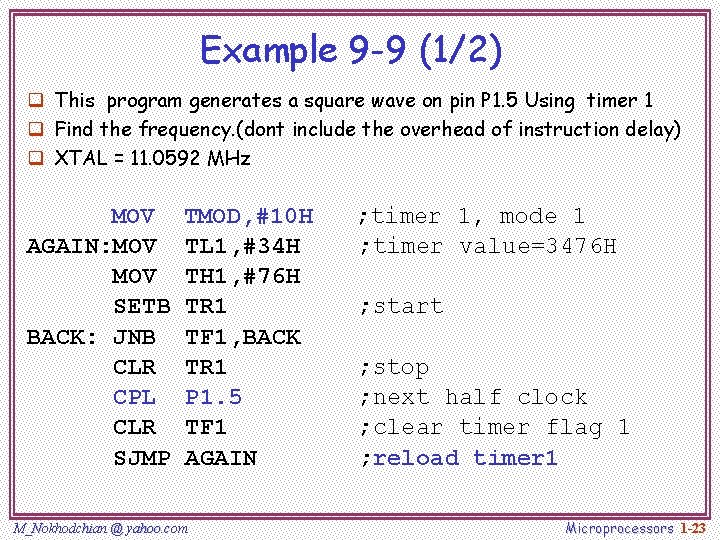

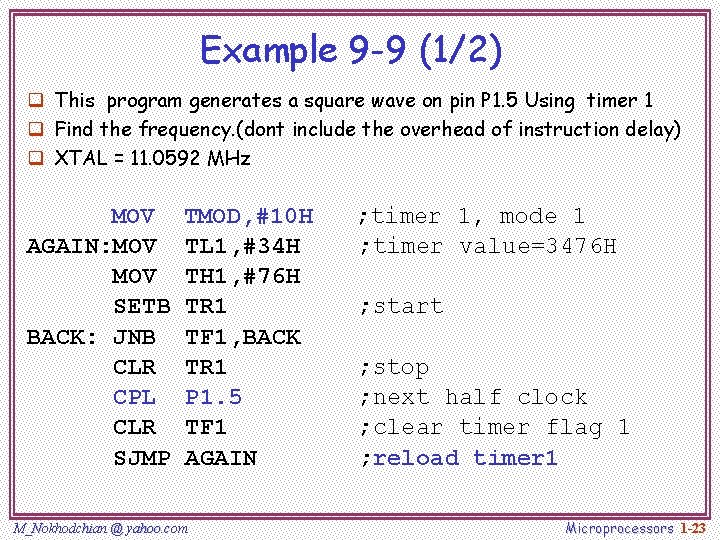

Example 9 -9 (1/2) q This program generates a square wave on pin P 1. 5 Using timer 1 q Find the frequency. (dont include the overhead of instruction delay) q XTAL = 11. 0592 MHz MOV AGAIN: MOV SETB BACK: JNB CLR CPL CLR SJMP TMOD, #10 H TL 1, #34 H TH 1, #76 H TR 1 TF 1, BACK TR 1 P 1. 5 TF 1 AGAIN M_Nokhodchian @ yahoo. com ; timer 1, mode 1 ; timer value=3476 H ; start ; stop ; next half clock ; clear timer flag 1 ; reload timer 1 Microprocessors 1 -23

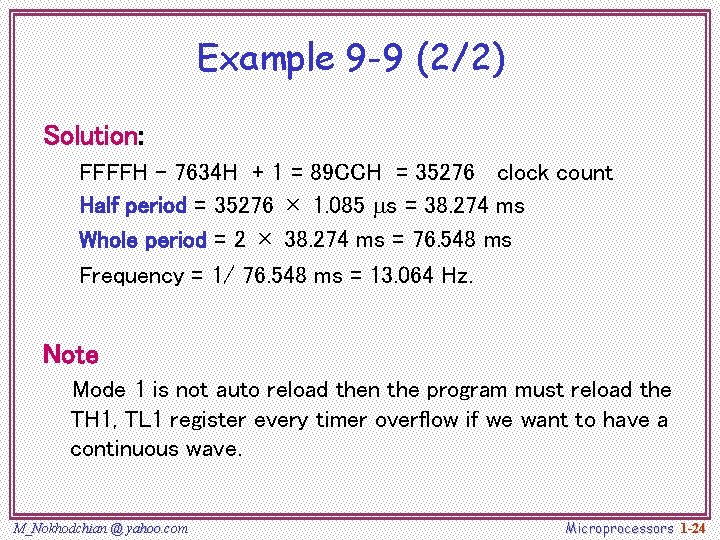

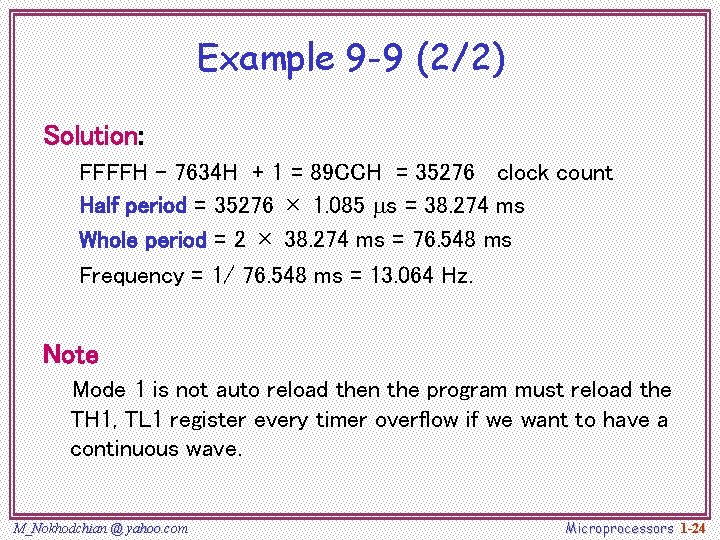

Example 9 -9 (2/2) Solution: FFFFH – 7634 H + 1 = 89 CCH = 35276 clock count Half period = 35276 × 1. 085 s = 38. 274 ms Whole period = 2 × 38. 274 ms = 76. 548 ms Frequency = 1/ 76. 548 ms = 13. 064 Hz. Note Mode 1 is not auto reload then the program must reload the TH 1, TL 1 register every timer overflow if we want to have a continuous wave. M_Nokhodchian @ yahoo. com Microprocessors 1 -24

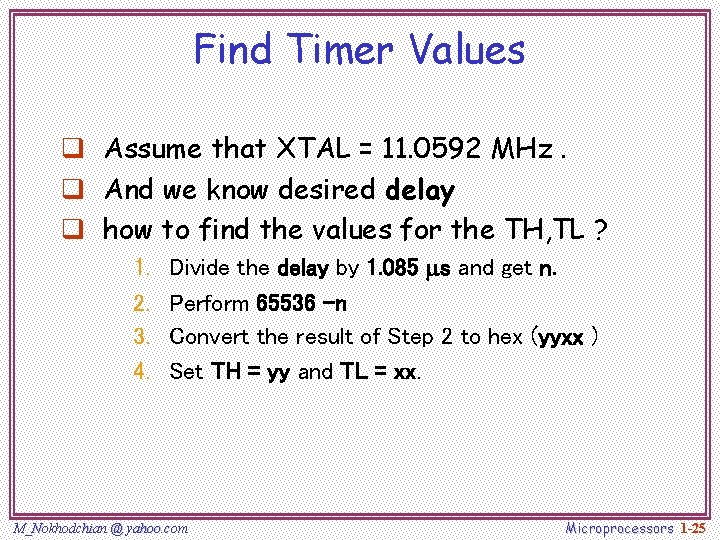

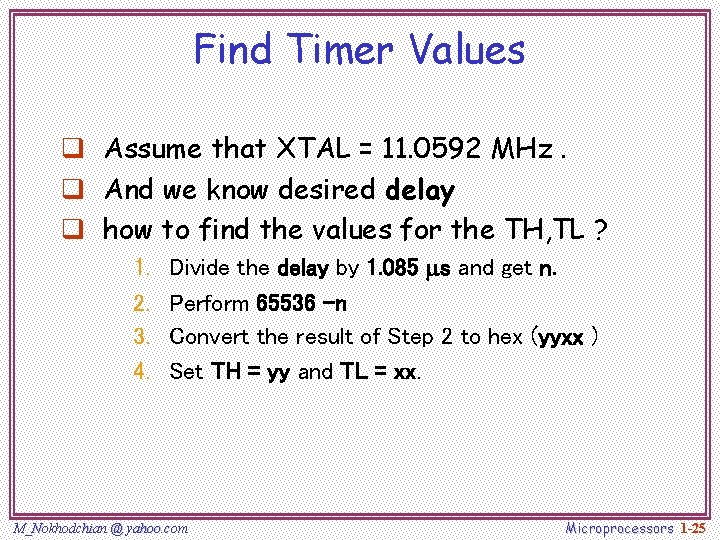

Find Timer Values q Assume that XTAL = 11. 0592 MHz. q And we know desired delay q how to find the values for the TH, TL ? 1. 2. 3. 4. Divide the delay by 1. 085 s and get n. Perform 65536 –n Convert the result of Step 2 to hex (yyxx ) Set TH = yy and TL = xx. M_Nokhodchian @ yahoo. com Microprocessors 1 -25

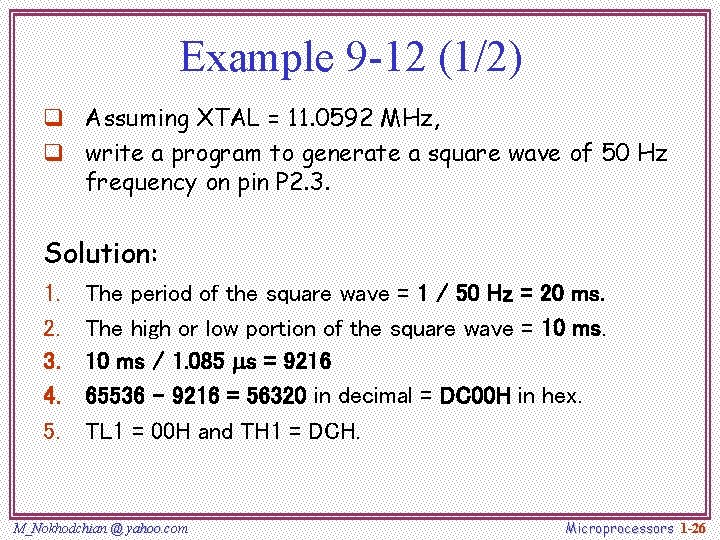

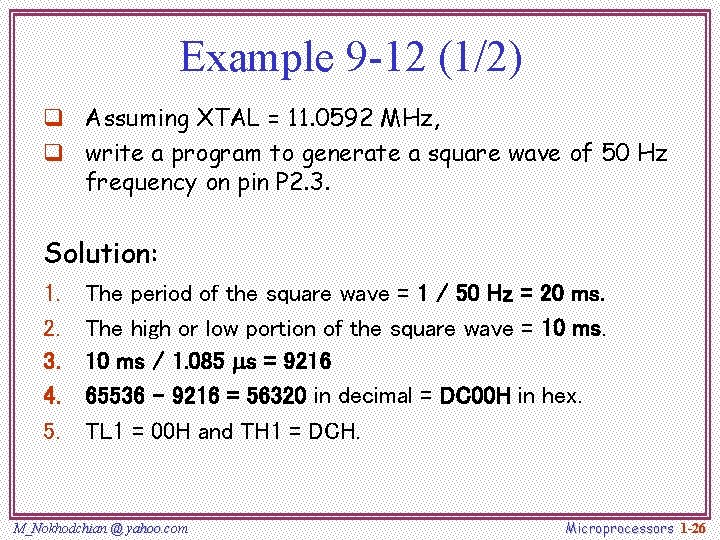

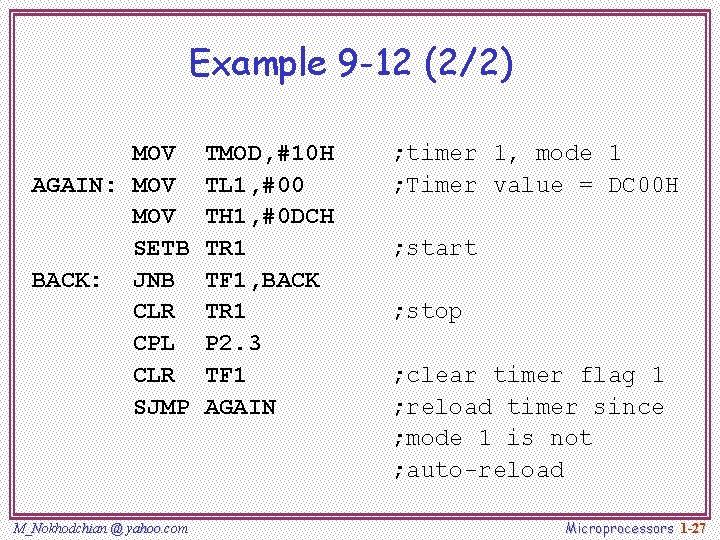

Example 9 -12 (1/2) q Assuming XTAL = 11. 0592 MHz, q write a program to generate a square wave of 50 Hz frequency on pin P 2. 3. Solution: 1. 2. 3. 4. 5. The period of the square wave = 1 / 50 Hz = 20 ms. The high or low portion of the square wave = 10 ms / 1. 085 s = 9216 65536 – 9216 = 56320 in decimal = DC 00 H in hex. TL 1 = 00 H and TH 1 = DCH. M_Nokhodchian @ yahoo. com Microprocessors 1 -26

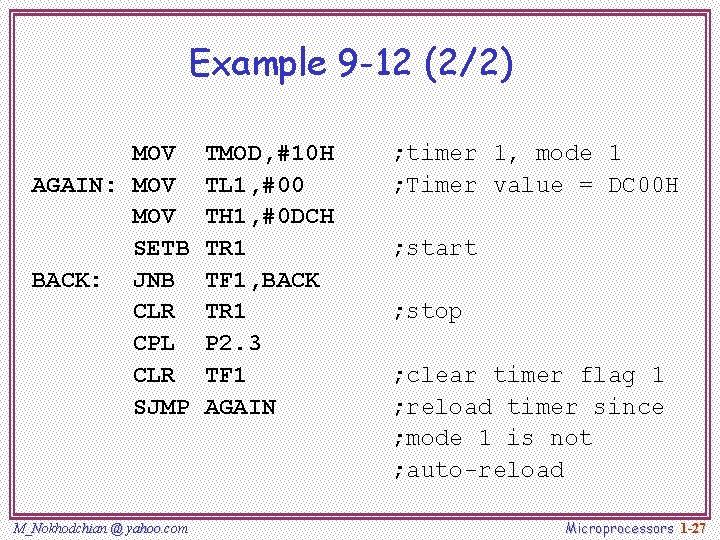

Example 9 -12 (2/2) MOV AGAIN: MOV SETB BACK: JNB CLR CPL CLR SJMP M_Nokhodchian @ yahoo. com TMOD, #10 H TL 1, #00 TH 1, #0 DCH TR 1 TF 1, BACK TR 1 P 2. 3 TF 1 AGAIN ; timer 1, mode 1 ; Timer value = DC 00 H ; start ; stop ; clear timer flag 1 ; reload timer since ; mode 1 is not ; auto-reload Microprocessors 1 -27

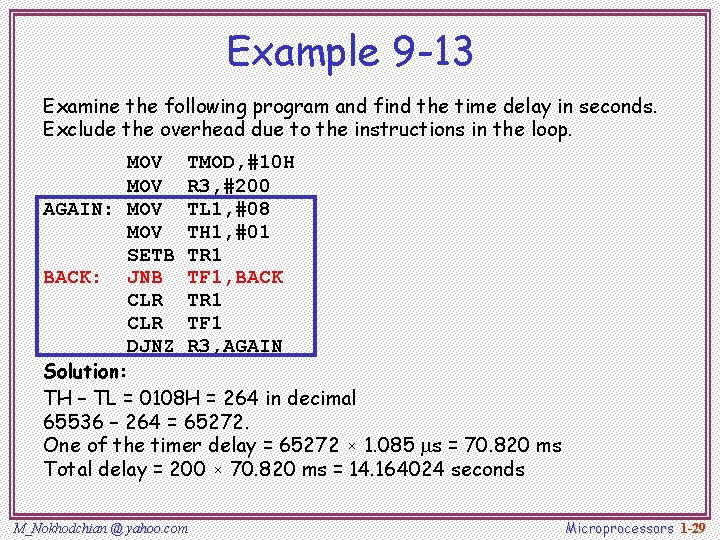

Generate a Large Time Delay q The size of the time delay depends on two factors: v They crystal frequency v The timer’s 16 -bit register, TH & TL q The largest time delay is achieved by making TH=TL=0. q What if that is not enough? q Next Example show to achieve large time delay M_Nokhodchian @ yahoo. com Microprocessors 1 -28

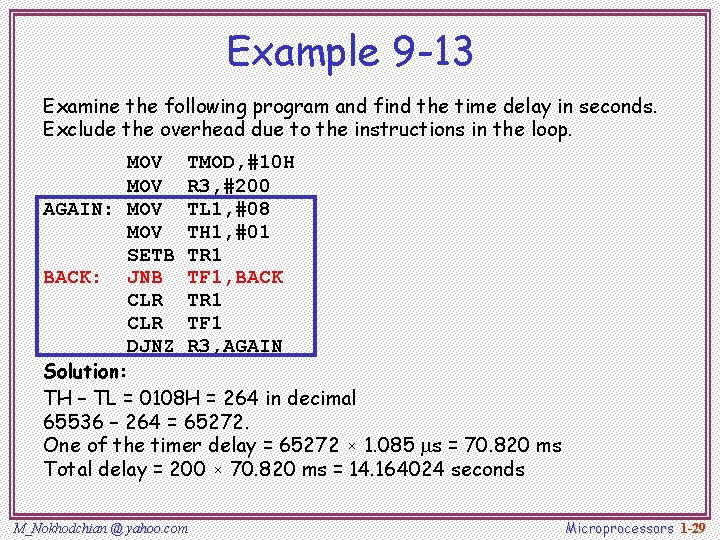

Example 9 -13 Examine the following program and find the time delay in seconds. Exclude the overhead due to the instructions in the loop. MOV TMOD, #10 H MOV R 3, #200 AGAIN: MOV TL 1, #08 MOV TH 1, #01 SETB TR 1 BACK: JNB TF 1, BACK CLR TR 1 CLR TF 1 DJNZ R 3, AGAIN Solution: TH – TL = 0108 H = 264 in decimal 65536 – 264 = 65272. One of the timer delay = 65272 × 1. 085 s = 70. 820 ms Total delay = 200 × 70. 820 ms = 14. 164024 seconds M_Nokhodchian @ yahoo. com Microprocessors 1 -29