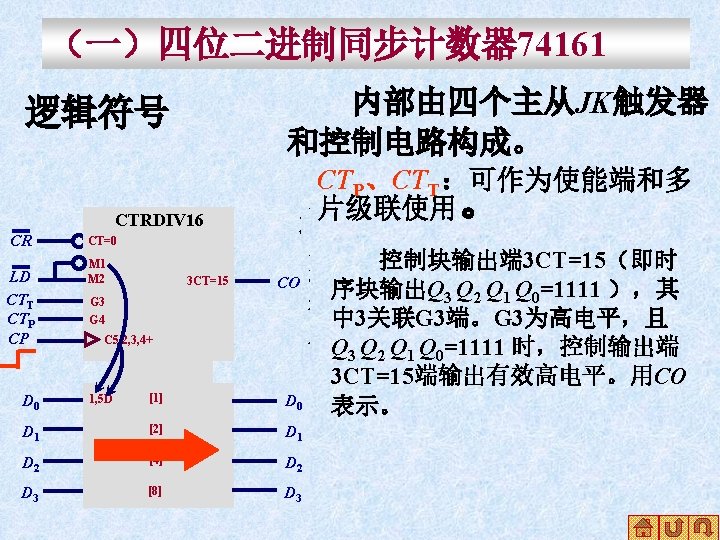

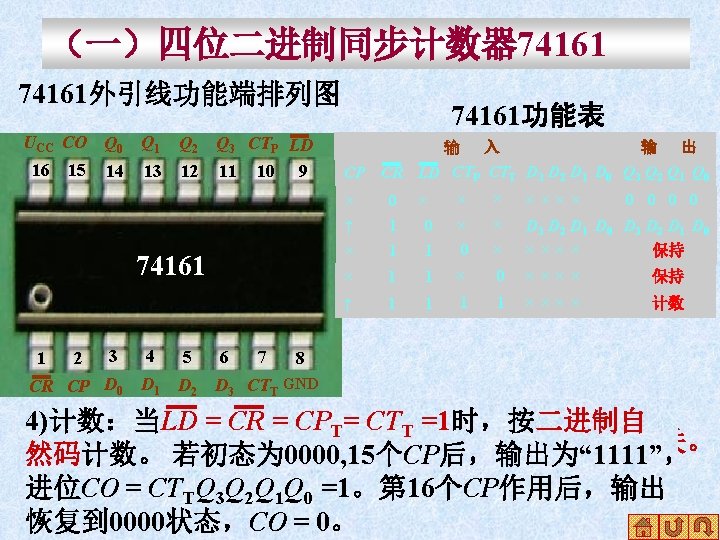

74161 VHDL 74161 LIBRARY BEGIN IEEE USEIFIEEE stdlogic1164

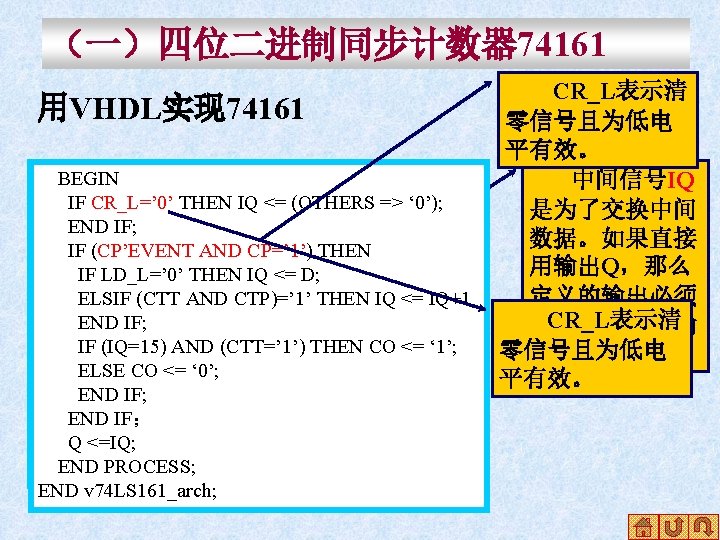

(一)四位二进制同步计数器 74161 用VHDL实现 74161 LIBRARY BEGIN IEEE USEIFIEEE. std_logic_1164. all; CR_L=’ 0’ THEN IQ <= (OTHERS => ‘ 0’); USEEND IEEE. std_logic_arith. all; IF; ENTITY IF (CP’EVENT v 74 LS 161 AND IS CP=’ 1’) THEN PORT IF LD_L=’ 0’ (CP, CR_L, LD_L, CTP, CTT: IN THEN IQ <= D; STD_LOGIC; ELSIF D: IN UNSIGNED (CTT AND CTP)=’ 1’ (3 DOWNTO THEN 0); IQ <= IQ+1 END Q: OUT IF; UNSIGNED (3 DOWNTO 0); IFCO: OUT (IQ=15)STD_LOGIC); AND (CTT=’ 1’) THEN CO <= ‘ 1’; ENDELSE v 74 LS 161; CO <= ‘ 0’; ARCHITECTURE END IF; v 74 LS 161_arch OF v 74 LS 161 IS SIGNAL END IF; IQ: UNSIGNED (3 DOWNTO 0); BEGIN Q <=IQ; PROCESS END PROCESS; (CP, CTT, CR_L) END v 74 LS 161_arch; CR_L表示清 零信号且为低电 平有效。 中间信号IQ 是为了交换中间 数据。如果直接 用输出Q,那么 定义的输出必须 CR_L表示清 为缓冲而不是输 零信号且为低电 出。 平有效。

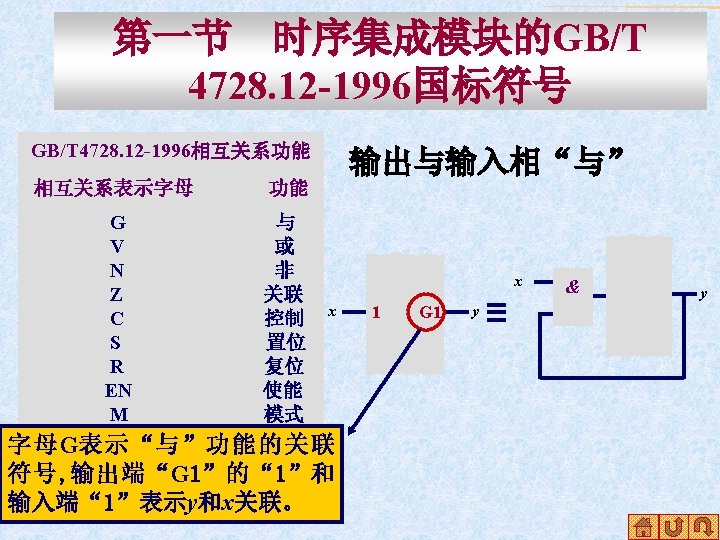

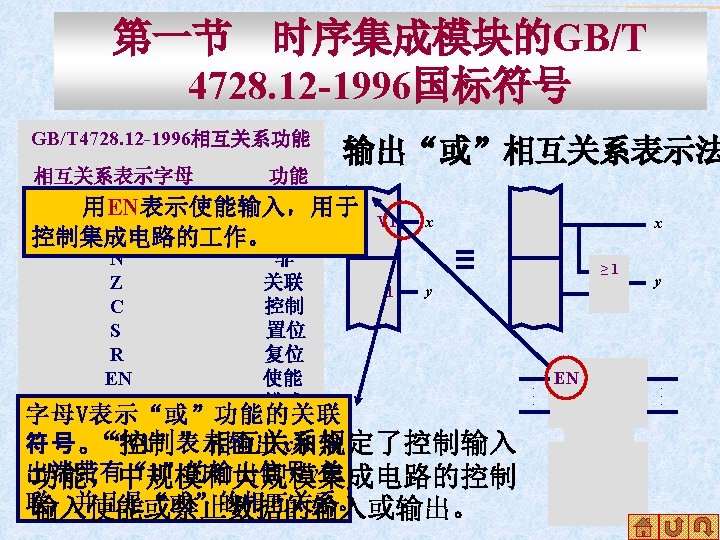

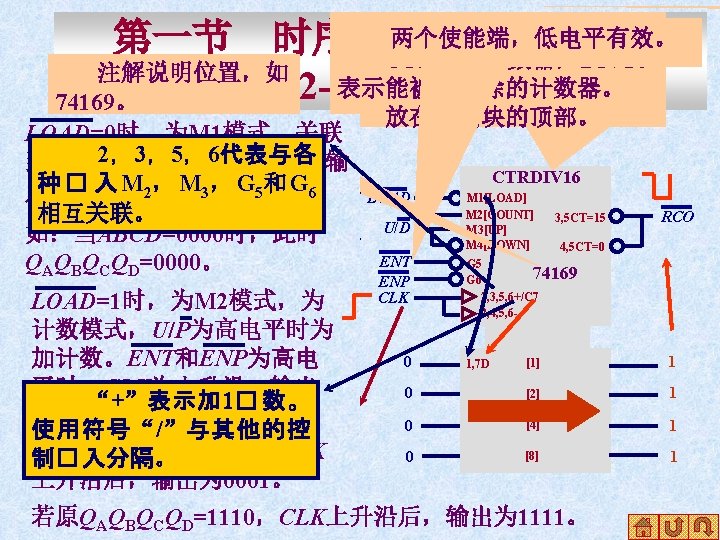

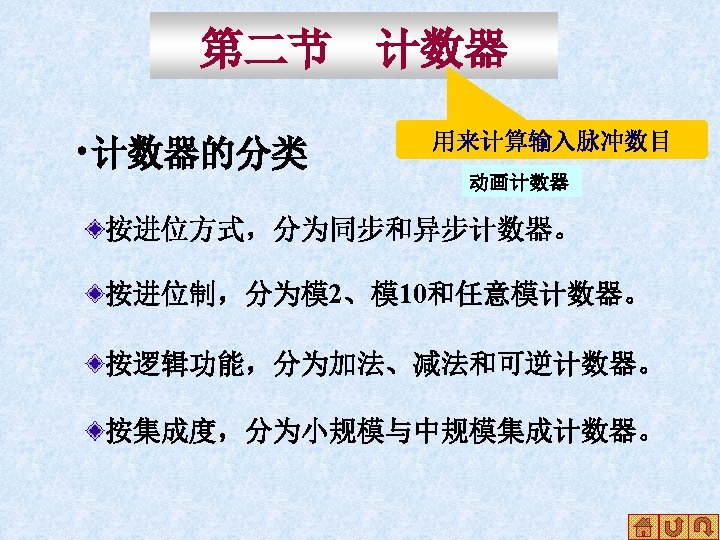

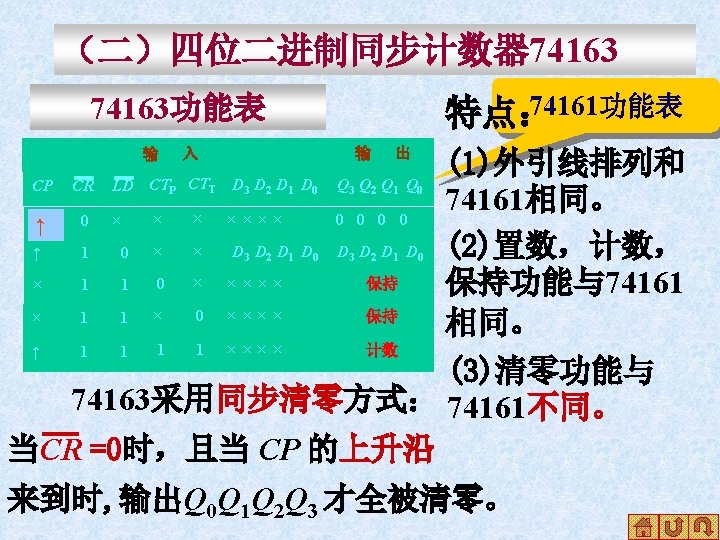

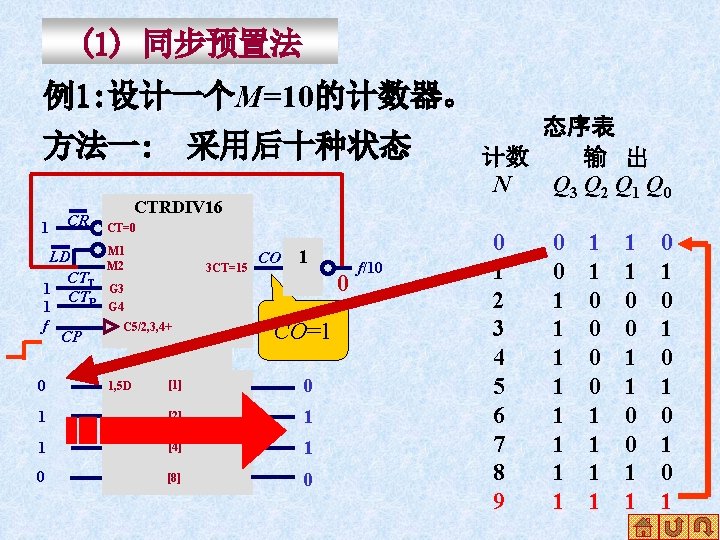

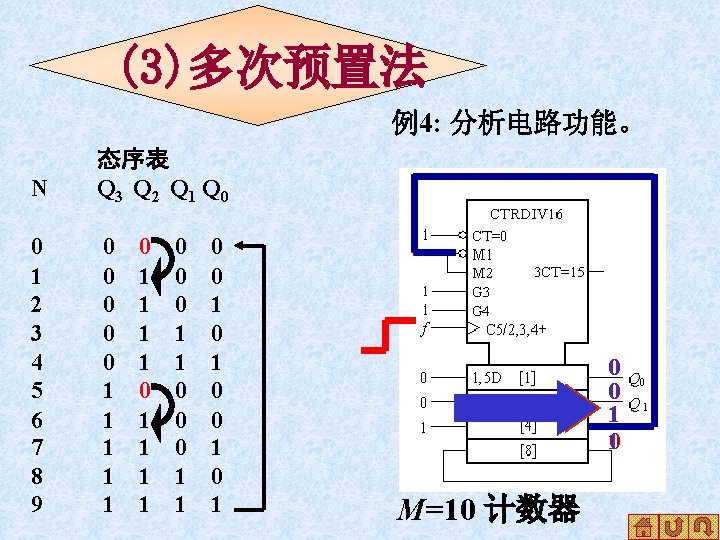

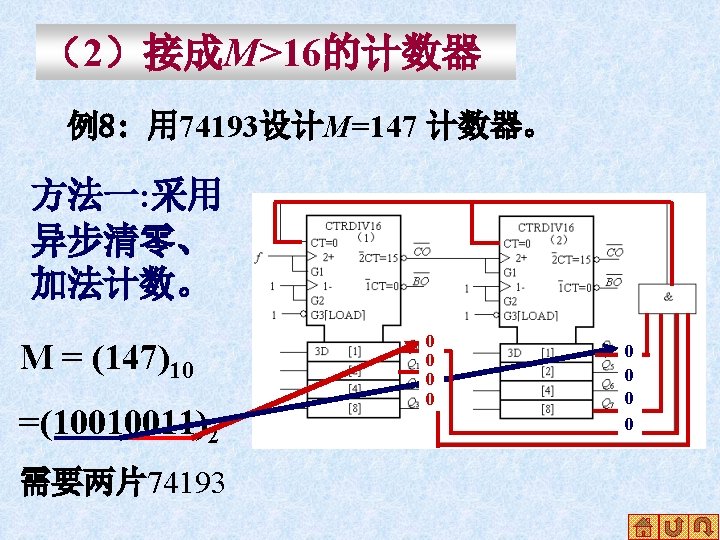

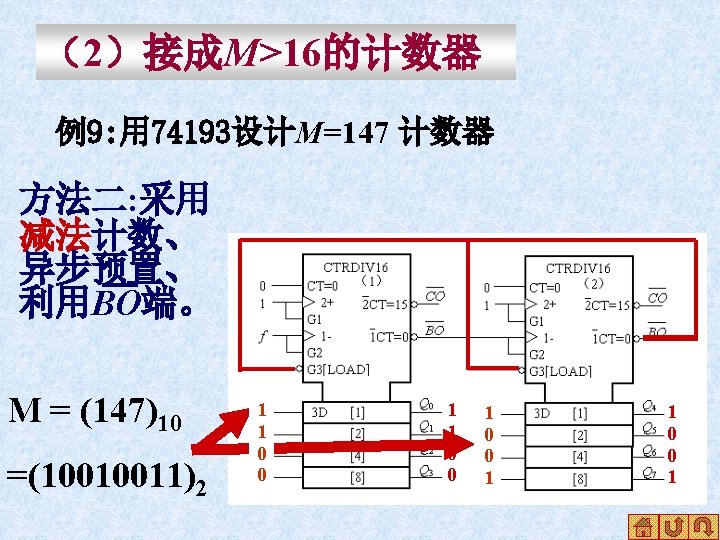

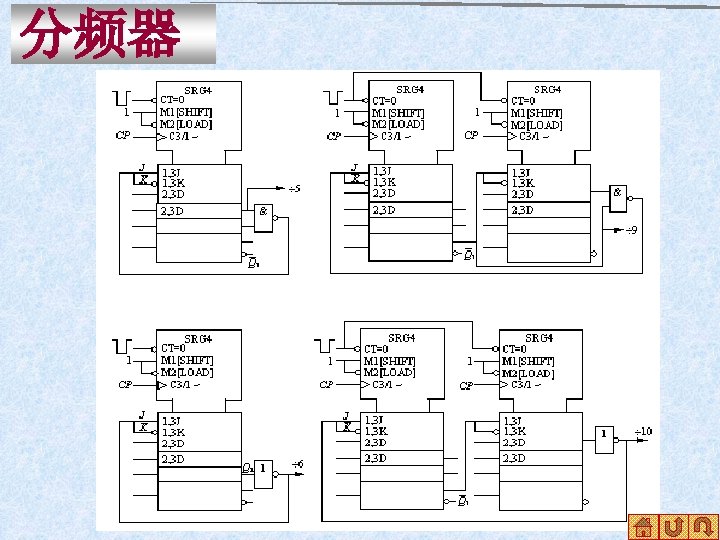

(1) 同步预置法 例1: 设计一个M=10的计数器。 方法一: 1 CR LD CT 1 CTT P 1 f CP 采用后十种状态 CTRDIV 16 CT=0 M 1 M 2 3 CT=15 CO 1 0 G 3 G 4 C 5/2, 3, 4+ CO=1 [1] 0 Q 0 11 [2] 1 Q 1 11 [4] 1 Q 2 00 [8] Q 03 00 1, 5 D f/10 态序表 计数 输 出 N Q 3 Q 2 Q 1 Q 0 0 1 2 3 4 5 6 7 8 9 0 1 1 0 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 0 1 1

例2: 同步预置法设计 M=24 计数器。 (24)10=(11000)2 需两片 初态为: 0000 0001 终态: 00011000 0 1 0 0 0 1 1 0 0 0 0 10 00 00 00

采用 74161 (2)反馈清零法 例3: 分析图示电路的功能。 0 1 0 0 1 N 态序表 Q 3 Q 2 Q 1 Q 0 0 1 2 3 4 5 6 7 8 9 10 11 12 0 0 0 0 1 1 1 0 0 1 0 0 1 0 1 0 1 0 1 0

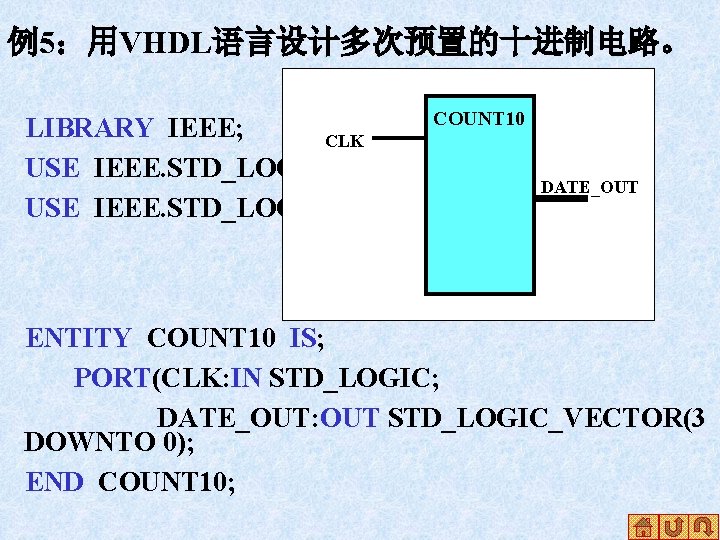

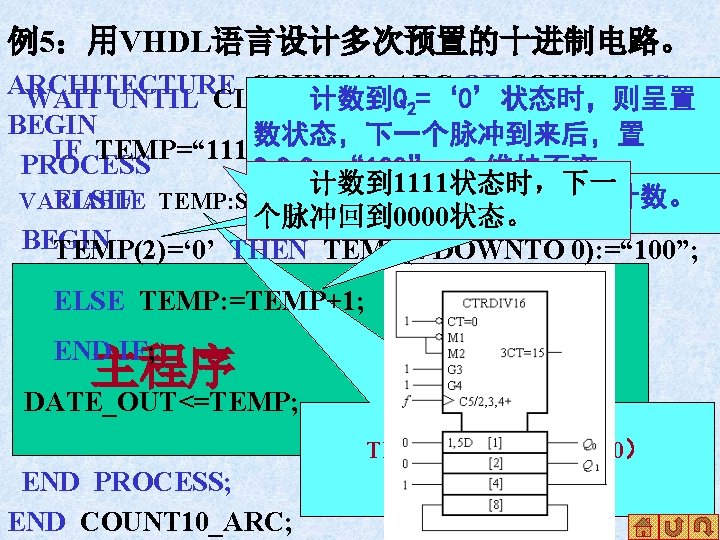

例5:用VHDL语言设计多次预置的十进制电路。 COUNT 10 LIBRARY IEEE; CLK USE IEEE. STD_LOGIC_1164. ALL; DATE_OUT USE IEEE. STD_LOGIC_UNSIGNED. ALL; ENTITY COUNT 10 IS; PORT(CLK: IN STD_LOGIC; DATE_OUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); END COUNT 10;

例5:用VHDL语言设计多次预置的十进制电路。 ARCHITECTURE COUNT 10_ARC OF COUNT 10 IS; 计数到Q WAIT UNTIL CLK’EVENT AND CLK=‘ 1’ ; 2=‘ 0’状态时,则呈置 BEGIN 数状态,下一个脉冲到来后,置 IF TEMP=“ 1111” THEN TEMP=“ 0000” PROCESS Q 2 Q 1 Q 0=“ 100”,Q 3维持不变。 计数到 1111状态时,下一 其它情况按照 8421码计数。 ELSIF TEMP: STD_LOGIC_VECTOR(3 VARIABLE DOWNTO 0); 个脉冲回到 0000状态。 BEGIN TEMP(2)=‘ 0’ THEN TEMP(2 DOWNTO 0): =“ 100”; ELSE TEMP: =TEMP+1; END IF; 主程序 DATE_OUT<=TEMP; END PROCESS; END COUNT 10_ARC; 中间变量 TEMP(3)到TEMP(0) 对应输出Q 3 Q 2 Q 1 Q 0

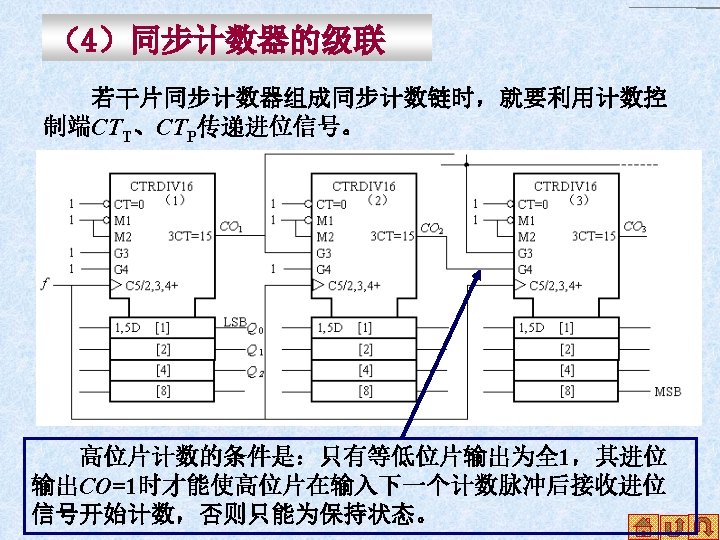

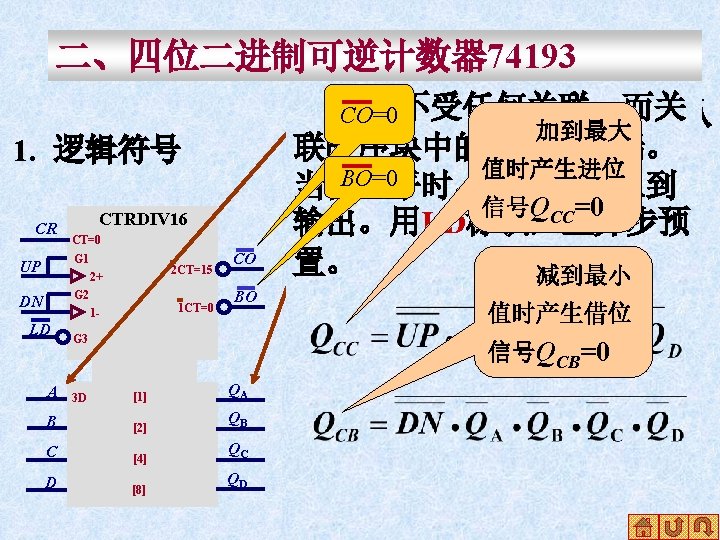

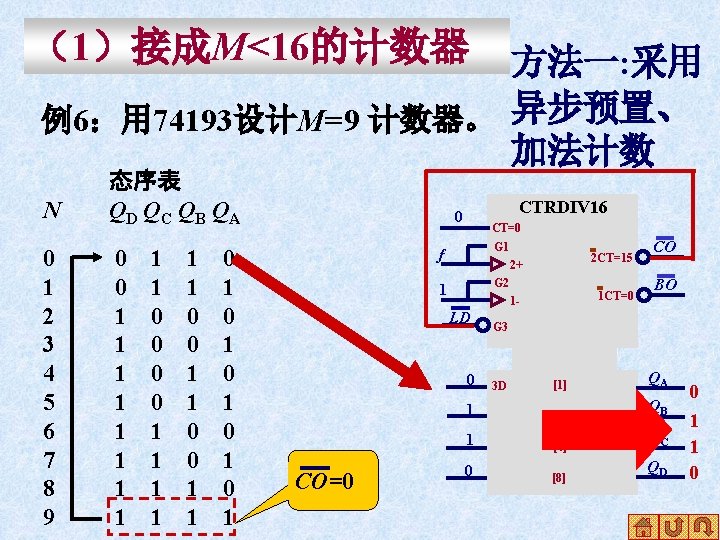

(1)接成M<16的计数器 方法一: 采用 例6:用 74193设计M=9 计数器。 异步预置、 加法计数 N 态序表 QD QC QB QA 0 1 2 3 4 5 6 7 8 9 0 0 1 1 1 1 1 0 0 1 1 0 1 0 1 0 1 CTRDIV 16 0 CT=0 f G 1 1 G 2 2+ 1 CT=0 1 - LD 0 CO=0 2 CT=15 CO BO G 3 3 D [1] 1 [2] 1 [4] 0 [8] QA QB QC QD 0 1 1 0

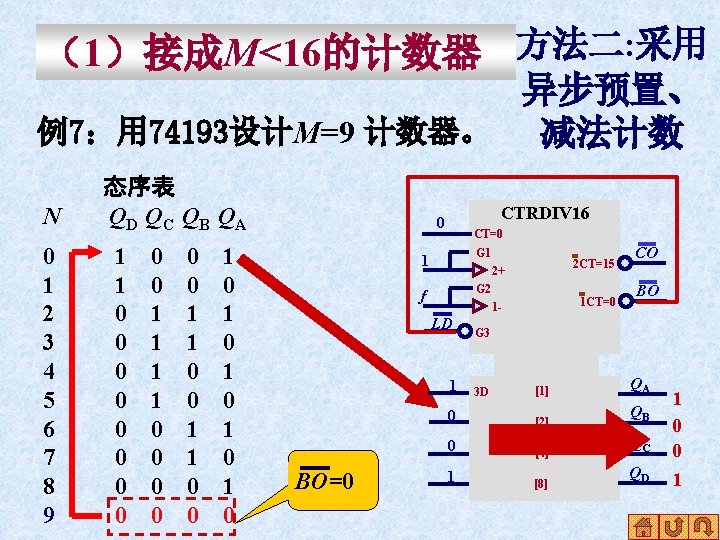

(1)接成M<16的计数器 方法二: 采用 异步预置、 例7:用 74193设计M=9 计数器。 减法计数 N 0 1 2 3 4 5 6 7 8 9 态序表 QD QC QB QA 1 1 0 0 0 0 0 1 1 0 0 1 0 1 0 1 0 CTRDIV 16 0 CT=0 1 G 1 f G 2 2+ 1 CT=0 1 - LD 1 BO=0 2 CT=15 CO BO G 3 3 D [1] 0 [2] 0 [4] 1 [8] QA QB QC QD 1 0 0 1

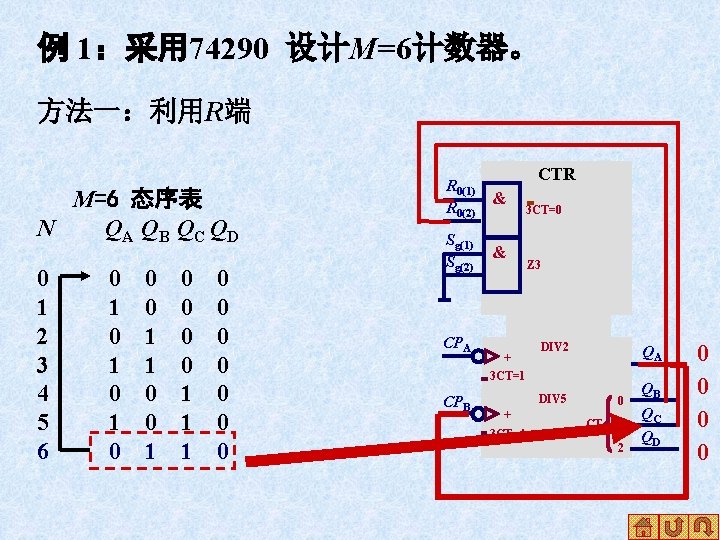

例 1:采用 74290 设计M=6计数器。 方法一:利用R端 M=6 态序表 N QA QB QC QD 0 1 2 3 4 5 6 0 1 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 CTR R 0(1) R 0(2) & Sg(1) Sg(2) & CPA + 3 CT=0 Z 3 DIV 2 QA 3 CT=1 CPB DIV 5 + 3 CT=4 0 CT 2 QB QC QD 00 01 01 00

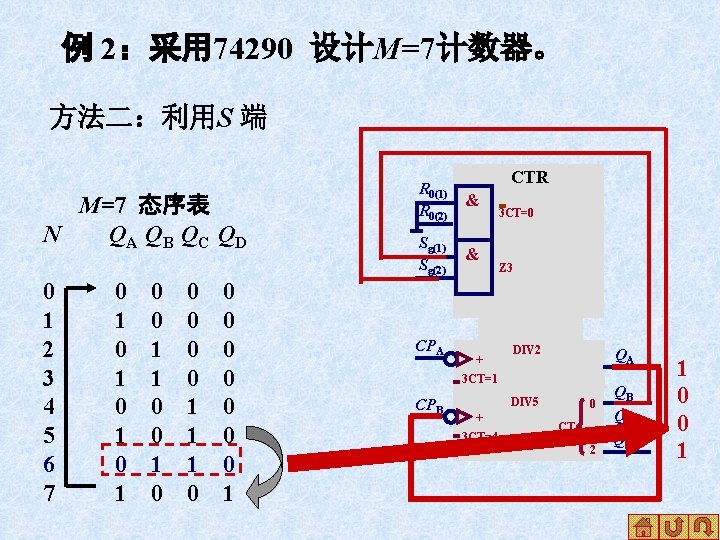

例 2:采用 74290 设计M=7计数器。 方法二:利用S 端 M=7 态序表 N Q A QB QC QD 0 1 2 3 4 5 6 7 0 1 0 1 0 0 1 1 0 0 0 0 0 1 1 1 0 0 0 0 1 CTR R 0(1) R 0(2) & Sg(1) Sg(2) & CPA + 3 CT=0 Z 3 DIV 2 QA 3 CT=1 CPB DIV 5 + 3 CT=4 0 CT 2 QB QC QD 10 01 01 10

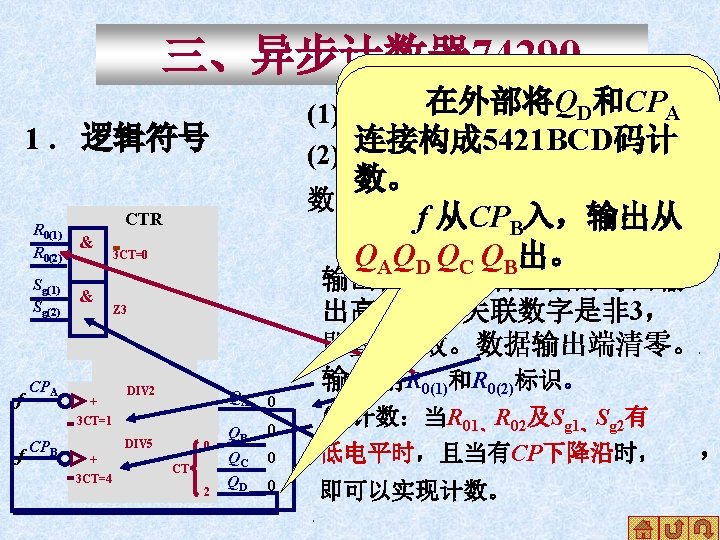

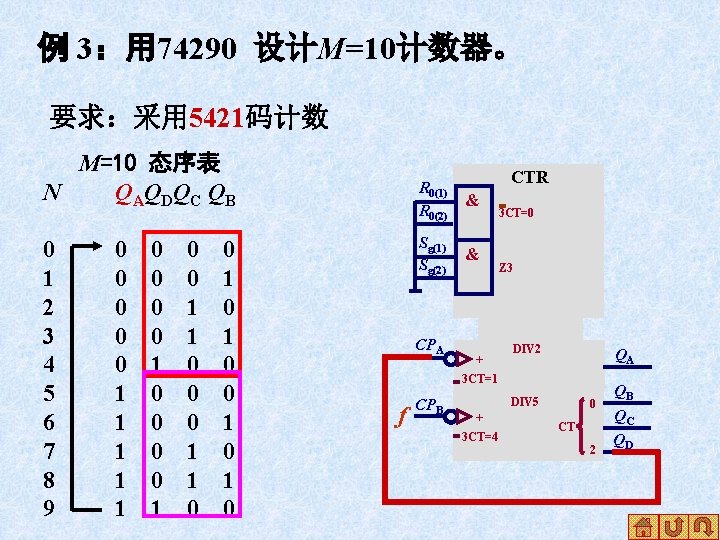

例 3:用 74290 设计M=10计数器。 要求:采用 5421码计数 M=10 态序表 N Q AQ DQ C Q B 0 1 2 3 4 5 6 7 8 9 0 0 0 1 1 1 0 0 0 0 1 1 0 0 1 0 1 0 CTR R 0(1) R 0(2) & Sg(1) Sg(2) & CPA + 3 CT=0 Z 3 DIV 2 QA 3 CT=1 f CPB DIV 5 + 3 CT=4 0 CT 2 QB QC QD

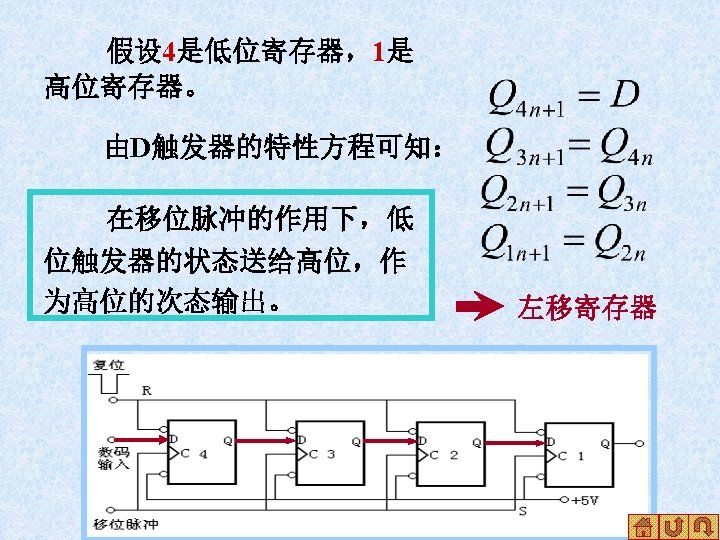

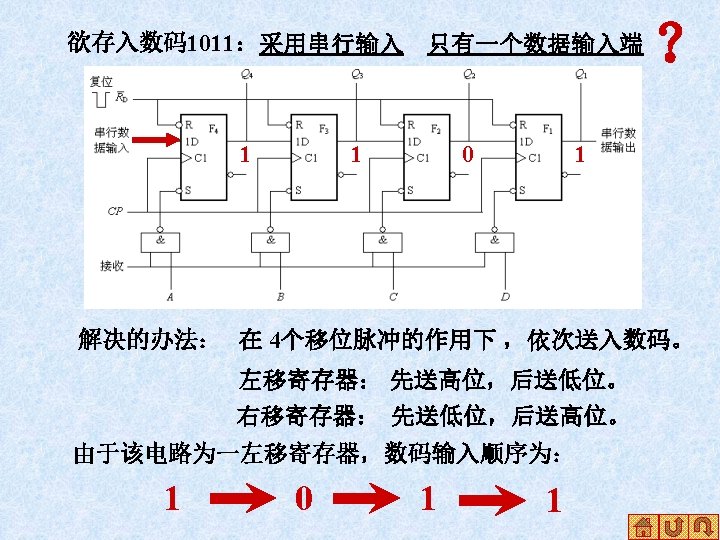

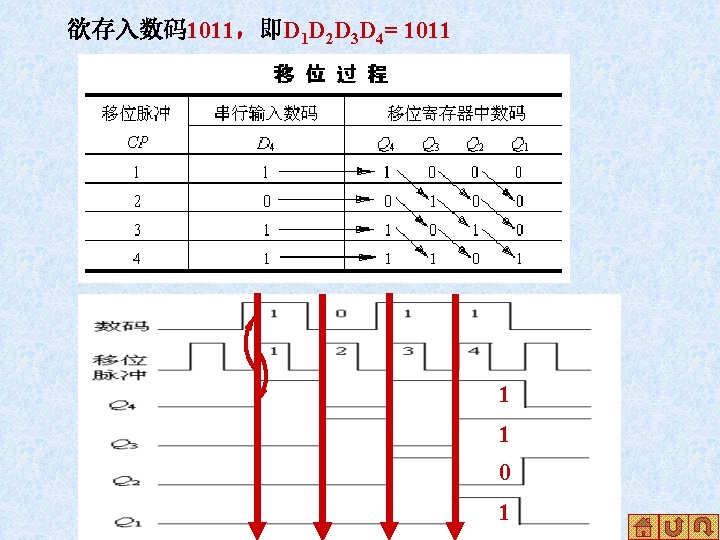

欲存入数码1011,即D 1 D 2 D 3 D 4= 1011 1 1 0 1

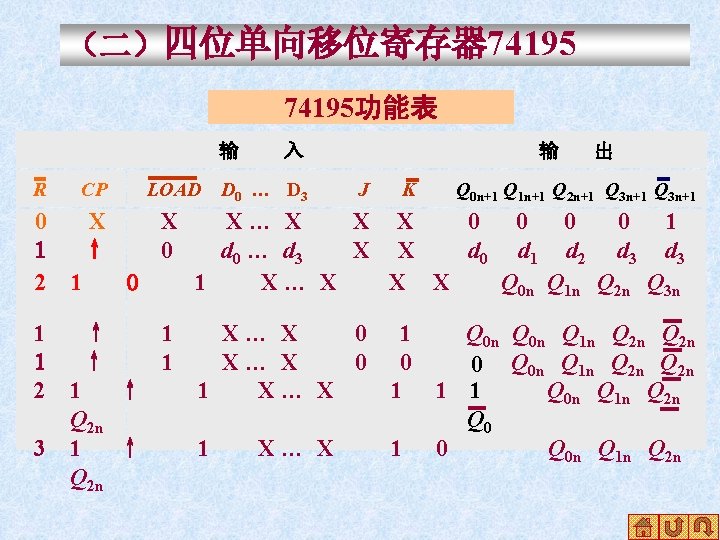

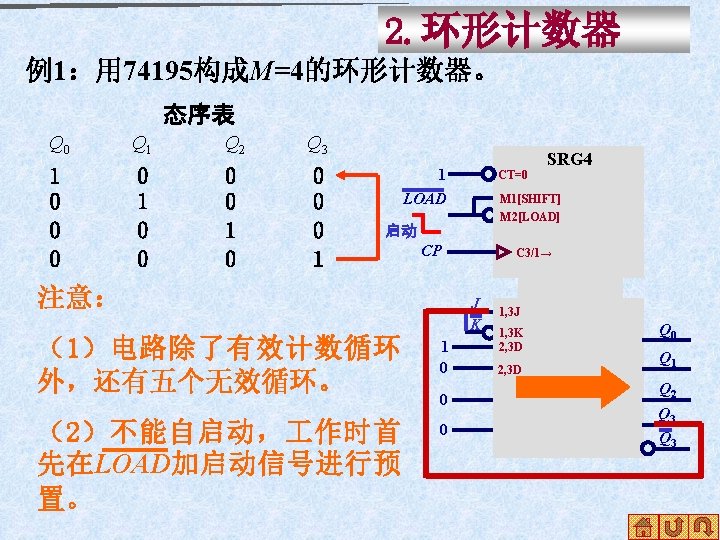

(二)四位单向移位寄存器 74195功能表 输 R CP 入 LOAD D 0 … D 3 0 X X X… X 1 ↑ 0 d 0 … d 3 2 1 0 1 X… X Q 3 n 1 ↑ 1 X… X 2 1 ↑ 1 X… X Q 2 n 3 1 ↑ 1 X… X Q 2 n 输 J K 出 Q 0 n+1 Q 1 n+1 Q 2 n+1 Q 3 n+1 X X X 0 0 1 X d 0 d 1 d 2 d 3 X X Q 0 n Q 1 n Q 2 n Q 3 n 0 0 1 1 Q 0 n Q 1 n Q 2 n 0 Q 0 n Q 1 n Q 2 n 1 1 Q 0 n Q 1 n Q 2 n Q 0 0 Q 0 n Q 1 n Q 2 n

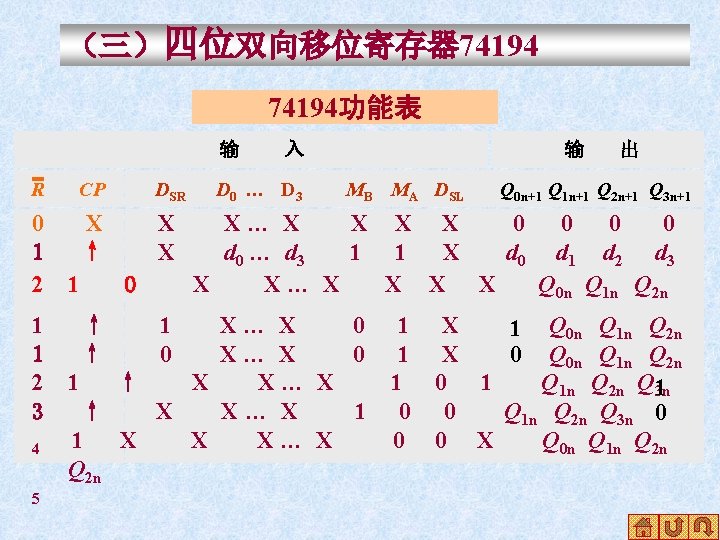

(三)四位双向移位寄存器 74194功能表 输 R CP DSR 入 D 0 … D 3 0 X X X… X 1 ↑ X d 0 … d 3 2 1 0 X X… X 3 n 1 Q↑ 1 X… X 1 ↑ 0 X… X 2 1 ↑ X X… X 3 ↑ X X… X 1 X X X… X 4 Q 2 n 5 输 MB MA DSL 出 Q 0 n+1 Q 1 n+1 Q 2 n+1 Q 3 n+1 X X 0 0 1 X d 0 d 1 d 2 d 3 X X X Q 0 n Q 1 n Q 2 n 0 0 1 1 1 0 0 1 X 1 Q 0 n Q 1 n Q 2 n X 0 Q 0 n Q 1 n Q 2 n 0 1 Q 1 n Q 2 n Q 3 n 1 0 Q 1 n Q 2 n Q 3 n 0 0 X Q 0 n Q 1 n Q 2 n

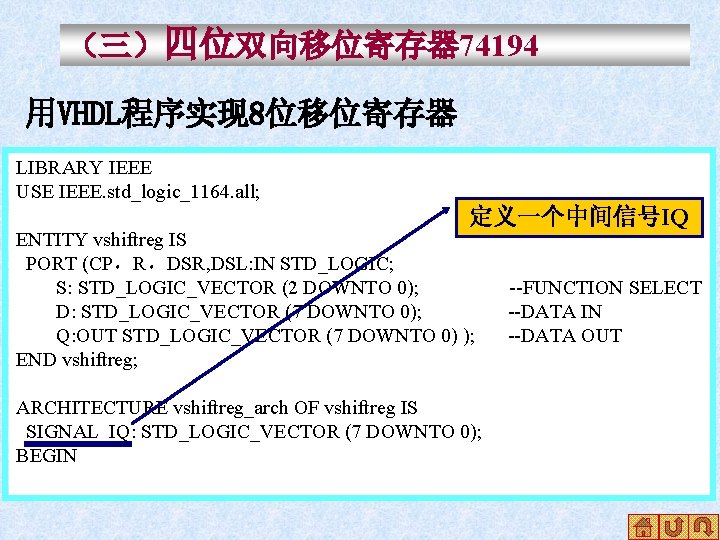

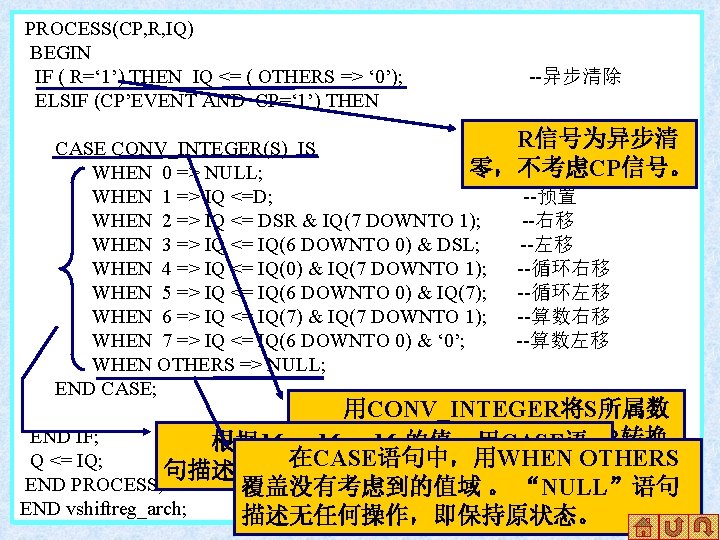

(三)四位双向移位寄存器 74194 用VHDL程序实现 8位移位寄存器 LIBRARY IEEE USE IEEE. std_logic_1164. all; 定义一个中间信号IQ ENTITY vshiftreg IS PORT (CP,R,DSR, DSL: IN STD_LOGIC; S: STD_LOGIC_VECTOR (2 DOWNTO 0); D: STD_LOGIC_VECTOR (7 DOWNTO 0); Q: OUT STD_LOGIC_VECTOR (7 DOWNTO 0) ); END vshiftreg; ARCHITECTURE vshiftreg_arch OF vshiftreg IS SIGNAL IQ: STD_LOGIC_VECTOR (7 DOWNTO 0); BEGIN --FUNCTION SELECT --DATA IN --DATA OUT

PROCESS(CP, R, IQ) BEGIN IF ( R=‘ 1’) THEN IQ <= ( OTHERS => ‘ 0’); ELSIF (CP’EVENT AND CP=‘ 1’) THEN --异步清除 R信号为异步清 CASE CONV_INTEGER(S) IS 零,不考虑CP信号。 WHEN 0 => NULL; --保持 WHEN 1 => IQ <=D; --预置 WHEN 2 => IQ <= DSR & IQ(7 DOWNTO 1); --右移 WHEN 3 => IQ <= IQ(6 DOWNTO 0) & DSL; --左移 WHEN 4 => IQ <= IQ(0) & IQ(7 DOWNTO 1); --循环右移 WHEN 5 => IQ <= IQ(6 DOWNTO 0) & IQ(7); --循环左移 WHEN 6 => IQ <= IQ(7) & IQ(7 DOWNTO 1); --算数右移 WHEN 7 => IQ <= IQ(6 DOWNTO 0) & ‘ 0’; --算数左移 WHEN OTHERS => NULL; END CASE; 用CONV_INTEGER将S所属数 END IF; 据类型STD_LOGIC_VECTOR转换 根据MA、M B、MC的值,用CASE语 在CASE语句中,用WHEN OTHERS Q <= IQ; 到整数类型。 句描述了8种移位操作。 END PROCESS; 覆盖没有考虑到的值域 。 “NULL”语句 END vshiftreg_arch; 描述无任何操作,即保持原状态。

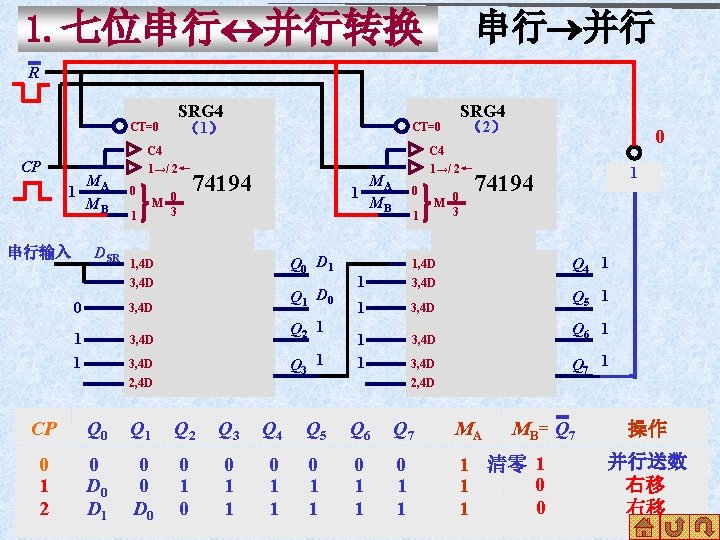

1. 七位串行 并行转换 串行 并行 R SRG 4 (1) CT=0 CP MA 1 MB DSR 串行输入 C 4 1→/ 2← 0 1 M 0 3 SRG 4 (2) CT=0 74194 C 4 1→/ 2← MA 1 MB Q 0 D 010 1, 4 D 3, 4 D 0 3, 4 D Q 1 1 D 00 1 1 3, 4 D Q 2 1 0 3, 4 D Q 3 1 0 0 1 M 0 3 01 1 74194 Q 4 1 0 1, 4 D 1 3, 4 D Q 5 1 0 1 1 3, 4 D Q 6 1 0 3, 4 D Q 7 1 0 2, 4 D CP Q 0 Q 1 Q 2 Q 3 Q 4 Q 5 Q 6 Q 7 MA MB= Q 7 0 1 2 0 D 1 0 0 D 0 0 1 1 0 1 1 1 清零 1 0 1 操作 并行送数 右移 右移

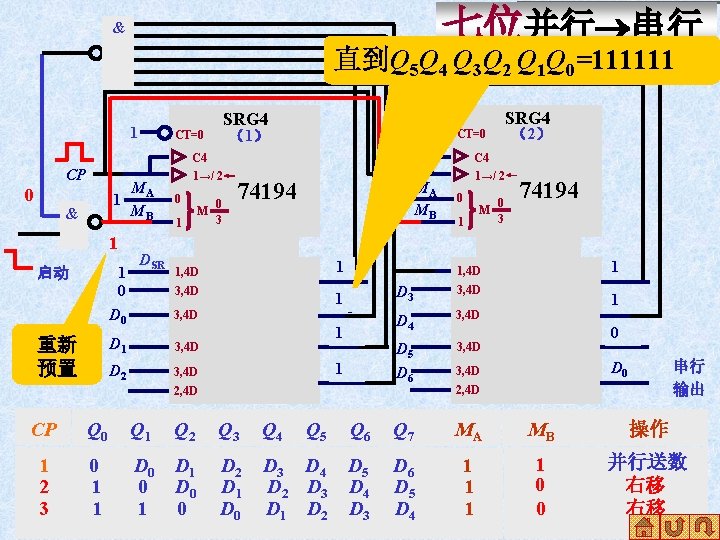

七位并行 串行 & 直到Q 5 Q 4 Q 3 Q 2 Q 1 Q 0=111111 1 CP 0 1 & 1 1 0 D 0 启动 重新 预置 SRG 4 MA MB DSR C 4 1→/ 2← 0 1 1 (1) CT=0 0 M 3 74194 1 10 0 Q 1, 4 D 3, 4 D 1 Q 0 D 0 1 3, 4 D D 2 3, 4 D MA MB 1 Q D 201 1 Q D 312 2, 4 D Q 5 CT=0 SRG 4 (2) C 4 1→/ 2← 0 1 0 M 3 74194 1 DQ 234 1, 4 D D 3 3, 4 D D 4 3, 4 D 1 DQ 345 D 6 3, 4 D 0 DQ 456 3, 4 D DQ 0567 2, 4 D 串行 输出 CP Q 0 Q 1 Q 2 Q 3 Q 4 Q 6 Q 7 MA MB 操作 1 2 3 0 1 1 D 0 0 D 2 D 1 D 0 D 3 D 4 D 5 D 2 D 3 D 4 D 1 D 2 D 3 D 6 D 5 D 4 1 1 0 0 并行送数 右移 右移

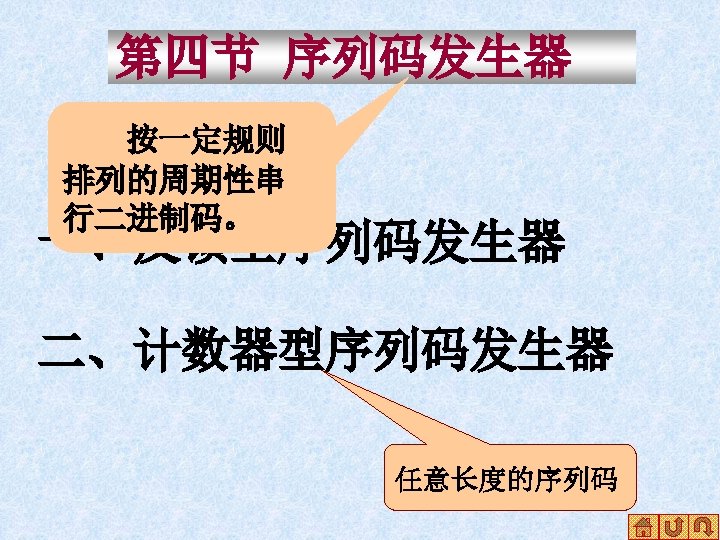

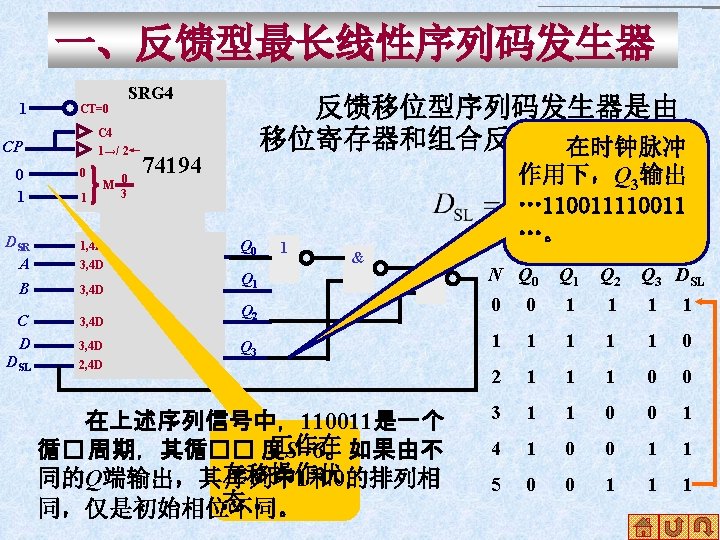

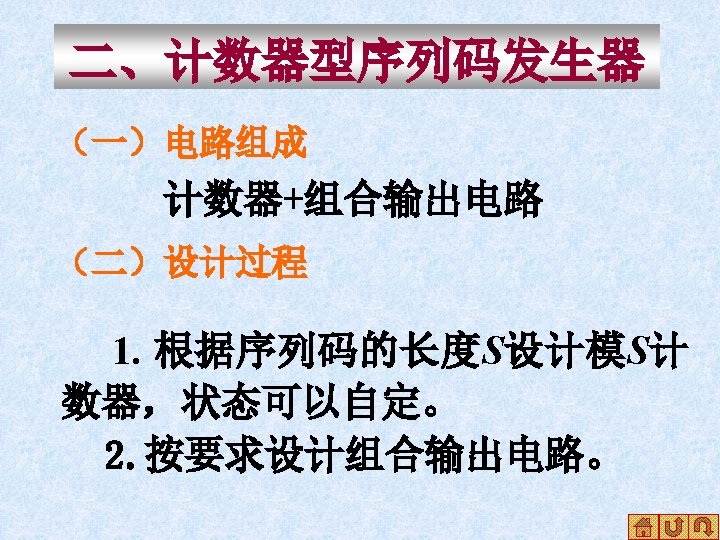

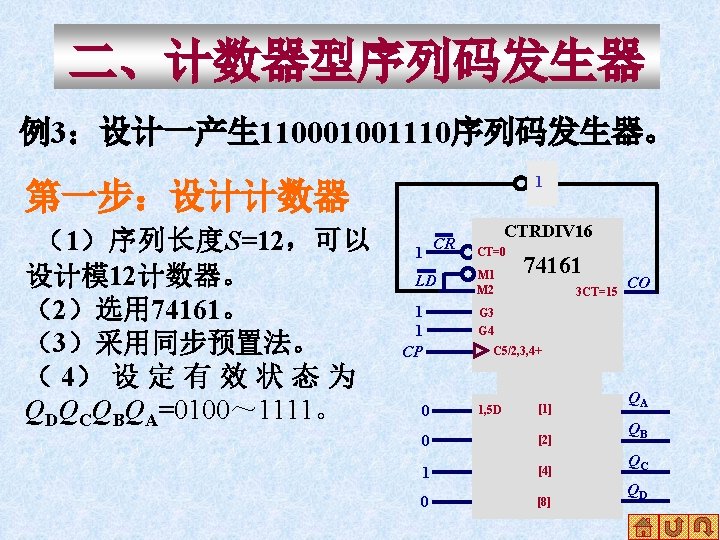

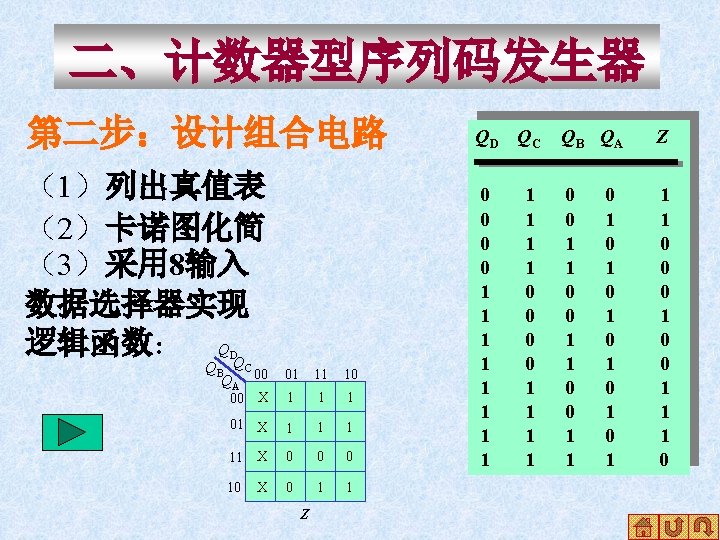

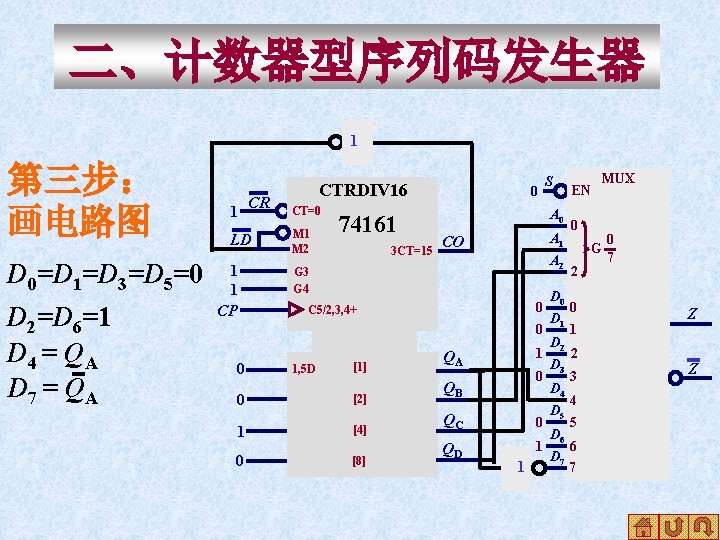

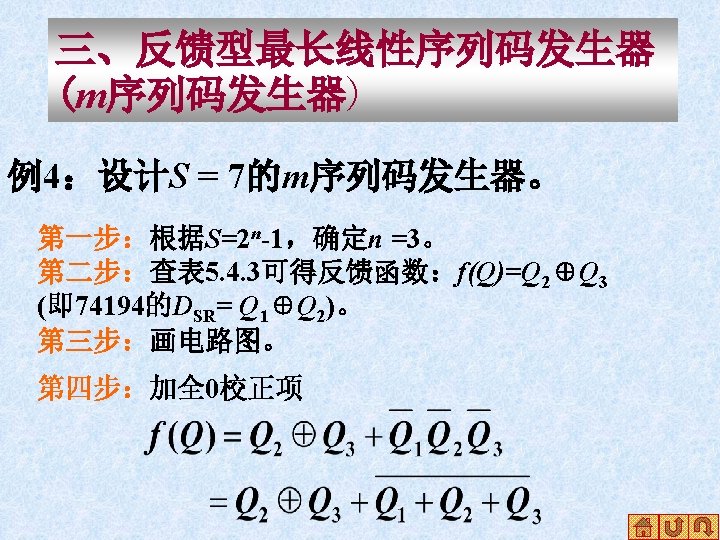

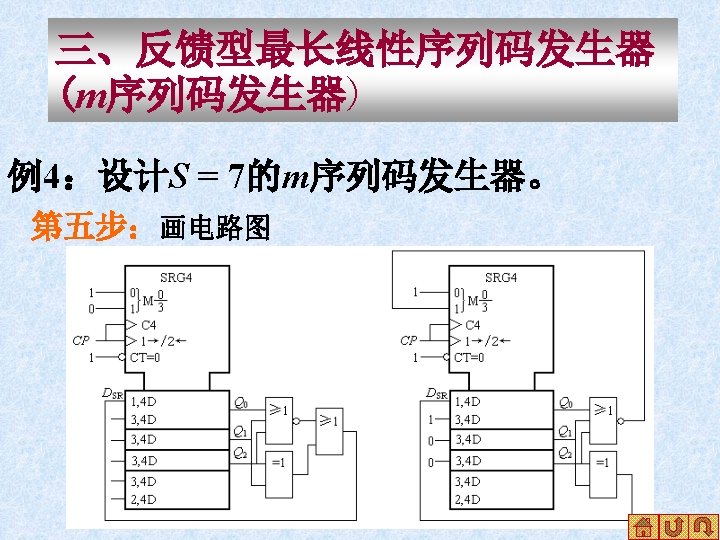

二、计数器型序列码发生器 1 第三步: 画电路图 D 0=D 1=D 3=D 5=0 D 2=D 6=1 D 4 = QA D 7 = QA 1 CR LD 1 1 CP CTRDIV 16 CT=0 M 1 M 2 74161 3 CT=15 0 A 1 CO A 2 G 3 G 4 0 C 5/2, 3, 4+ 0 0 1, 5 D [1] 0 [2] 1 [4] 0 [8] S 1 QA 0 QB QC 0 QD 1 1 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 EN 0 G 2 0 1 2 3 4 5 6 7 MUX 0 7 Z Z

- Slides: 75