7 Segment Displays Digilent Spartan 3 Board Discussion

7 -Segment Displays Digilent Spartan 3 Board Discussion D 3. 4

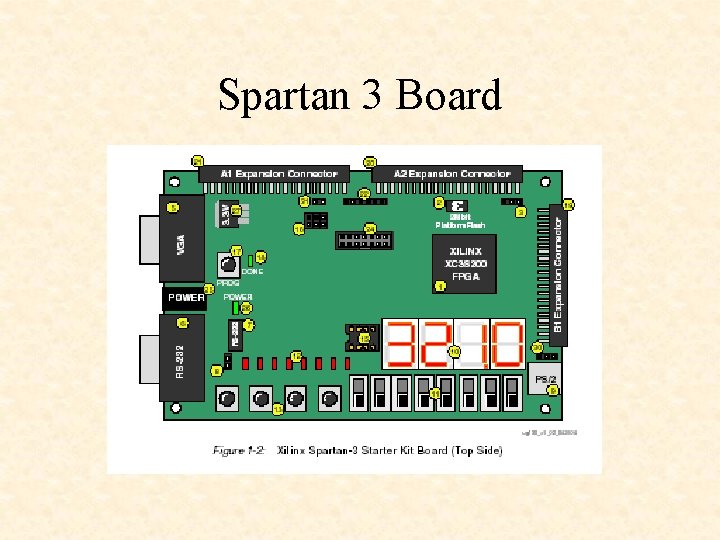

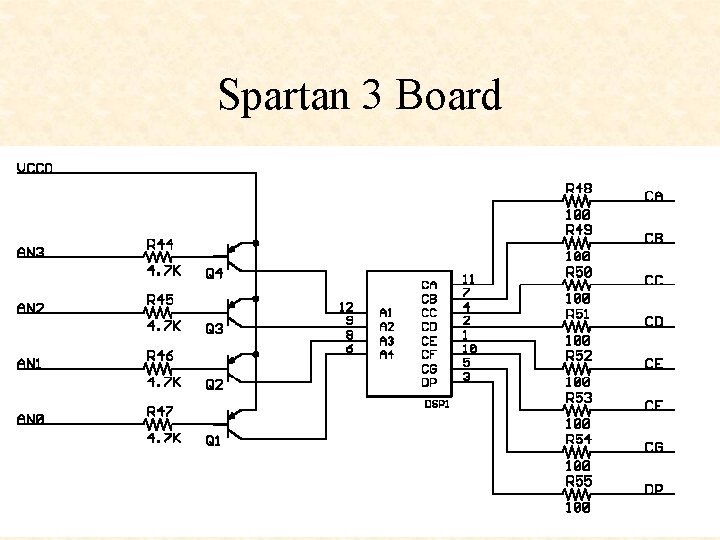

Spartan 3 Board

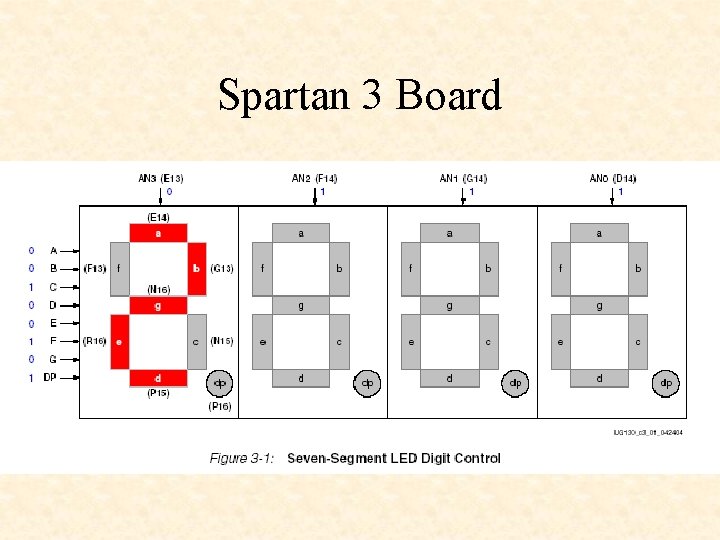

Spartan 3 Board

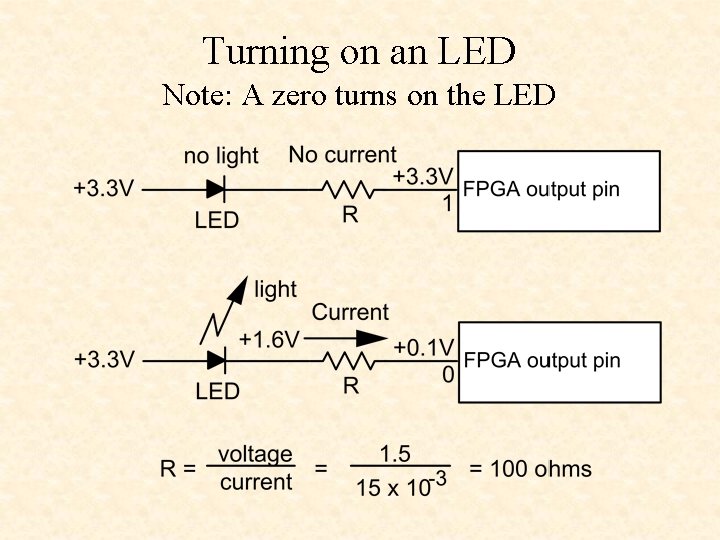

Turning on an LED Note: A zero turns on the LED

Spartan 3 Board

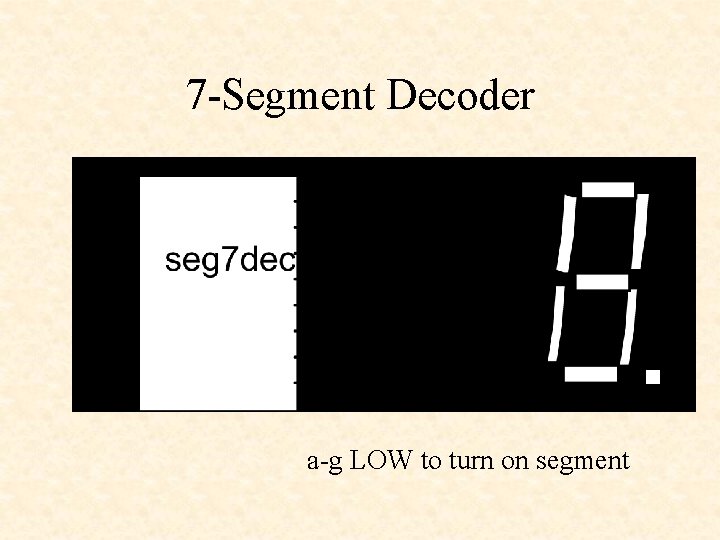

7 -Segment Decoder a-g LOW to turn on segment

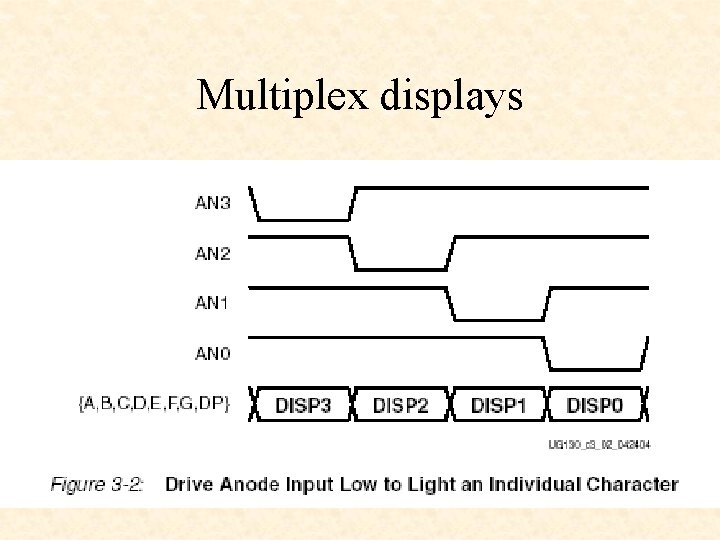

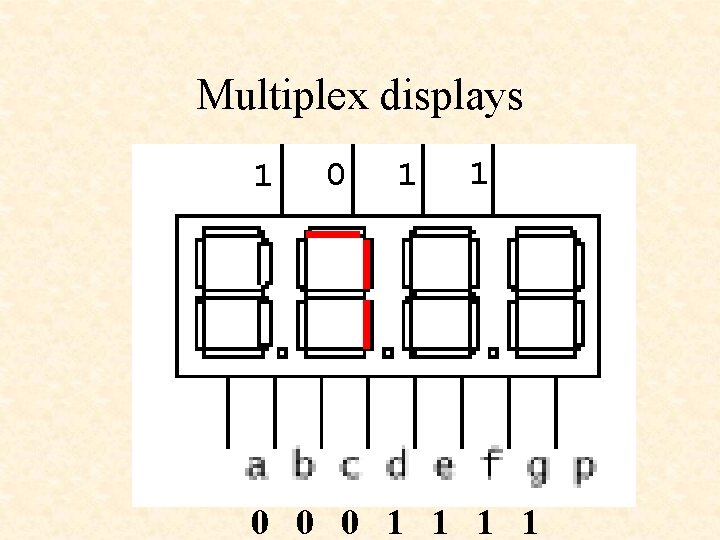

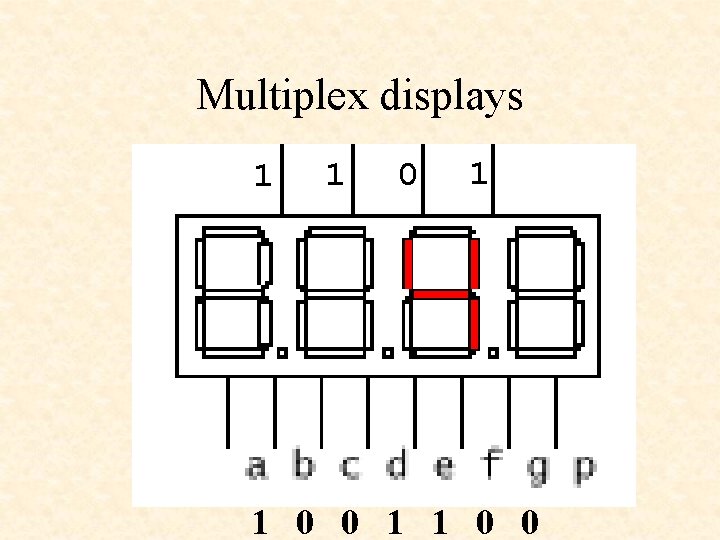

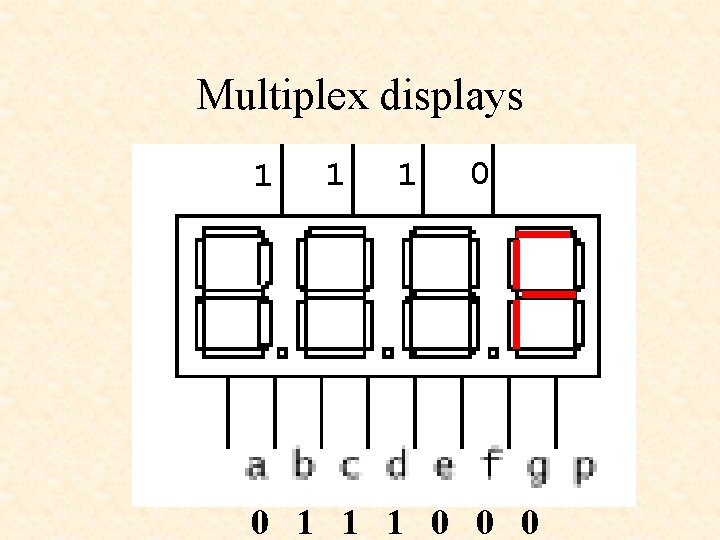

Multiplex displays

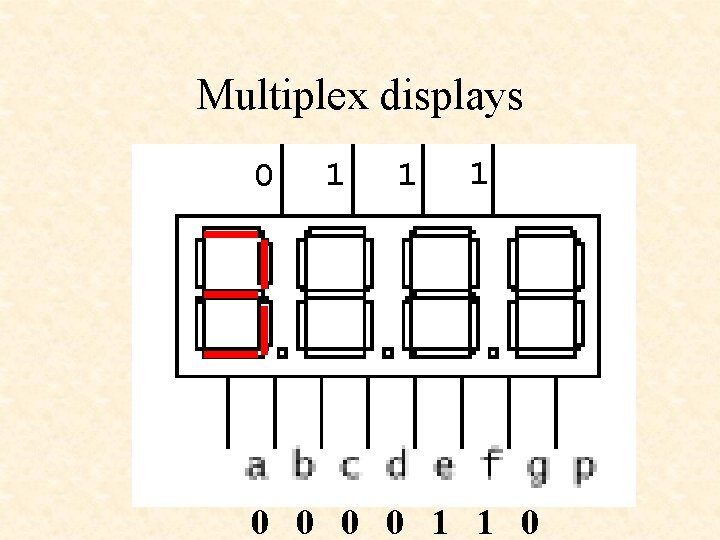

Multiplex displays 0 1 1 1 0 0 1 1 0

Multiplex displays 1 0 1 1 0 0 0 1 1

Multiplex displays 1 1 0 0

Multiplex displays 1 1 1 0 0 0

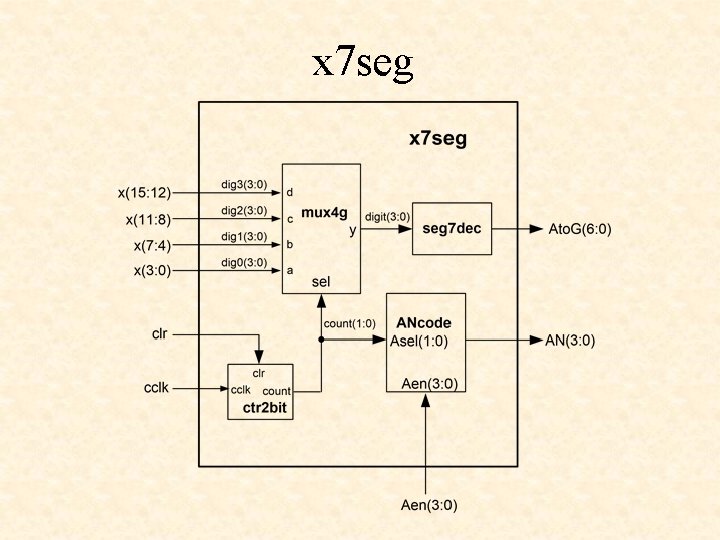

x 7 seg

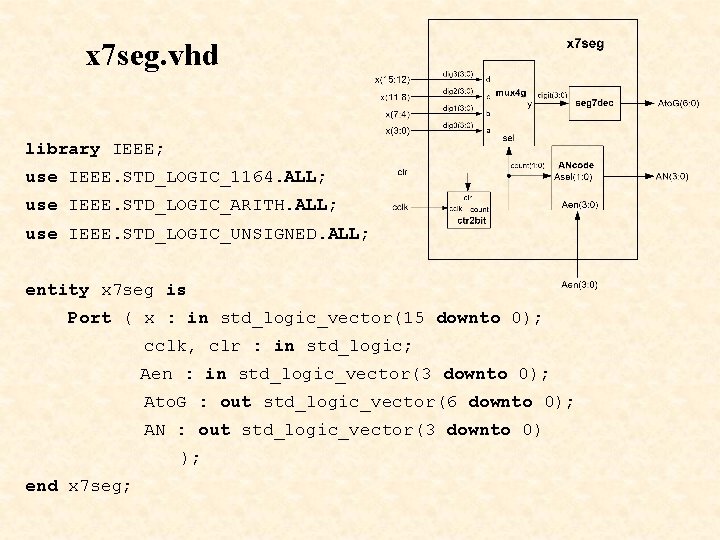

x 7 seg. vhd library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity x 7 seg is Port ( x : in std_logic_vector(15 downto 0); cclk, clr : in std_logic; Aen : in std_logic_vector(3 downto 0); Ato. G : out std_logic_vector(6 downto 0); AN : out std_logic_vector(3 downto 0) ); end x 7 seg;

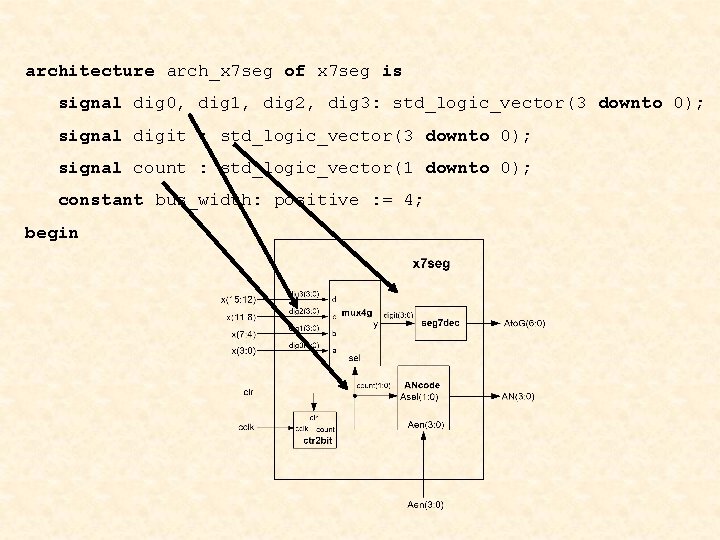

architecture arch_x 7 seg of x 7 seg is signal dig 0, dig 1, dig 2, dig 3: std_logic_vector(3 downto 0); signal digit : std_logic_vector(3 downto 0); signal count : std_logic_vector(1 downto 0); constant bus_width: positive : = 4; begin

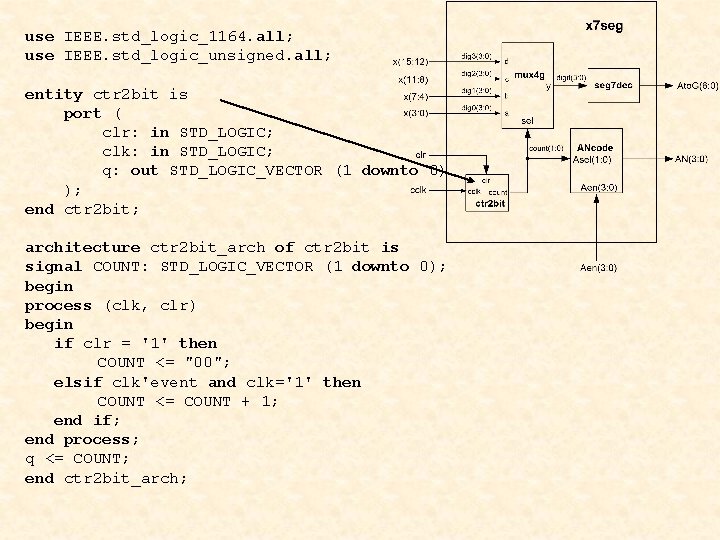

use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; entity ctr 2 bit is port ( clr: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (1 downto 0) ); end ctr 2 bit; architecture ctr 2 bit_arch of ctr 2 bit is signal COUNT: STD_LOGIC_VECTOR (1 downto 0); begin process (clk, clr) begin if clr = '1' then COUNT <= "00"; elsif clk'event and clk='1' then COUNT <= COUNT + 1; end if; end process; q <= COUNT; end ctr 2 bit_arch;

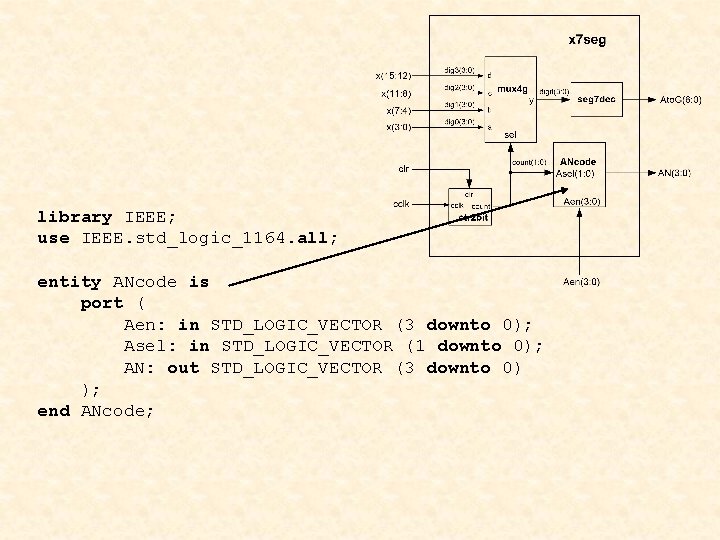

library IEEE; use IEEE. std_logic_1164. all; entity ANcode is port ( Aen: in STD_LOGIC_VECTOR (3 downto 0); Asel: in STD_LOGIC_VECTOR (1 downto 0); AN: out STD_LOGIC_VECTOR (3 downto 0) ); end ANcode;

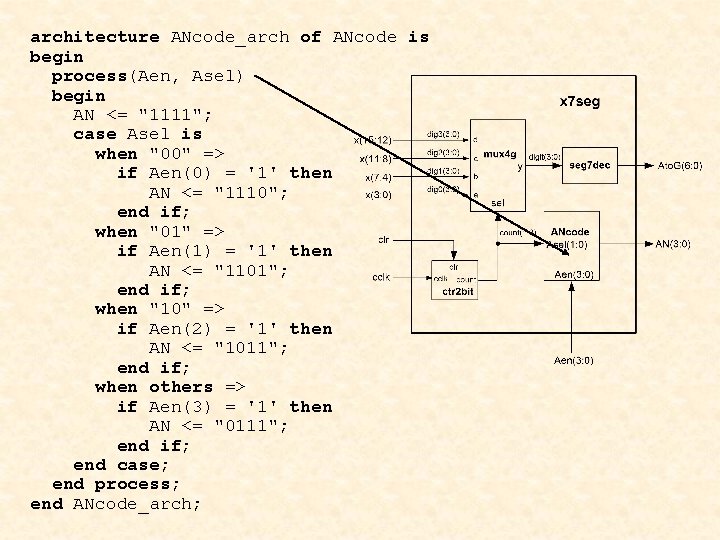

architecture ANcode_arch of ANcode is begin process(Aen, Asel) begin AN <= "1111"; case Asel is when "00" => if Aen(0) = '1' then AN <= "1110"; end if; when "01" => if Aen(1) = '1' then AN <= "1101"; end if; when "10" => if Aen(2) = '1' then AN <= "1011"; end if; when others => if Aen(3) = '1' then AN <= "0111"; end if; end case; end process; end ANcode_arch;

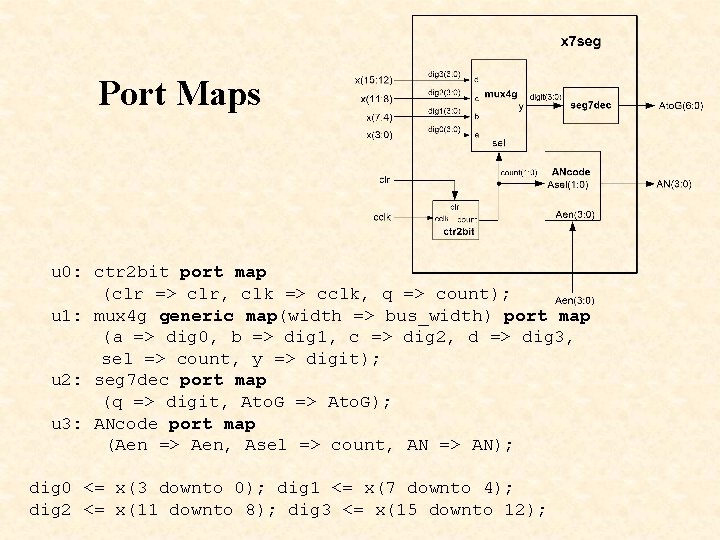

Port Maps u 0: ctr 2 bit port map (clr => clr, clk => cclk, q => count); u 1: mux 4 g generic map(width => bus_width) port map (a => dig 0, b => dig 1, c => dig 2, d => dig 3, sel => count, y => digit); u 2: seg 7 dec port map (q => digit, Ato. G => Ato. G); u 3: ANcode port map (Aen => Aen, Asel => count, AN => AN); dig 0 <= x(3 downto 0); dig 1 <= x(7 downto 4); dig 2 <= x(11 downto 8); dig 3 <= x(15 downto 12);

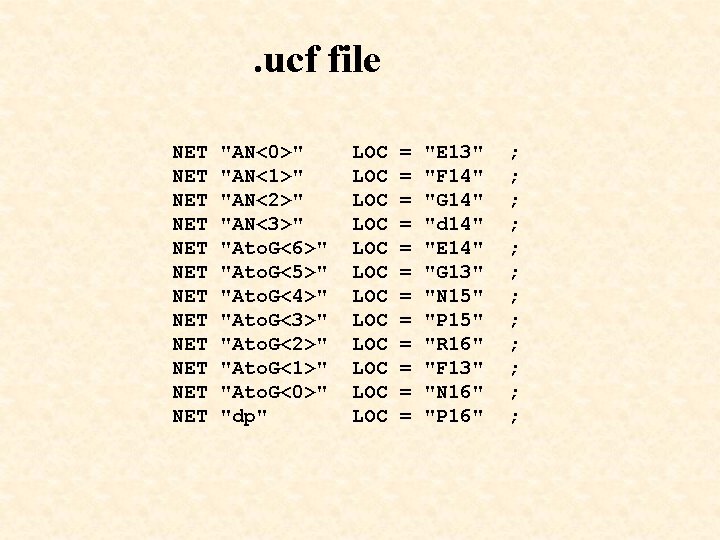

. ucf file NET NET NET "AN<0>" "AN<1>" "AN<2>" "AN<3>" "Ato. G<6>" "Ato. G<5>" "Ato. G<4>" "Ato. G<3>" "Ato. G<2>" "Ato. G<1>" "Ato. G<0>" "dp" LOC LOC LOC = = = "E 13" "F 14" "G 14" "d 14" "E 14" "G 13" "N 15" "P 15" "R 16" "F 13" "N 16" "P 16" ; ; ;

- Slides: 19