7 3 Block RAM 7 3 1 Block

7. 3 Block RAM设计

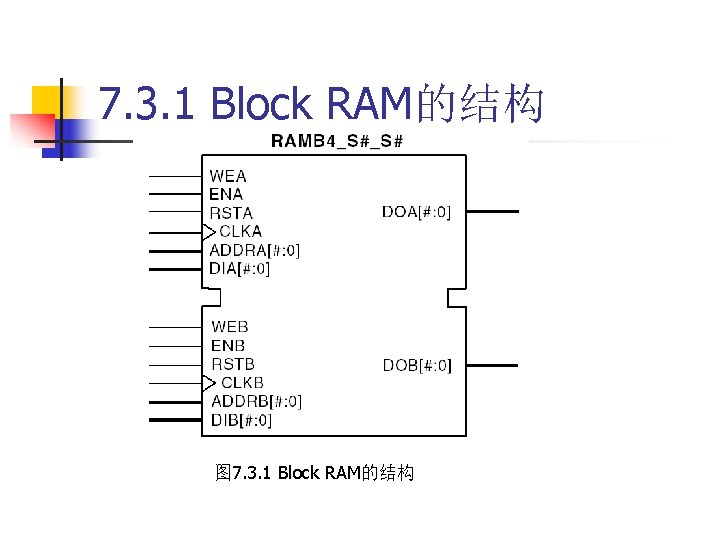

7. 3. 1 Block RAM的结构 图 7. 3. 1 Block RAM的结构

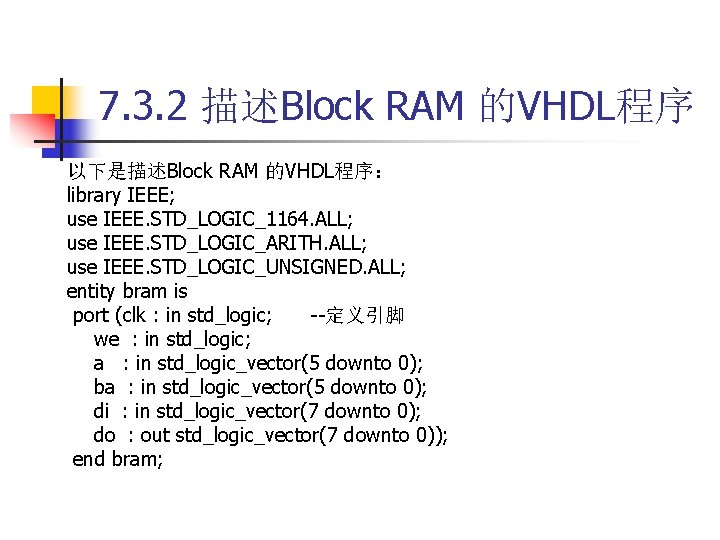

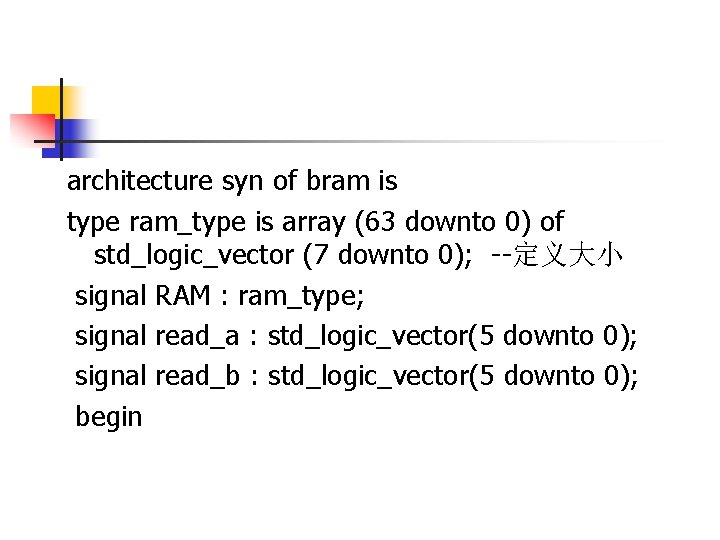

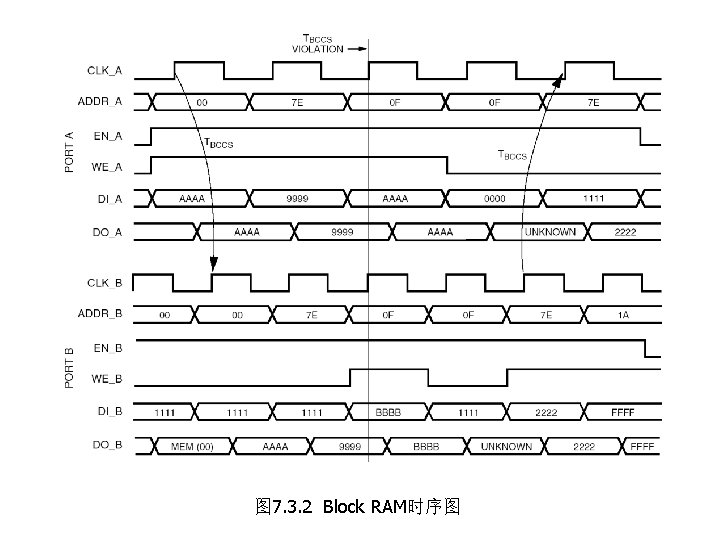

7. 3. 2 描述Block RAM 的VHDL程序 以下是描述Block RAM 的VHDL程序: library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity bram is port (clk : in std_logic; --定义引脚 we : in std_logic; a : in std_logic_vector(5 downto 0); ba : in std_logic_vector(5 downto 0); di : in std_logic_vector(7 downto 0); do : out std_logic_vector(7 downto 0)); end bram;

architecture syn of bram is type ram_type is array (63 downto 0) of std_logic_vector (7 downto 0); --定义大小 signal RAM : ram_type; signal read_a : std_logic_vector(5 downto 0); signal read_b : std_logic_vector(5 downto 0); begin

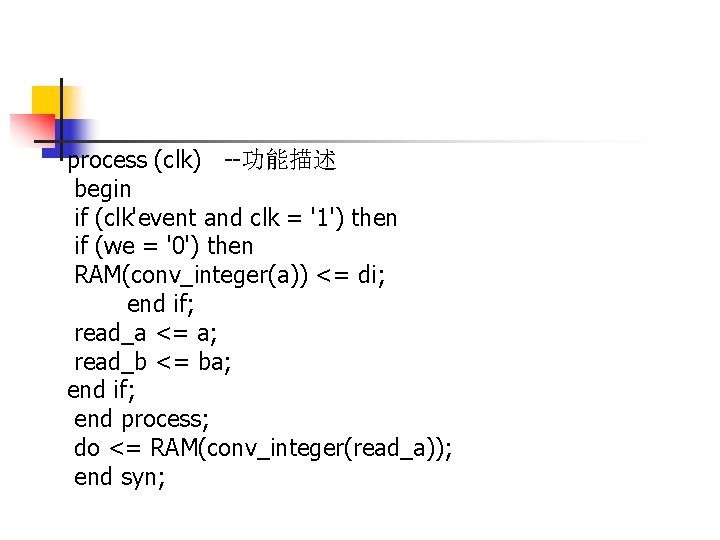

process (clk) --功能描述 begin if (clk'event and clk = '1') then if (we = '0') then RAM(conv_integer(a)) <= di; end if; read_a <= a; read_b <= ba; end if; end process; do <= RAM(conv_integer(read_a)); end syn;

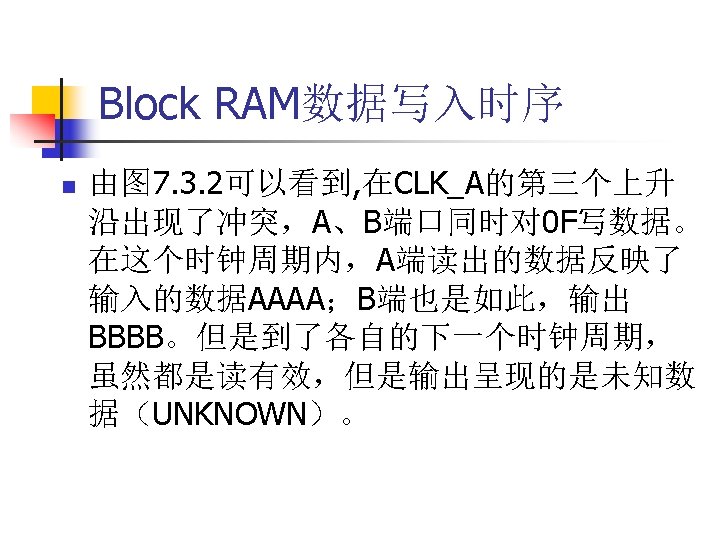

图 7. 3. 2 Block RAM时序图

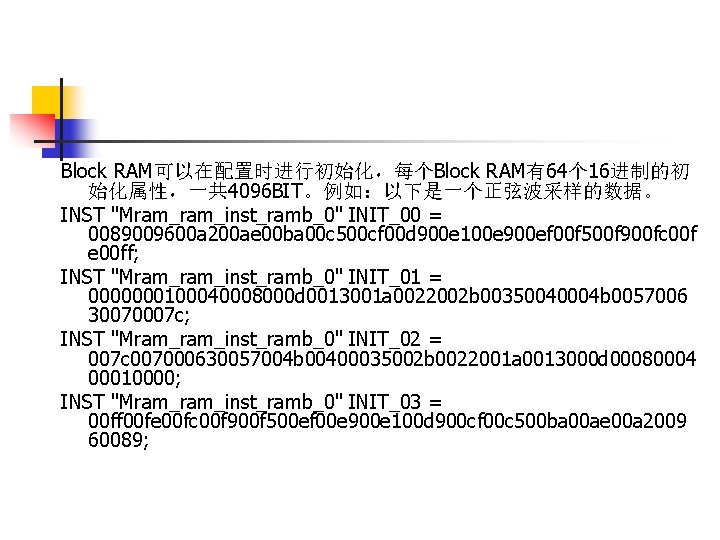

Block RAM可以在配置时进行初始化,每个Block RAM有64个 16进制的初 始化属性,一共 4096 BIT。例如:以下是一个正弦波采样的数据。 INST "Mram_inst_ramb_0" INIT_00 = 0089009600 a 200 ae 00 ba 00 c 500 cf 00 d 900 e 100 e 900 ef 00 f 500 f 900 fc 00 f e 00 ff; INST "Mram_inst_ramb_0" INIT_01 = 0000000100040008000 d 0013001 a 0022002 b 00350040004 b 0057006 30070007 c; INST "Mram_inst_ramb_0" INIT_02 = 007 c 007000630057004 b 00400035002 b 0022001 a 0013000 d 00080004 00010000; INST "Mram_inst_ramb_0" INIT_03 = 00 ff 00 fe 00 fc 00 f 900 f 500 ef 00 e 900 e 100 d 900 cf 00 c 500 ba 00 ae 00 a 2009 60089;

- Slides: 16