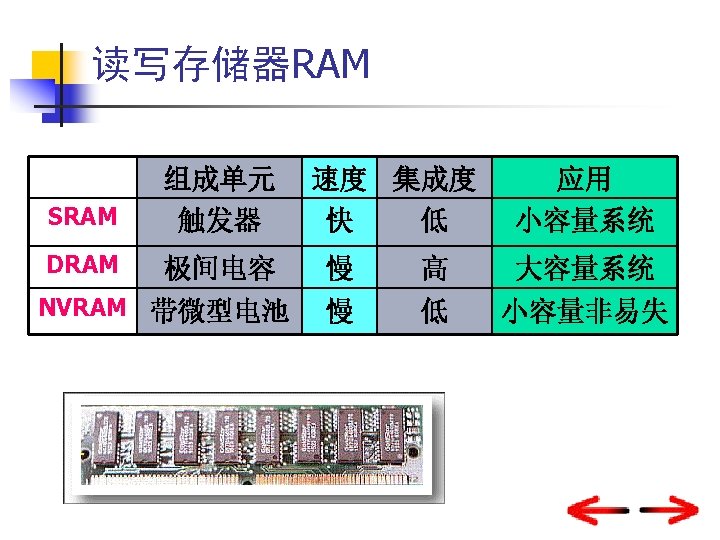

6 n n n SRAM 2114DRAM 4116 EPROM

- Slides: 55

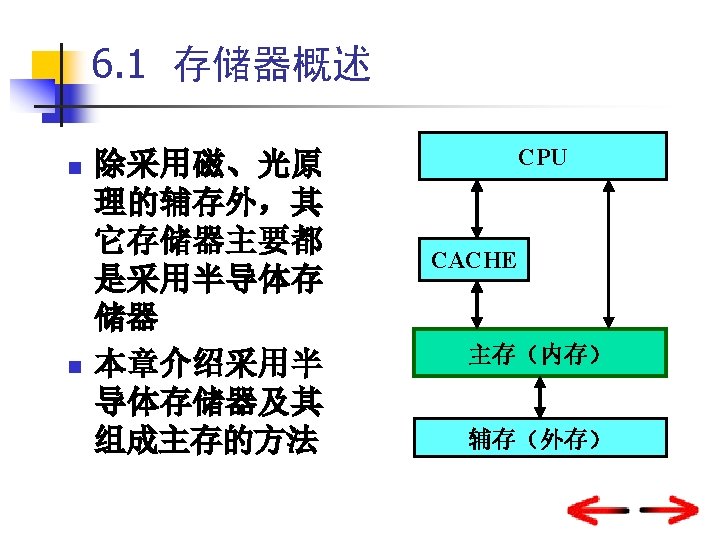

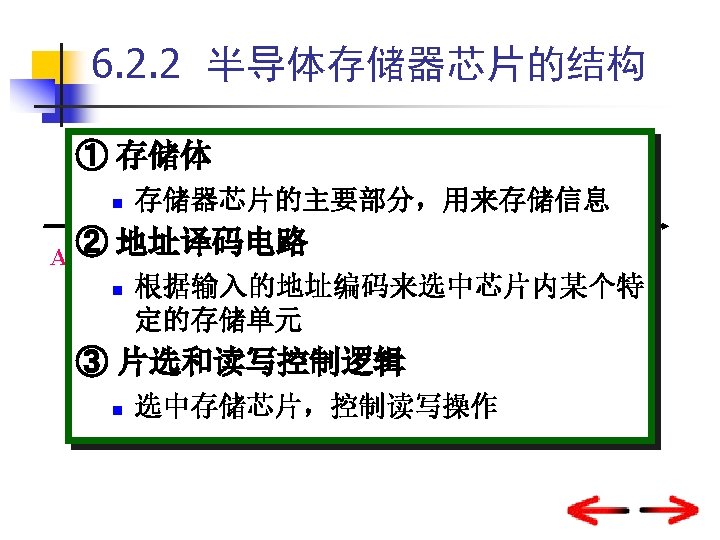

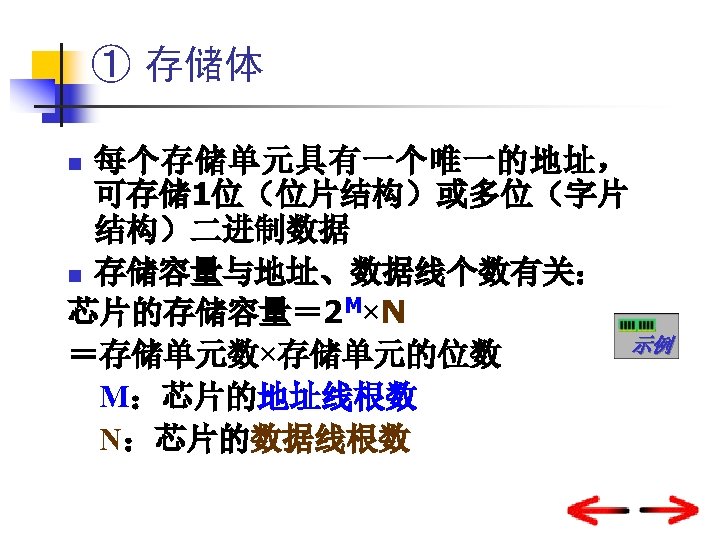

第 6章 存储器系统 教学重点 n n n 芯片SRAM 2114和DRAM 4116 芯片EPROM 2764和EEPROM 2817 A SRAM、EPROM与CPU的连接

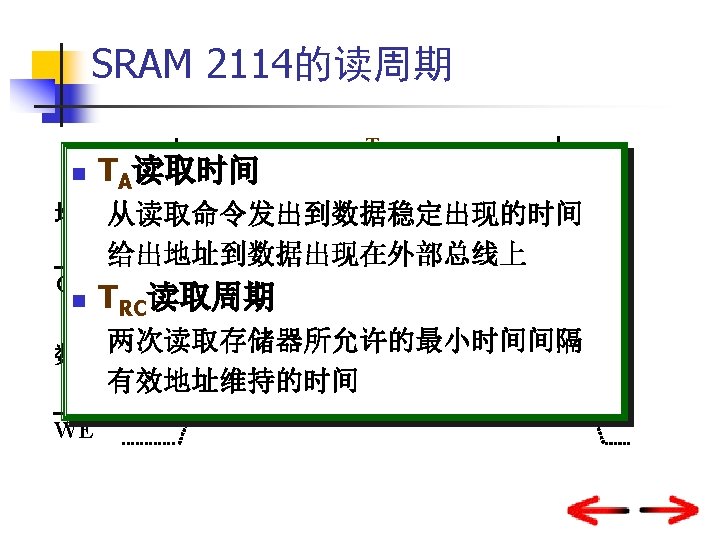

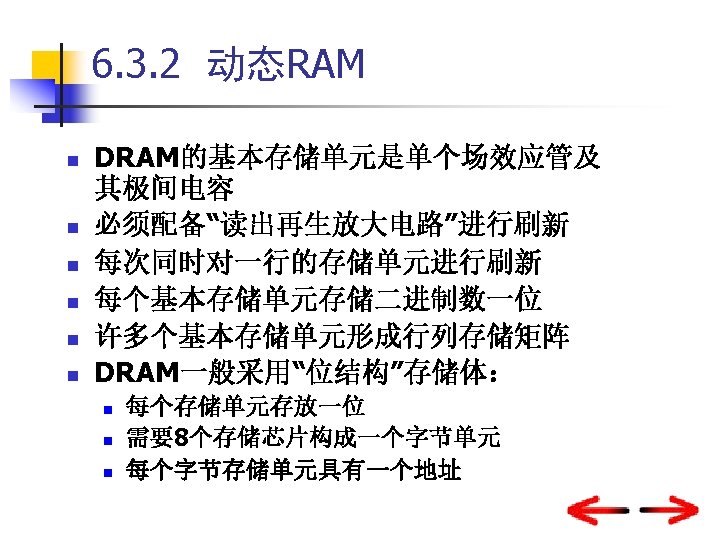

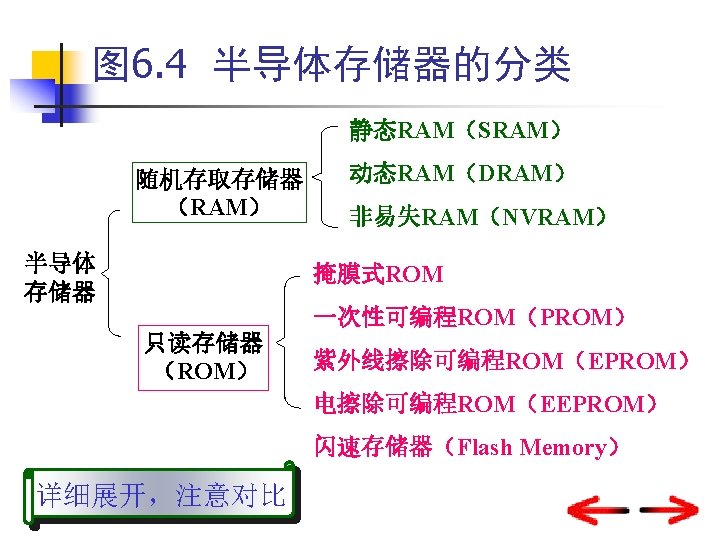

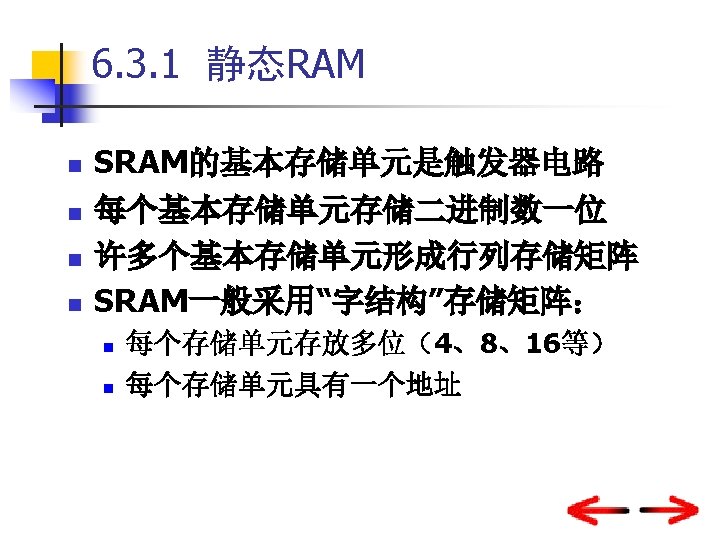

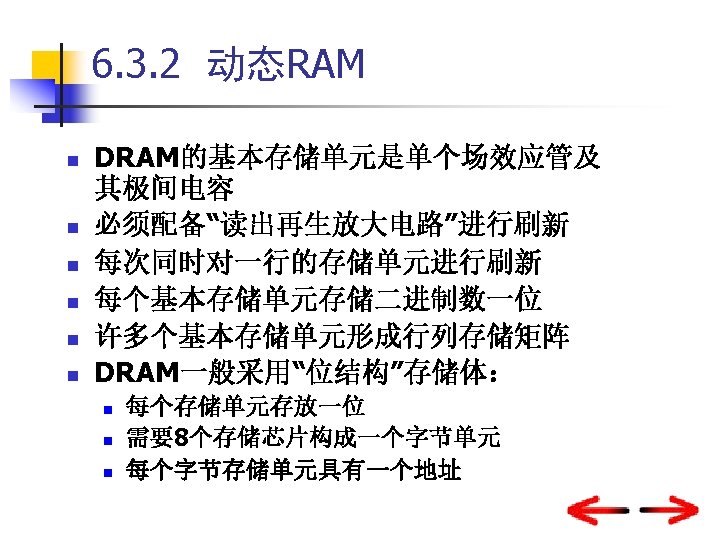

6. 3 随机存取存储器 静态RAM SRAM 2114 SRAM 6264 动态RAM DRAM 4116 DRAM 2164

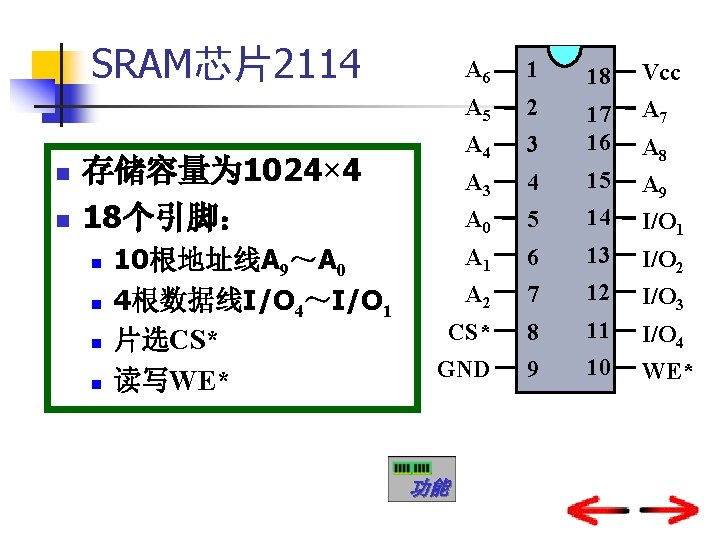

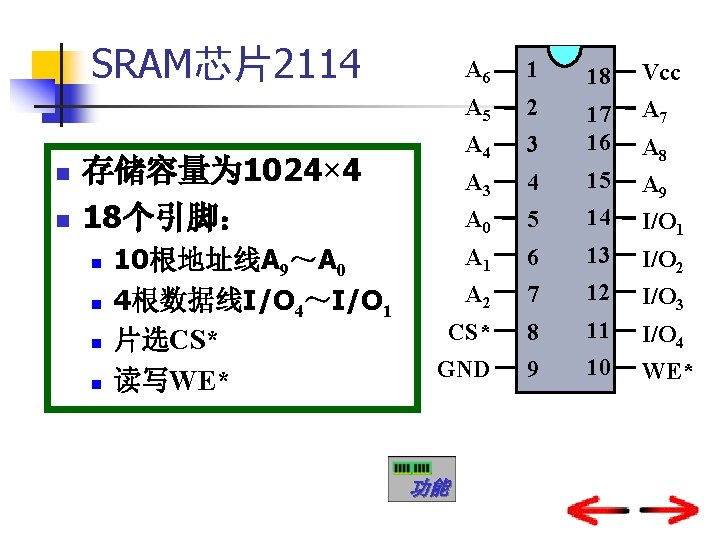

SRAM芯片2114 n n A 6 1 18 Vcc A 5 2 A 7 A 4 3 17 16 A 3 4 15 A 9 A 0 5 14 I/O 1 A 1 6 13 I/O 2 A 2 7 12 I/O 3 CS* 8 11 I/O 4 GND 9 10 WE* 存储容量为 1024× 4 18个引脚: n n 10根地址线A 9~A 0 4根数据线I/O 4~I/O 1 片选CS* 读写WE* 功能 A 8

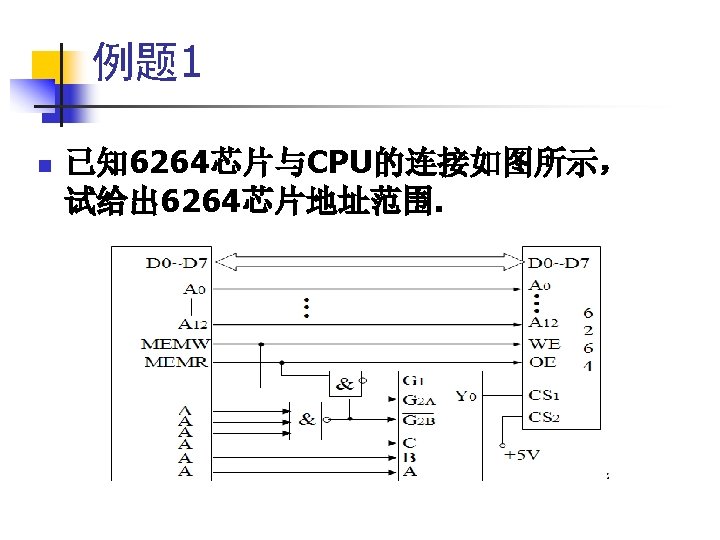

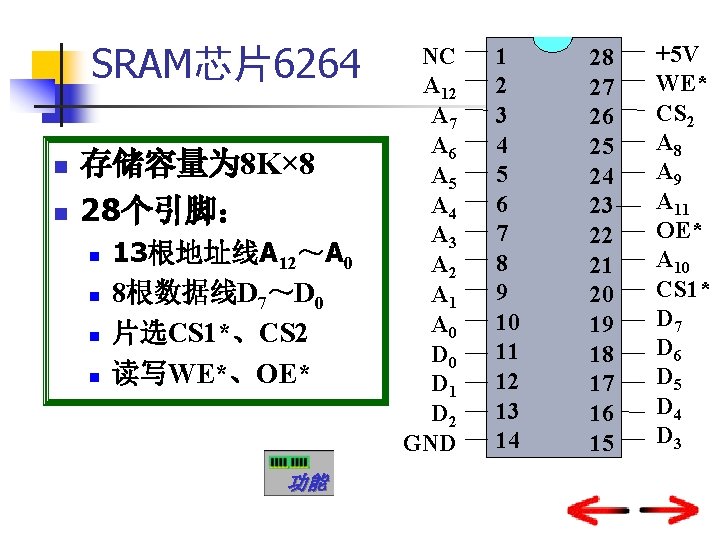

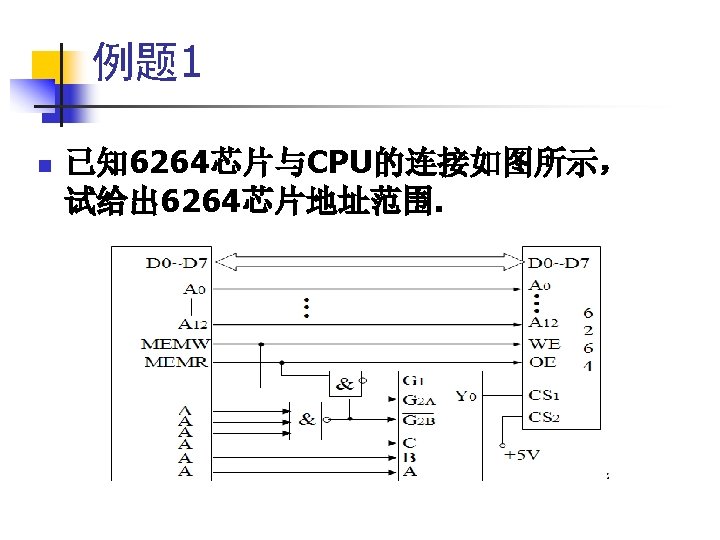

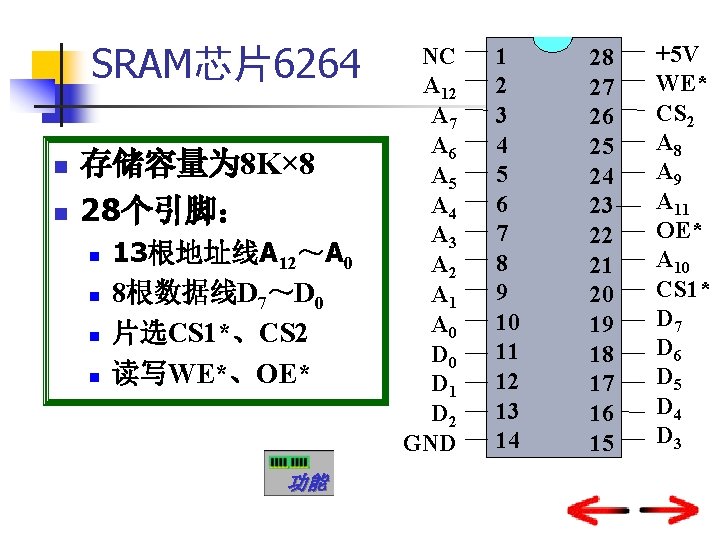

SRAM芯片6264 n n 存储容量为 8 K× 8 28个引脚: n n 13根地址线A 12~A 0 8根数据线D 7~D 0 片选CS 1*、CS 2 读写WE*、OE* 功能 NC A 12 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 D 1 D 2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 +5 V WE* CS 2 A 8 A 9 A 11 OE* A 10 CS 1* D 7 D 6 D 5 D 4 D 3

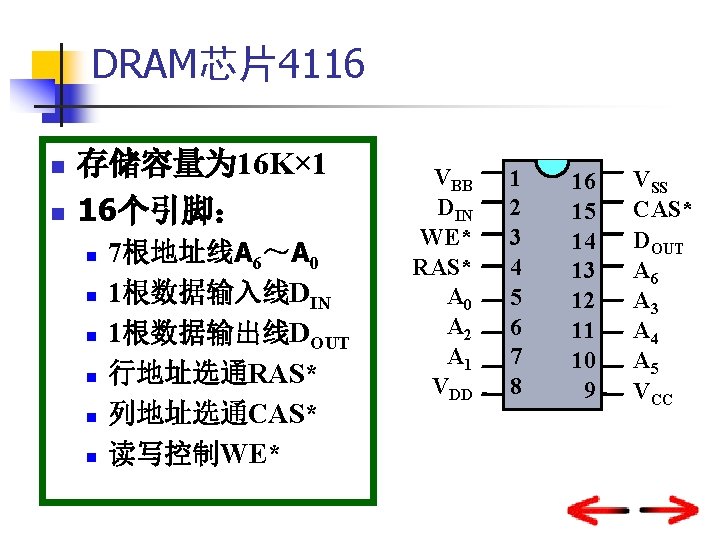

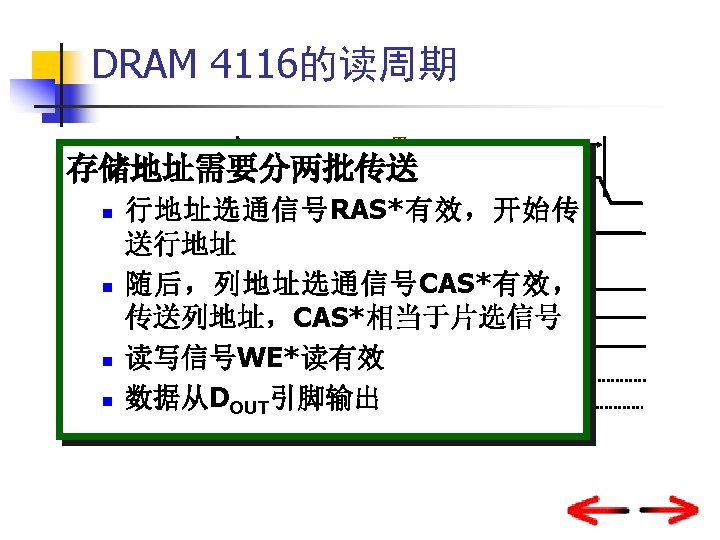

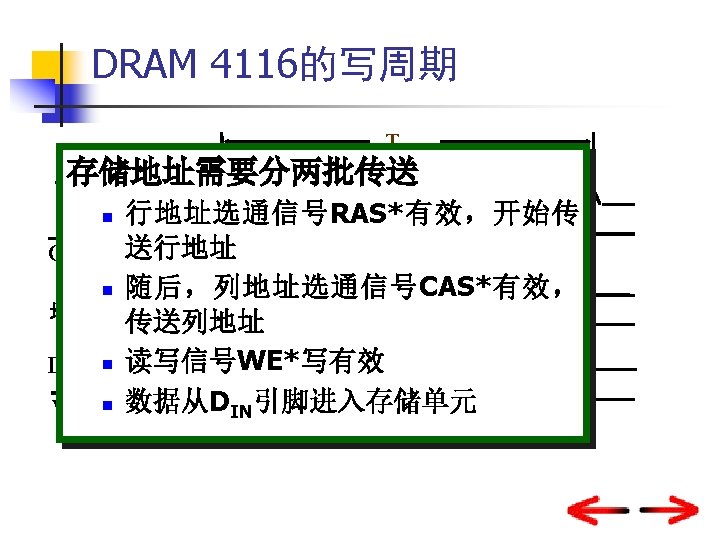

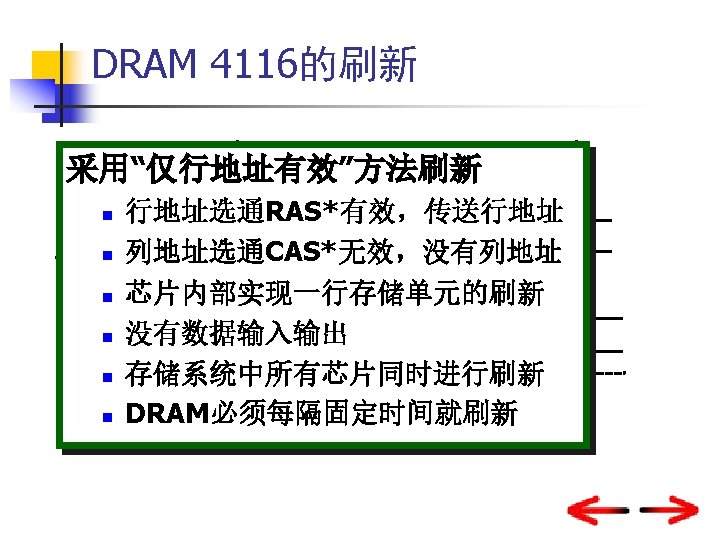

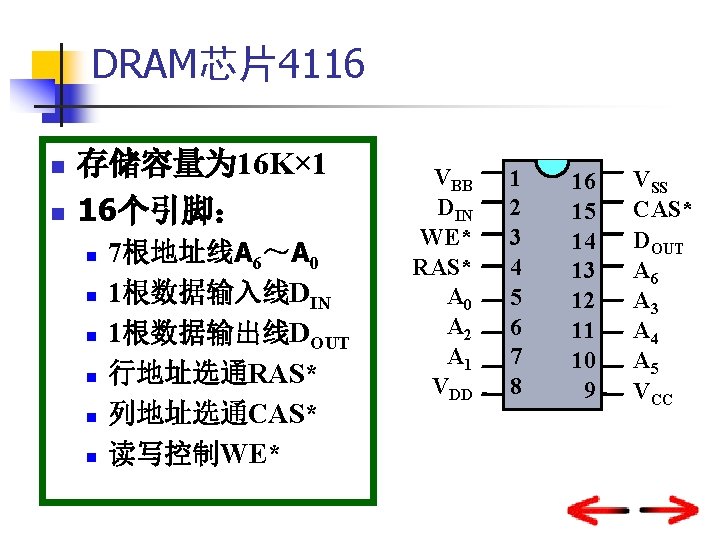

DRAM芯片4116 n n 存储容量为 16 K× 1 16个引脚: n n n 7根地址线A 6~A 0 1根数据输入线DIN 1根数据输出线DOUT 行地址选通RAS* 列地址选通CAS* 读写控制WE* VBB DIN WE* RAS* A 0 A 2 A 1 VDD 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 VSS CAS* DOUT A 6 A 3 A 4 A 5 VCC

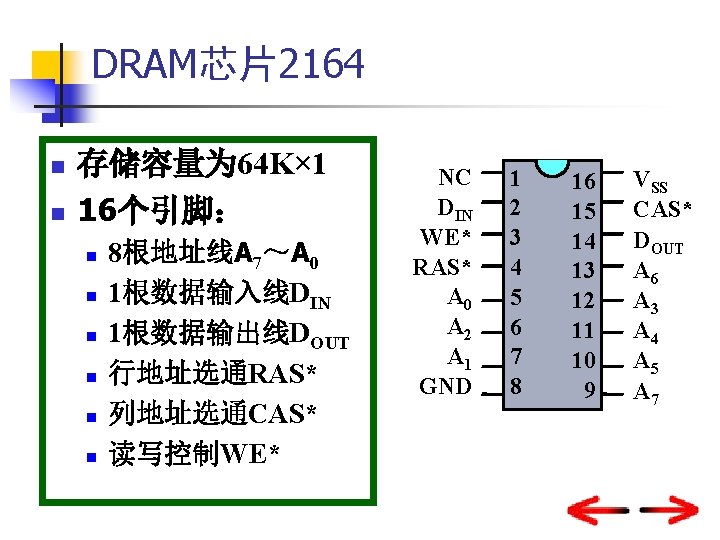

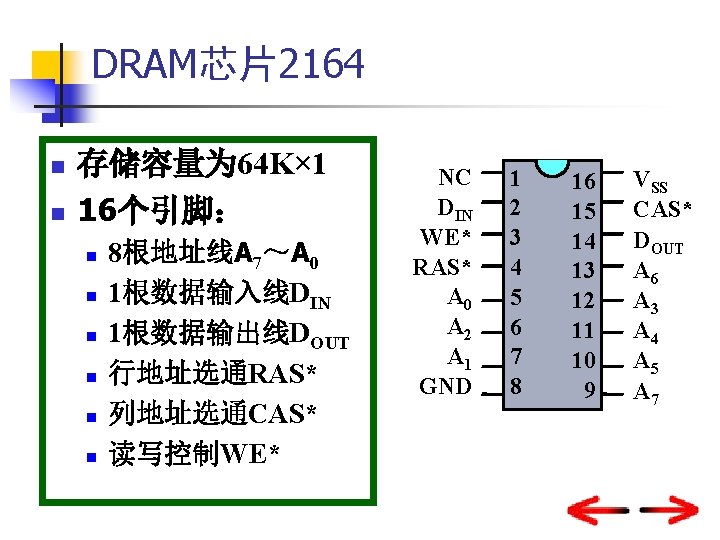

DRAM芯片2164 n n 存储容量为 64 K× 1 16个引脚: n n n 8根地址线A 7~A 0 1根数据输入线DIN 1根数据输出线DOUT 行地址选通RAS* 列地址选通CAS* 读写控制WE* NC DIN WE* RAS* A 0 A 2 A 1 GND 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 VSS CAS* DOUT A 6 A 3 A 4 A 5 A 7

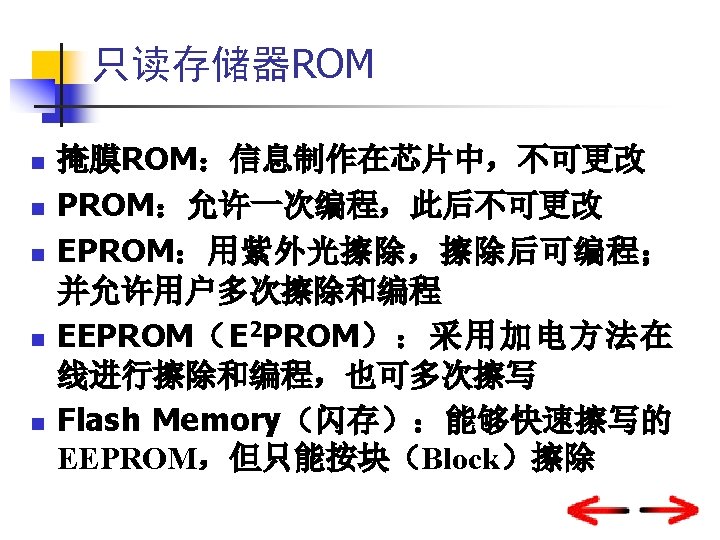

6. 4 只读存储器 EPROM 2716 EPROM 2764 EEPROM 2717 A EEPROM 2864 A

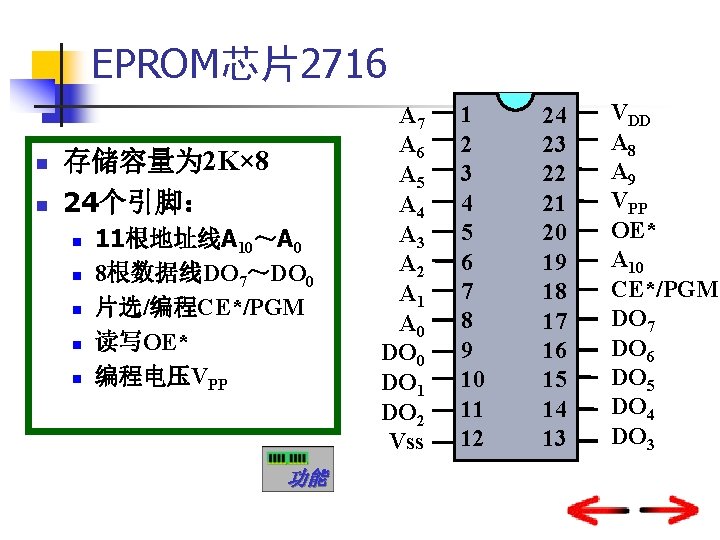

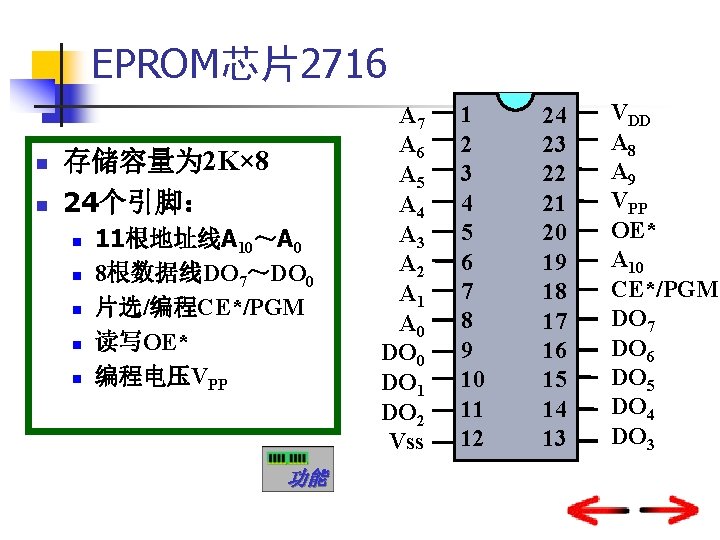

EPROM芯片2716 n n 存储容量为 2 K× 8 24个引脚: n n n 11根地址线A 10~A 0 8根数据线DO 7~DO 0 片选/编程CE*/PGM 读写OE* 编程电压VPP 功能 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 DO 1 DO 2 Vss 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 VDD A 8 A 9 VPP OE* A 10 CE*/PGM DO 7 DO 6 DO 5 DO 4 DO 3

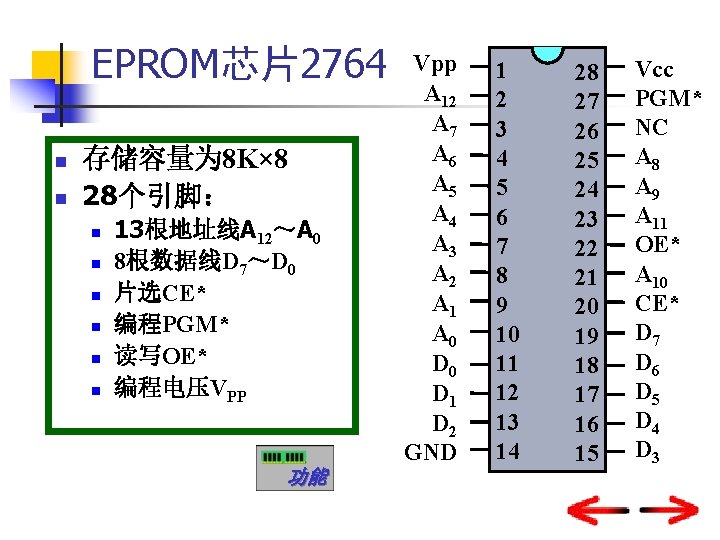

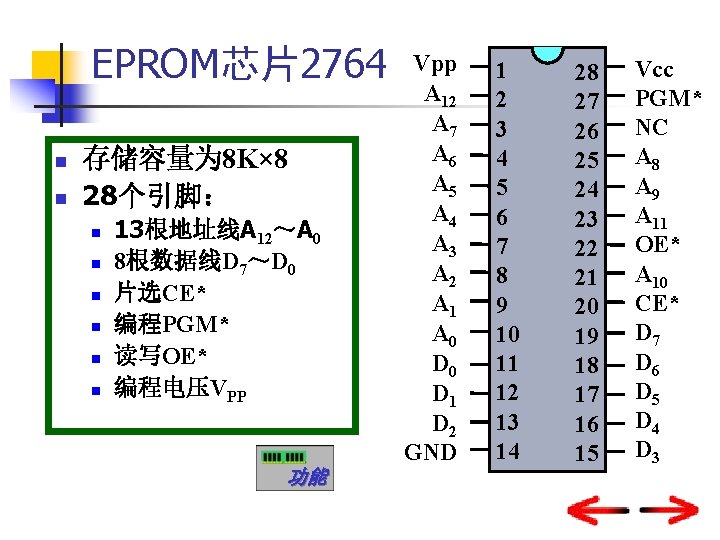

EPROM芯片2764 n n 存储容量为 8 K× 8 28个引脚: n n n 13根地址线A 12~A 0 8根数据线D 7~D 0 片选CE* 编程PGM* 读写OE* 编程电压VPP 功能 Vpp A 12 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 D 1 D 2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc PGM* NC A 8 A 9 A 11 OE* A 10 CE* D 7 D 6 D 5 D 4 D 3

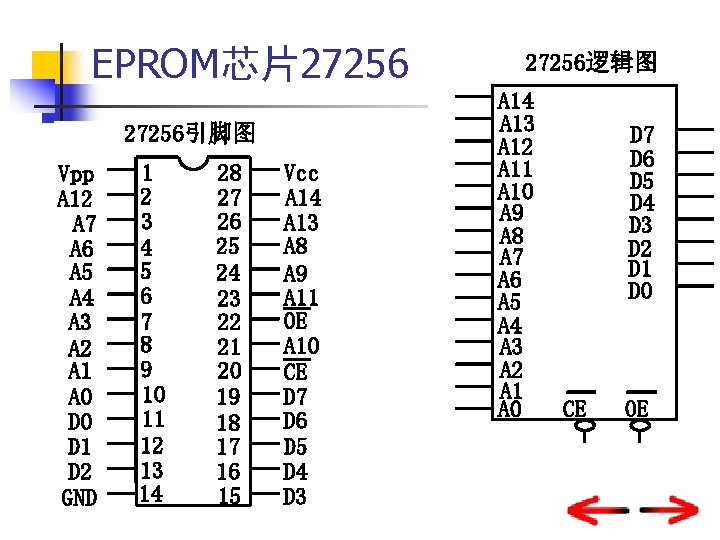

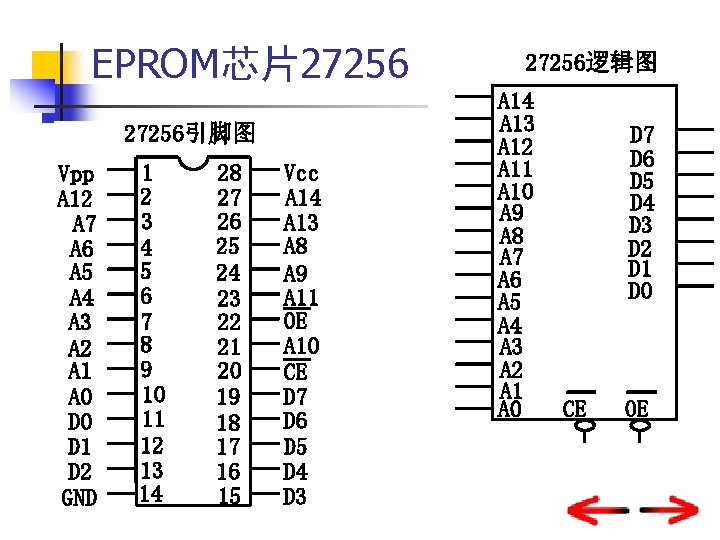

EPROM芯片27256引脚图 Vpp A 12 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 D 1 D 2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc A 14 A 13 A 8 A 9 A 11 OE A 10 CE D 7 D 6 D 5 D 4 D 3 27256逻辑图 A 14 A 13 A 12 A 11 A 10 A 9 A 8 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 CE OE

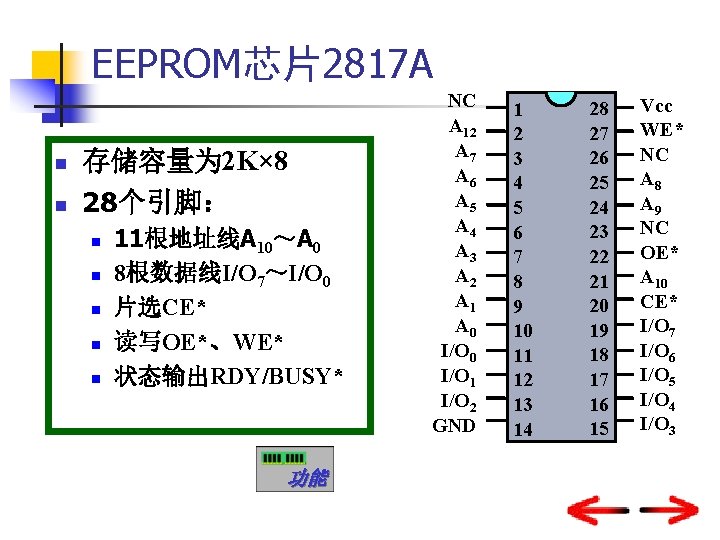

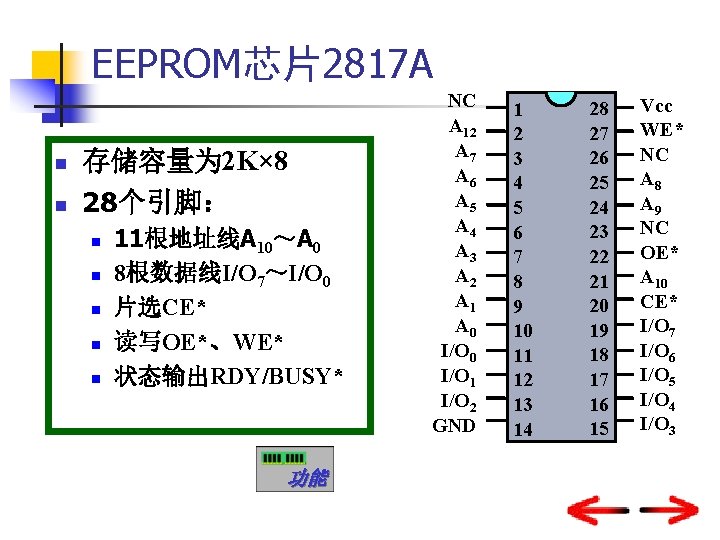

EEPROM芯片2817 A n n 存储容量为 2 K× 8 28个引脚: n n n 11根地址线A 10~A 0 8根数据线I/O 7~I/O 0 片选CE* 读写OE*、WE* 状态输出RDY/BUSY* 功能 NC A 12 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 I/O 1 I/O 2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc WE* NC A 8 A 9 NC OE* A 10 CE* I/O 7 I/O 6 I/O 5 I/O 4 I/O 3

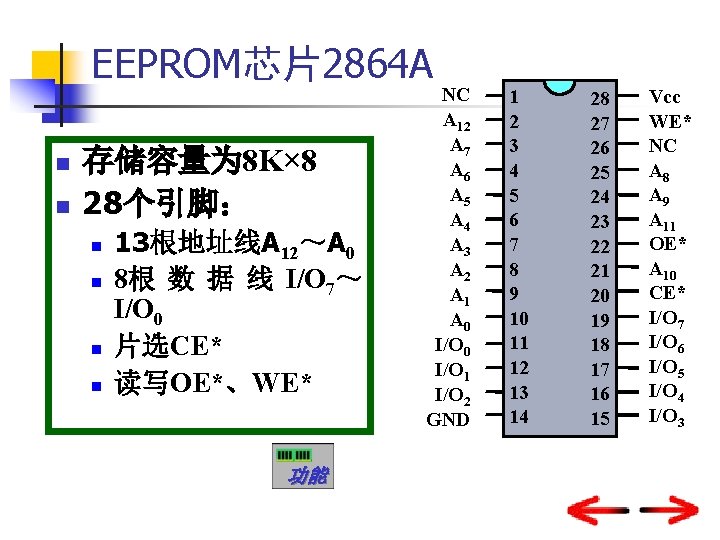

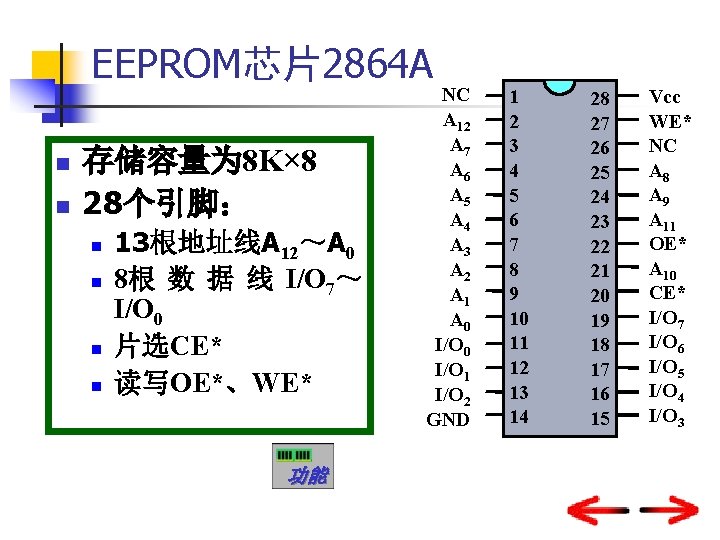

EEPROM芯片2864 A n n 存储容量为 8 K× 8 28个引脚: n n 13根地址线A 12~A 0 8根 数 据 线 I/O 7~ I/O 0 片选CE* 读写OE*、WE* 功能 NC A 12 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 I/O 1 I/O 2 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc WE* NC A 8 A 9 A 11 OE* A 10 CE* I/O 7 I/O 6 I/O 5 I/O 4 I/O 3

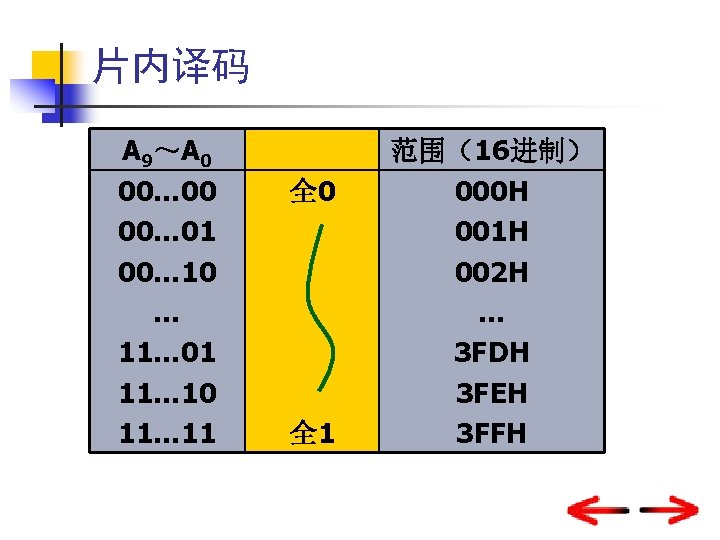

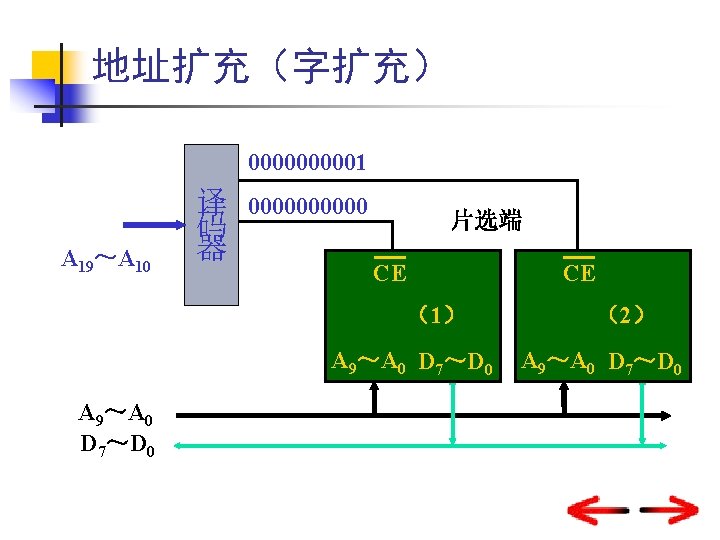

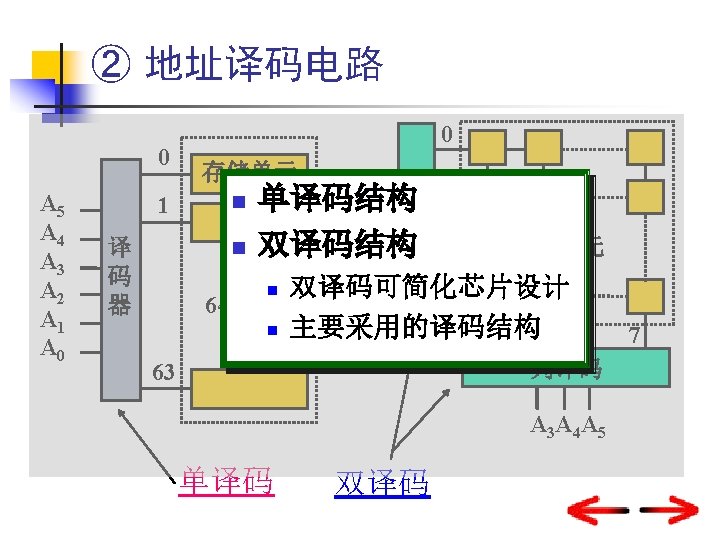

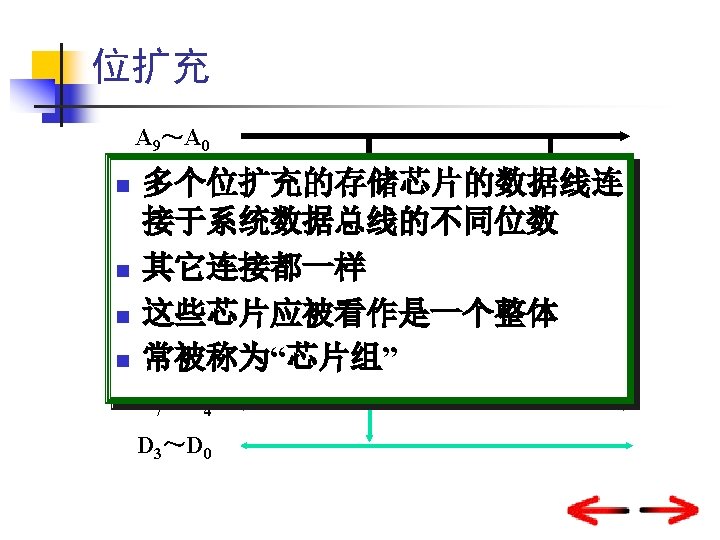

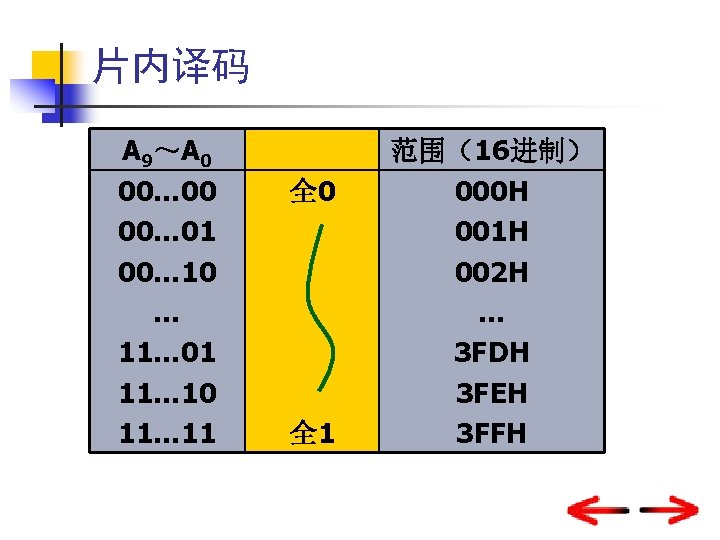

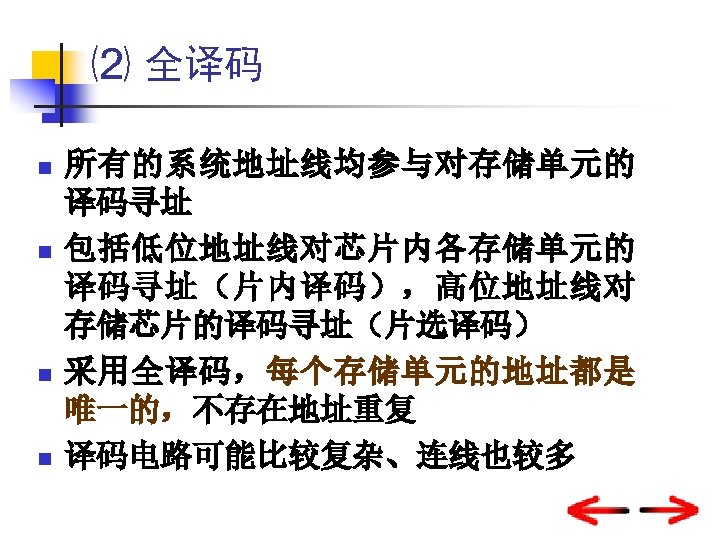

片内译码 存储芯片 A 9~A 0 范围(16进制) 00… 00 全 0 000 H 00… 01 001 H 00… 10 A 9~A 0 002 H … … 11… 01 3 FDH 11… 10 3 FEH 11… 11 全 1 3 FFH

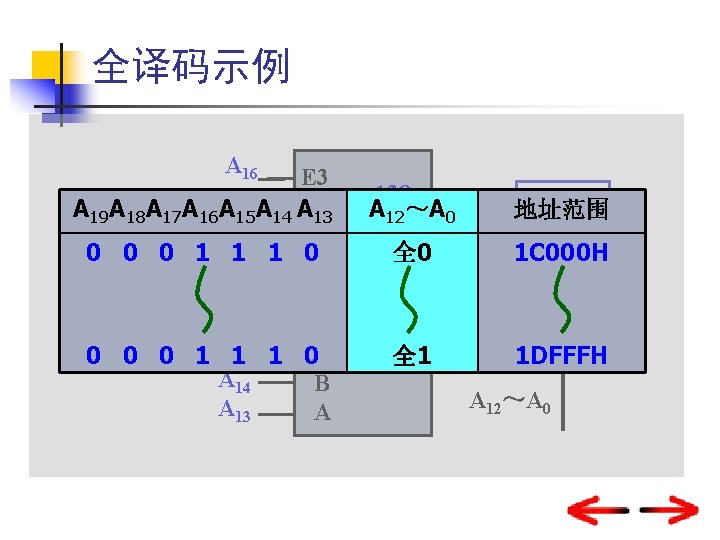

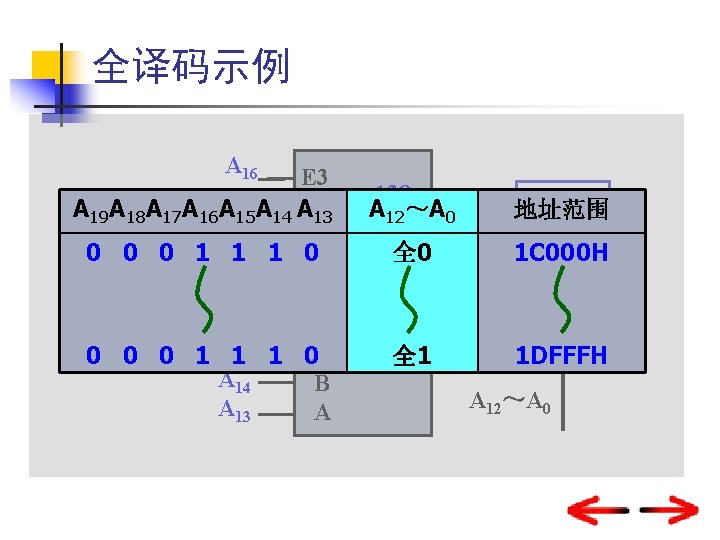

全译码示例 A 16 E 3 A 19 A 18 A 17 AIO/M 16 A 15 A 14 A 13 E 2 0 A 190 0 1 1 1 0 A 18 E 1 A 17 0 0 0 1 A 115 1 0 C A 14 B A 138 A 12~A 0 全 0 Y 6 全 1 地址范围 2764 1 C 000 H CE 1 DFFFH A 12~A 0

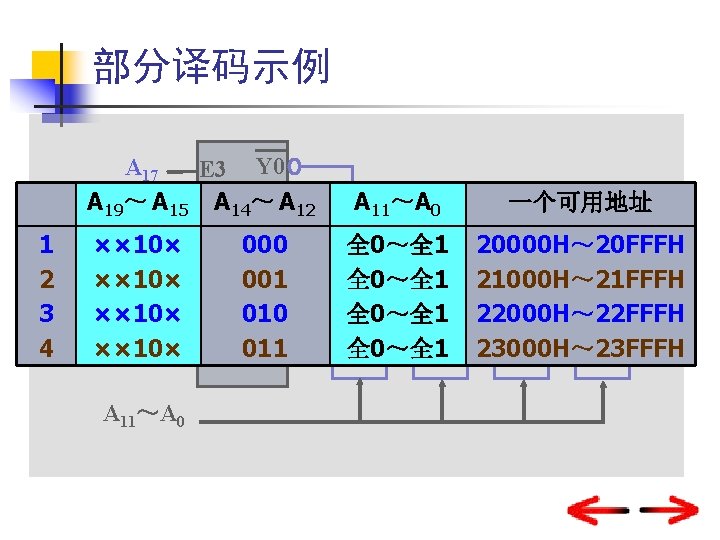

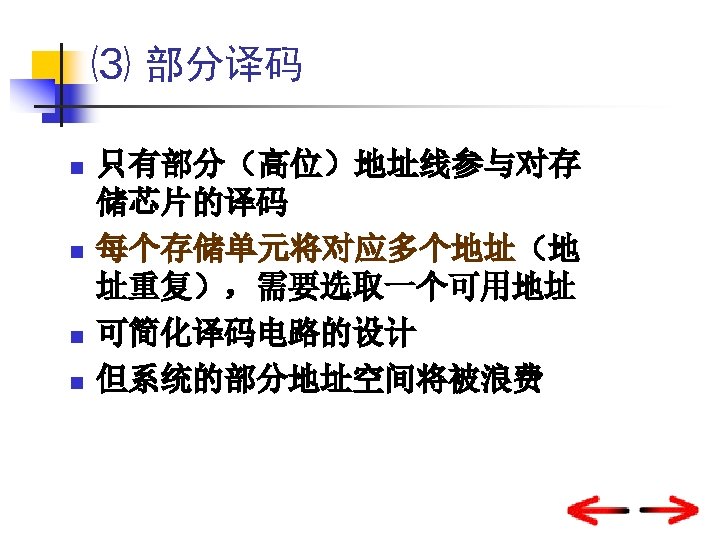

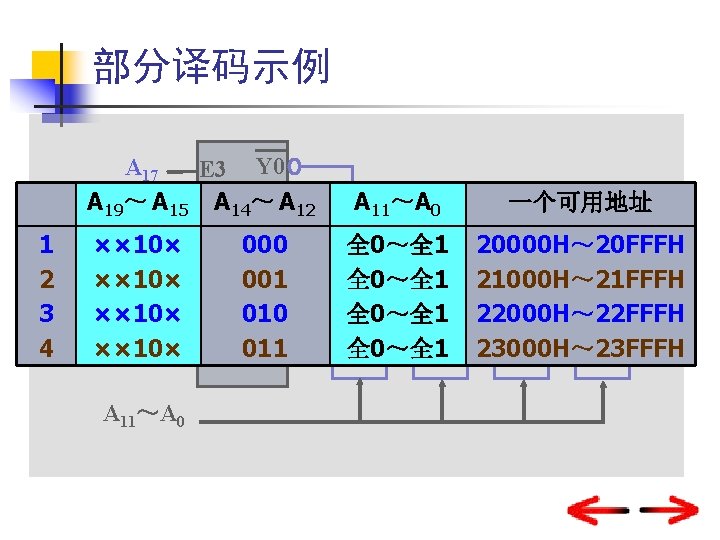

部分译码示例 1 2 3 4 A 17 E 3 Y 0 A 16 A 15 E 2 Y 1 A 12 A 19~ A 14~ A 11~A 0 Y 2 E 1 IO/M ×× 10× 000 全 0~全 1 Y 3 ×× 10× 001 CE全 0~全 1 CE A 14 C ×× 10× 010 全 0~全 1 A 13 2732 B 138 ×× 10× 全 0~全 1 (1) (2) A 12 A 011 A 11~A 0 一个可用地址 20000 H~ 20 FFFH 21000 H~ 21 FFFH CE CE 22000 H~ 22 FFFH 2732 23000 H~ 23 FFFH (3) (4)

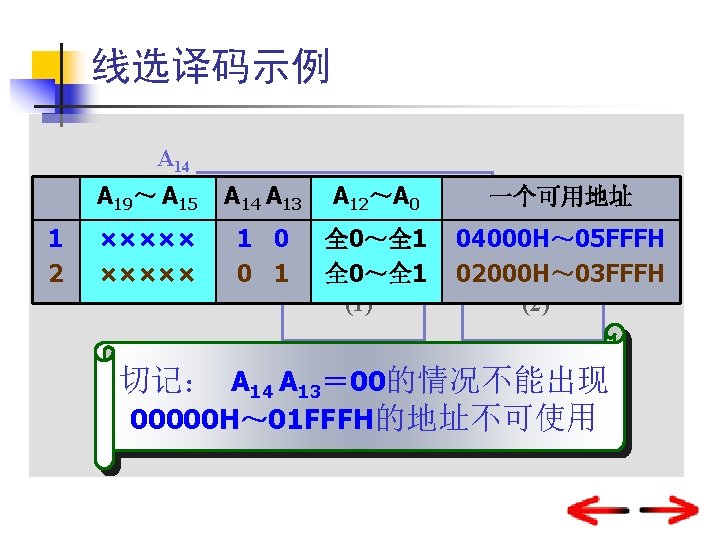

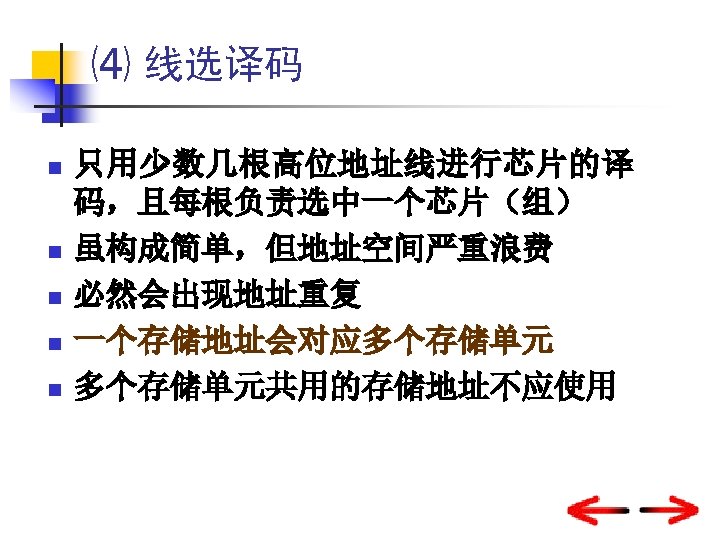

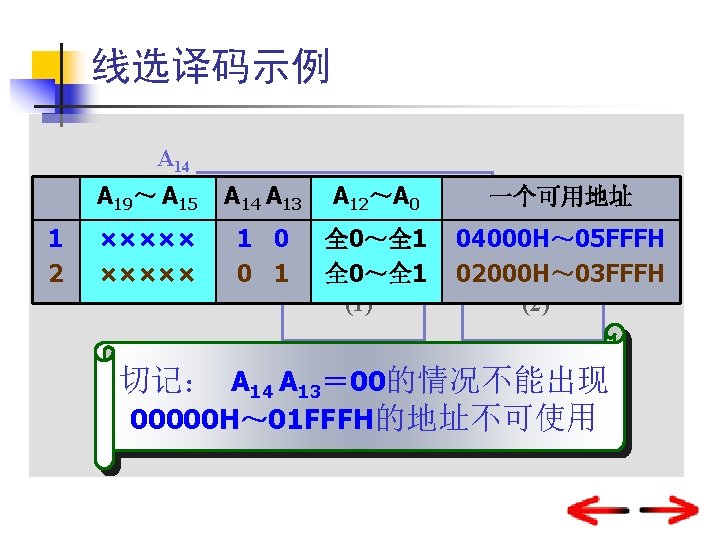

线选译码示例 A 14 1 2 A 19~A A 1315 A 14 A 13 ××××× 1 0 0 1 A 12~A 0 CE 全 0~全 1 2764 全 0~全 1 (1) 一个可用地址 CE 04000 H~ 05 FFFH 2764 02000 H~ 03 FFFH (2) A 12~A 0 切记: A 14 A 13= 00的情况不能出现 00000 H~ 01 FFFH的地址不可使用