5 DC and Transient Response Lecture 4 Delay

- Slides: 44

5: DC and Transient Response Lecture 4: Delay Optimization and Logical Effort 1

Outline q q q q RC Delay Models Delay Estimation Logical Effort Delay in a Logic Gate Multistage Logic Networks Choosing the Best Number of Stages Examples Summary 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 2

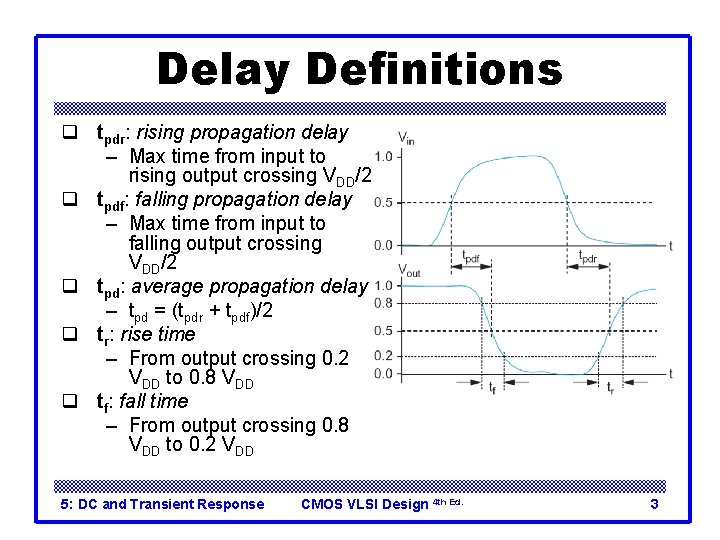

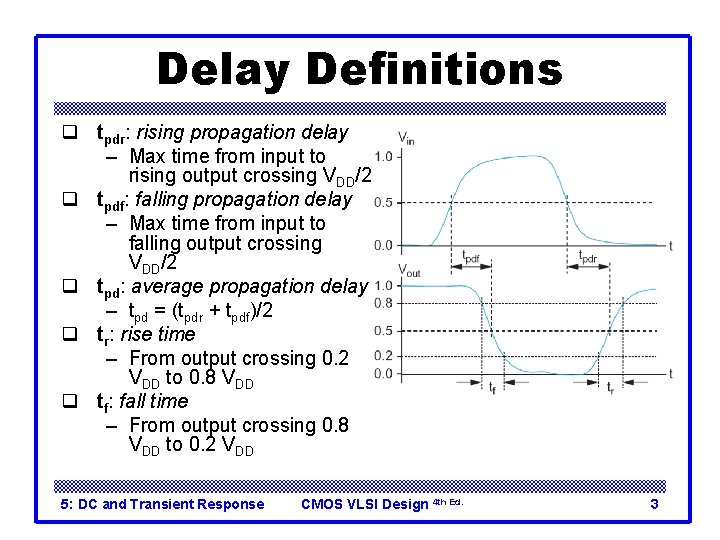

Delay Definitions q tpdr: rising propagation delay – Max time from input to rising output crossing VDD/2 q tpdf: falling propagation delay – Max time from input to falling output crossing VDD/2 q tpd: average propagation delay – tpd = (tpdr + tpdf)/2 q tr: rise time – From output crossing 0. 2 VDD to 0. 8 VDD q tf: fall time – From output crossing 0. 8 VDD to 0. 2 VDD 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 3

Delay Definitions q tcdr: rising contamination delay – Min time from input to rising output crossing VDD/2 q tcdf: falling contamination delay – Min time from input to falling output crossing VDD/2 q tcd: average contamination delay – tcd = (tcdr + tcdf)/2 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 4

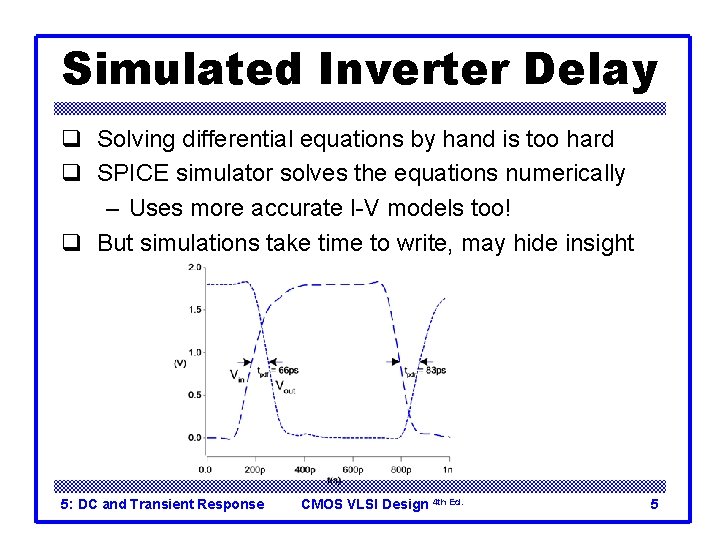

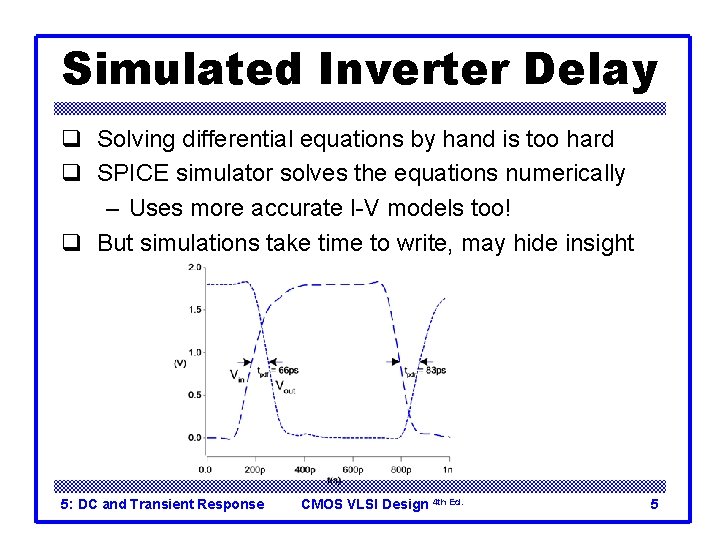

Simulated Inverter Delay q Solving differential equations by hand is too hard q SPICE simulator solves the equations numerically – Uses more accurate I-V models too! q But simulations take time to write, may hide insight 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 5

Delay Estimation q We would like to be able to easily estimate delay – Not as accurate as simulation – But easier to ask “What if? ” q The step response usually looks like a 1 st order RC response with a decaying exponential. q Use RC delay models to estimate delay – C = total capacitance on output node – Use effective resistance R – So that tpd = RC q Characterize transistors by finding their effective R – Depends on average current as gate switches 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 6

Effective Resistance q Shockley models have limited value – Not accurate enough for modern transistors – Too complicated for much hand analysis q Simplification: treat transistor as resistor – Replace Ids(Vds, Vgs) with effective resistance R • Ids = Vds/R – R averaged across switching of digital gate q Too inaccurate to predict current at any given time – But good enough to predict RC delay 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 7

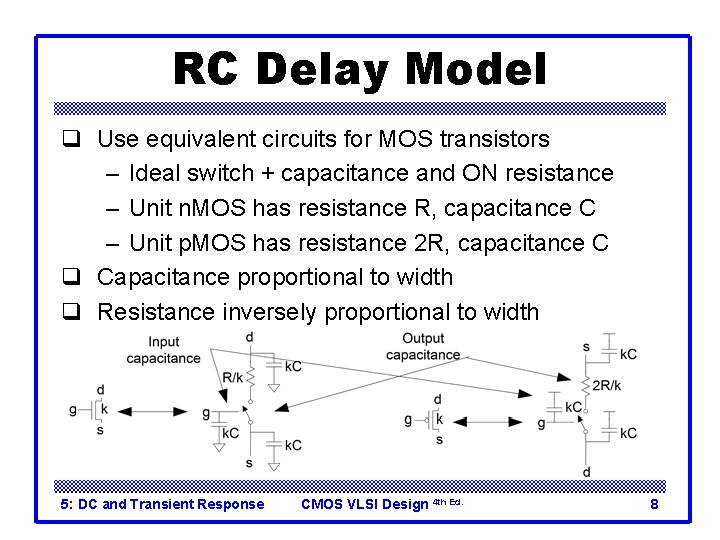

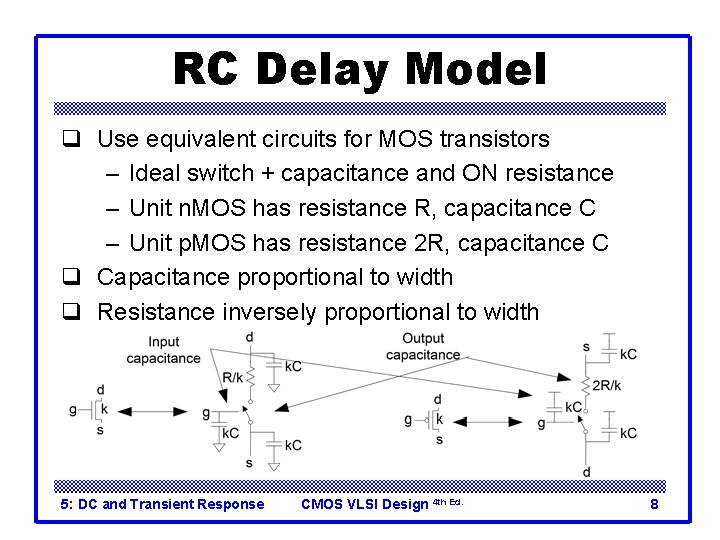

RC Delay Model q Use equivalent circuits for MOS transistors – Ideal switch + capacitance and ON resistance – Unit n. MOS has resistance R, capacitance C – Unit p. MOS has resistance 2 R, capacitance C q Capacitance proportional to width q Resistance inversely proportional to width 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 8

RC Values q Capacitance – C = Cg = Cs = Cd = 2 f. F/mm of gate width in 0. 6 mm – Gradually decline to 1 f. F/mm in nanometer techs. q Resistance – R 6 KW*mm in 0. 6 mm process – Improves with shorter channel lengths q Unit transistors – May refer to minimum contacted device (4/2 l) – Or maybe 1 mm wide device – Doesn’t matter as long as you are consistent 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 9

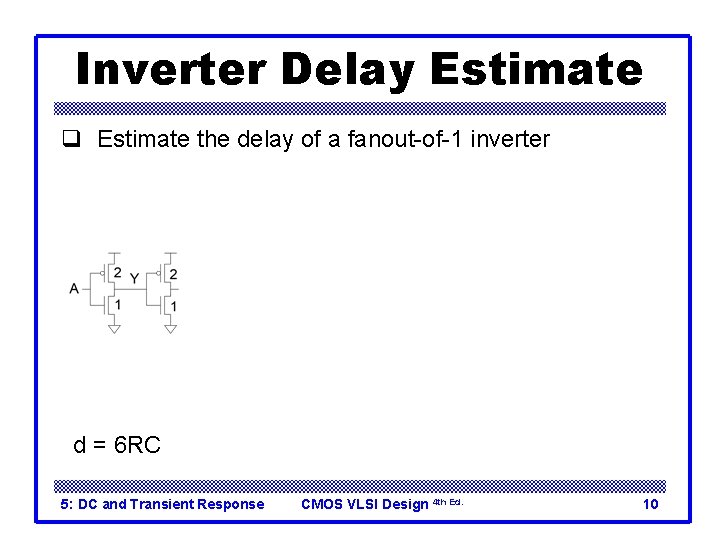

Inverter Delay Estimate q Estimate the delay of a fanout-of-1 inverter d = 6 RC 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 10

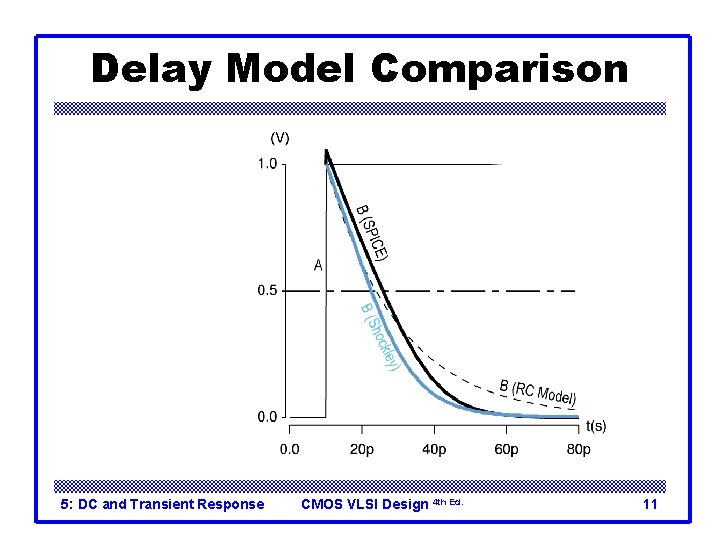

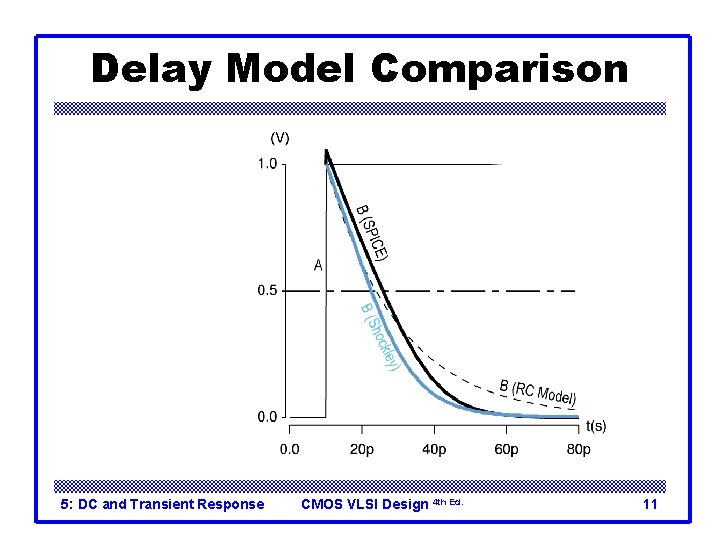

Delay Model Comparison 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 11

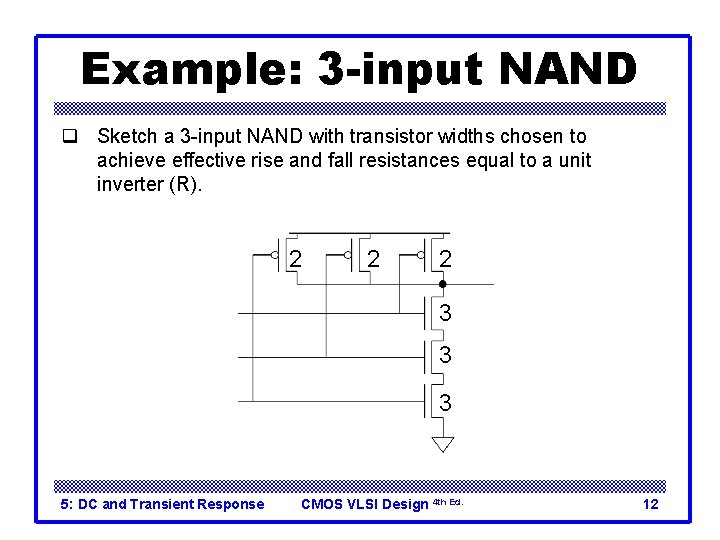

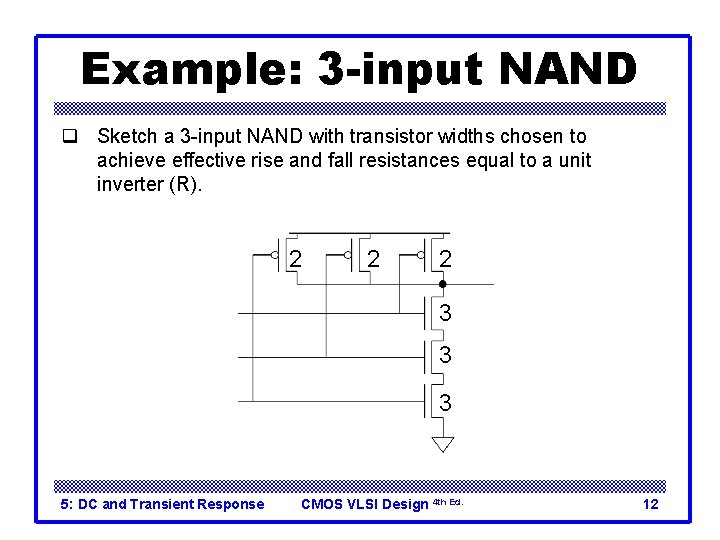

Example: 3 -input NAND q Sketch a 3 -input NAND with transistor widths chosen to achieve effective rise and fall resistances equal to a unit inverter (R). 2 2 2 3 3 3 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 12

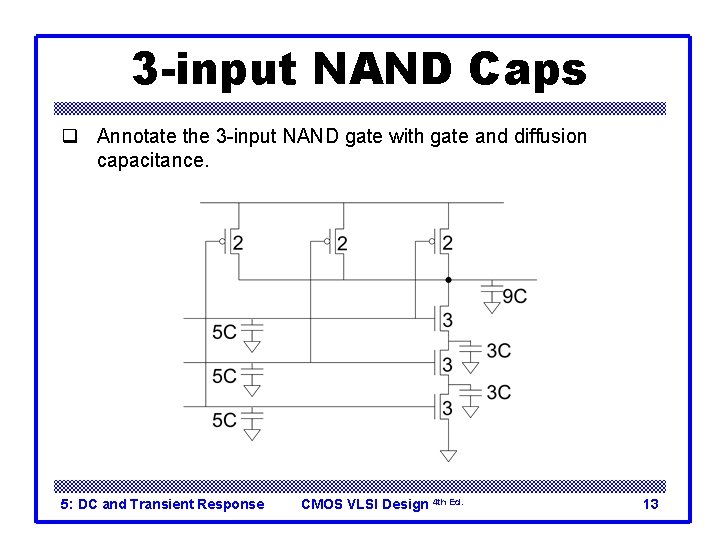

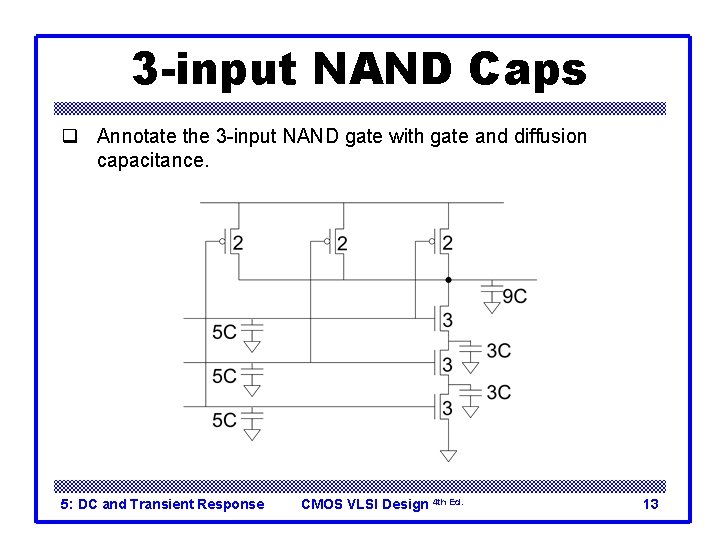

3 -input NAND Caps q Annotate the 3 -input NAND gate with gate and diffusion capacitance. 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 13

Example q Sketch a 2 -input NOR gate with selected transistor widths so that effective rise and fall resistances are equal to a unit inverter’s. Annotate the gate and diffusion capacitances. 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 14

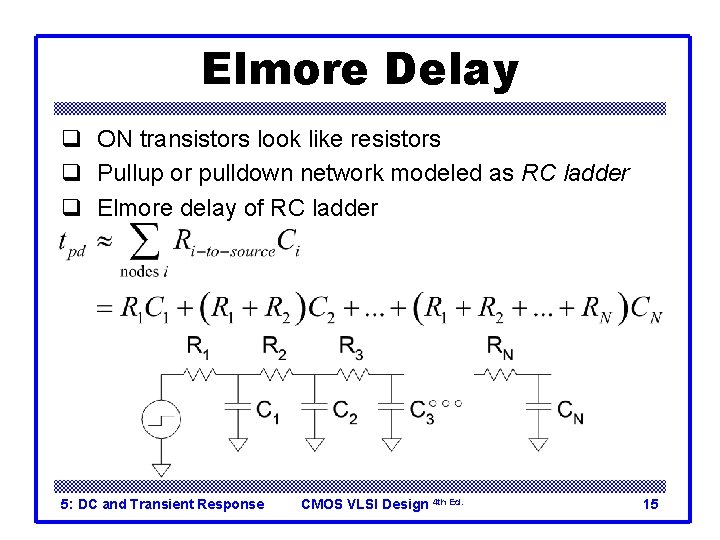

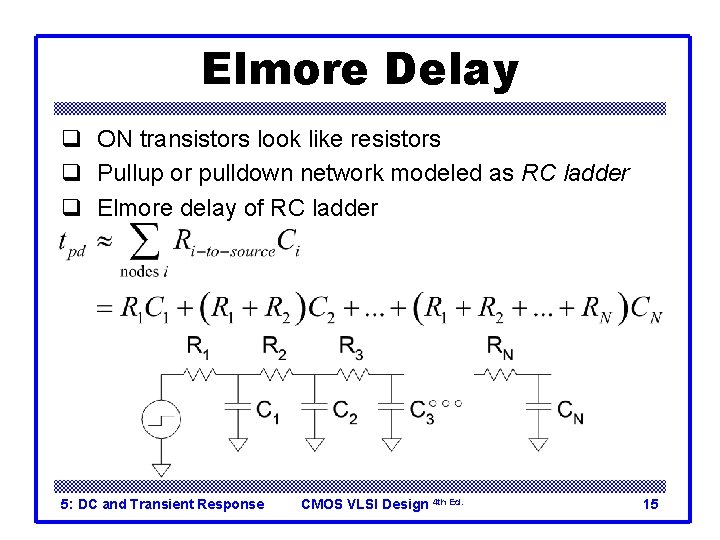

Elmore Delay q ON transistors look like resistors q Pullup or pulldown network modeled as RC ladder q Elmore delay of RC ladder 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 15

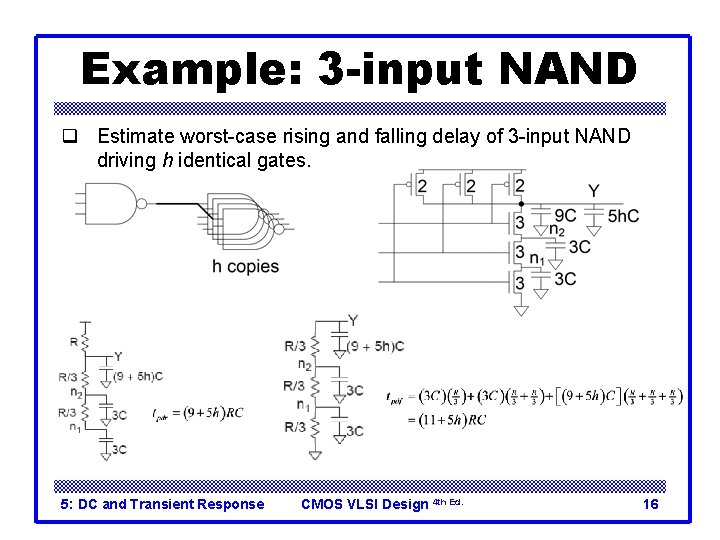

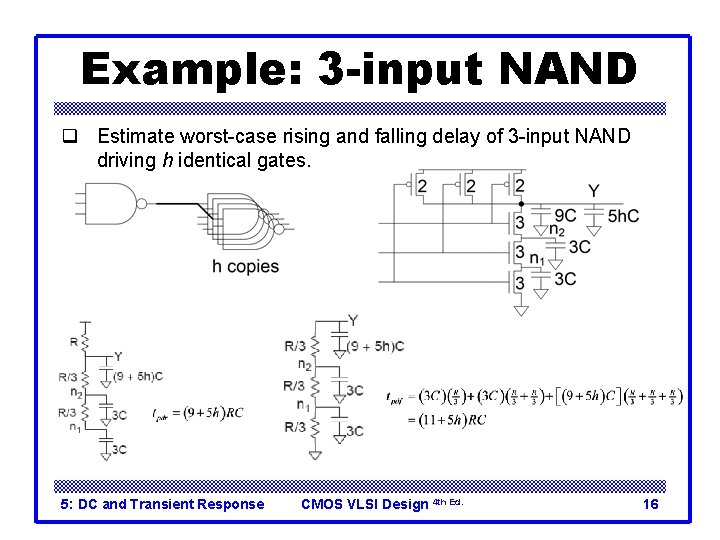

Example: 3 -input NAND q Estimate worst-case rising and falling delay of 3 -input NAND driving h identical gates. 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 16

Delay Components q Delay has two parts – Parasitic delay • 9 or 11 RC • Independent of load – Effort delay • 5 h RC • Proportional to load capacitance 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 17

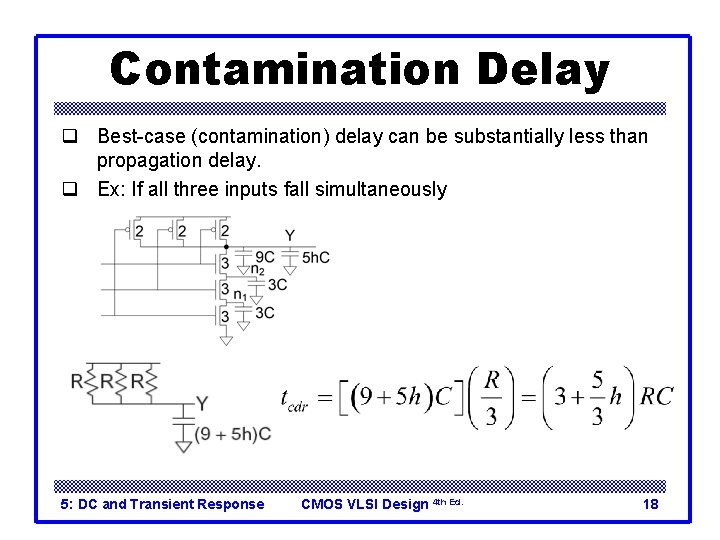

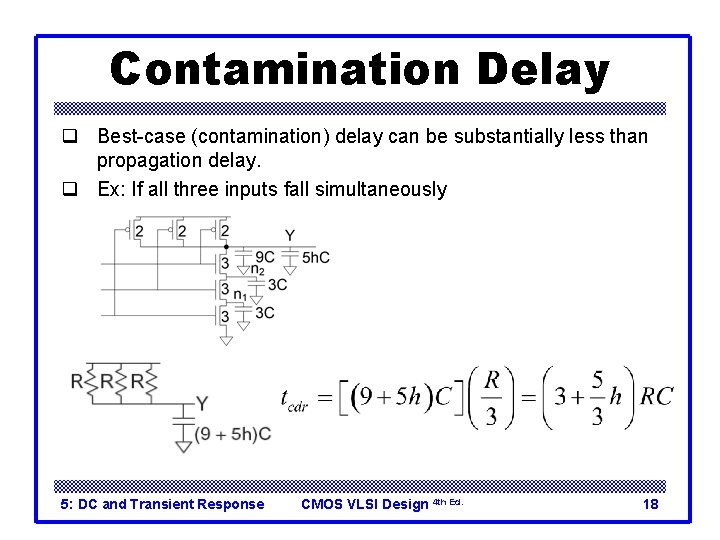

Contamination Delay q Best-case (contamination) delay can be substantially less than propagation delay. q Ex: If all three inputs fall simultaneously 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 18

Delay in a Logic Gate q Express delays in process-independent unit q Delay has two components: d = f + p t = 3 RC q f: effort delay = gh (a. k. a. stage effort) 3 ps in 65 nm process – Again has two components 60 ps in 0. 6 mm process q g: logical effort – Measures relative ability of gate to deliver current – g 1 for inverter q h: electrical effort = Cout / Cin – Ratio of output to input capacitance – Sometimes called fanout q p: parasitic delay – Represents delay of gate driving no load – Set by internal parasitic capacitance 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 19

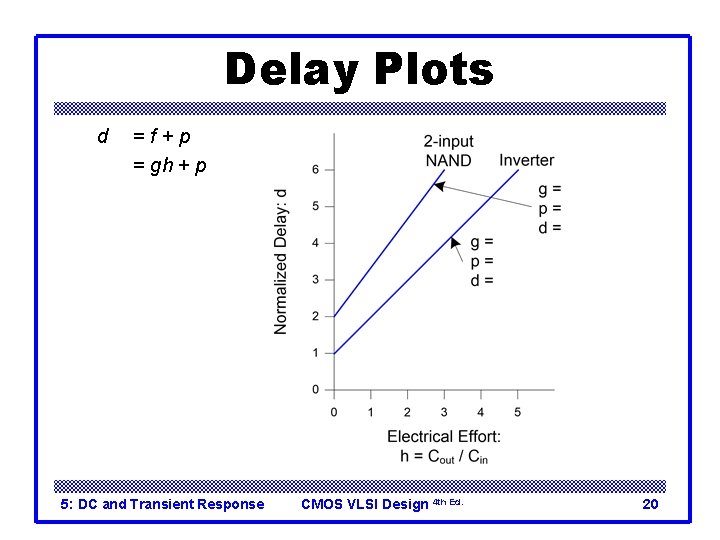

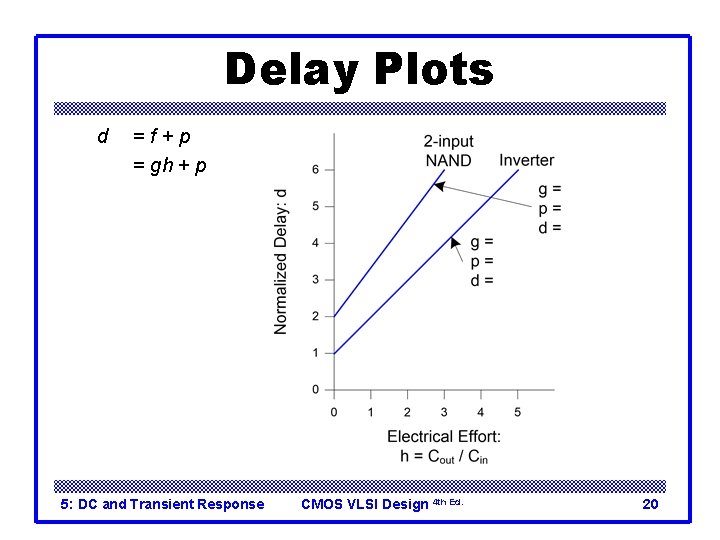

Delay Plots d =f+p = gh + p q What about NOR 2? 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 20

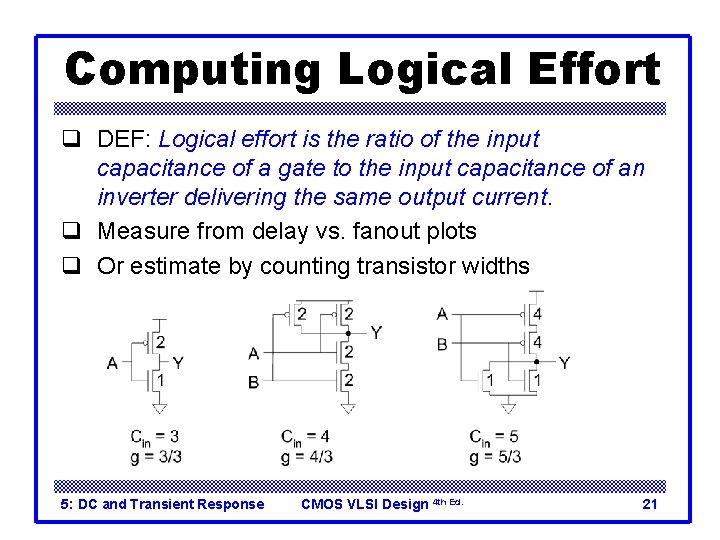

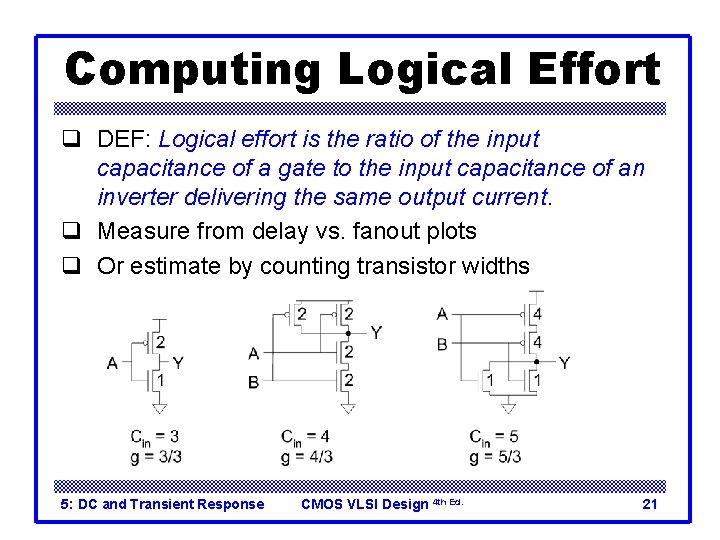

Computing Logical Effort q DEF: Logical effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current. q Measure from delay vs. fanout plots q Or estimate by counting transistor widths 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 21

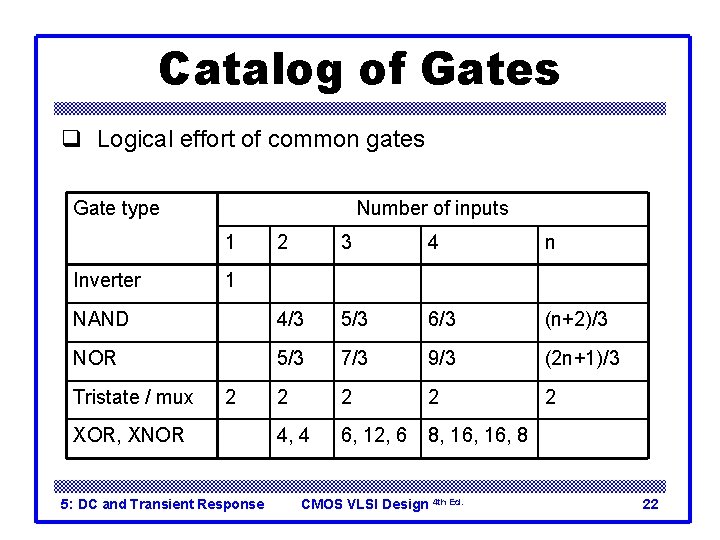

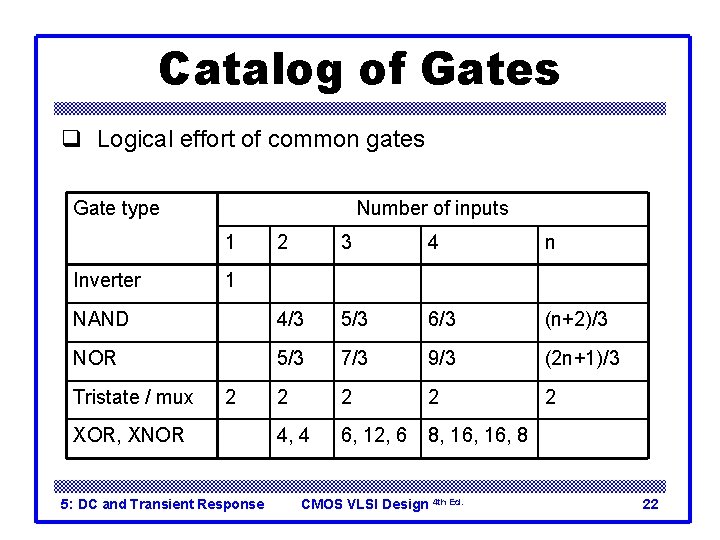

Catalog of Gates q Logical effort of common gates Gate type Number of inputs 1 2 3 4 n NAND 4/3 5/3 6/3 (n+2)/3 NOR 5/3 7/3 9/3 (2 n+1)/3 2 2 4, 4 6, 12, 6 8, 16, 8 Inverter Tristate / mux 1 2 XOR, XNOR 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 22

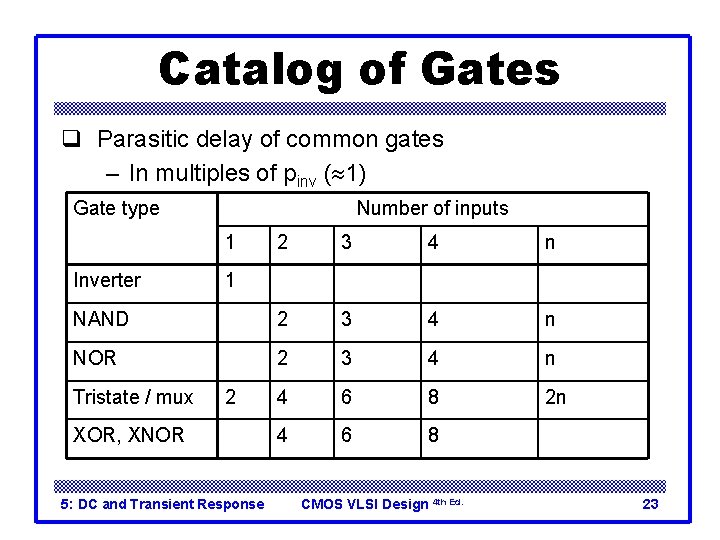

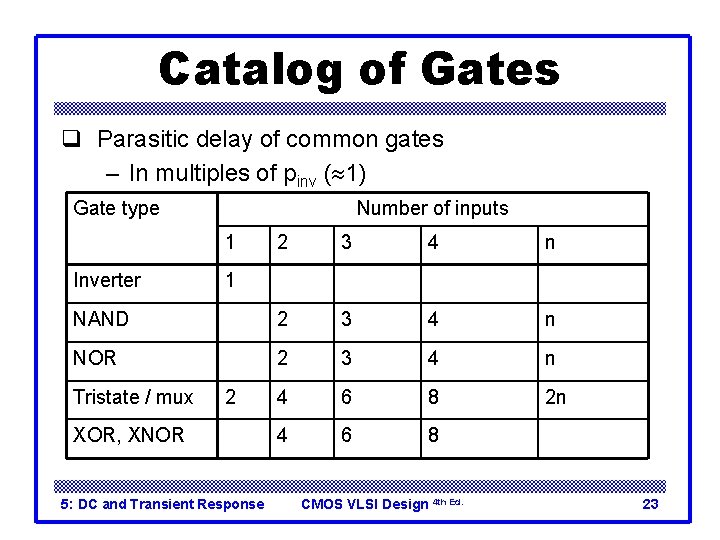

Catalog of Gates q Parasitic delay of common gates – In multiples of pinv ( 1) Gate type Number of inputs 1 2 3 4 n NAND 2 3 4 n NOR 2 3 4 n 4 6 8 2 n 4 6 8 Inverter Tristate / mux 1 2 XOR, XNOR 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 23

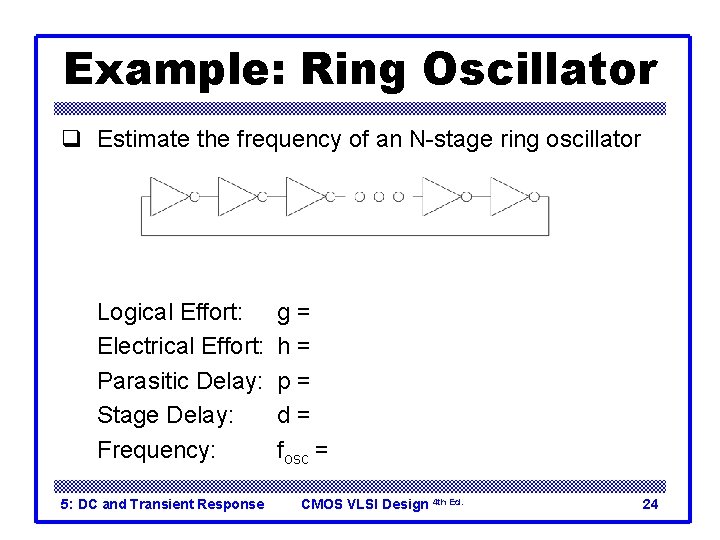

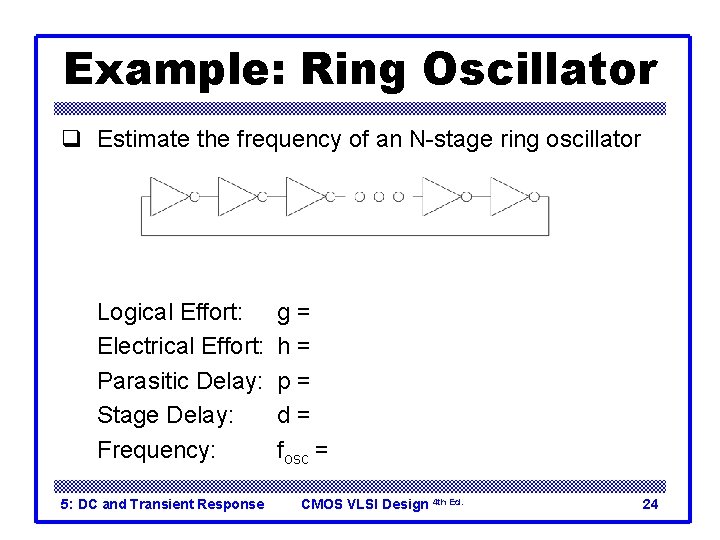

Example: Ring Oscillator q Estimate the frequency of an N-stage ring oscillator Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: Frequency: 5: DC and Transient Response 31 stage ring oscillator in g=1 0. 6 mm process has h=1 frequency of ~ 200 MHz p=1 d=2 fosc = 1/(2*N*d) = 1/4 N CMOS VLSI Design 4 th Ed. 24

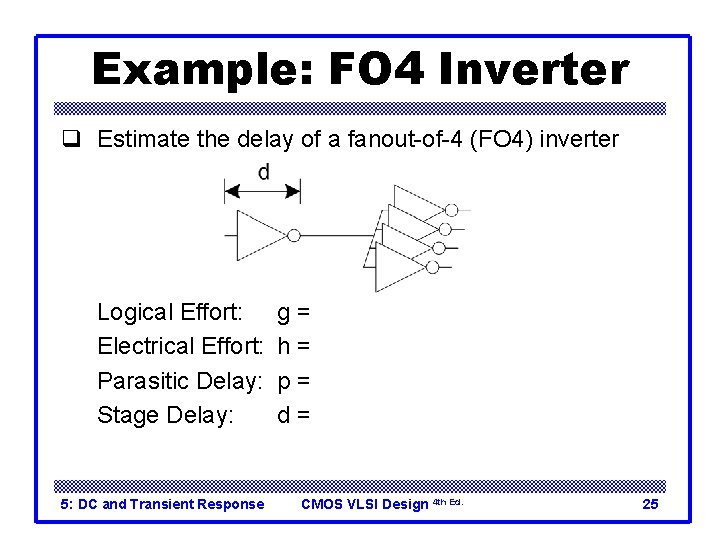

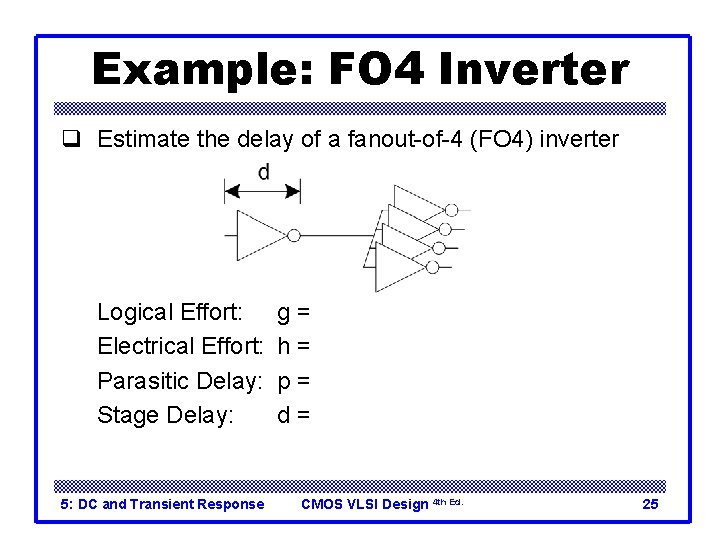

Example: FO 4 Inverter q Estimate the delay of a fanout-of-4 (FO 4) inverter Logical Effort: Electrical Effort: Parasitic Delay: Stage Delay: 5: DC and Transient Response g=1 h=4 p=1 d=5 The FO 4 delay is about 300 ps in 0. 6 mm process 15 ps in a 65 nm process CMOS VLSI Design 4 th Ed. 25

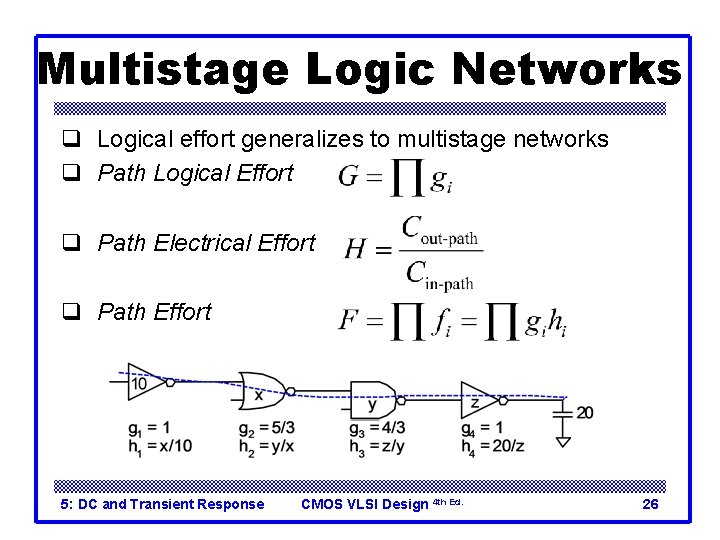

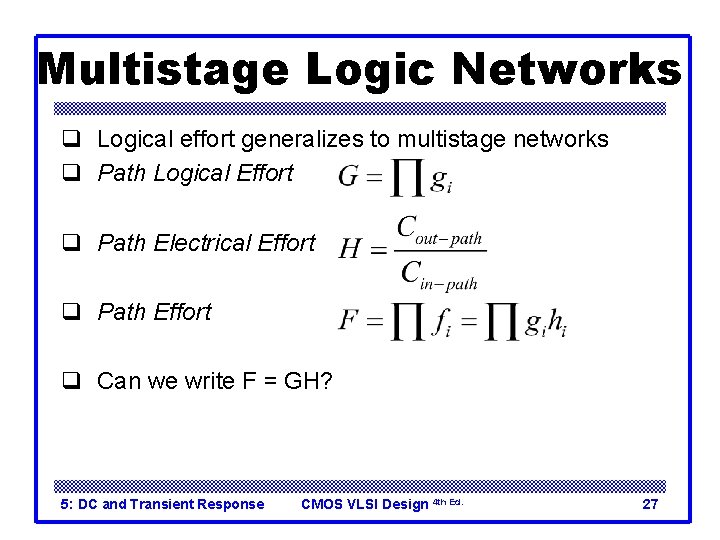

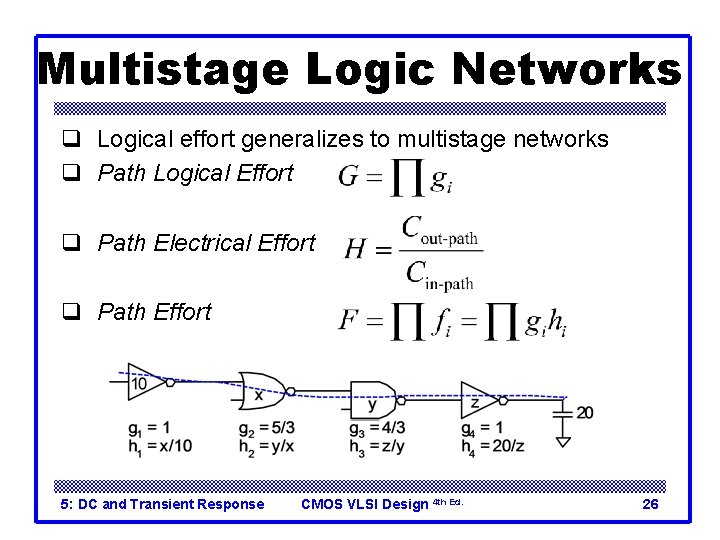

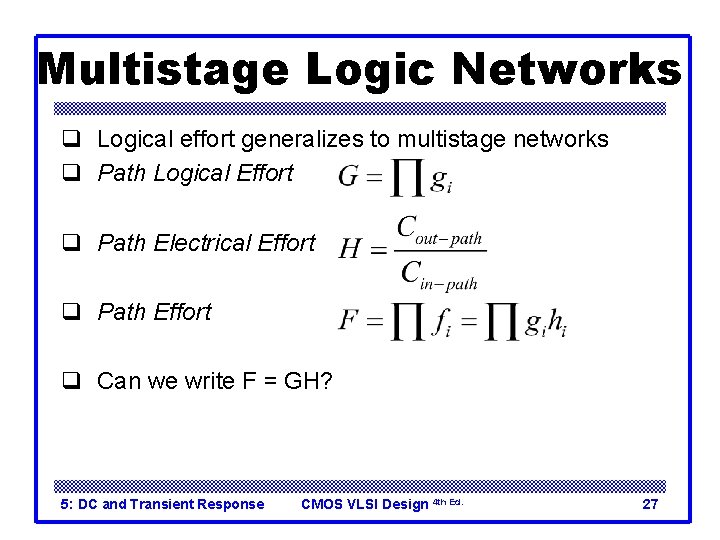

Multistage Logic Networks q Logical effort generalizes to multistage networks q Path Logical Effort q Path Electrical Effort q Path Effort 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 26

Multistage Logic Networks q Logical effort generalizes to multistage networks q Path Logical Effort q Path Electrical Effort q Path Effort q Can we write F = GH? 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 27

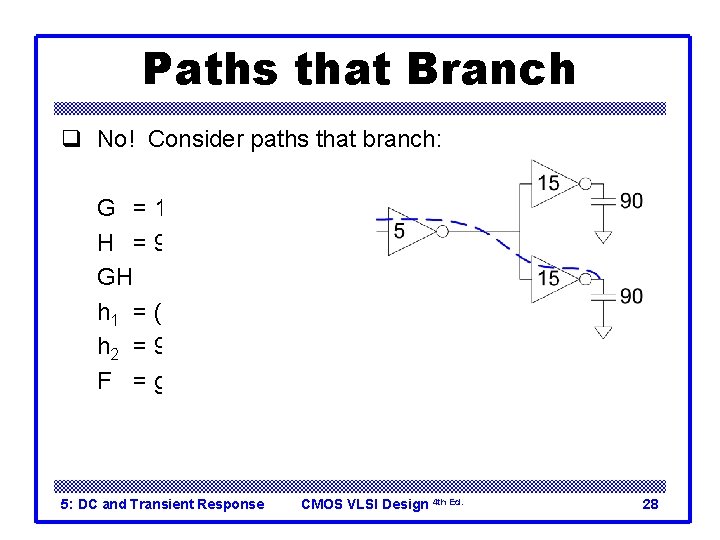

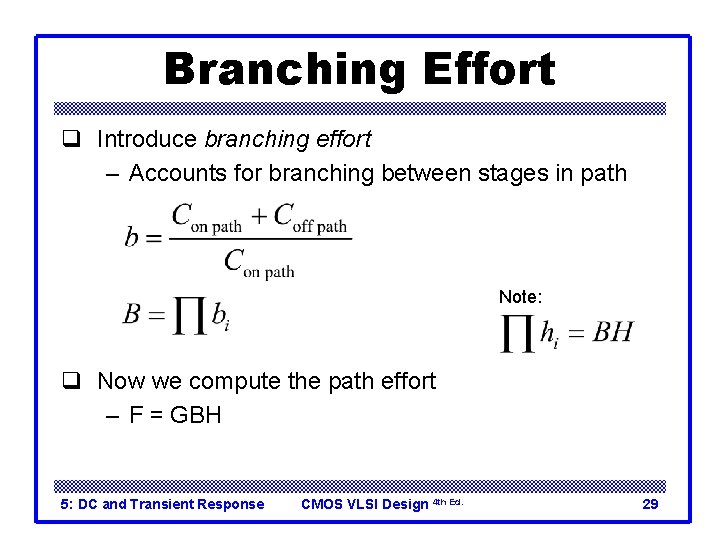

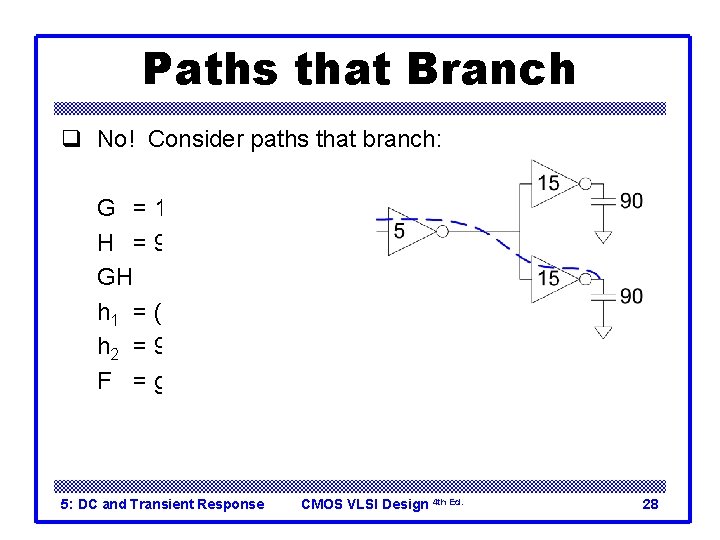

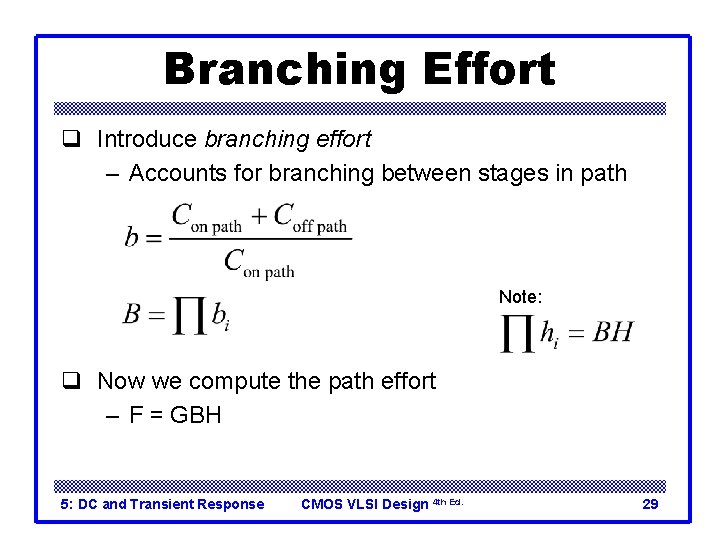

Paths that Branch q No! Consider paths that branch: G =1 H = 90 / 5 = 18 GH = 18 h 1 = (15 +15) / 5 = 6 h 2 = 90 / 15 = 6 F = g 1 g 2 h 1 h 2 = 36 = 2 GH 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 28

Branching Effort q Introduce branching effort – Accounts for branching between stages in path Note: q Now we compute the path effort – F = GBH 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 29

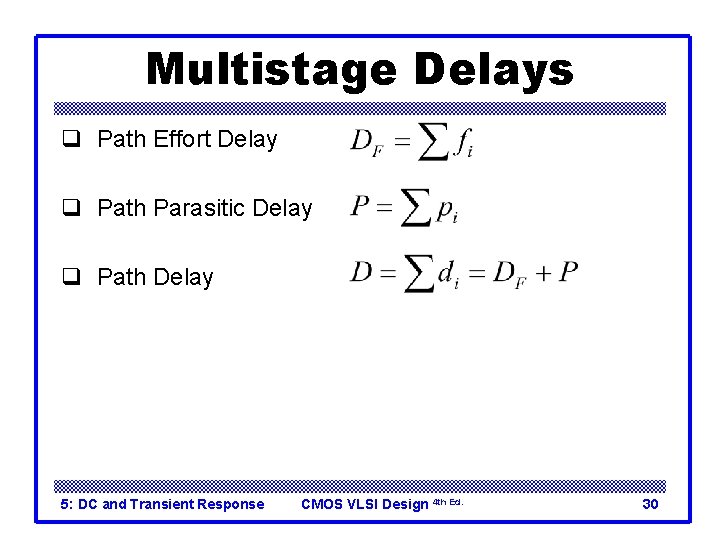

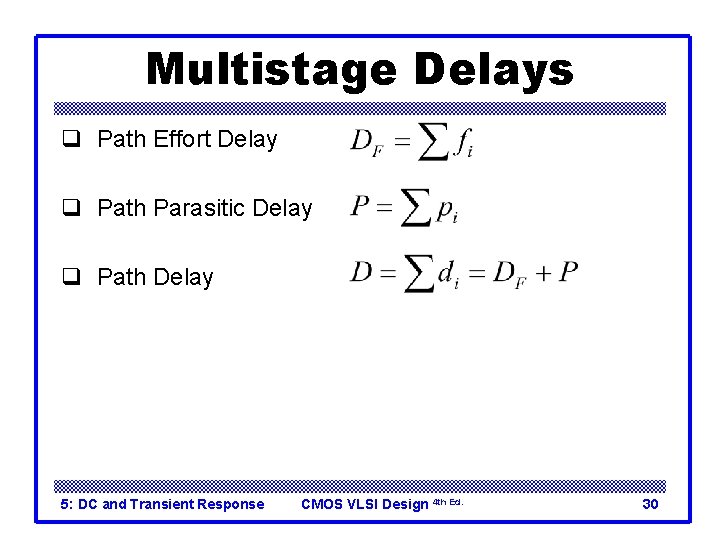

Multistage Delays q Path Effort Delay q Path Parasitic Delay q Path Delay 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 30

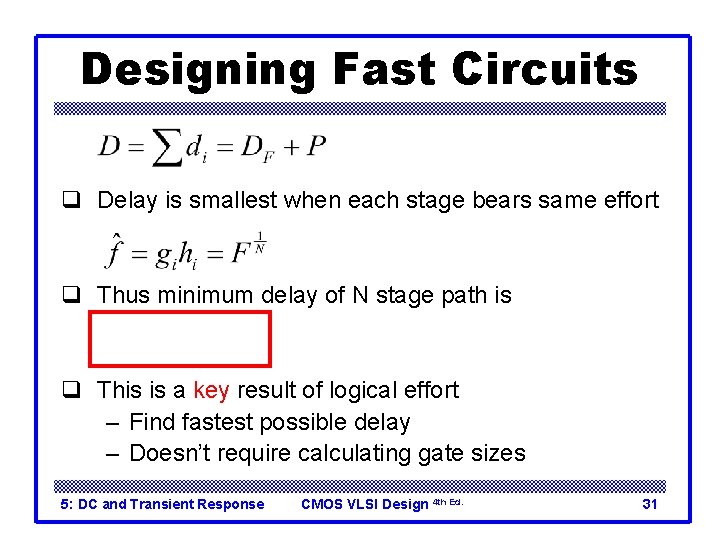

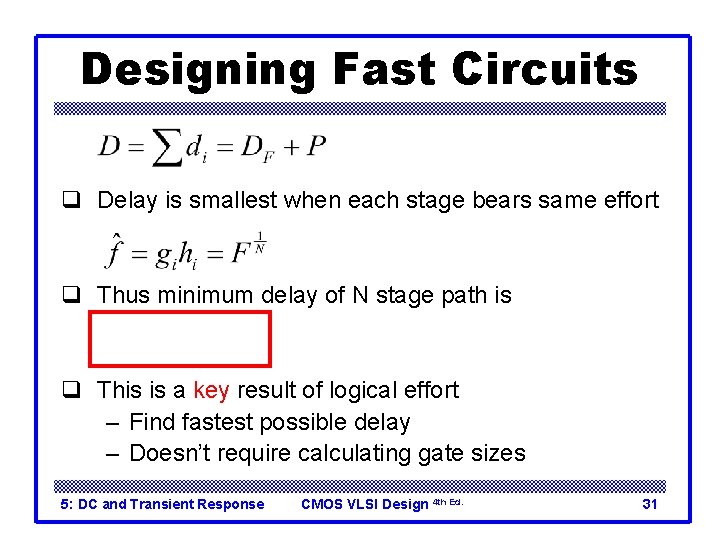

Designing Fast Circuits q Delay is smallest when each stage bears same effort q Thus minimum delay of N stage path is q This is a key result of logical effort – Find fastest possible delay – Doesn’t require calculating gate sizes 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 31

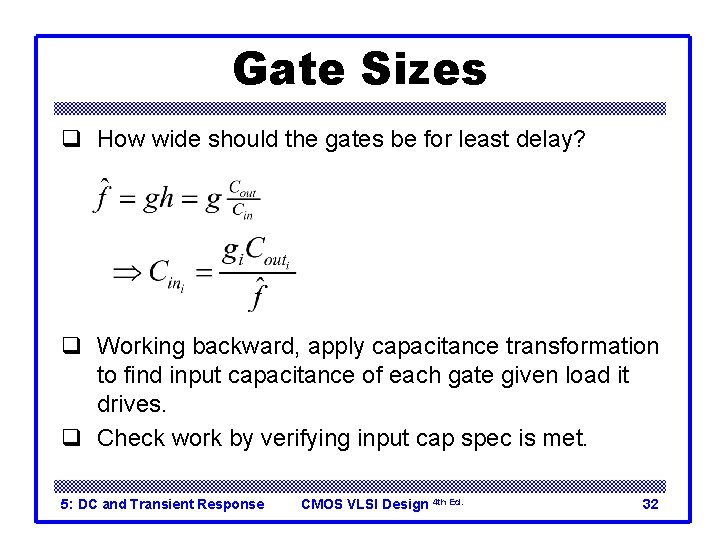

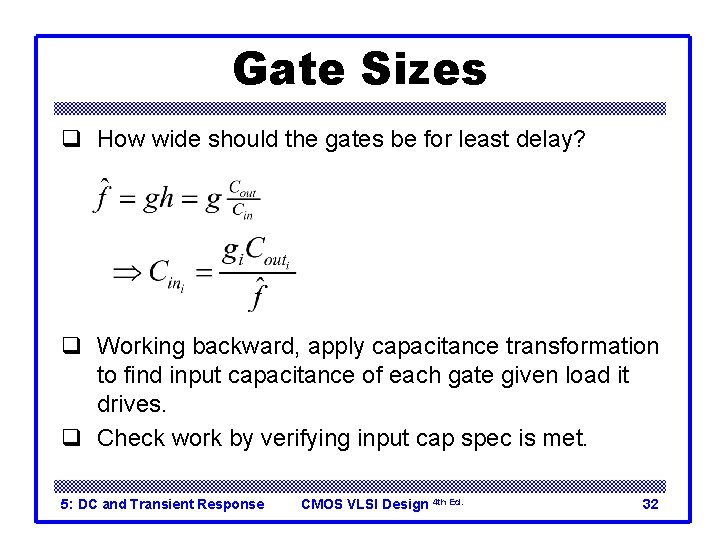

Gate Sizes q How wide should the gates be for least delay? q Working backward, apply capacitance transformation to find input capacitance of each gate given load it drives. q Check work by verifying input cap spec is met. 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 32

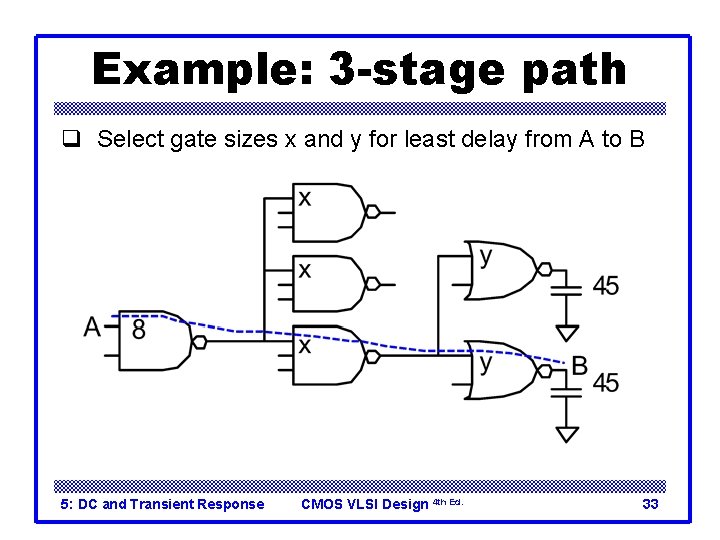

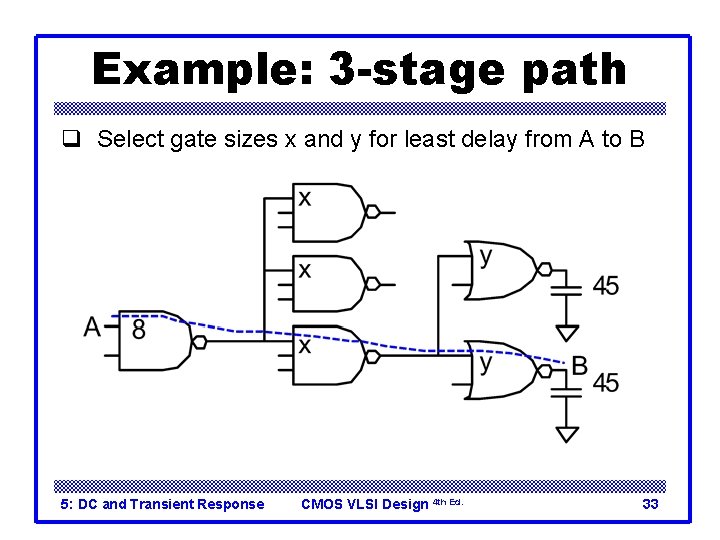

Example: 3 -stage path q Select gate sizes x and y for least delay from A to B 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 33

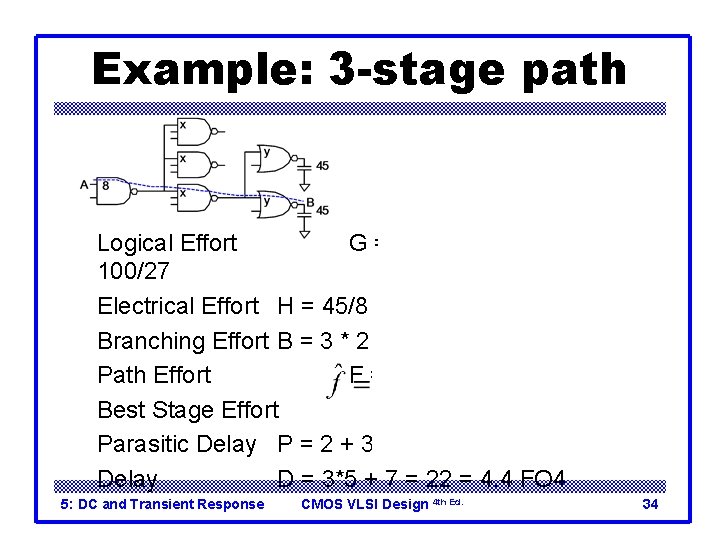

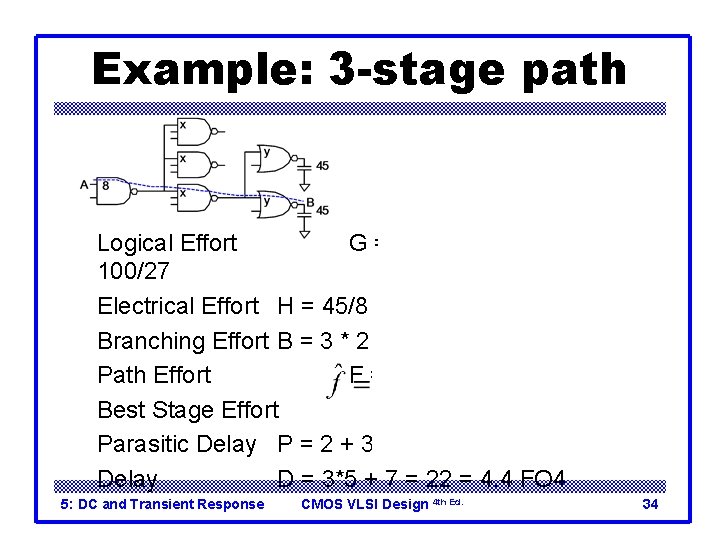

Example: 3 -stage path Logical Effort G = (4/3)*(5/3) = 100/27 Electrical Effort H = 45/8 Branching Effort B = 3 * 2 = 6 Path Effort F = GBH = 125 Best Stage Effort Parasitic Delay P = 2 + 3 + 2 = 7 Delay D = 3*5 + 7 = 22 = 4. 4 FO 4 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 34

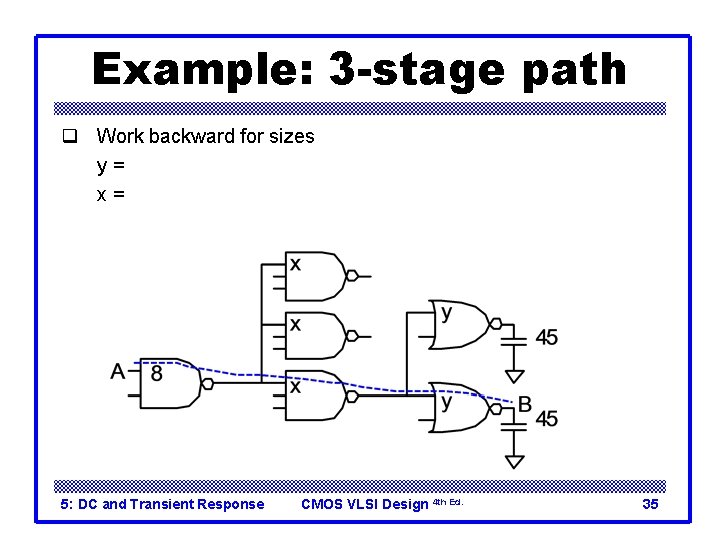

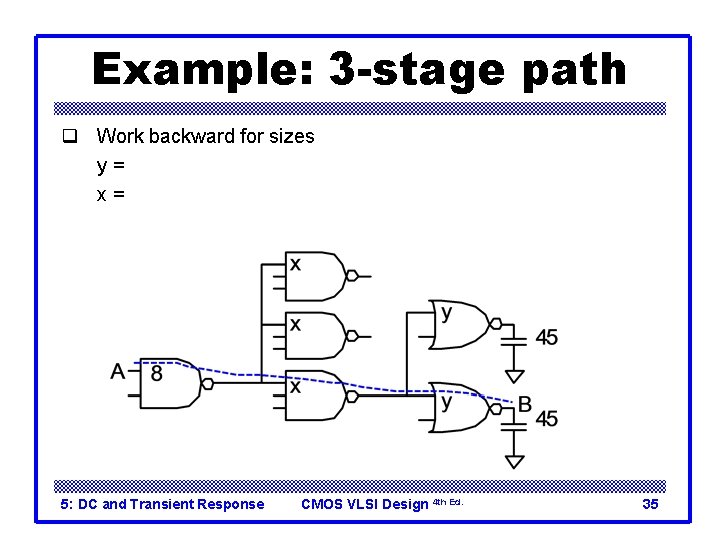

Example: 3 -stage path q Work backward for sizes y = 45 * (5/3) / 5 = 15 x = (15*2) * (5/3) / 5 = 10 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 35

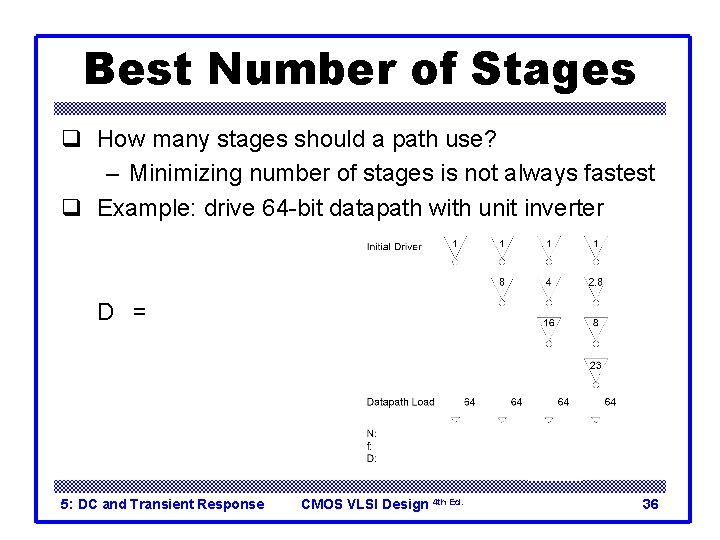

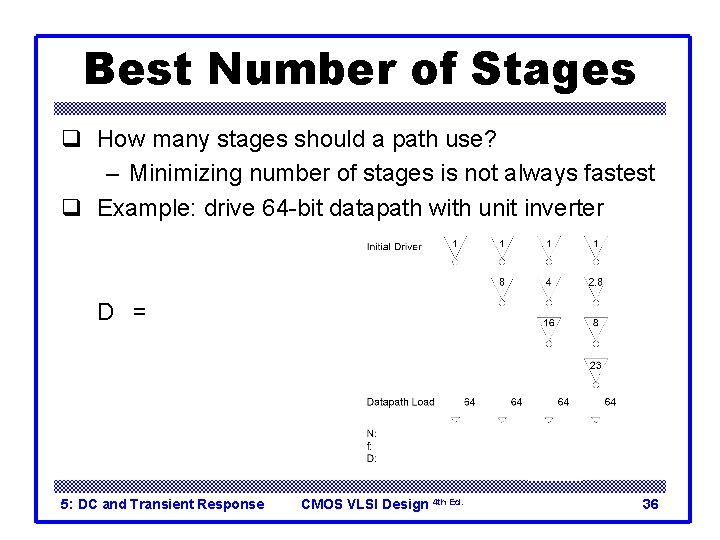

Best Number of Stages q How many stages should a path use? – Minimizing number of stages is not always fastest q Example: drive 64 -bit datapath with unit inverter D = NF 1/N + P = N(64)1/N + N 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 36

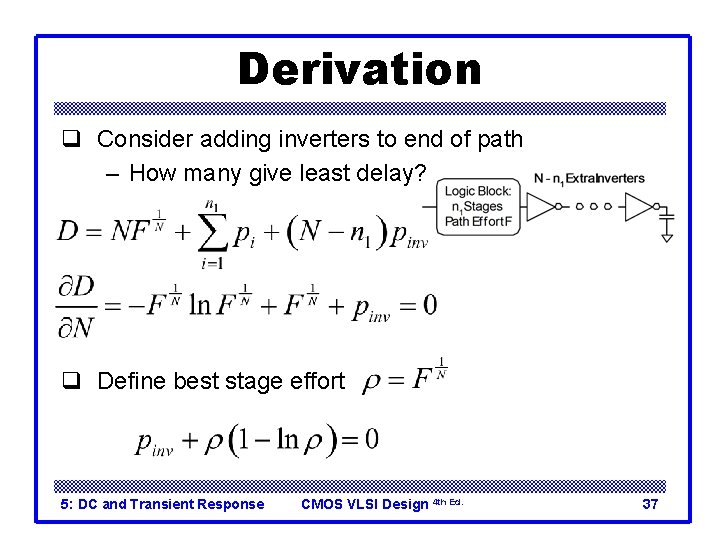

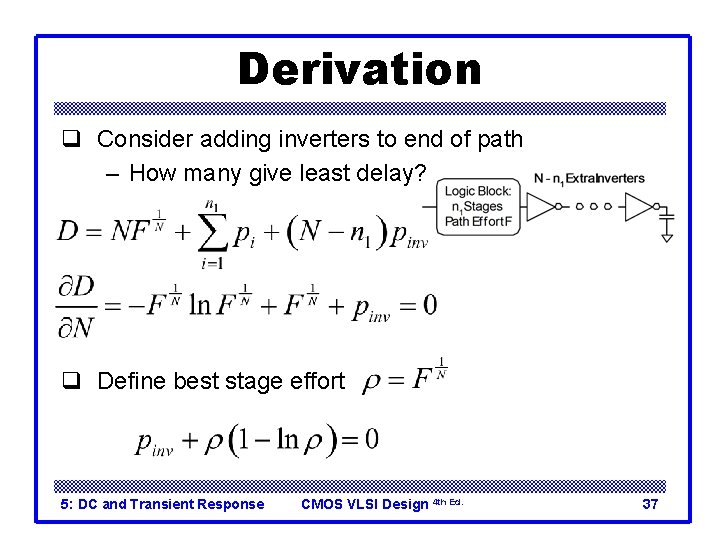

Derivation q Consider adding inverters to end of path – How many give least delay? q Define best stage effort 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 37

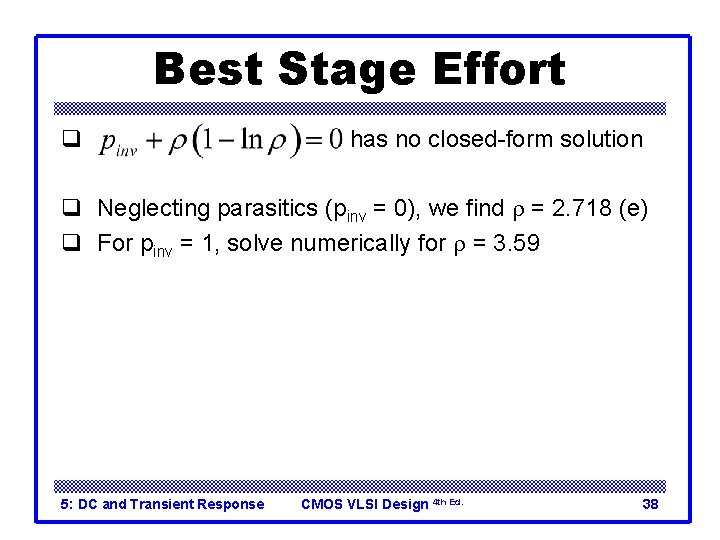

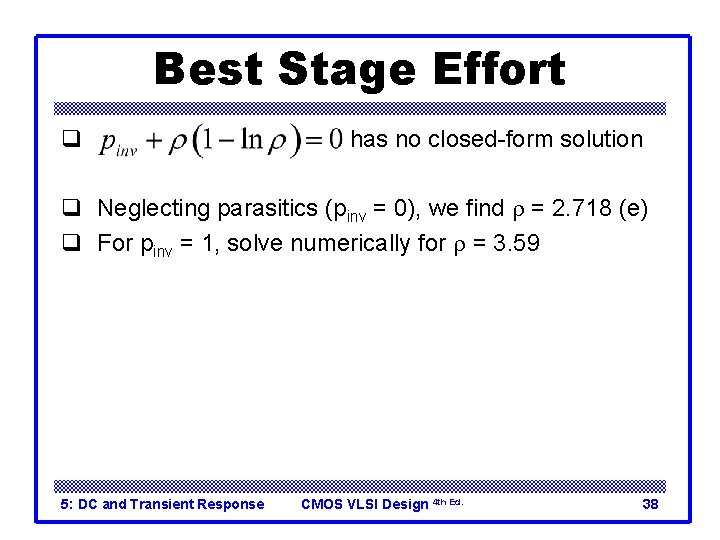

Best Stage Effort q has no closed-form solution q Neglecting parasitics (pinv = 0), we find r = 2. 718 (e) q For pinv = 1, solve numerically for r = 3. 59 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 38

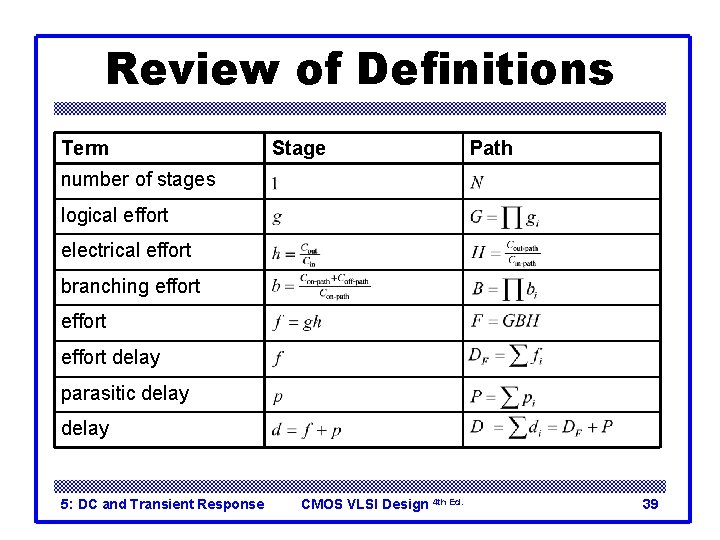

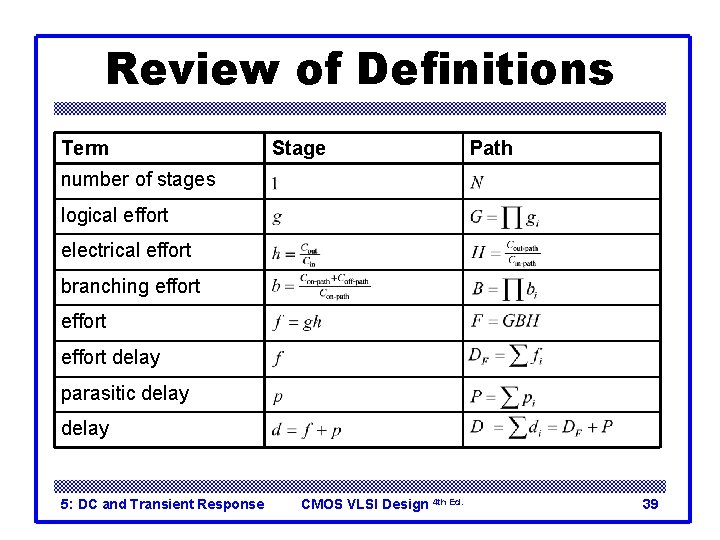

Review of Definitions Term Stage Path number of stages logical effort electrical effort branching effort delay parasitic delay 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 39

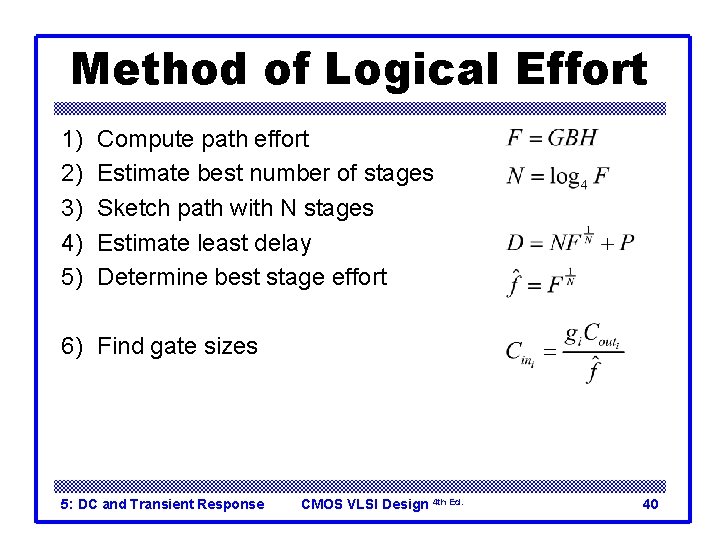

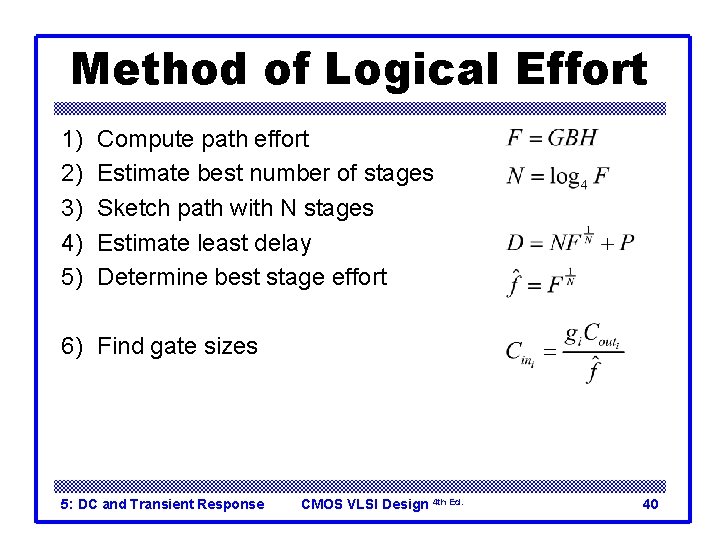

Method of Logical Effort 1) 2) 3) 4) 5) Compute path effort Estimate best number of stages Sketch path with N stages Estimate least delay Determine best stage effort 6) Find gate sizes 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 40

Limits of Logical Effort q Chicken and egg problem – Need path to compute G – But don’t know number of stages without G q Simplistic delay model – Neglects input rise time effects q Interconnect – Iteration required in designs with wire q Maximum speed only – Not minimum area/power for constrained delay 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 41

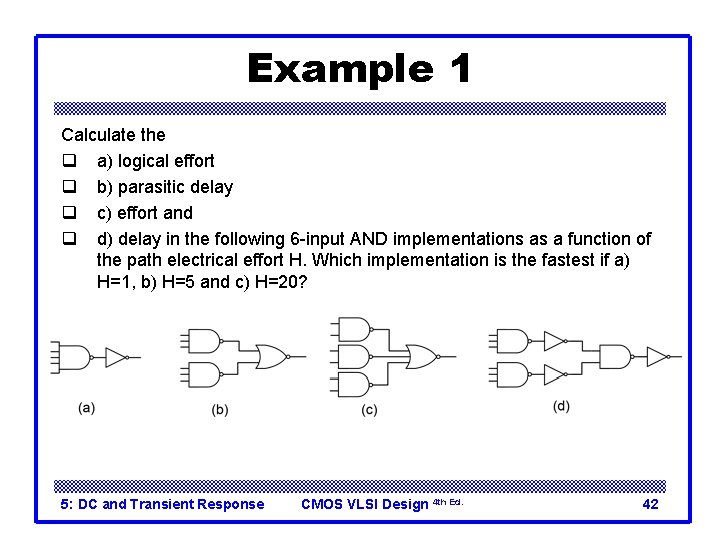

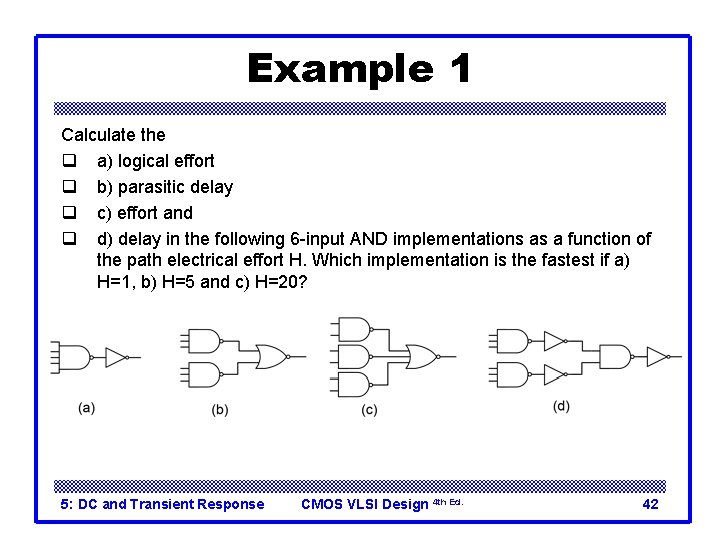

Example 1 Calculate the q a) logical effort q b) parasitic delay q c) effort and q d) delay in the following 6 -input AND implementations as a function of the path electrical effort H. Which implementation is the fastest if a) H=1, b) H=5 and c) H=20? 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 42

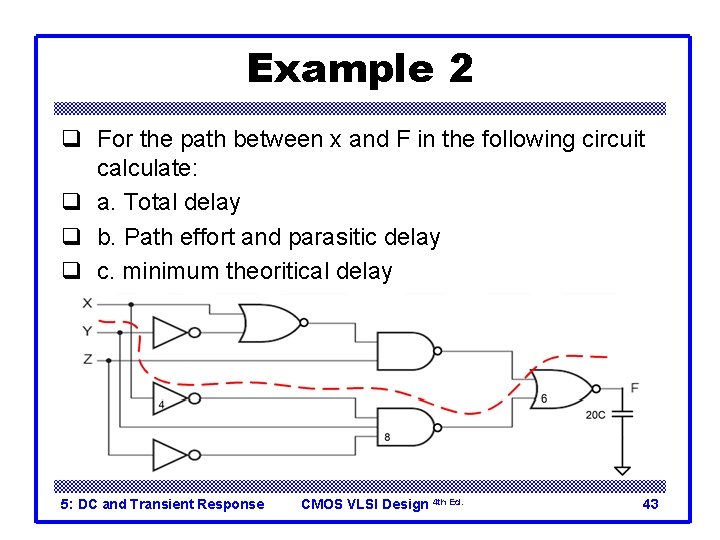

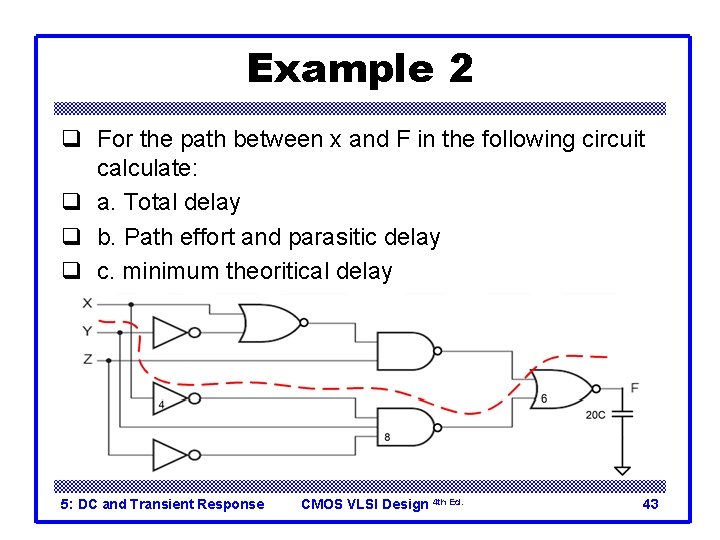

Example 2 q For the path between x and F in the following circuit calculate: q a. Total delay q b. Path effort and parasitic delay q c. minimum theoritical delay 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 43

Summary q Logical effort is useful for thinking of delay in circuits – Numeric logical effort characterizes gates – NANDs are faster than NORs in CMOS – Paths are fastest when effort delays are ~4 – Path delay is weakly sensitive to stages, sizes – But using fewer stages doesn’t mean faster paths – Delay of path is about log 4 F FO 4 inverter delays – Inverters and NAND 2 best for driving large caps q Provides language for discussing fast circuits – But requires practice to master 5: DC and Transient Response CMOS VLSI Design 4 th Ed. 44