5 8 GHz CMOS A low voltage high

- Slides: 28

應用於 5. 8 GHz頻段之低電壓, 高線性度CMOS降頻混頻器 A low voltage, high linearity CMOS downconversion mixer for 5. 8 GHz application Process: U 18 -95 A FTP No. : 24 Date: 2006/02/18

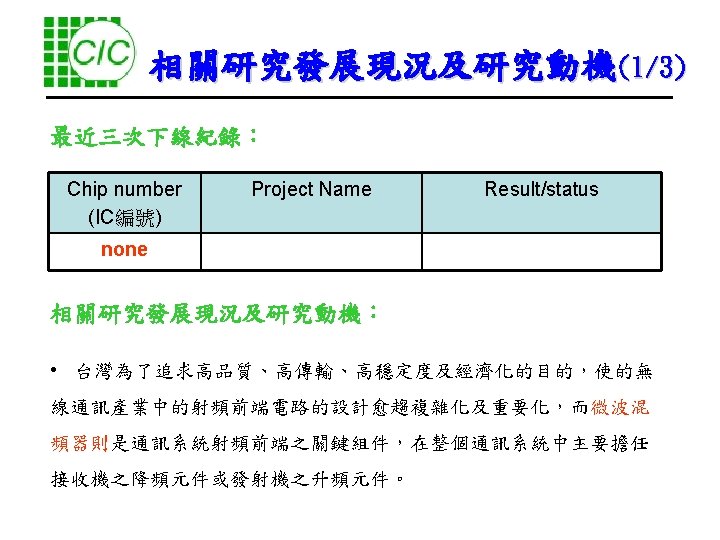

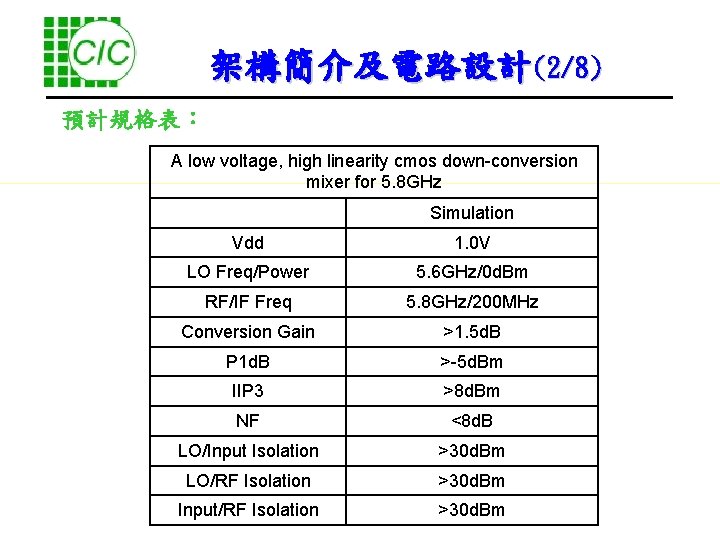

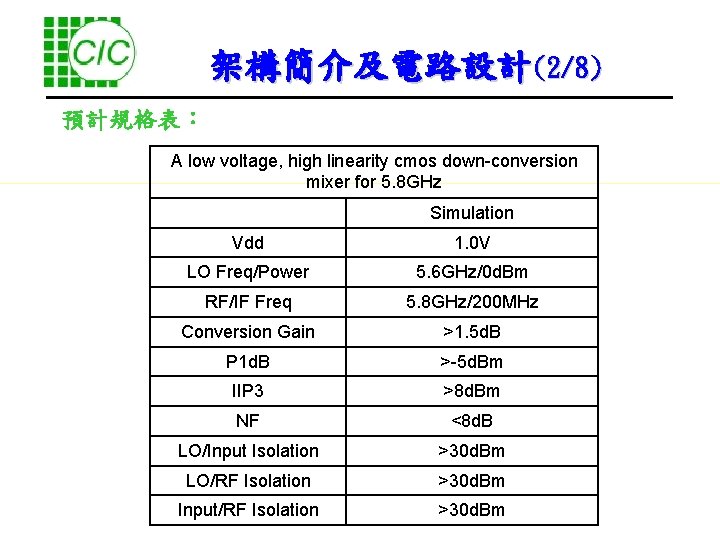

架構簡介及電路設計(2/8) 預計規格表: A low voltage, high linearity cmos down-conversion mixer for 5. 8 GHz Simulation Vdd 1. 0 V LO Freq/Power 5. 6 GHz/0 d. Bm RF/IF Freq 5. 8 GHz/200 MHz Conversion Gain >1. 5 d. B P 1 d. B >-5 d. Bm IIP 3 >8 d. Bm NF <8 d. B LO/Input Isolation >30 d. Bm LO/RF Isolation >30 d. Bm Input/RF Isolation >30 d. Bm

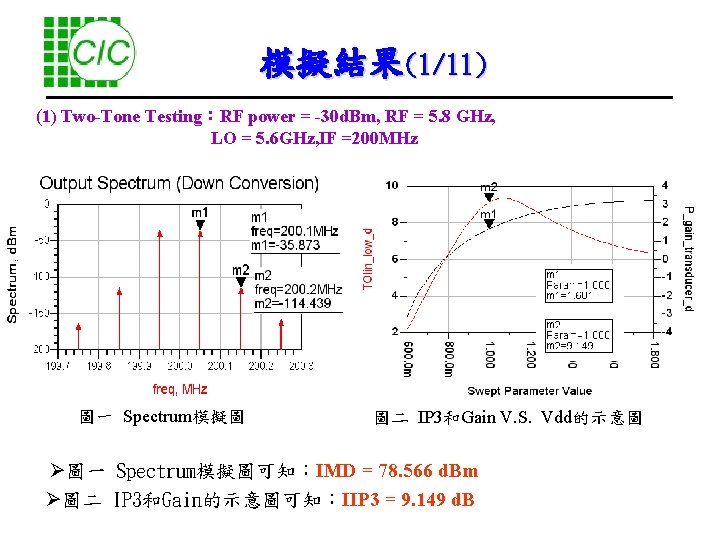

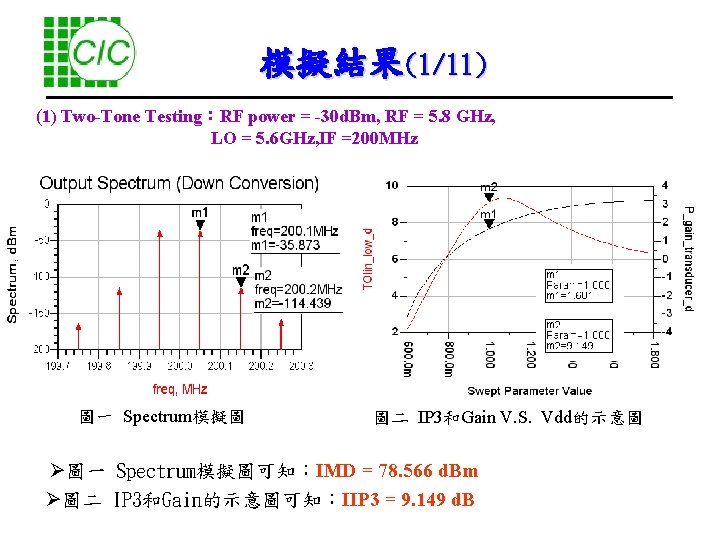

模擬結果(1/11) (1) Two-Tone Testing:RF power = -30 d. Bm, RF = 5. 8 GHz, LO = 5. 6 GHz, IF =200 MHz 圖一 Spectrum模擬圖 圖二 IP 3和Gain V. S. Vdd的示意圖 圖一 Spectrum模擬圖可知:IMD = 78. 566 d. Bm 圖二 IP 3和Gain的示意圖可知:IIP 3 = 9. 149 d. B

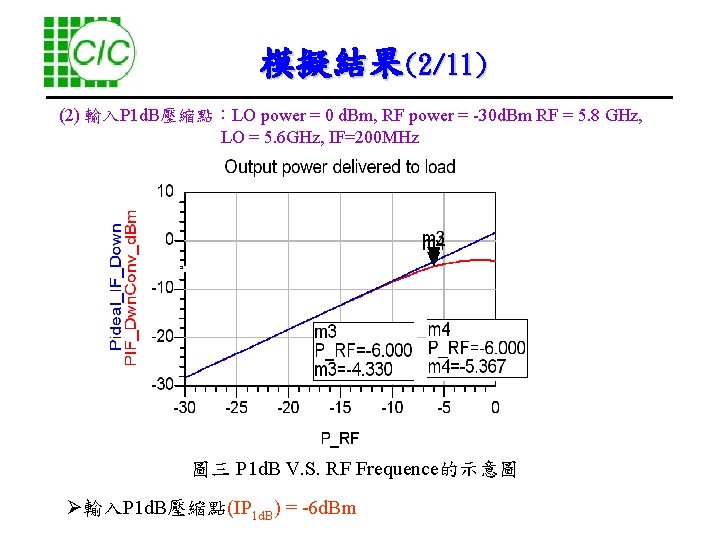

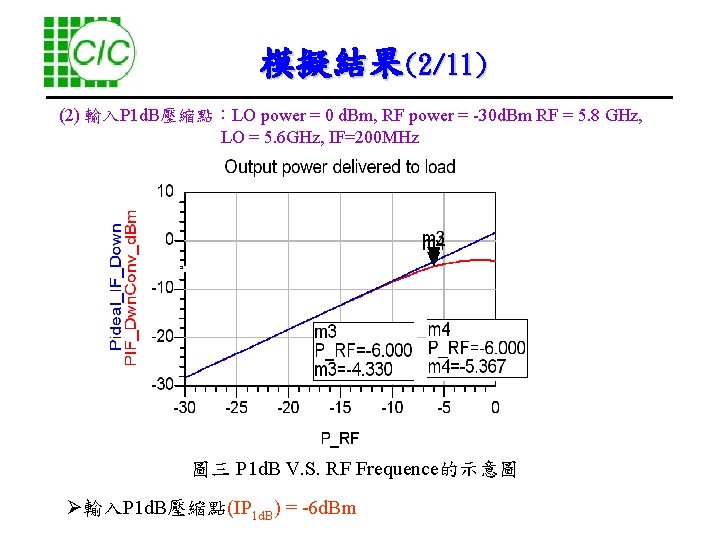

模擬結果(2/11) (2) 輸入P 1 d. B壓縮點:LO power = 0 d. Bm, RF power = -30 d. Bm RF = 5. 8 GHz, LO = 5. 6 GHz, IF=200 MHz 圖三 P 1 d. B V. S. RF Frequence的示意圖 輸入P 1 d. B壓縮點(IP 1 d. B) = -6 d. Bm

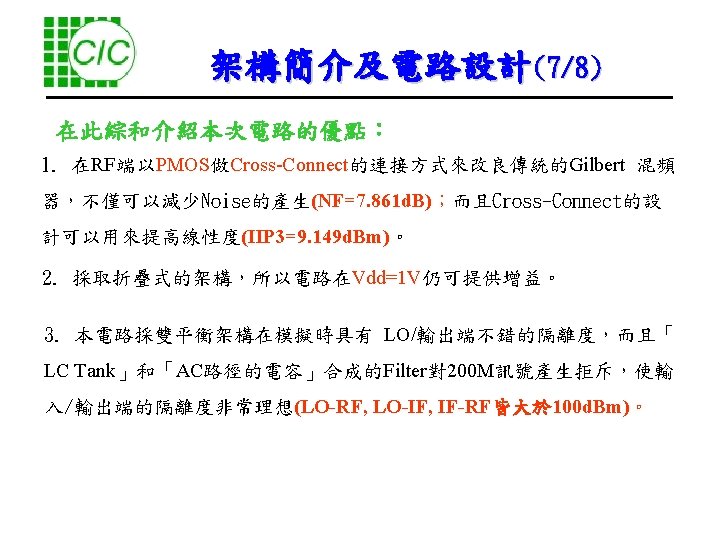

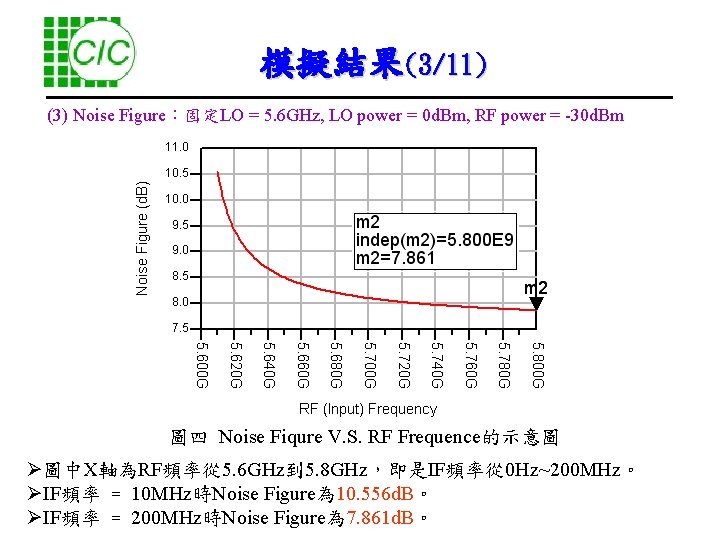

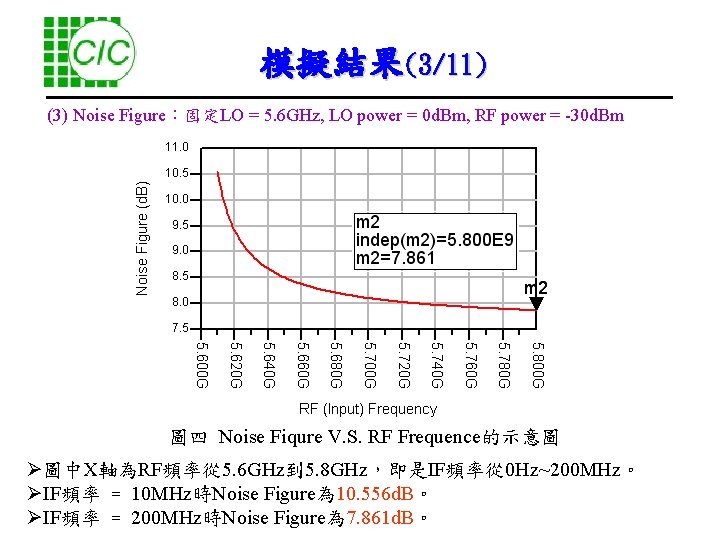

模擬結果(3/11) (3) Noise Figure:固定LO = 5. 6 GHz, LO power = 0 d. Bm, RF power = -30 d. Bm 圖四 Noise Fiqure V. S. RF Frequence的示意圖 圖中X軸為RF頻率從 5. 6 GHz到 5. 8 GHz,即是IF頻率從 0 Hz~200 MHz。 IF頻率 = 10 MHz時Noise Figure為 10. 556 d. B。 IF頻率 = 200 MHz時Noise Figure為 7. 861 d. B。

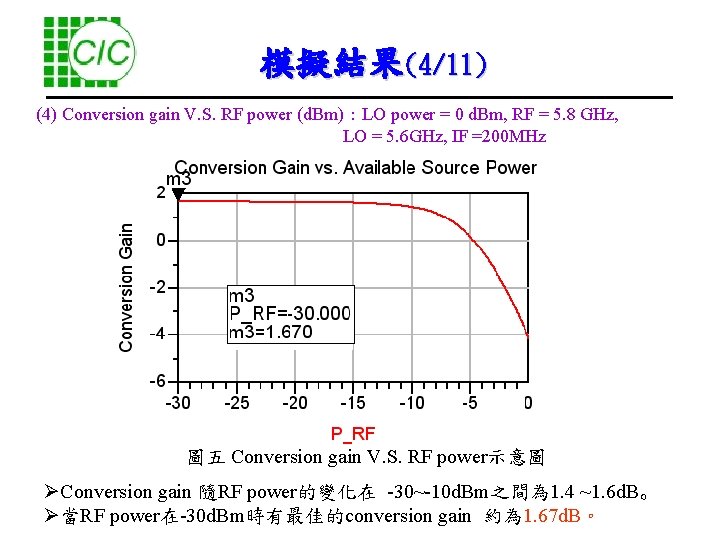

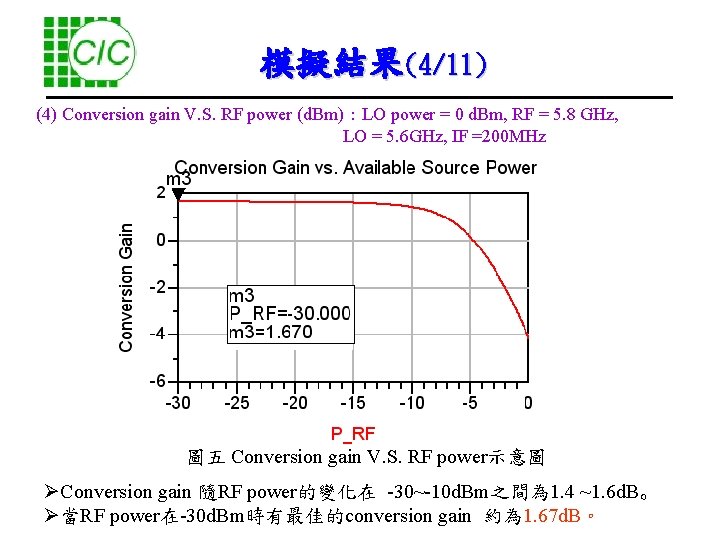

模擬結果(4/11) (4) Conversion gain V. S. RF power (d. Bm):LO power = 0 d. Bm, RF = 5. 8 GHz, LO = 5. 6 GHz, IF =200 MHz 圖五 Conversion gain V. S. RF power示意圖 Conversion gain 隨RF power的變化在 -30~-10 d. Bm之間為 1. 4 ~1. 6 d. B。 當RF power在-30 d. Bm時有最佳的conversion gain 約為 1. 67 d. B。

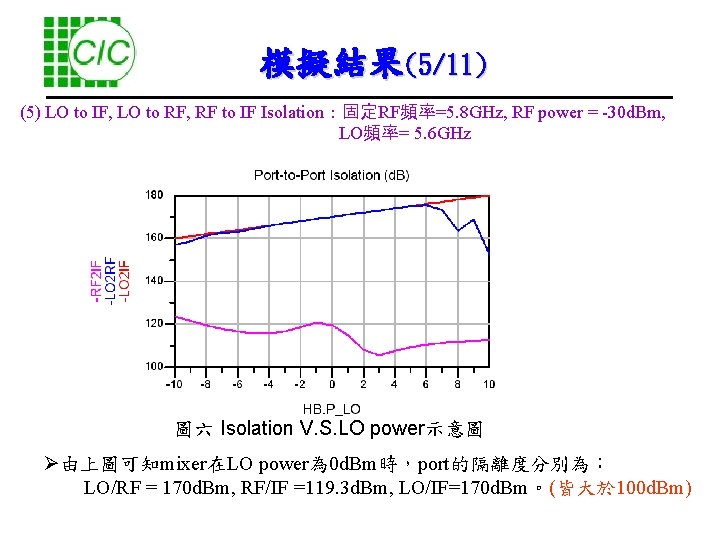

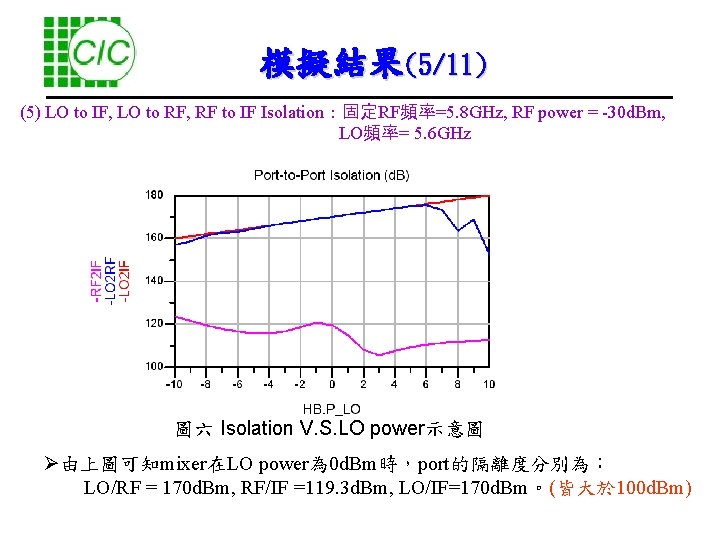

模擬結果(5/11) (5) LO to IF, LO to RF, RF to IF Isolation:固定RF頻率=5. 8 GHz, RF power = -30 d. Bm, LO頻率= 5. 6 GHz 圖六 Isolation V. S. LO power示意圖 由上圖可知mixer在LO power為 0 d. Bm時,port的隔離度分別為: LO/RF = 170 d. Bm, RF/IF =119. 3 d. Bm, LO/IF=170 d. Bm。(皆大於 100 d. Bm)

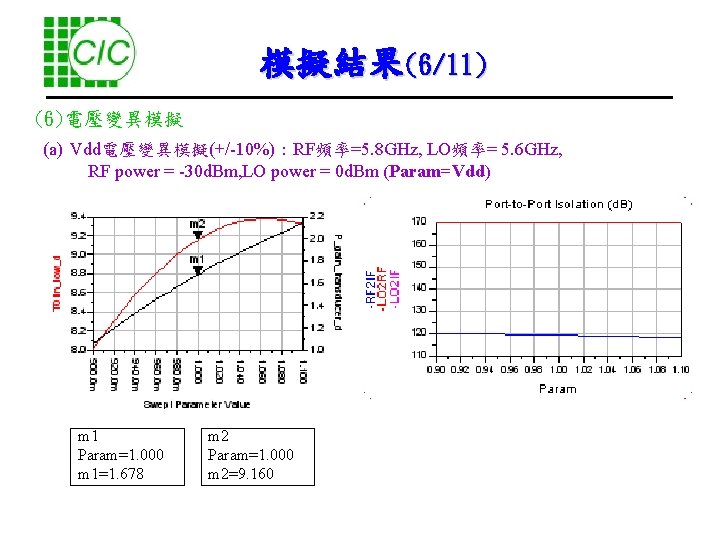

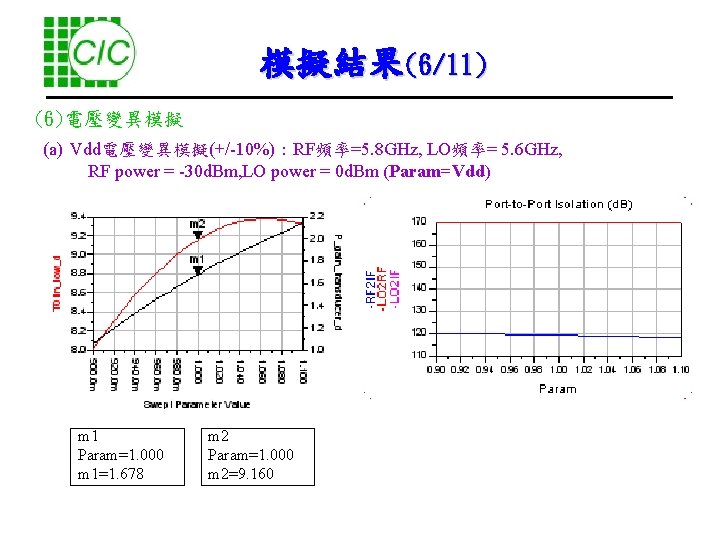

模擬結果(6/11) (6)電壓變異模擬 (a) Vdd電壓變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=Vdd) m 1 Param=1. 000 m 1=1. 678 m 2 Param=1. 000 m 2=9. 160

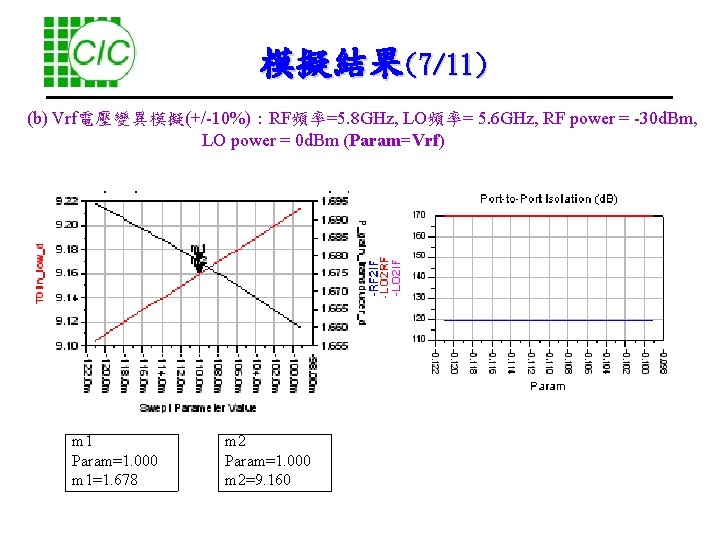

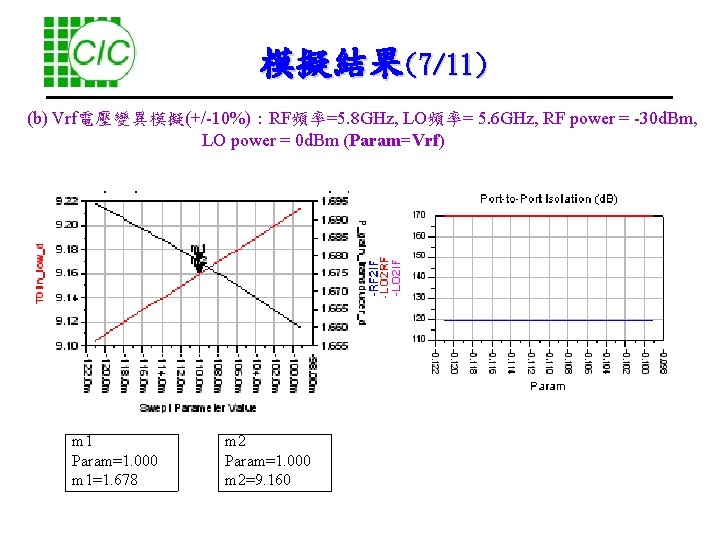

模擬結果(7/11) (b) Vrf電壓變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=Vrf) m 1 Param=1. 000 m 1=1. 678 m 2 Param=1. 000 m 2=9. 160

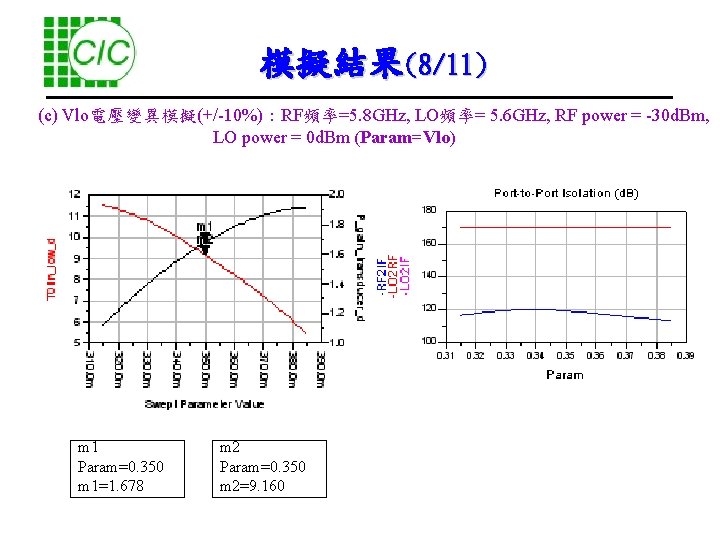

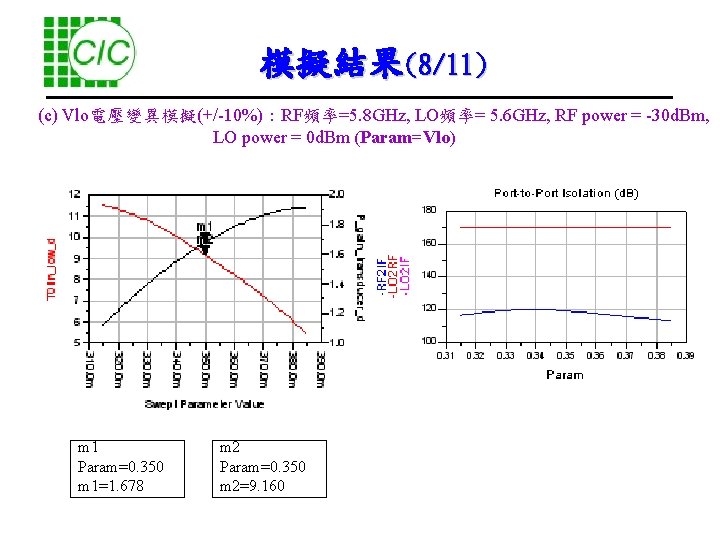

模擬結果(8/11) (c) Vlo電壓變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=Vlo) m 1 Param=0. 350 m 1=1. 678 m 2 Param=0. 350 m 2=9. 160

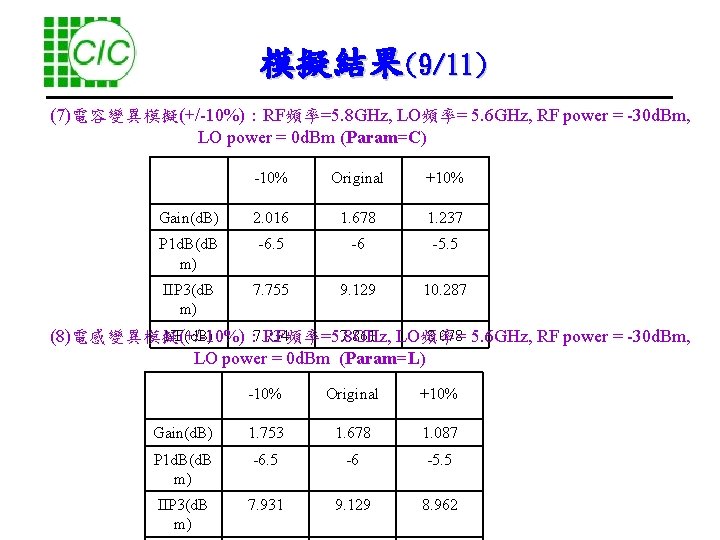

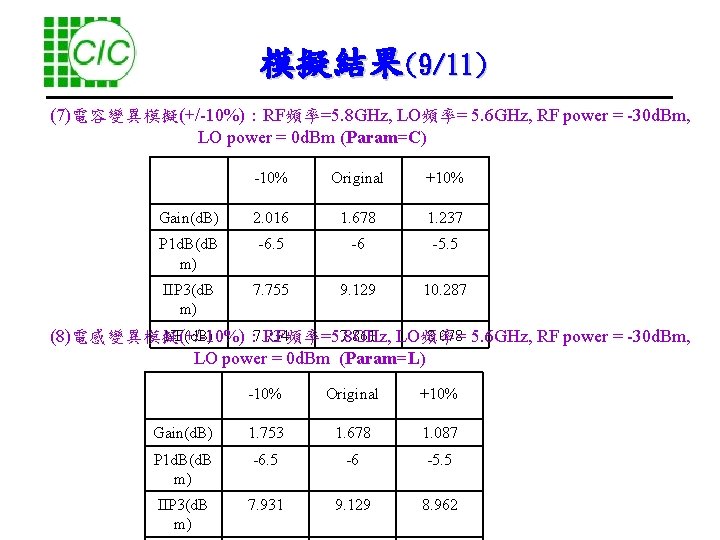

模擬結果(9/11) (7)電容變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=C) -10% Original +10% Gain(d. B) 2. 016 1. 678 1. 237 P 1 d. B(d. B m) -6. 5 -6 -5. 5 IIP 3(d. B m) 7. 755 9. 129 10. 287 NF(d. B) 7. 734 7. 861 8. 078 (8)電感變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=L) -10% Original +10% Gain(d. B) 1. 753 1. 678 1. 087 P 1 d. B(d. B m) -6. 5 -6 -5. 5 IIP 3(d. B m) 7. 931 9. 129 8. 962

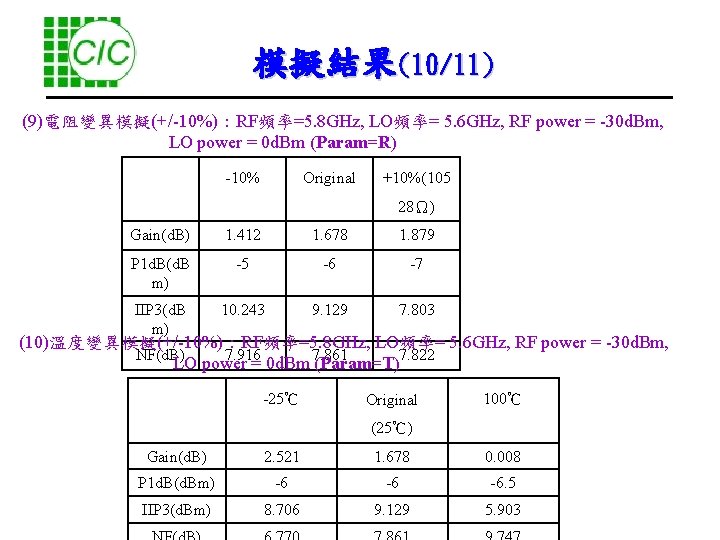

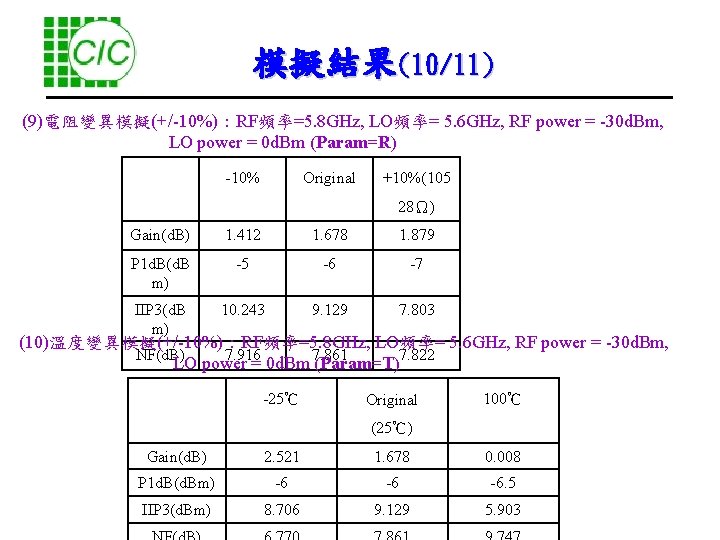

模擬結果(10/11) (9)電阻變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, LO power = 0 d. Bm (Param=R) -10% Original +10%(105 28Ω) Gain(d. B) 1. 412 1. 678 1. 879 P 1 d. B(d. B m) -5 -6 -7 IIP 3(d. B m) 10. 243 9. 129 7. 803 NF(d. B) 7. 916 (10)溫度變異模擬(+/-10%):RF頻率=5. 8 GHz, LO頻率= 5. 6 GHz, RF power = -30 d. Bm, 7. 861 7. 822 LO power = 0 d. Bm (Param=T) -25℃ Original 100℃ (25℃) Gain(d. B) 2. 521 1. 678 0. 008 P 1 d. B(d. Bm) -6 -6 -6. 5 IIP 3(d. Bm) 8. 706 9. 129 5. 903

與現有技術之比較(11/11) This work (3) Tuncer, H. M et. Al 2004 (4) Xuezhen Wang et. Al 2003 (5) Hung-Che Wei et. al 2004 Supply voltage(V) 1 1. 8 1. 5 RF Freq(GHz) 5. 8 5. 25 5. 8 2. 4 Conversion Gain(d. B) 1. 681 3. 4 7 1 P 1 d. B(d. Bm) -6 **** -1. 15 IIP 3(d. Bm) 9. 149 -1. 2 -2. 94 11 NF(d. B) 7. 861 9. 1 14. 3 17. 3 LO-RF& LO-IF Isolation (d. B) >60 >50 **** Process UMC 0. 18 um TSMC 0. 18 um Supply voltage = 1 V 已小於其他論文,適合於低電壓系統的應用。 IIP 3 = 9. 149 d. Bm已大於其他論文,線性度改善了約12 d. Bm。 NF = 7. 861 d. B已小於其他論文,改善了約9 d. B的雜訊。

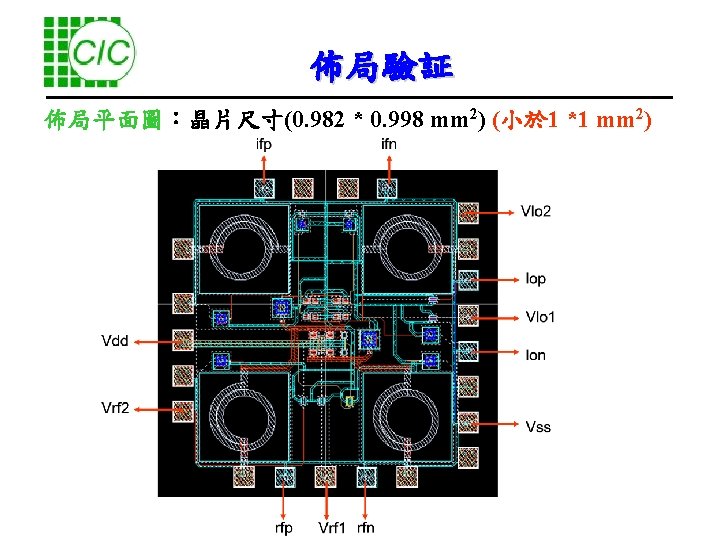

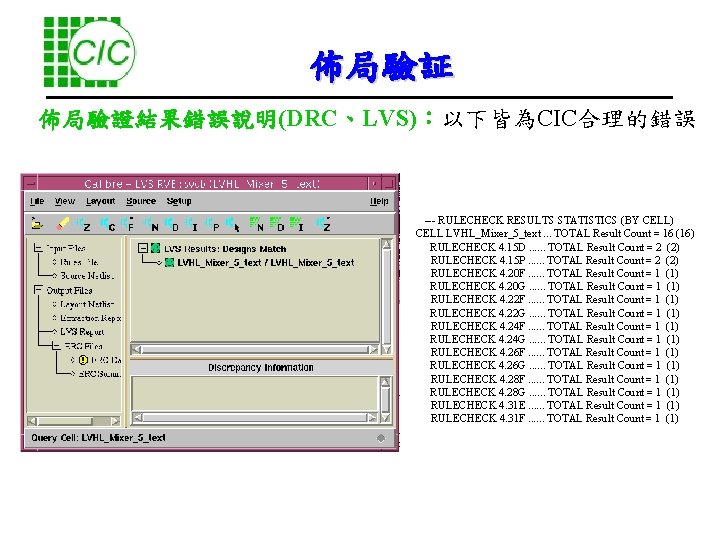

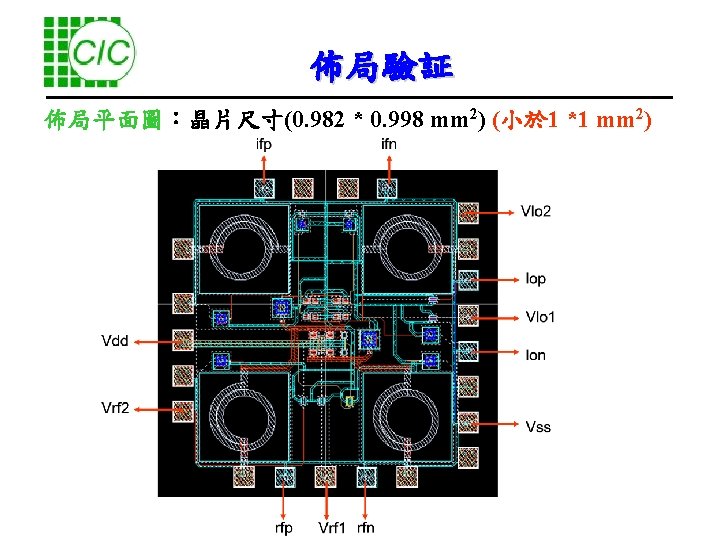

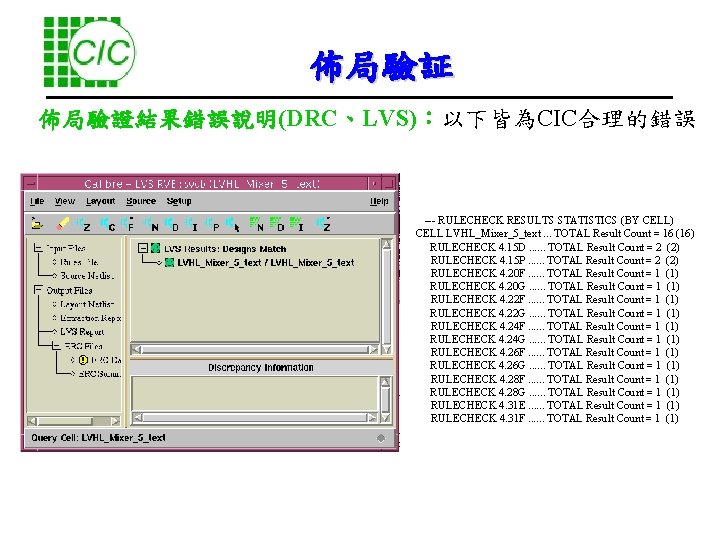

佈局驗証 佈局驗證結果錯誤說明(DRC、LVS):以下皆為CIC合理的錯誤 --- RULECHECK RESULTS STATISTICS (BY CELL) CELL LVHL_Mixer_5_text. . . TOTAL Result Count = 16 (16) RULECHECK 4. 15 D. . . TOTAL Result Count = 2 (2) RULECHECK 4. 15 P. . . TOTAL Result Count = 2 (2) RULECHECK 4. 20 F. . . TOTAL Result Count = 1 (1) RULECHECK 4. 20 G. . . TOTAL Result Count = 1 (1) RULECHECK 4. 22 F. . . TOTAL Result Count = 1 (1) RULECHECK 4. 22 G. . . TOTAL Result Count = 1 (1) RULECHECK 4. 24 F. . . TOTAL Result Count = 1 (1) RULECHECK 4. 24 G. . . TOTAL Result Count = 1 (1) RULECHECK 4. 26 F. . . TOTAL Result Count = 1 (1) RULECHECK 4. 26 G. . . TOTAL Result Count = 1 (1) RULECHECK 4. 28 F. . . TOTAL Result Count = 1 (1) RULECHECK 4. 28 G. . . TOTAL Result Count = 1 (1) RULECHECK 4. 31 E. . . TOTAL Result Count = 1 (1) RULECHECK 4. 31 F. . . TOTAL Result Count = 1 (1)

參考資料 1. Mitrea, O. ; Popa, C. ; Manolescu, A. M. ; Glesner, M. , “A linearization technique for radio frequency CMOS Gilbert-type mixers, ” ieeexplore. ieee. org/xpl/Recent. Con. jsp? punumber=9125 Volume 3, 14 -17 Dec. 2003 Page(s): 1086 - 1089 Vol. 3. 2. C. -C. Tang, W. -S. Lu, L. -D. Van, and W. -S. Feng, “A 2. 4 GHz CMOS down-conversion doubly balanced mixer with low supply voltage, ” in Proc. IEEE Int. Symp. Circuits Systems(ISCAS), vol. 4, May 2001, pp. 794 -797. 3. Tuncer, H. M. ; Udrea, F. ; Amaratunga, G. A. J. , “A 5 GHz low power 0. 18/spl mu/m CMOS Gilbert cell mixer, ” in Proc. IEEE Int. Symp. Semiconductor Conference, 2004. CAS 2004 Proceedings. 2004 International, Volume 1, 4 -6 Oct. 4. Xuezhen Wang; Weber, R. , “A novel low-voltage low-power 5. 8 GHz CMOS down-conversion mixer design, ” Radio and Wireless Conference, 2003. RAWCON '03. Proceedings, 10 -13 Aug. 2003 Page(s): 301 – 304. 5. Hung-Che Wei; Ro-Min Weng; Kun-Yi Lin , “A 1. 5 V high-linearity CMOS mixer for 2. 4 GHz applications, ” Circuits and Systems, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on Volume 1, 23 -26 May 2004 Page(s): I - 561 -4 Vol. 1