5 4 Decoders A decoder is a multipleinput

- Slides: 11

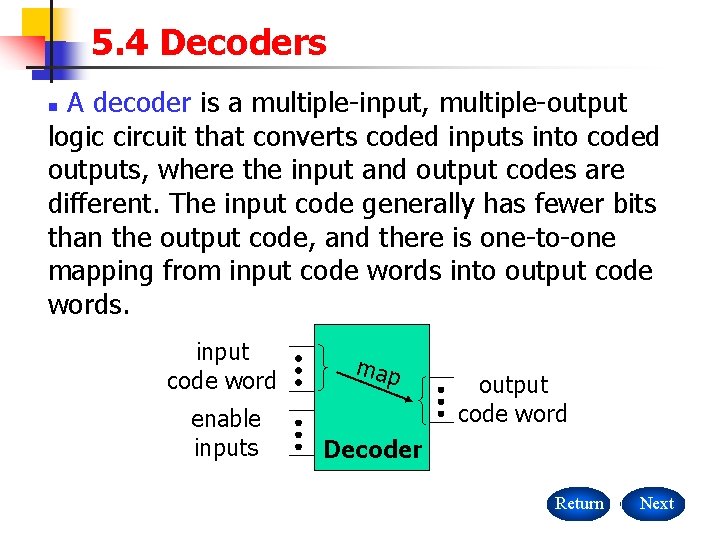

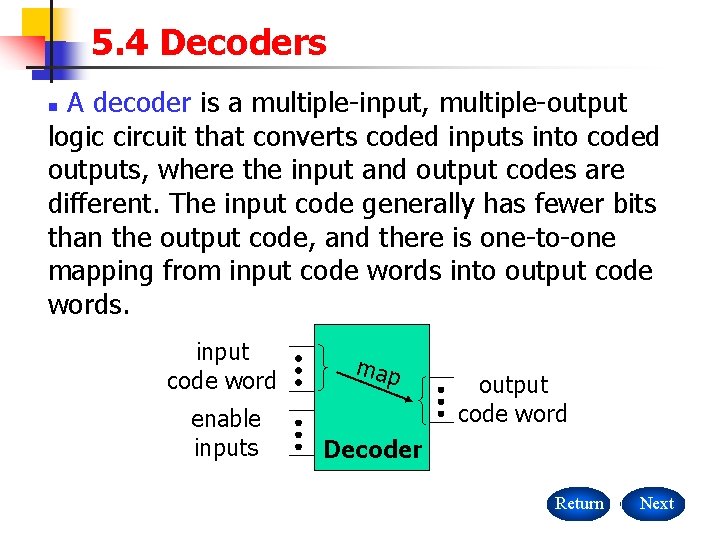

5. 4 Decoders A decoder is a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. The input code generally has fewer bits than the output code, and there is one-to-one mapping from input code words into output code words. n input code word map enable inputs Decoder output code word Return Next

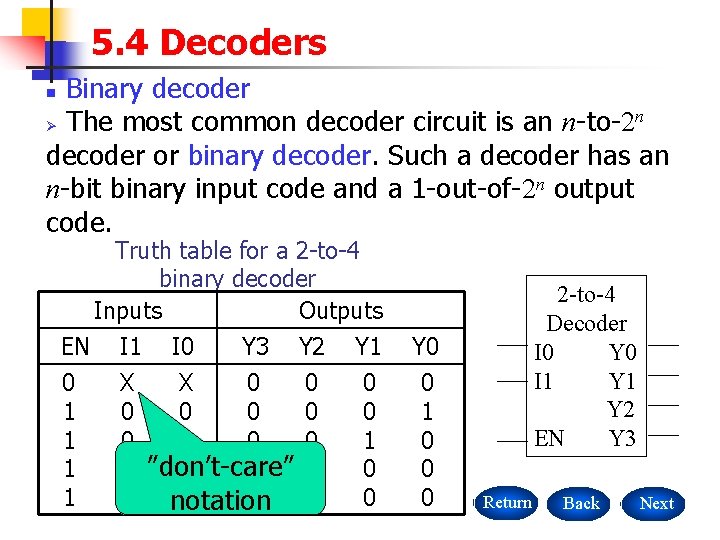

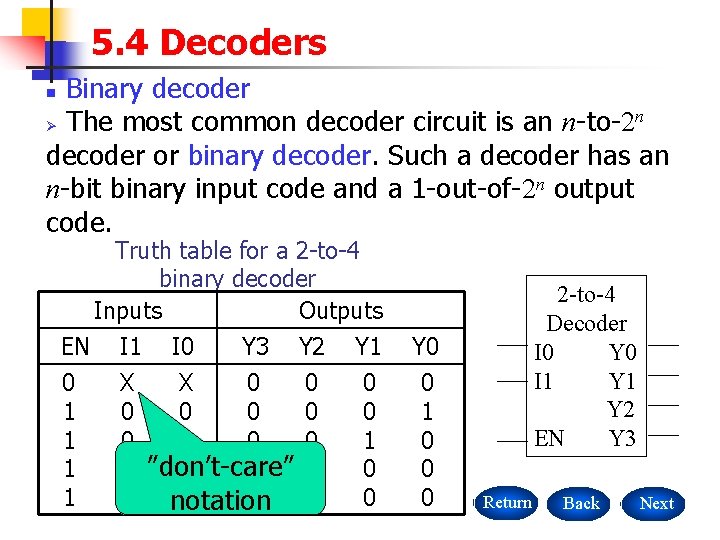

5. 4 Decoders Binary decoder n Ø The most common decoder circuit is an n-to-2 decoder or binary decoder. Such a decoder has an n-bit binary input code and a 1 -out-of-2 n output code. n Truth table for a 2 -to-4 binary decoder Inputs Outputs EN I 1 I 0 Y 3 Y 2 Y 1 0 X X 0 0 0 1 0 0 1 1 1 ”don’t-care” 0 0 1 1 notation 1 1 0 0 Y 0 0 1 0 0 0 2 -to-4 Decoder I 0 Y 0 I 1 Y 2 EN Y 3 Return Back Next

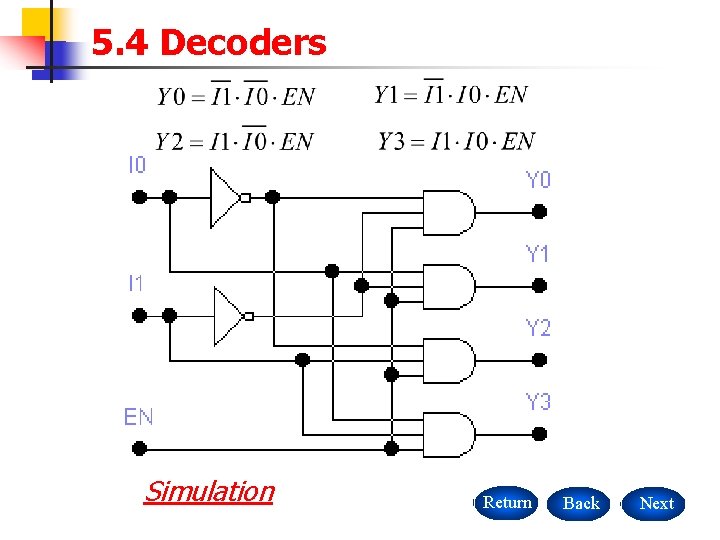

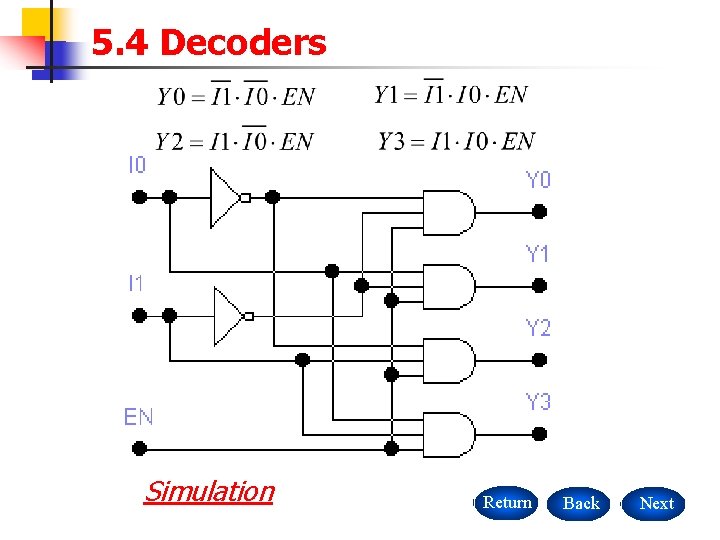

5. 4 Decoders Simulation Return Back Next

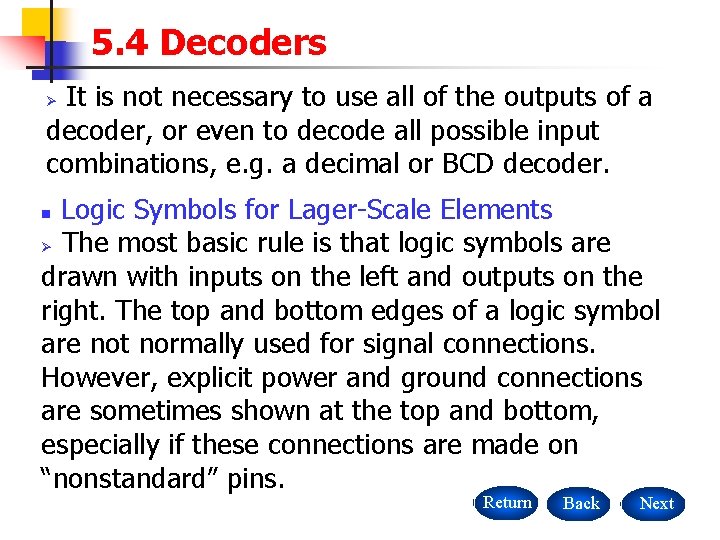

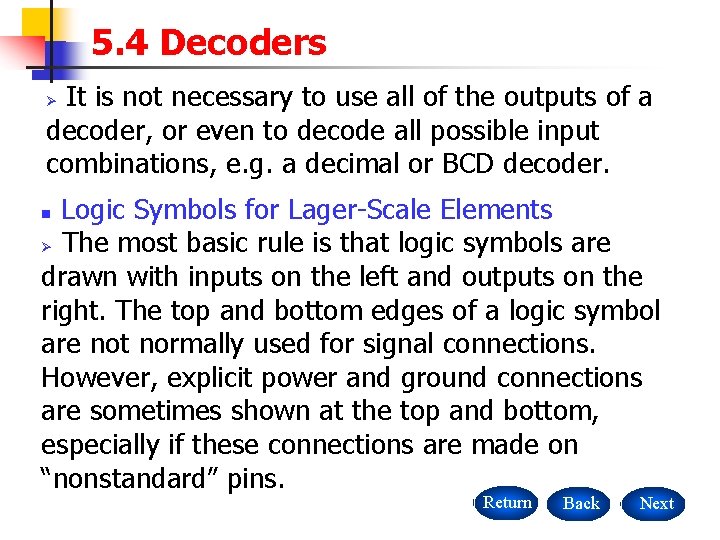

5. 4 Decoders It is not necessary to use all of the outputs of a decoder, or even to decode all possible input combinations, e. g. a decimal or BCD decoder. Ø Logic Symbols for Lager-Scale Elements Ø The most basic rule is that logic symbols are drawn with inputs on the left and outputs on the right. The top and bottom edges of a logic symbol are not normally used for signal connections. However, explicit power and ground connections are sometimes shown at the top and bottom, especially if these connections are made on “nonstandard” pins. n Return Back Next

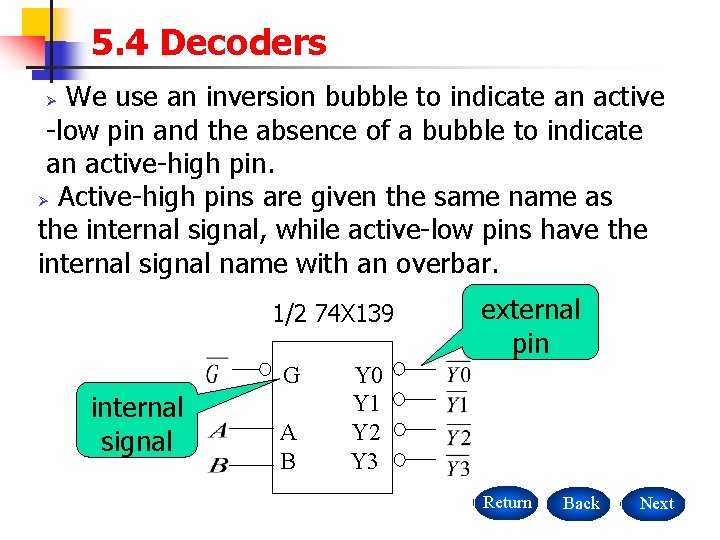

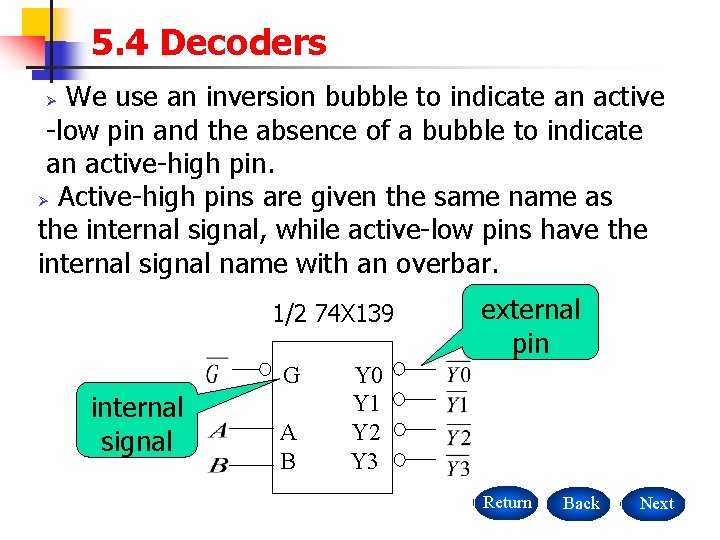

5. 4 Decoders We use an inversion bubble to indicate an active -low pin and the absence of a bubble to indicate an active-high pin. Ø Active-high pins are given the same name as the internal signal, while active-low pins have the internal signal name with an overbar. Ø 1/2 74 X 139 G internal signal A B external pin Y 0 Y 1 Y 2 Y 3 Return Back Next

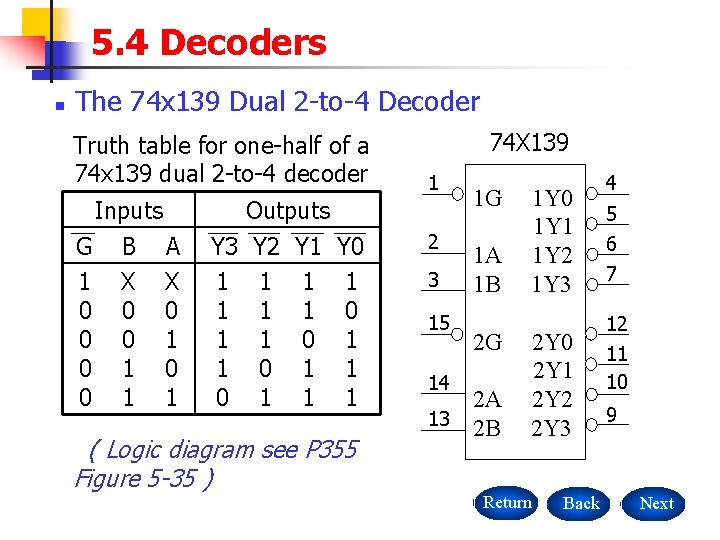

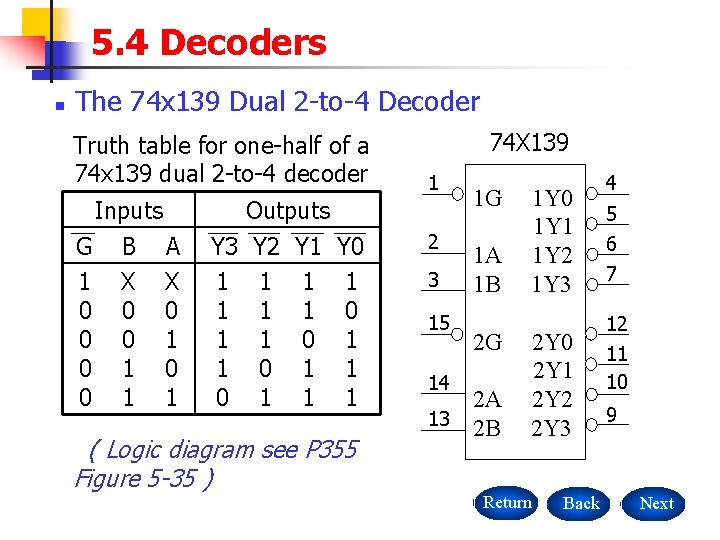

5. 4 Decoders n The 74 x 139 Dual 2 -to-4 Decoder Truth table for one-half of a 74 x 139 dual 2 -to-4 decoder Inputs G B A 1 X X 0 0 0 1 1 Y 3 1 1 0 Outputs Y 2 Y 1 1 1 0 0 1 1 1 Y 0 1 1 1 ( Logic diagram see P 355 Figure 5 -35 ) 74 X 139 1 2 3 15 14 1 G 1 A 1 B 2 G 2 A 13 2 B 1 Y 0 1 Y 1 1 Y 2 1 Y 3 2 Y 0 2 Y 1 2 Y 2 2 Y 3 Return Back 4 5 6 7 12 11 10 9 Next

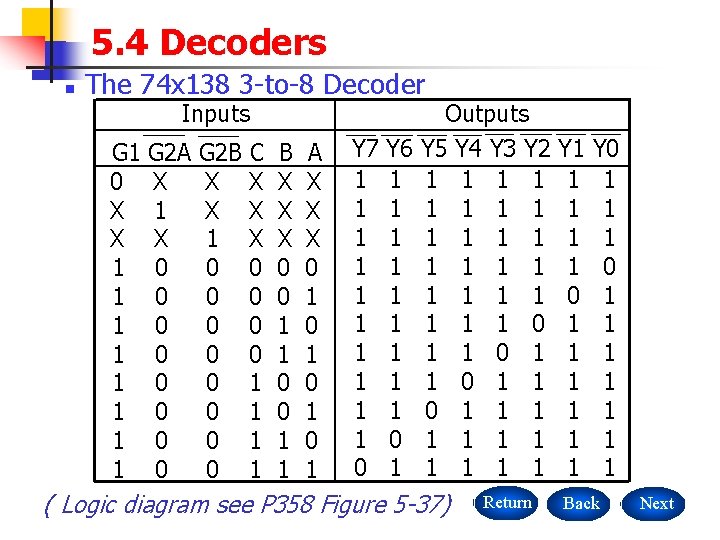

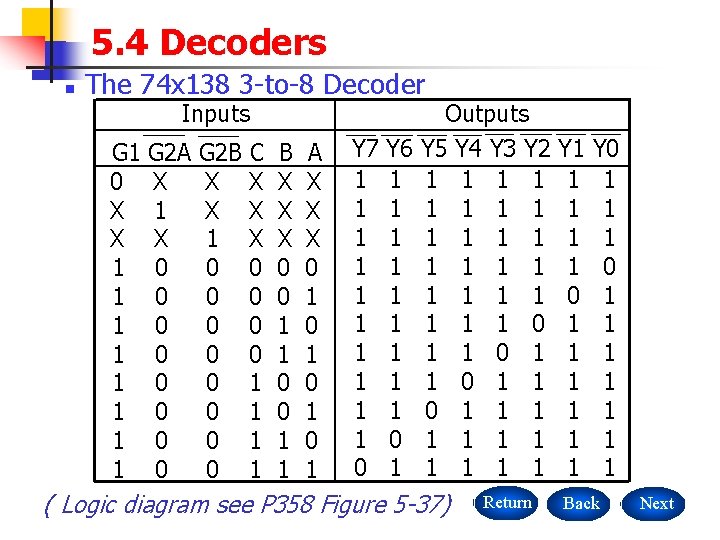

5. 4 Decoders n The 74 x 138 3 -to-8 Decoder Inputs G 1 0 X X 1 1 1 1 G 2 A X 1 X 0 0 0 0 G 2 B C X X 1 X 0 0 0 0 0 1 0 1 B X X X 0 0 1 1 A X X X 0 1 0 1 Y 7 1 1 1 1 1 0 Y 6 1 1 1 1 1 0 1 Outputs Y 5 Y 4 Y 3 Y 2 1 1 1 1 1 1 0 1 1 1 1 1 1 ( Logic diagram see P 358 Figure 5 -37) Return Y 1 1 1 0 1 1 1 Y 0 1 1 1 1 1 Back Next

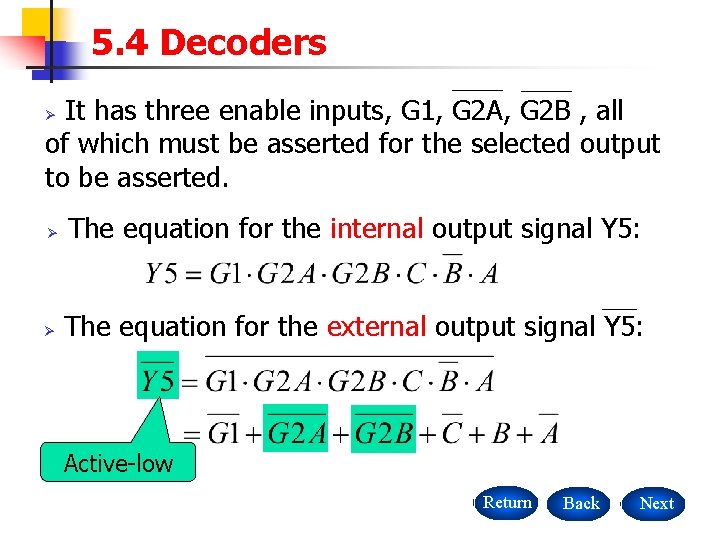

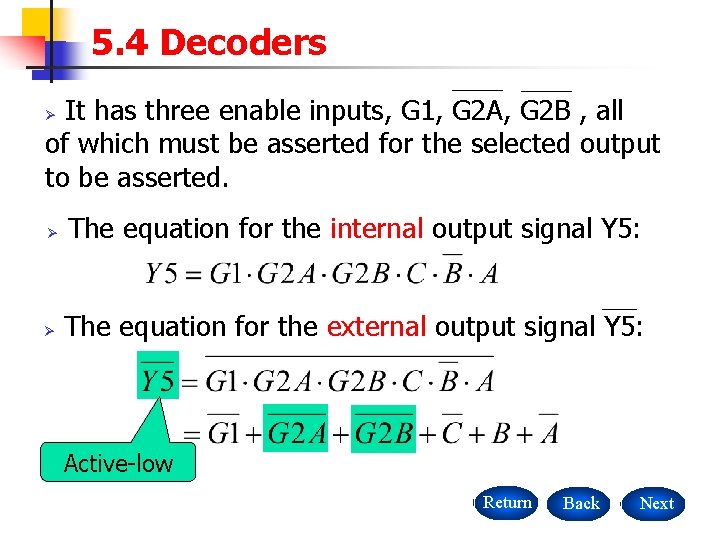

5. 4 Decoders It has three enable inputs, G 1, G 2 A, G 2 B , all of which must be asserted for the selected output to be asserted. Ø Ø The equation for the internal output signal Y 5: Ø The equation for the external output signal Y 5: Active-low Return Back Next

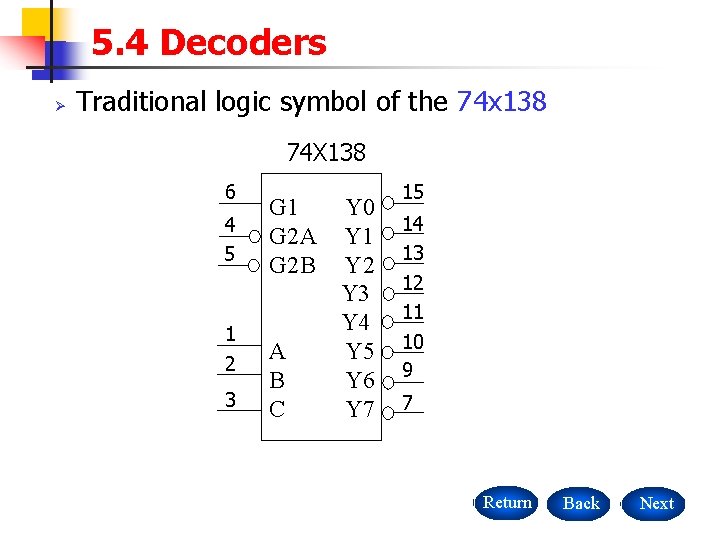

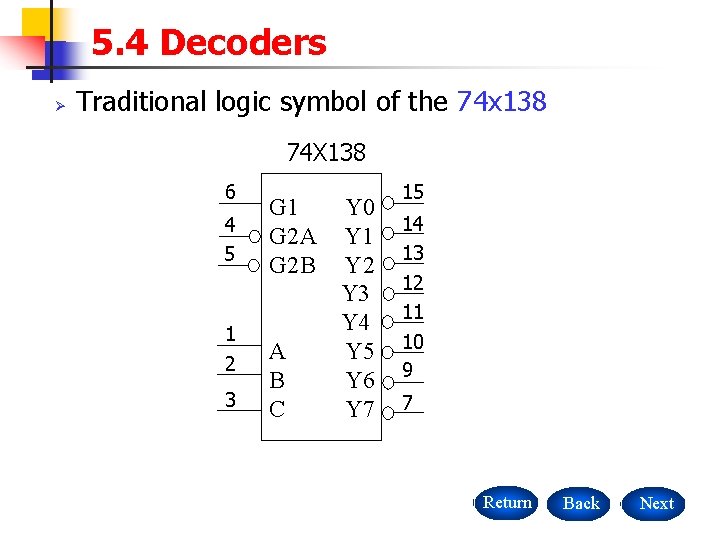

5. 4 Decoders Ø Traditional logic symbol of the 74 x 138 74 X 138 6 4 5 1 2 3 G 1 G 2 A G 2 B A B C Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 15 14 13 12 11 10 9 7 Return Back Next

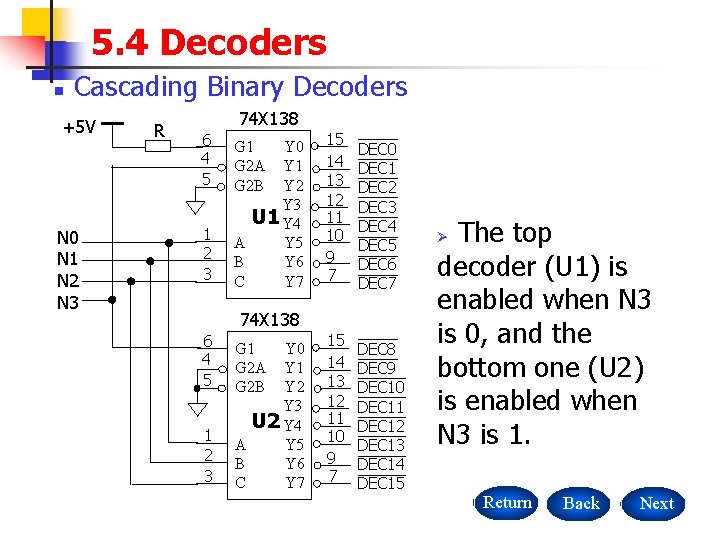

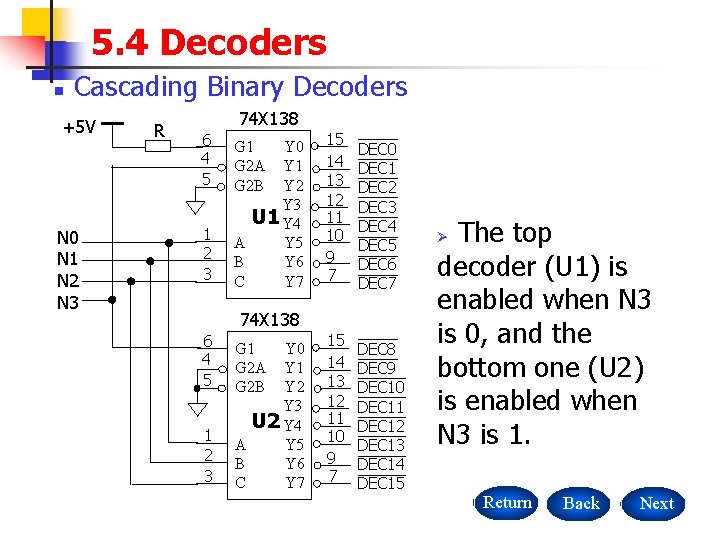

5. 4 Decoders n Cascading Binary Decoders +5 V N 0 N 1 N 2 N 3 R 74 X 138 6 4 5 1 2 3 G 1 G 2 A G 2 B Y 0 Y 1 Y 2 Y 3 U 1 Y 4 A Y 5 B Y 6 C Y 7 15 14 13 12 11 10 9 7 DEC 0 DEC 1 DEC 2 DEC 3 DEC 4 DEC 5 DEC 6 DEC 7 74 X 138 6 4 5 1 2 3 G 1 G 2 A G 2 B Y 0 Y 1 Y 2 Y 3 U 2 Y 4 A Y 5 B Y 6 C Y 7 15 14 13 12 11 10 9 7 DEC 8 DEC 9 DEC 10 DEC 11 DEC 12 DEC 13 DEC 14 DEC 15 The top decoder (U 1) is enabled when N 3 is 0, and the bottom one (U 2) is enabled when N 3 is 1. Ø Return Back Next

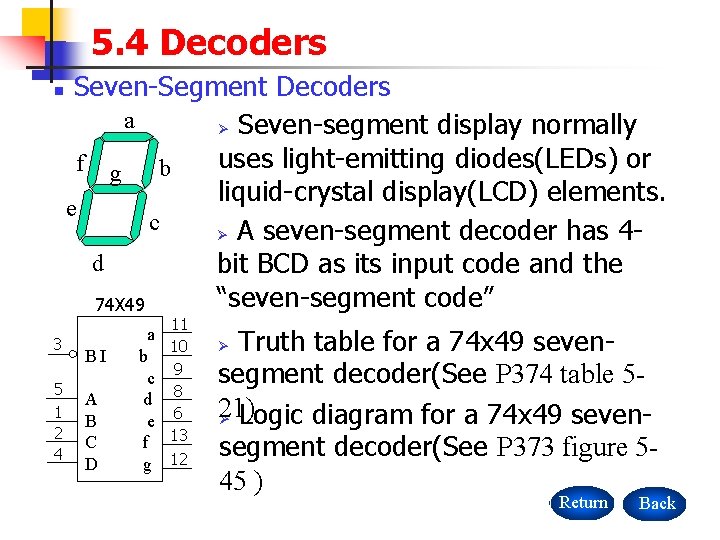

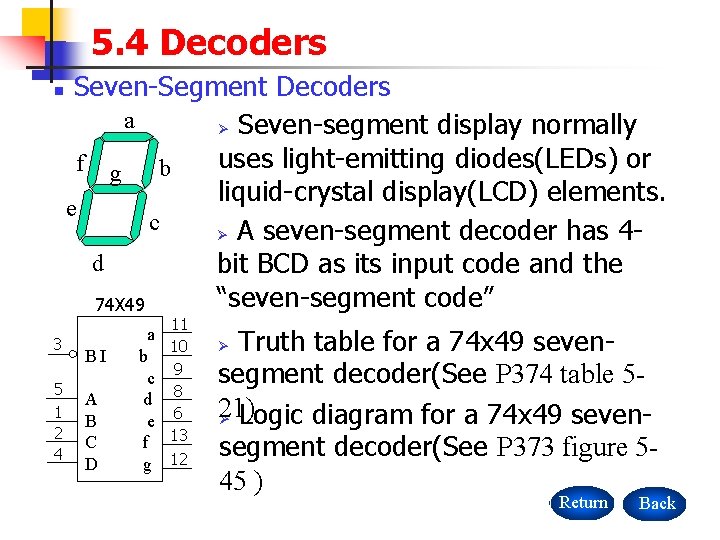

5. 4 Decoders n Seven-Segment Decoders a Ø Seven-segment display normally uses light-emitting diodes(LEDs) or f g b liquid-crystal display(LCD) elements. e c Ø A seven-segment decoder has 4 d bit BCD as its input code and the “seven-segment code” 74 X 49 11 3 5 1 2 4 BI A B C D a 10 b c 9 d 8 e 6 f 13 g 12 Truth table for a 74 x 49 sevensegment decoder(See P 374 table 521) Ø Logic diagram for a 74 x 49 sevensegment decoder(See P 373 figure 545 ) Ø Return Back