332 437 Lecture 10 Verilog Language Details n

![Composite Types -- Memories Arrays of registers reg [0: 3] table 8 xr 4 Composite Types -- Memories Arrays of registers reg [0: 3] table 8 xr 4](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-6.jpg)

![8 -bit Register Description module reg_logic (input [0: 7] d, input clk, output [0: 8 -bit Register Description module reg_logic (input [0: 7] d, input clk, output [0:](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-20.jpg)

![8 -bit Register, Asynchronous Reset, Synchronous Preset module reg_logic (input d [0: 7], input 8 -bit Register, Asynchronous Reset, Synchronous Preset module reg_logic (input d [0: 7], input](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-22.jpg)

- Slides: 29

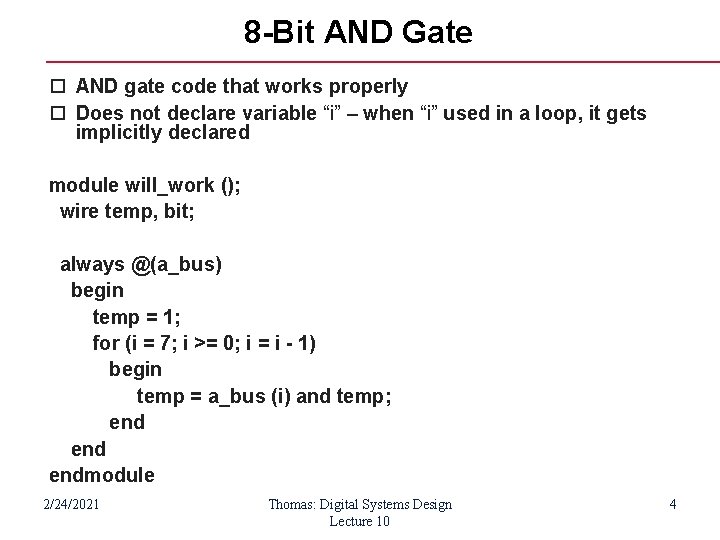

332: 437 Lecture 10 Verilog Language Details n n n n Parameters Blocking Assignment Operator Delay time units Arrays of registers FIFO Example Flip-flop descriptions Verilog Operators Summary Material from The Verilog Hardware Description Language, by Thomas and Moorby, Kluwer Academic Publishers, VHDL for Programmable Logic, by Kevin Skahill, Addison Wesley Longman. 2/24/2021 Thomas: Digital Systems Design Lecture 10 1

Parameters – hold value that cannot change within design description #(parameter width = 8, delay=10) assign #(delay) xout <= xin 1 ^ xin 2; 2/24/2021 Thomas: Digital Systems Design Lecture 10 2

Blocking Assignment Operator Can be used everywhere, including in functions & tasks MAY NOT BE SYNTHESIZED INTO WIRES OR MEMORY ELEMENTS Blocking assignment –- immediate, not scheduled, holds only 1 value at a time = is the blocking assignment operator 2/24/2021 Thomas: Digital Systems Design Lecture 10 3

8 -Bit AND Gate AND gate code that works properly Does not declare variable “i” – when “i” used in a loop, it gets implicitly declared module will_work (); wire temp, bit; always @(a_bus) begin temp = 1; for (i = 7; i >= 0; i = i - 1) begin temp = a_bus (i) and temp; end endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 4

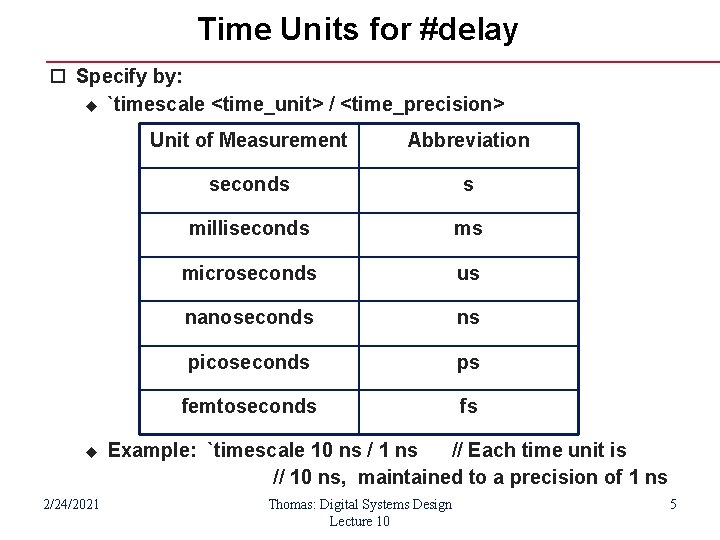

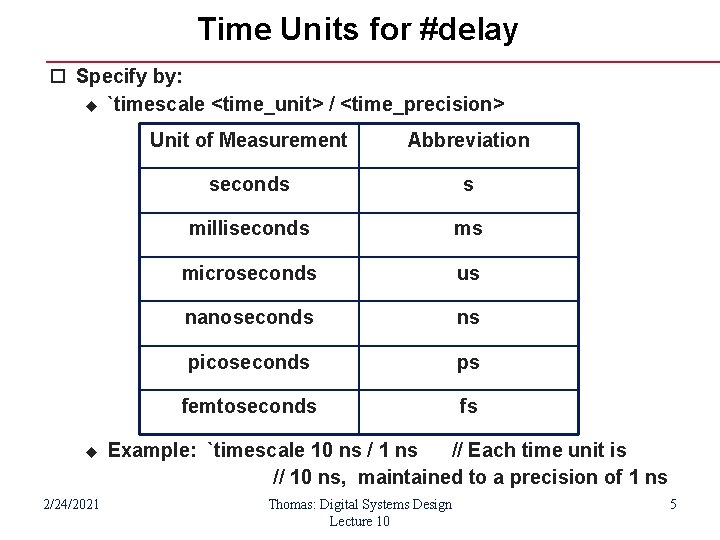

Time Units for #delay Specify by: `timescale <time_unit> / <time_precision> 2/24/2021 Unit of Measurement Abbreviation seconds s milliseconds ms microseconds us nanoseconds ns picoseconds ps femtoseconds fs Example: `timescale 10 ns / 1 ns // Each time unit is // 10 ns, maintained to a precision of 1 ns Thomas: Digital Systems Design Lecture 10 5

![Composite Types Memories Arrays of registers reg 0 3 table 8 xr 4 Composite Types -- Memories Arrays of registers reg [0: 3] table 8 xr 4](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-6.jpg)

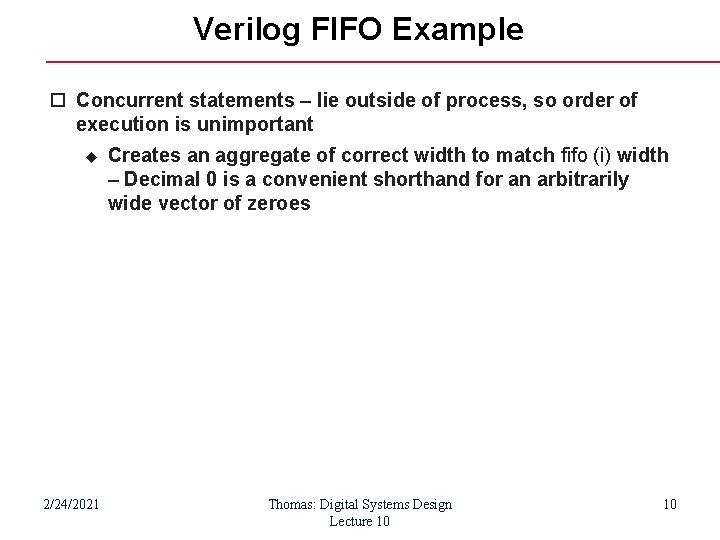

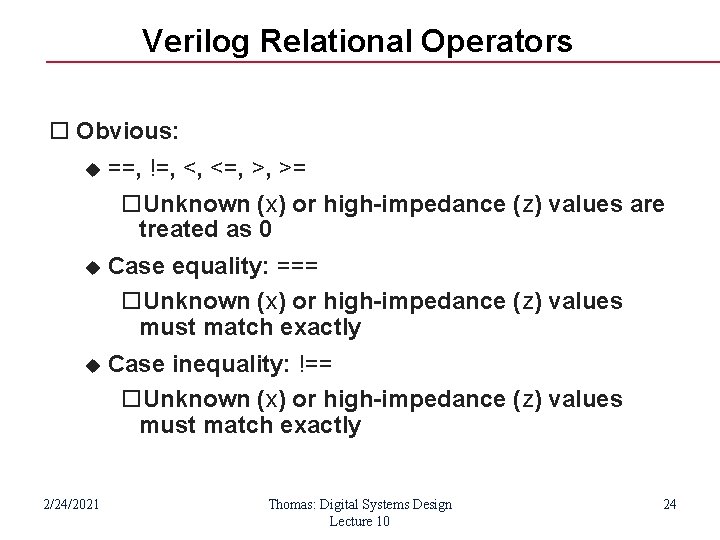

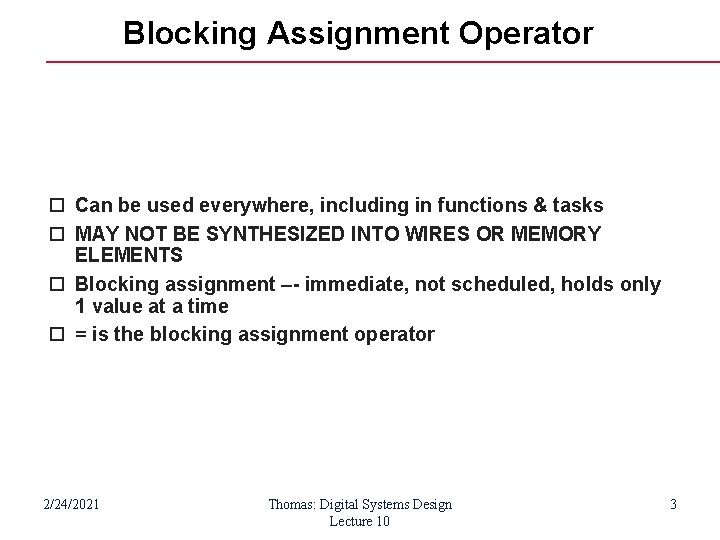

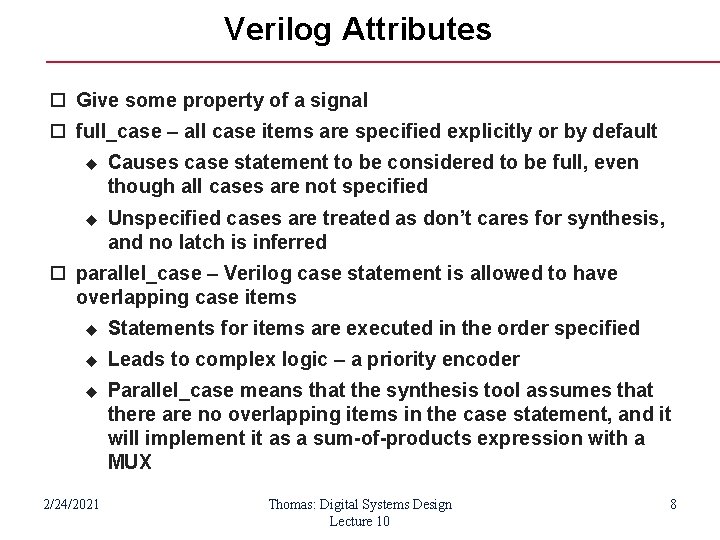

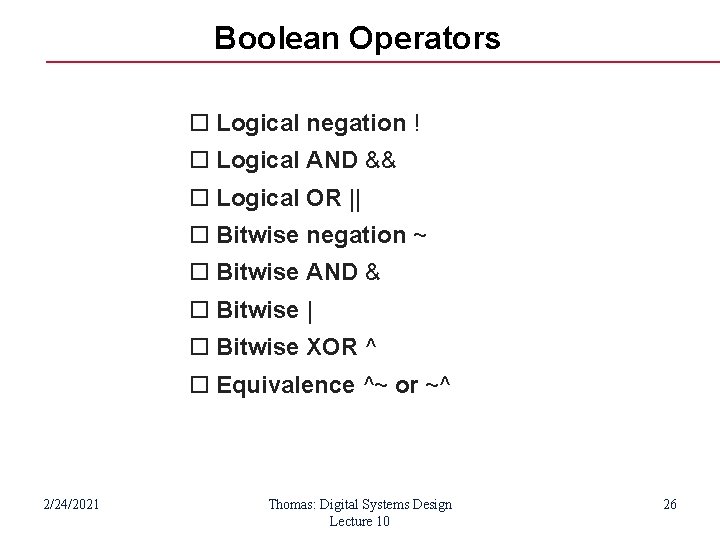

Composite Types -- Memories Arrays of registers reg [0: 3] table 8 xr 4 [0: 7]; initial begin table 8 xr 4 = {b’ 000_0, b’ 001_1, b’ 010_1, b’ 011_0, b’ 100_1, b’ 101_0, b’ 110_0, b’ 111_1}; end 2/24/2021 Thomas: Digital Systems Design Lecture 10 6

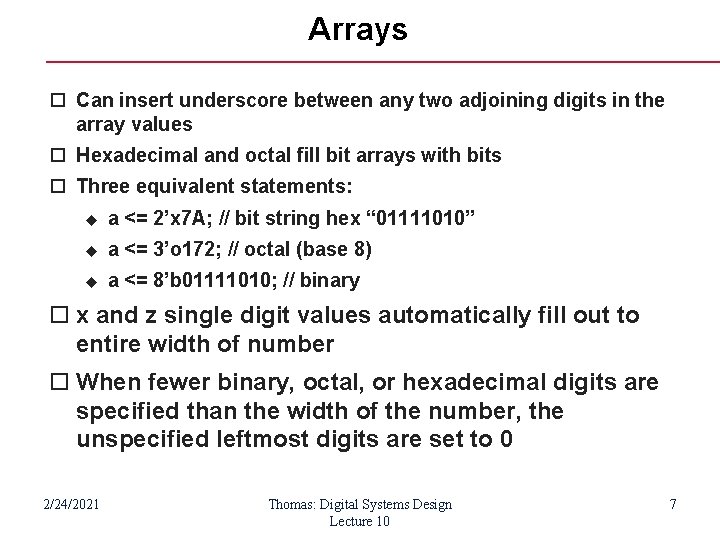

Arrays Can insert underscore between any two adjoining digits in the array values Hexadecimal and octal fill bit arrays with bits Three equivalent statements: a <= 2’x 7 A; // bit string hex “ 01111010” a <= 3’o 172; // octal (base 8) a <= 8’b 01111010; // binary x and z single digit values automatically fill out to entire width of number When fewer binary, octal, or hexadecimal digits are specified than the width of the number, the unspecified leftmost digits are set to 0 2/24/2021 Thomas: Digital Systems Design Lecture 10 7

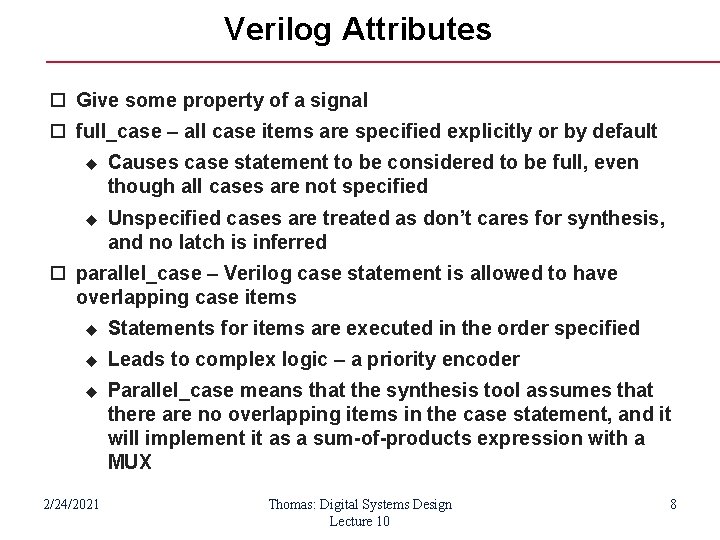

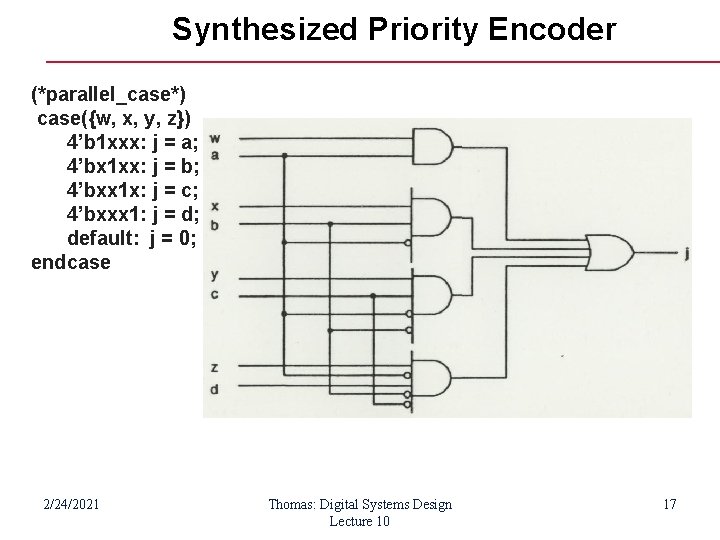

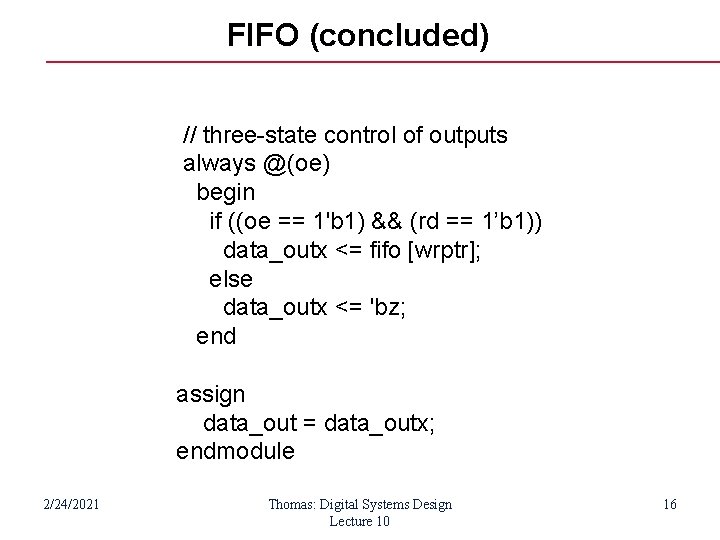

Verilog Attributes Give some property of a signal full_case – all case items are specified explicitly or by default Causes case statement to be considered to be full, even though all cases are not specified Unspecified cases are treated as don’t cares for synthesis, and no latch is inferred parallel_case – Verilog case statement is allowed to have overlapping case items Statements for items are executed in the order specified Leads to complex logic – a priority encoder Parallel_case means that the synthesis tool assumes that there are no overlapping items in the case statement, and it will implement it as a sum-of-products expression with a MUX 2/24/2021 Thomas: Digital Systems Design Lecture 10 8

Verilog Attribute Example module syn. Attributes (output reg f, input a, b, c); always @(*) (* full_case, parallel_case *) case ({a, b, c}) 3’b 001: f = 1’b 1; 3’b 010: f = 1’b 1; 3’b 011: f = 1’b 1; 3’b 100: f = 1’b 1; 3’b 110: f = 1’b 0; 3’b 111: f = 1’b 1; endcase endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 9

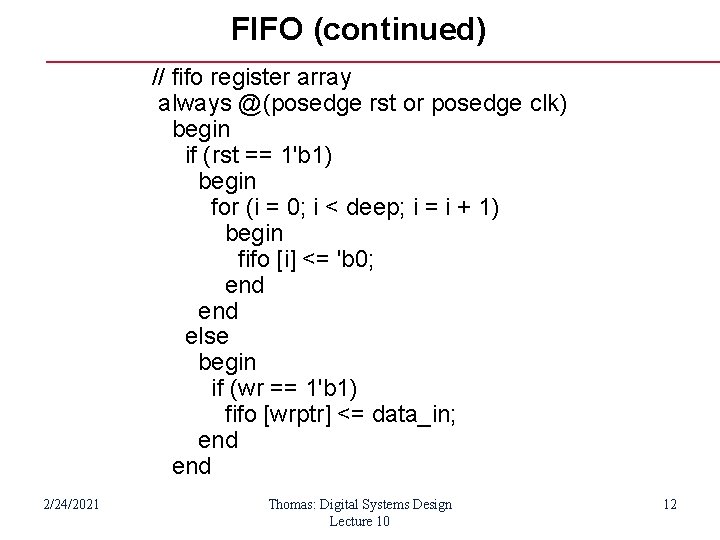

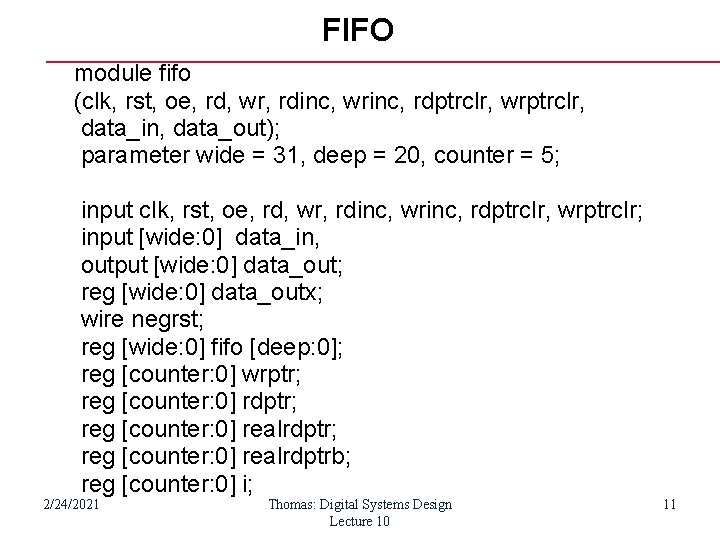

Verilog FIFO Example Concurrent statements – lie outside of process, so order of execution is unimportant 2/24/2021 Creates an aggregate of correct width to match fifo (i) width – Decimal 0 is a convenient shorthand for an arbitrarily wide vector of zeroes Thomas: Digital Systems Design Lecture 10 10

FIFO module fifo (clk, rst, oe, rd, wr, rdinc, wrinc, rdptrclr, wrptrclr, data_in, data_out); parameter wide = 31, deep = 20, counter = 5; input clk, rst, oe, rd, wr, rdinc, wrinc, rdptrclr, wrptrclr; input [wide: 0] data_in, output [wide: 0] data_out; reg [wide: 0] data_outx; wire negrst; reg [wide: 0] fifo [deep: 0]; reg [counter: 0] wrptr; reg [counter: 0] rdptr; reg [counter: 0] realrdptrb; reg [counter: 0] i; 2/24/2021 Thomas: Digital Systems Design Lecture 10 11

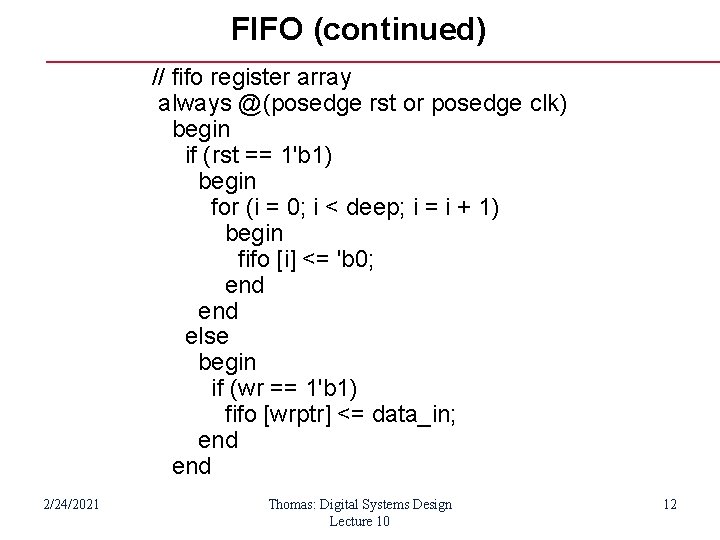

FIFO (continued) // fifo register array always @(posedge rst or posedge clk) begin if (rst == 1'b 1) begin for (i = 0; i < deep; i = i + 1) begin fifo [i] <= 'b 0; end else begin if (wr == 1'b 1) fifo [wrptr] <= data_in; end 2/24/2021 Thomas: Digital Systems Design Lecture 10 12

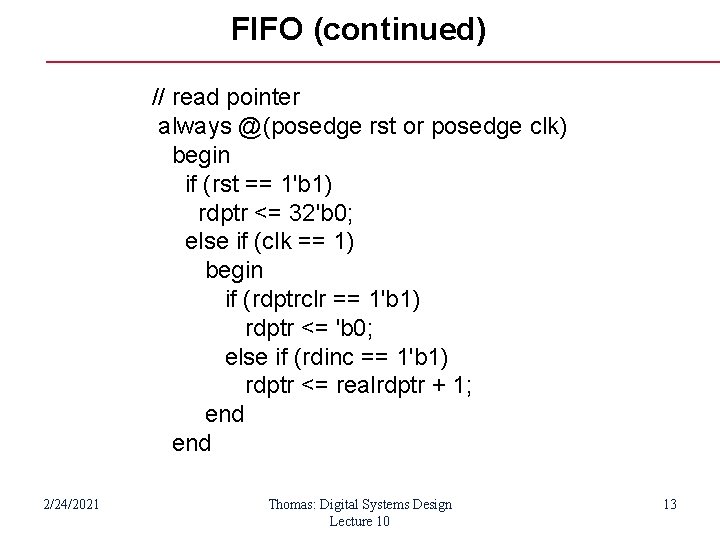

FIFO (continued) // read pointer always @(posedge rst or posedge clk) begin if (rst == 1'b 1) rdptr <= 32'b 0; else if (clk == 1) begin if (rdptrclr == 1'b 1) rdptr <= 'b 0; else if (rdinc == 1'b 1) rdptr <= realrdptr + 1; end 2/24/2021 Thomas: Digital Systems Design Lecture 10 13

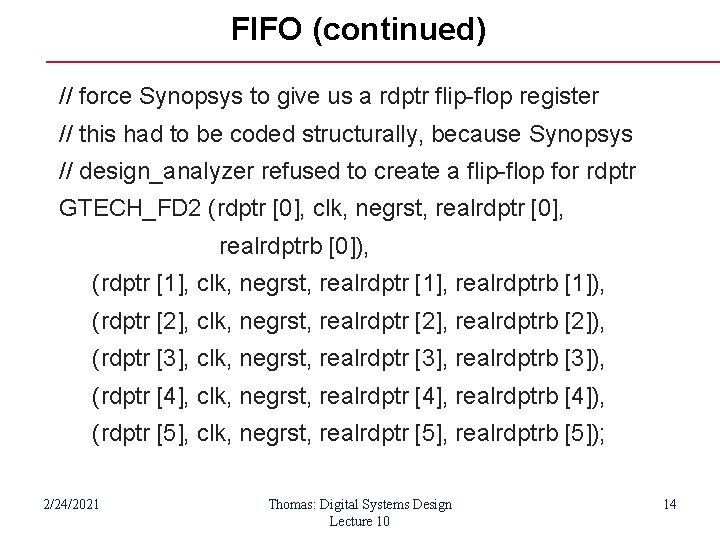

FIFO (continued) // force Synopsys to give us a rdptr flip-flop register // this had to be coded structurally, because Synopsys // design_analyzer refused to create a flip-flop for rdptr GTECH_FD 2 (rdptr [0], clk, negrst, realrdptr [0], realrdptrb [0]), (rdptr [1], clk, negrst, realrdptr [1], realrdptrb [1]), (rdptr [2], clk, negrst, realrdptr [2], realrdptrb [2]), (rdptr [3], clk, negrst, realrdptr [3], realrdptrb [3]), (rdptr [4], clk, negrst, realrdptr [4], realrdptrb [4]), (rdptr [5], clk, negrst, realrdptr [5], realrdptrb [5]); 2/24/2021 Thomas: Digital Systems Design Lecture 10 14

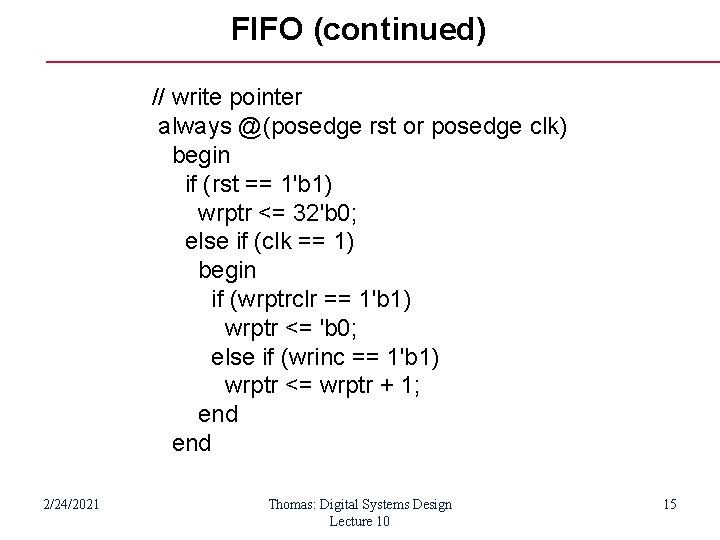

FIFO (continued) // write pointer always @(posedge rst or posedge clk) begin if (rst == 1'b 1) wrptr <= 32'b 0; else if (clk == 1) begin if (wrptrclr == 1'b 1) wrptr <= 'b 0; else if (wrinc == 1'b 1) wrptr <= wrptr + 1; end 2/24/2021 Thomas: Digital Systems Design Lecture 10 15

FIFO (concluded) // three-state control of outputs always @(oe) begin if ((oe == 1'b 1) && (rd == 1’b 1)) data_outx <= fifo [wrptr]; else data_outx <= 'bz; end assign data_out = data_outx; endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 16

Synthesized Priority Encoder (*parallel_case*) case({w, x, y, z}) 4’b 1 xxx: j = a; 4’bx 1 xx: j = b; 4’bxx 1 x: j = c; 4’bxxx 1: j = d; default: j = 0; endcase 2/24/2021 Thomas: Digital Systems Design Lecture 10 17

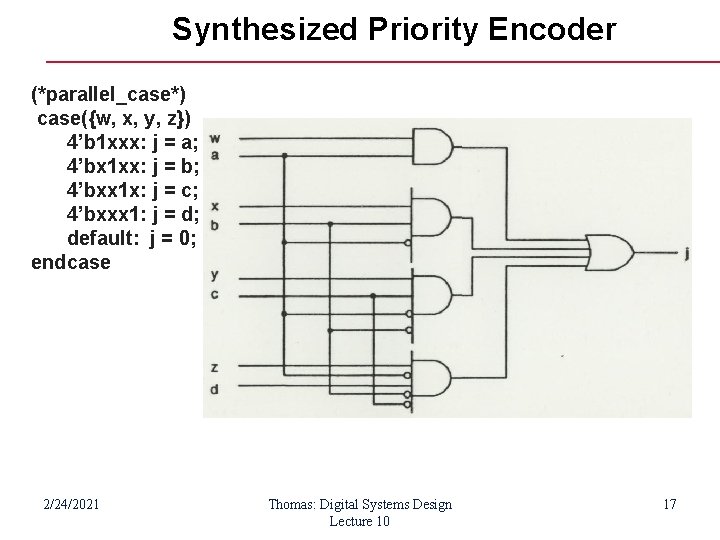

Level Sensitive Latch always @(clk, d) begin if (clk == 1’b 1) q <= d; end 2/24/2021 Thomas: Digital Systems Design Lecture 10 18

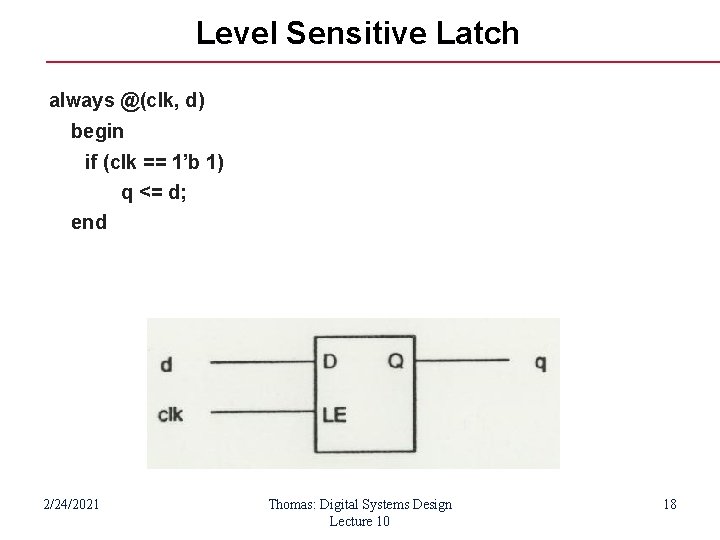

T Flip-Flop module tff_logic (input t, input clk, output q); always @(posedge clk) begin if (t == 1’b 1) q <= not (q); else q <= q; endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 19

![8 bit Register Description module reglogic input 0 7 d input clk output 0 8 -bit Register Description module reg_logic (input [0: 7] d, input clk, output [0:](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-20.jpg)

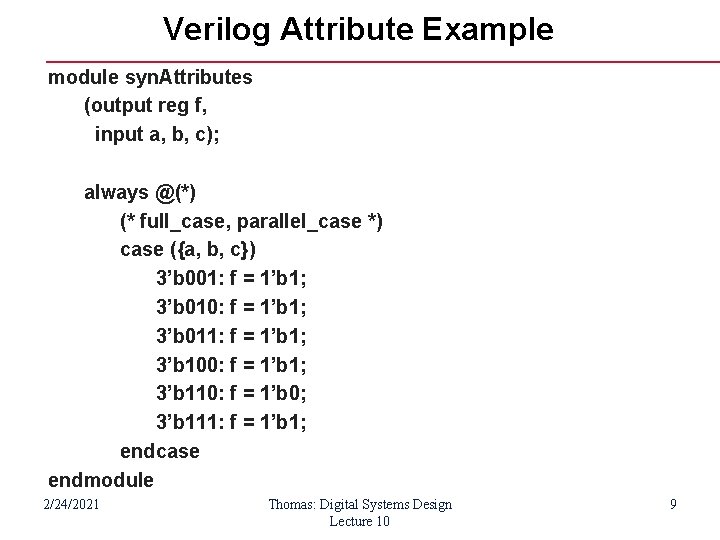

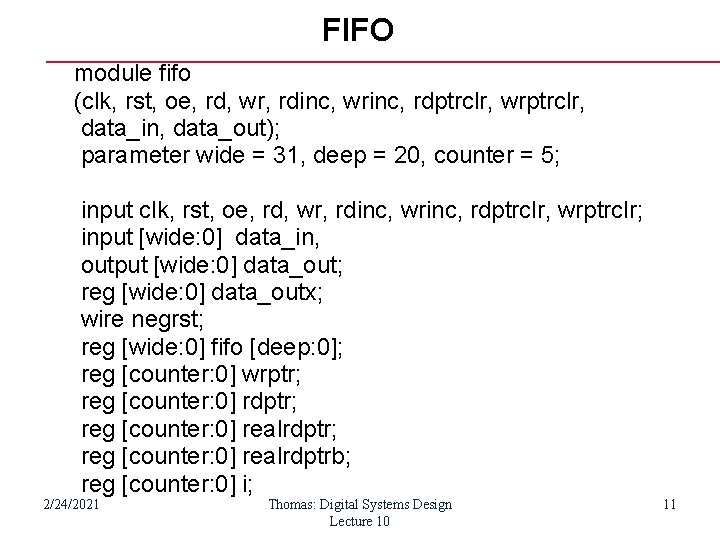

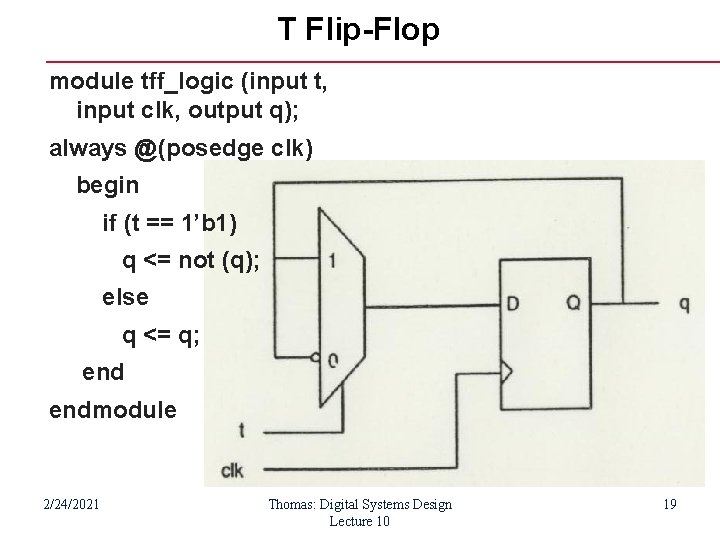

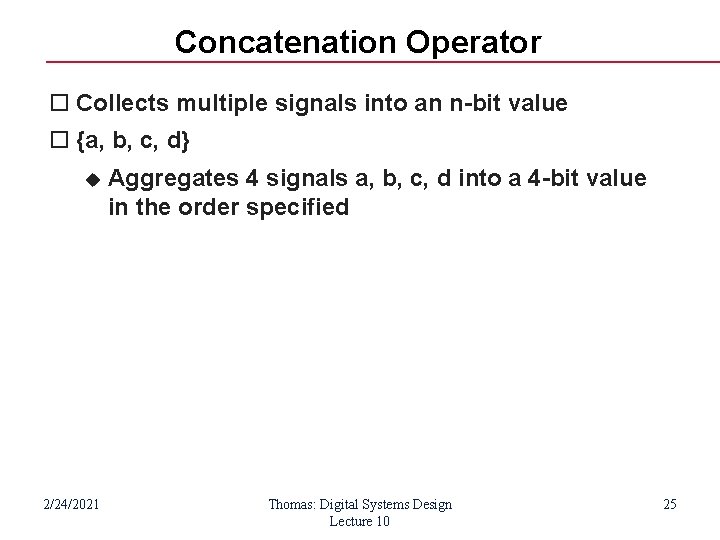

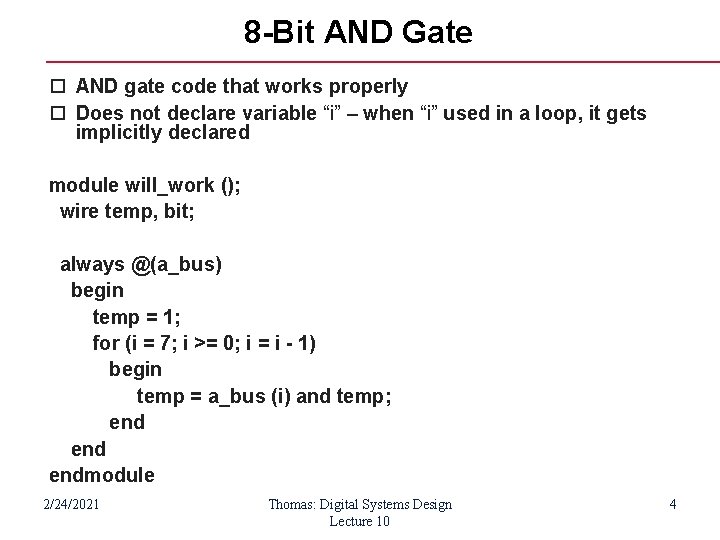

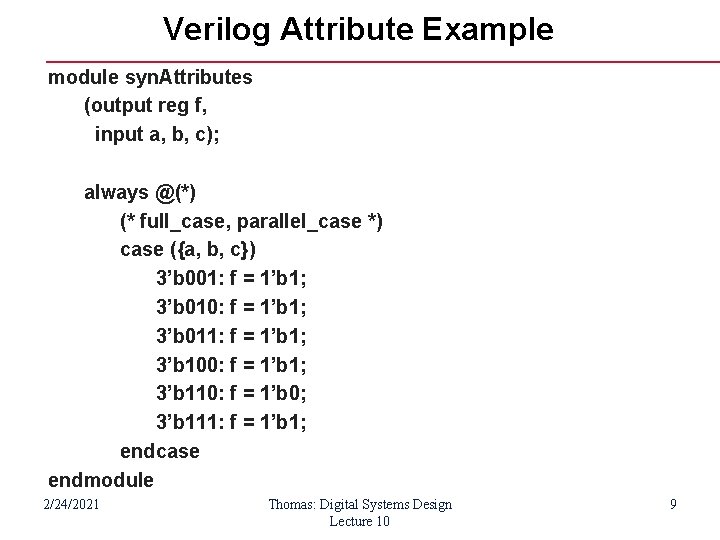

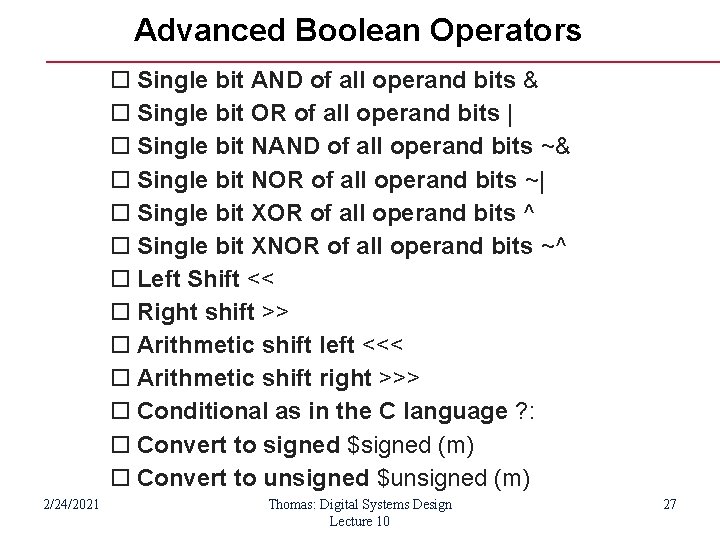

8 -bit Register Description module reg_logic (input [0: 7] d, input clk, output [0: 7] q); always @(posedge clk) begin q <= d; endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 20

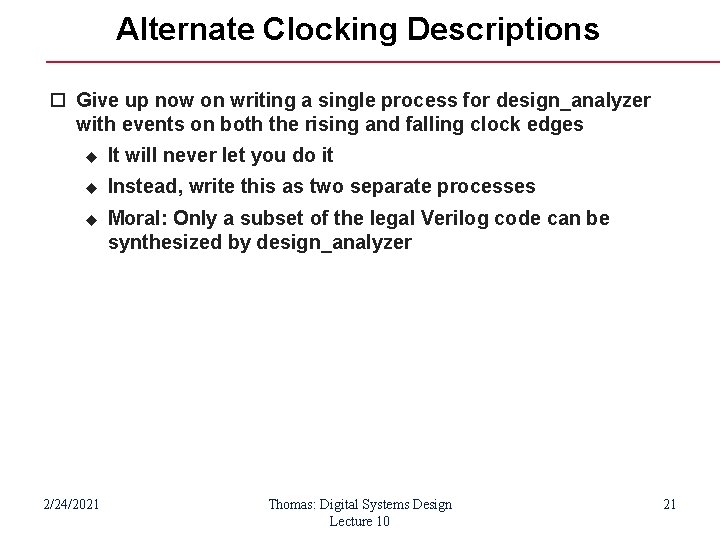

Alternate Clocking Descriptions Give up now on writing a single process for design_analyzer with events on both the rising and falling clock edges It will never let you do it Instead, write this as two separate processes Moral: Only a subset of the legal Verilog code can be synthesized by design_analyzer 2/24/2021 Thomas: Digital Systems Design Lecture 10 21

![8 bit Register Asynchronous Reset Synchronous Preset module reglogic input d 0 7 input 8 -bit Register, Asynchronous Reset, Synchronous Preset module reg_logic (input d [0: 7], input](https://slidetodoc.com/presentation_image_h/0ef40411a5ec5da2928c78e8aa780a25/image-22.jpg)

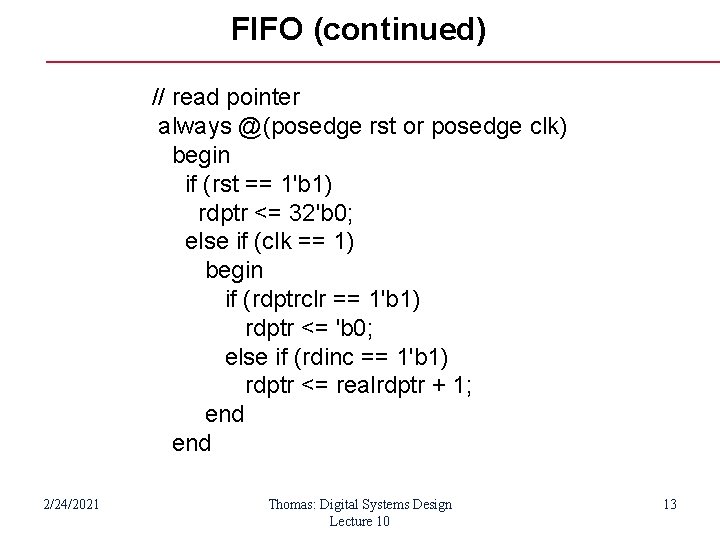

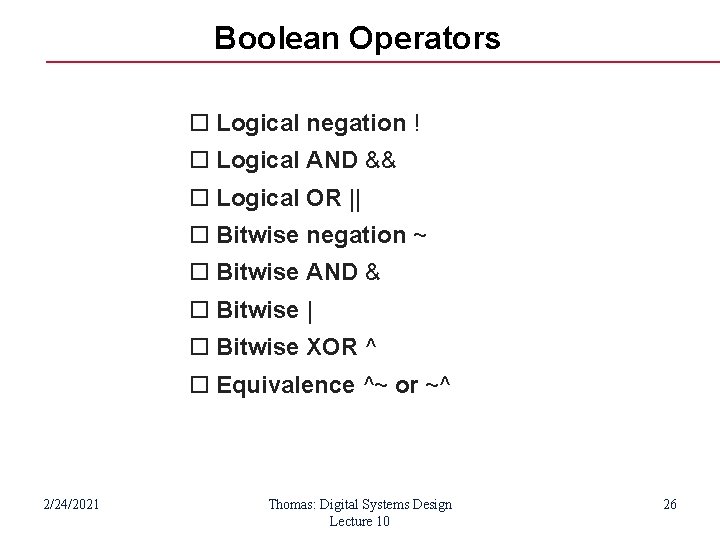

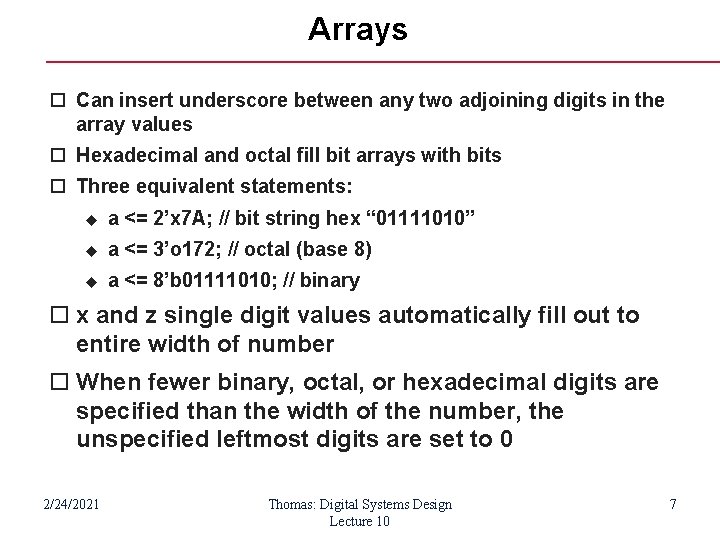

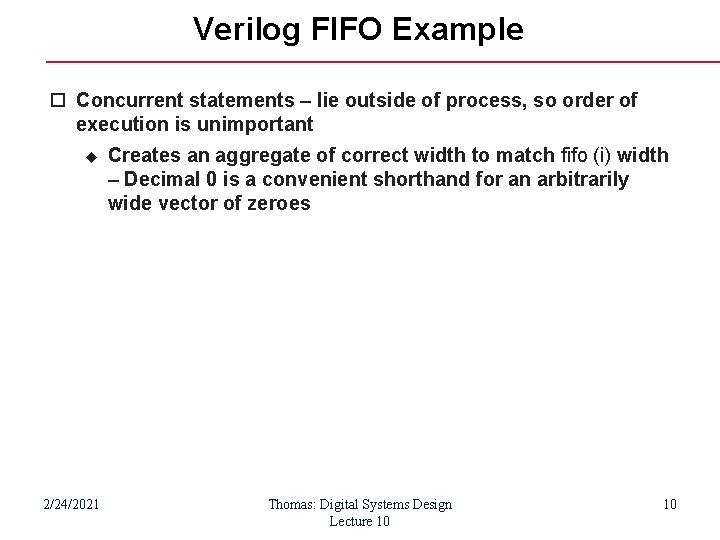

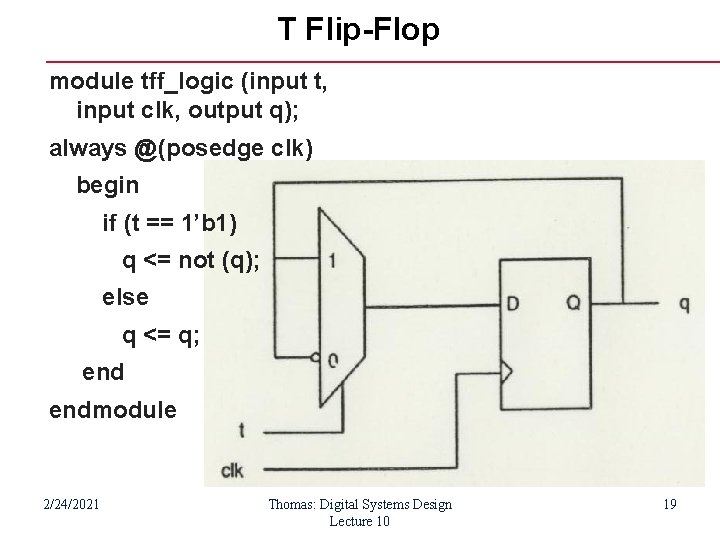

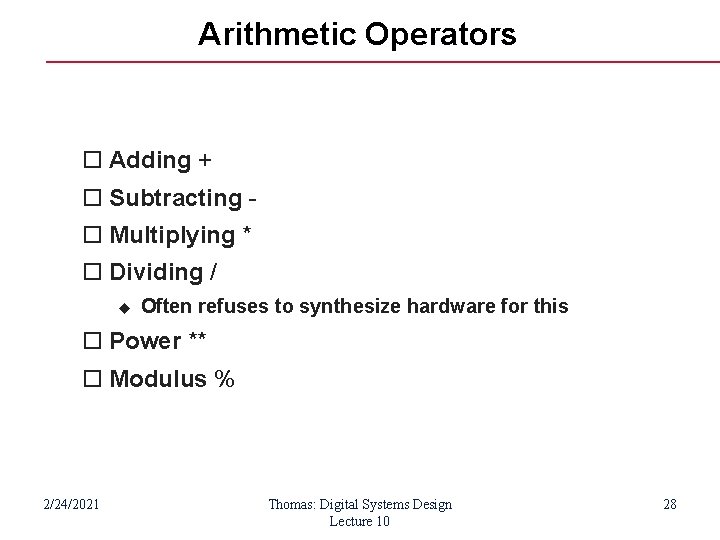

8 -bit Register, Asynchronous Reset, Synchronous Preset module reg_logic (input d [0: 7], input reset, input init, input clk, output q [0: 7]); always @(posedge clk, posedge reset) begin if (reset == 1’b 1) q <= 8’b 0; else begin if (init == 1’b 1) q <= 8’b 1111; // decimal -1 else q <= d; end endmodule 2/24/2021 Thomas: Digital Systems Design Lecture 10 22

Problems with Don’t Cares Synthesis treats x as a 1 that cannot occur Real hardware never has signals with x Comparing x to 0 or 1 with === operator always evaluates to false WHY? 2/24/2021 Because 0 or 1 does not EXACTLY match x Thomas: Digital Systems Design Lecture 10 23

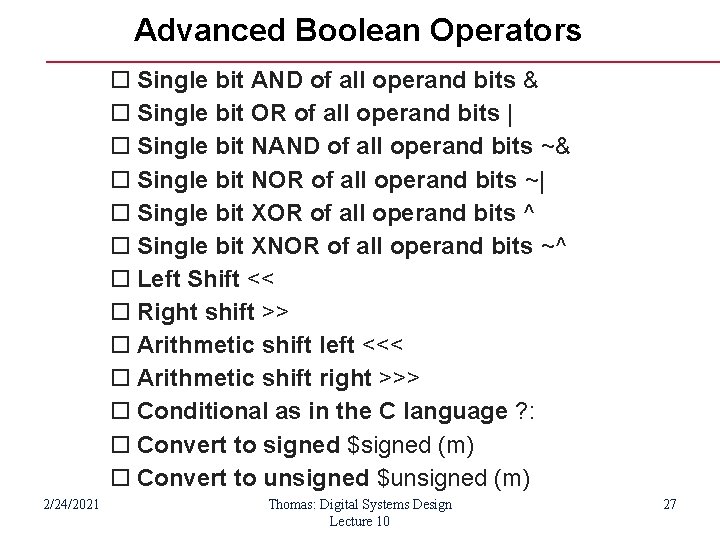

Verilog Relational Operators Obvious: ==, !=, <, <=, >, >= Unknown (x) or high-impedance (z) values are treated as 0 Case equality: === Unknown (x) or high-impedance (z) values must match exactly Case inequality: !== Unknown (x) or high-impedance (z) values must match exactly 2/24/2021 Thomas: Digital Systems Design Lecture 10 24

Concatenation Operator Collects multiple signals into an n-bit value {a, b, c, d} 2/24/2021 Aggregates 4 signals a, b, c, d into a 4 -bit value in the order specified Thomas: Digital Systems Design Lecture 10 25

Boolean Operators Logical negation ! Logical AND && Logical OR || Bitwise negation ~ Bitwise AND & Bitwise | Bitwise XOR ^ Equivalence ^~ or ~^ 2/24/2021 Thomas: Digital Systems Design Lecture 10 26

Advanced Boolean Operators Single bit AND of all operand bits & Single bit OR of all operand bits | Single bit NAND of all operand bits ~& Single bit NOR of all operand bits ~| Single bit XOR of all operand bits ^ Single bit XNOR of all operand bits ~^ Left Shift << Right shift >> Arithmetic shift left <<< Arithmetic shift right >>> Conditional as in the C language ? : Convert to signed $signed (m) Convert to unsigned $unsigned (m) 2/24/2021 Thomas: Digital Systems Design Lecture 10 27

Arithmetic Operators Adding + Subtracting Multiplying * Dividing / Often refuses to synthesize hardware for this Power ** Modulus % 2/24/2021 Thomas: Digital Systems Design Lecture 10 28

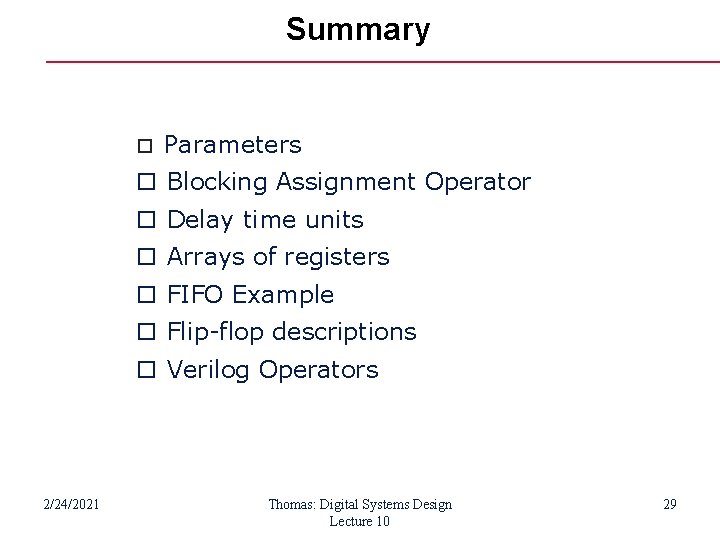

Summary Parameters Blocking Assignment Operator Delay time units Arrays of registers FIFO Example Flip-flop descriptions Verilog Operators 2/24/2021 Thomas: Digital Systems Design Lecture 10 29