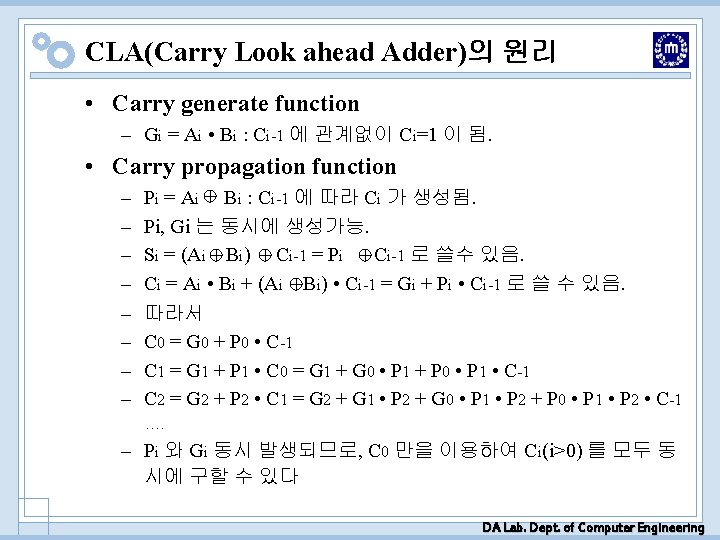

32 CLA RCARipple Carry Adder Simple but slow

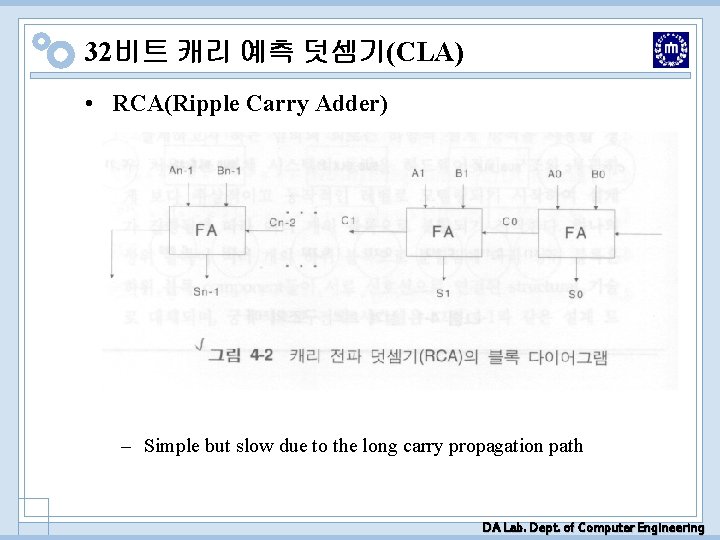

32비트 캐리 예측 덧셈기(CLA) • RCA(Ripple Carry Adder) – Simple but slow due to the long carry propagation path DA Lab. Dept. of Computer Engineering

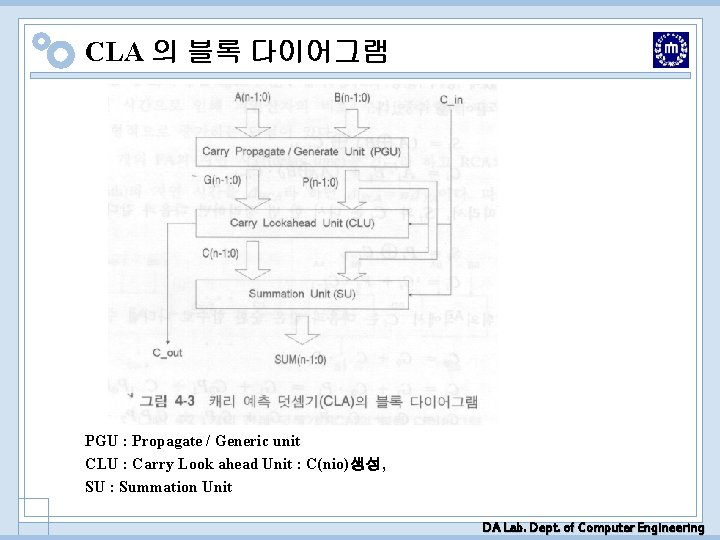

CLA 의 블록 다이어그램 PGU : Propagate / Generic unit CLU : Carry Look ahead Unit : C(nio)생성, SU : Summation Unit DA Lab. Dept. of Computer Engineering

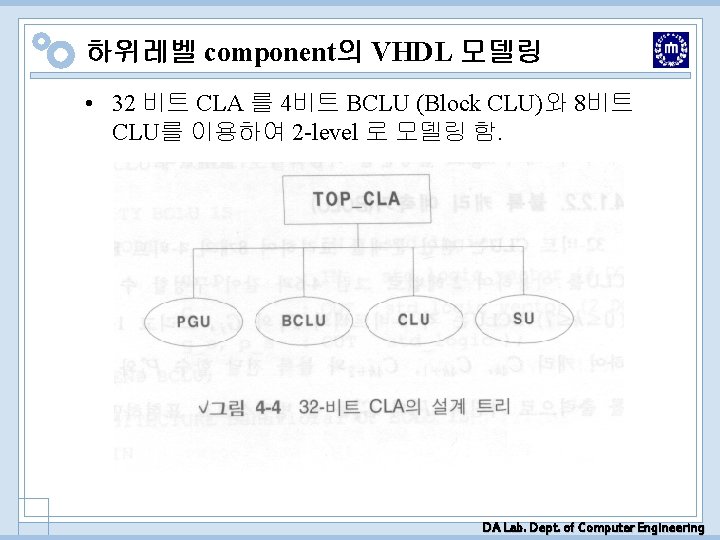

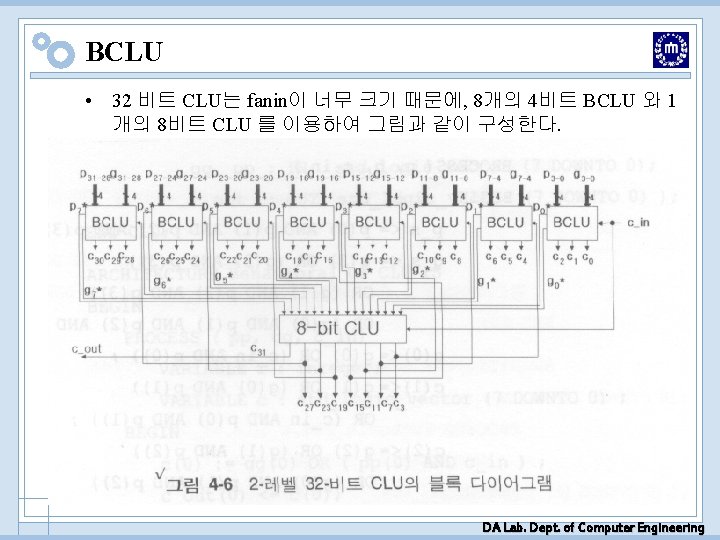

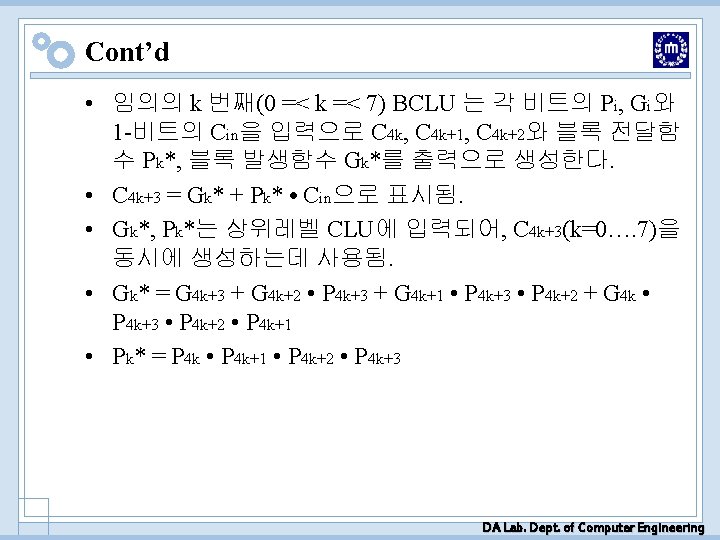

하위레벨 component의 VHDL 모델링 • 32 비트 CLA 를 4비트 BCLU (Block CLU)와 8비트 CLU를 이용하여 2 -level 로 모델링 함. DA Lab. Dept. of Computer Engineering

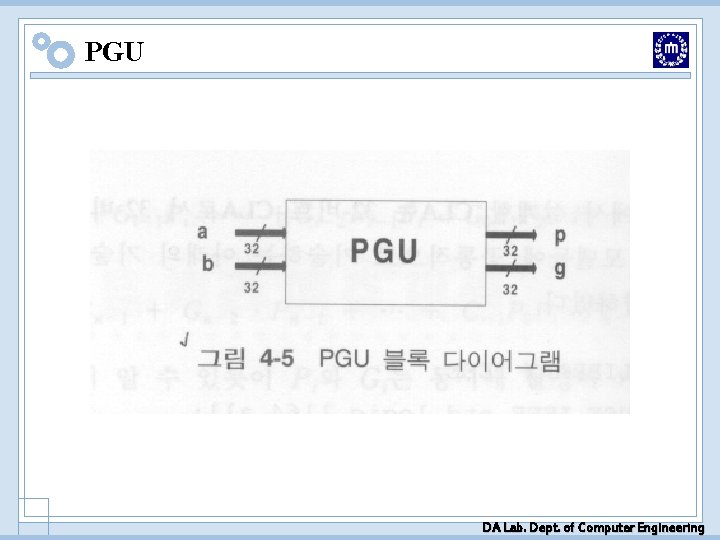

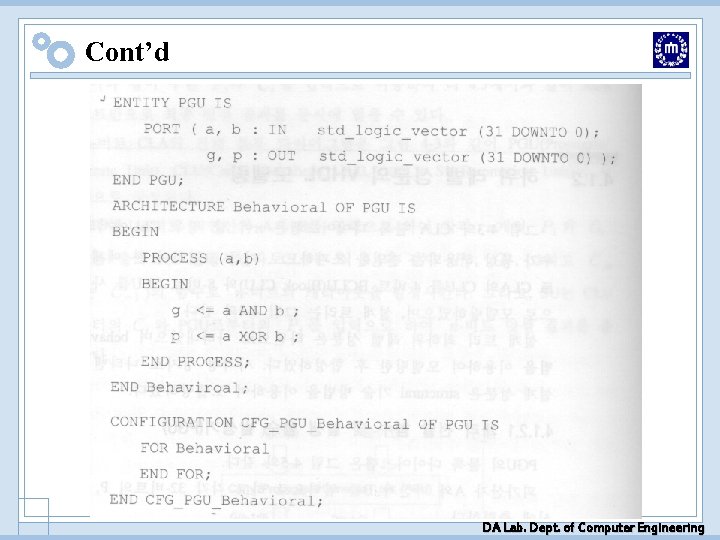

PGU DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

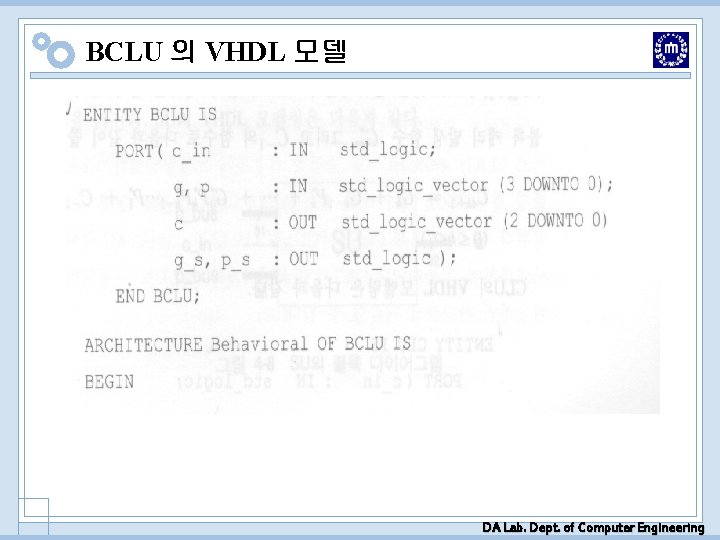

BCLU 의 VHDL 모델 DA Lab. Dept. of Computer Engineering

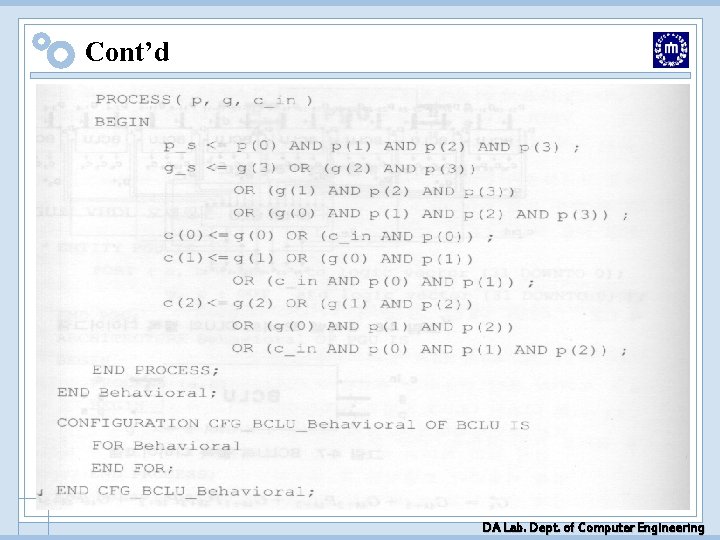

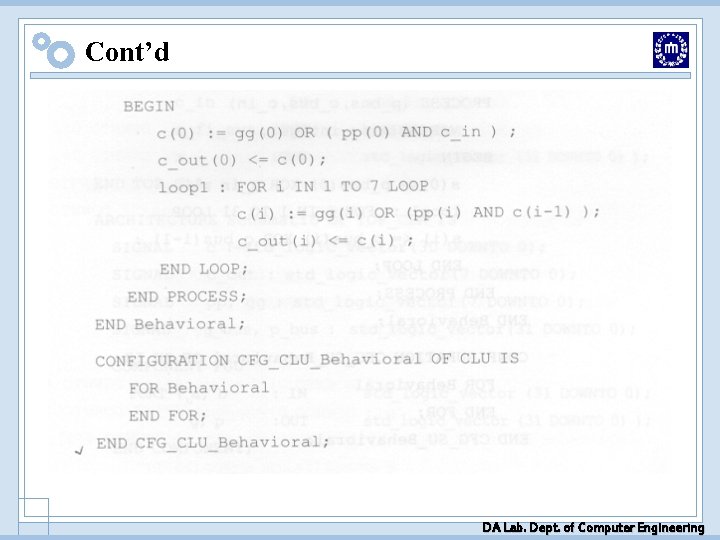

Cont’d DA Lab. Dept. of Computer Engineering

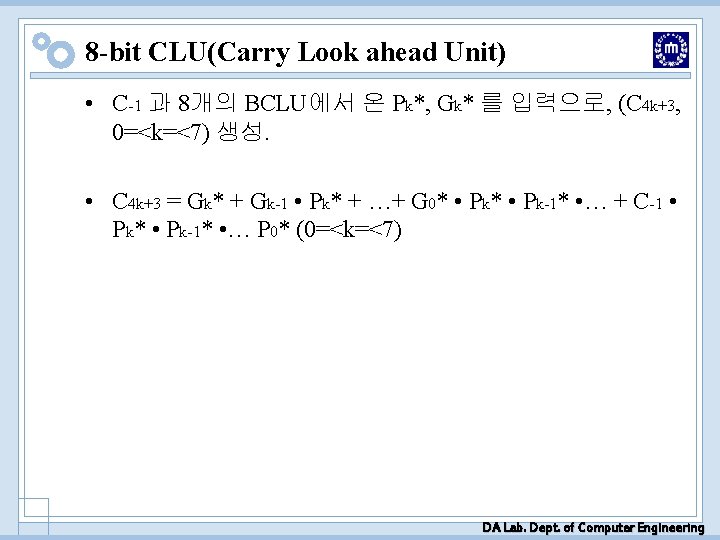

8 -bit CLU(Carry Look ahead Unit) • C-1 과 8개의 BCLU에서 온 Pk*, Gk* 를 입력으로, (C 4 k+3, 0=<k=<7) 생성. • C 4 k+3 = Gk* + Gk-1 • Pk* + …+ G 0* • Pk-1* • … + C-1 • Pk* • Pk-1* • … P 0* (0=<k=<7) DA Lab. Dept. of Computer Engineering

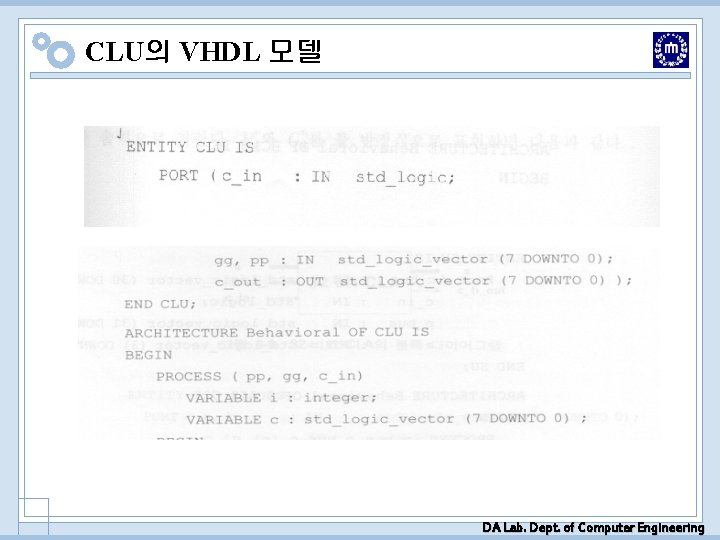

CLU의 VHDL 모델 DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

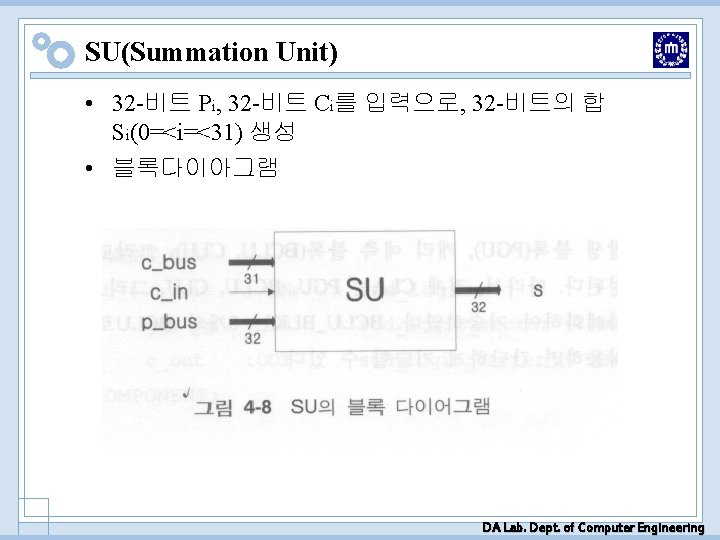

SU(Summation Unit) • 32 -비트 Pi, 32 -비트 Ci를 입력으로, 32 -비트의 합 Si(0=<i=<31) 생성 • 블록다이아그램 DA Lab. Dept. of Computer Engineering

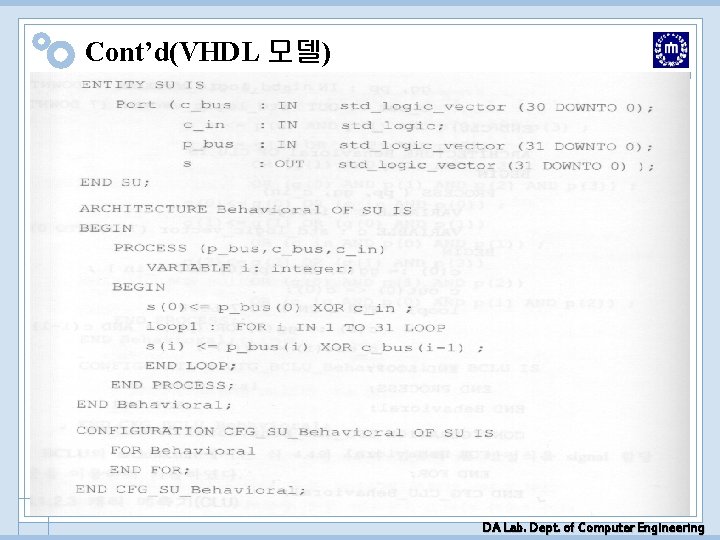

Cont’d(VHDL 모델) DA Lab. Dept. of Computer Engineering

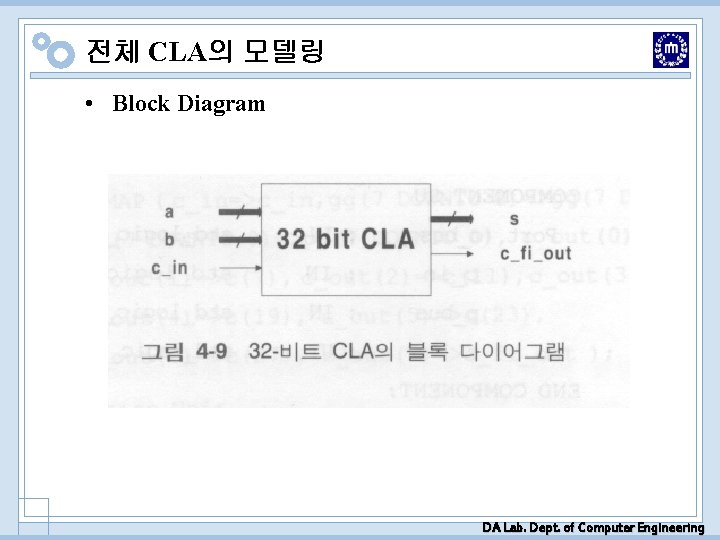

전체 CLA의 모델링 • Block Diagram DA Lab. Dept. of Computer Engineering

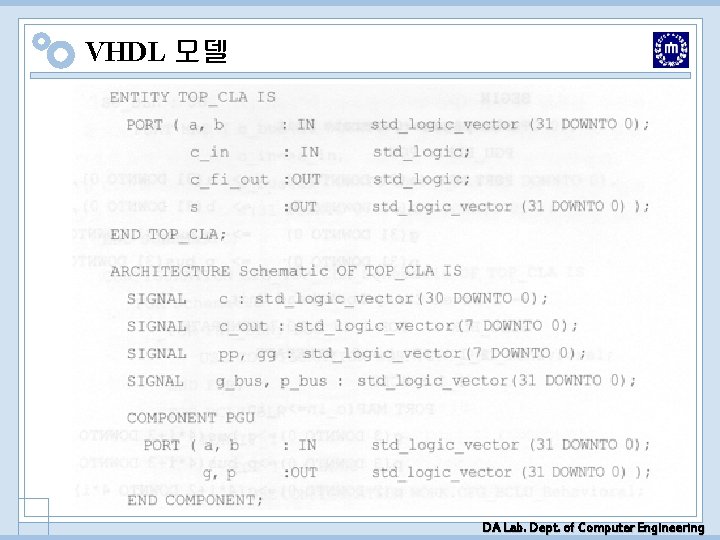

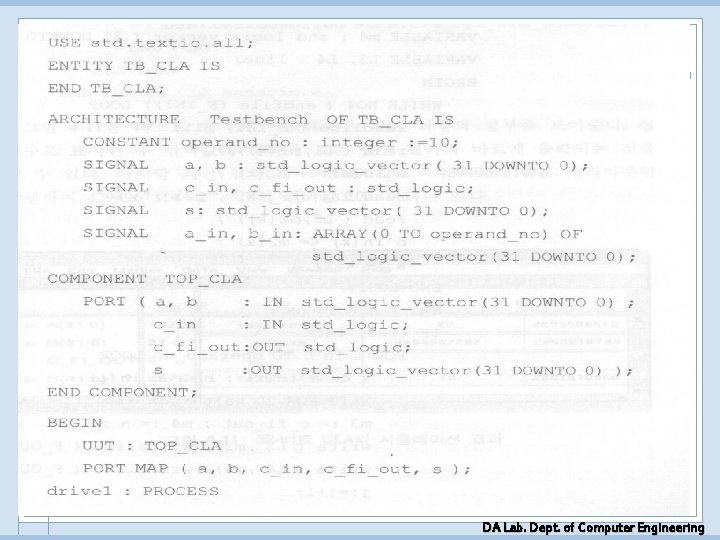

VHDL 모델 DA Lab. Dept. of Computer Engineering

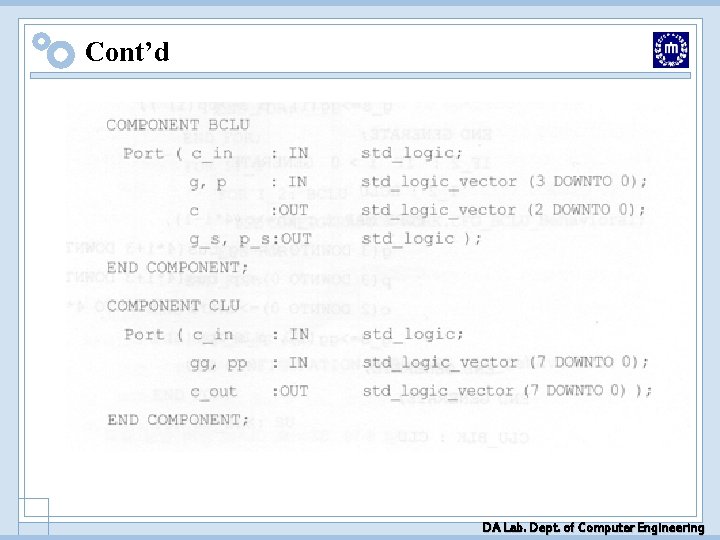

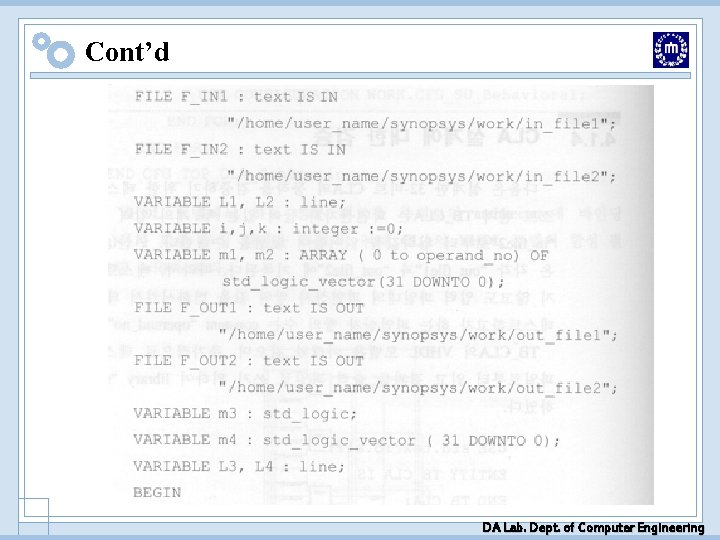

Cont’d DA Lab. Dept. of Computer Engineering

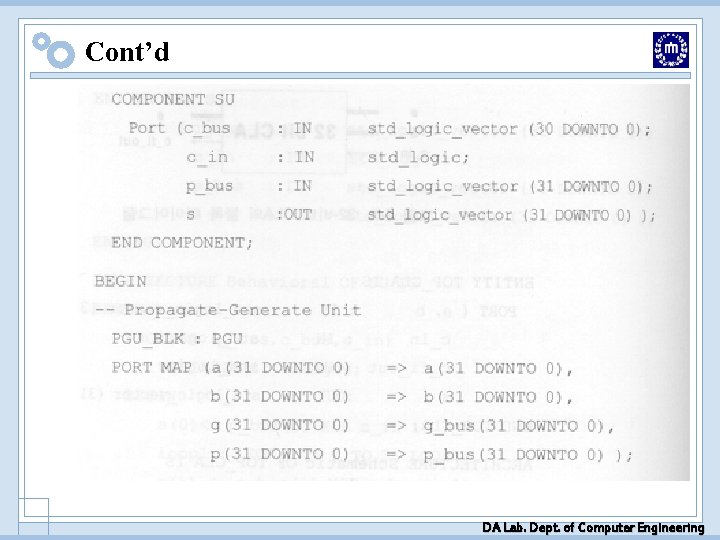

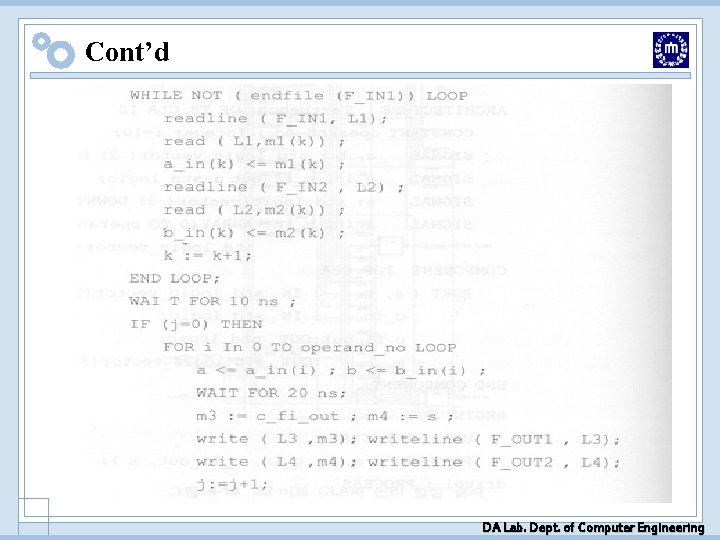

Cont’d DA Lab. Dept. of Computer Engineering

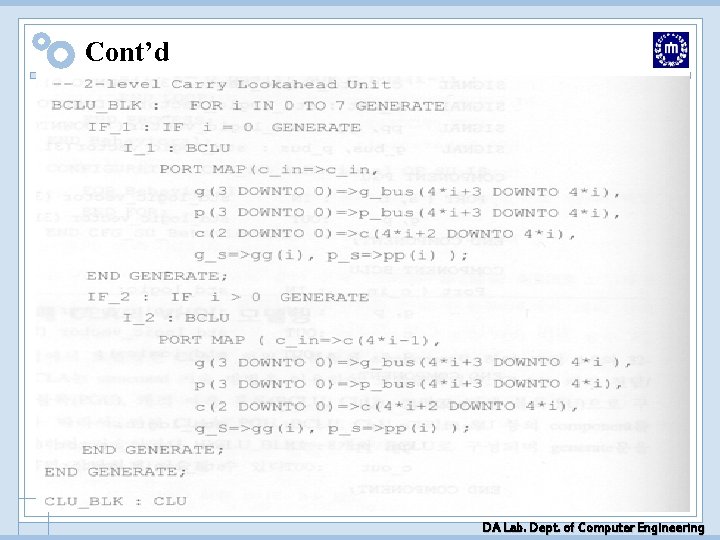

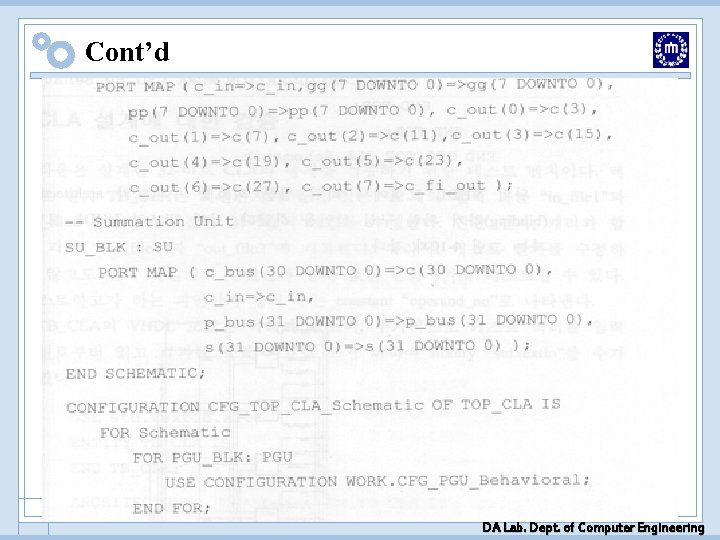

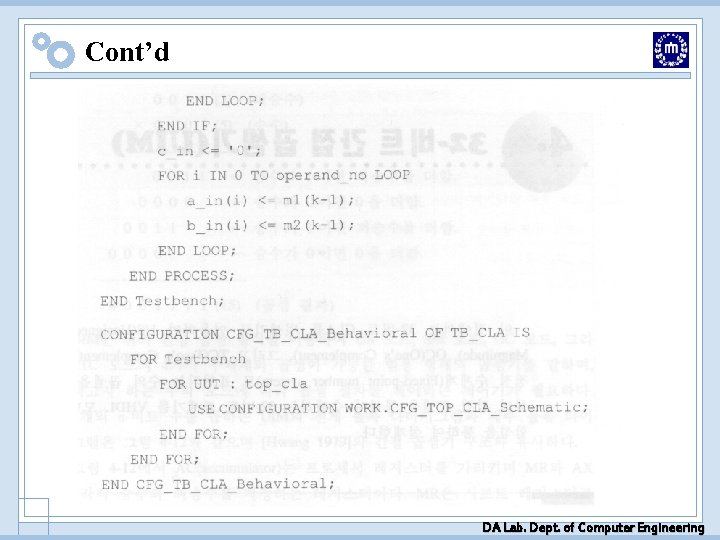

Cont’d DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

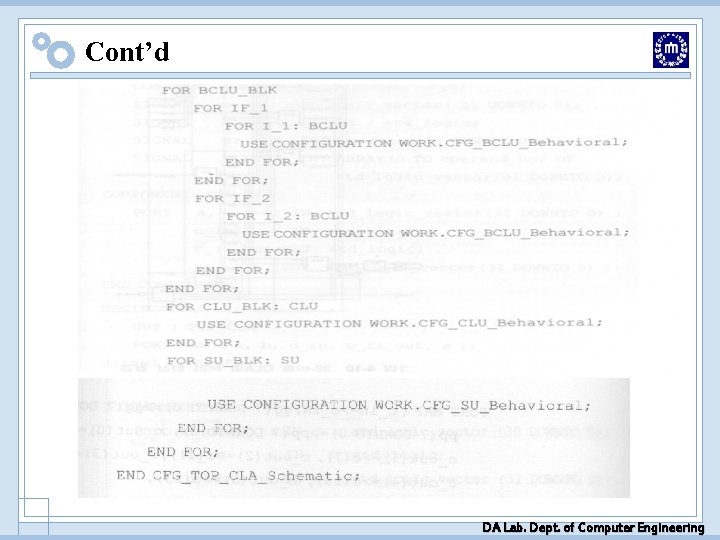

Cont’d DA Lab. Dept. of Computer Engineering

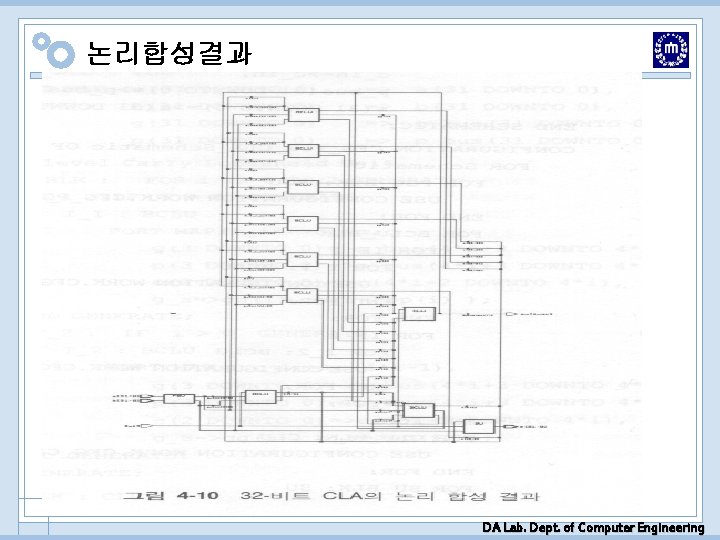

논리합성결과 DA Lab. Dept. of Computer Engineering

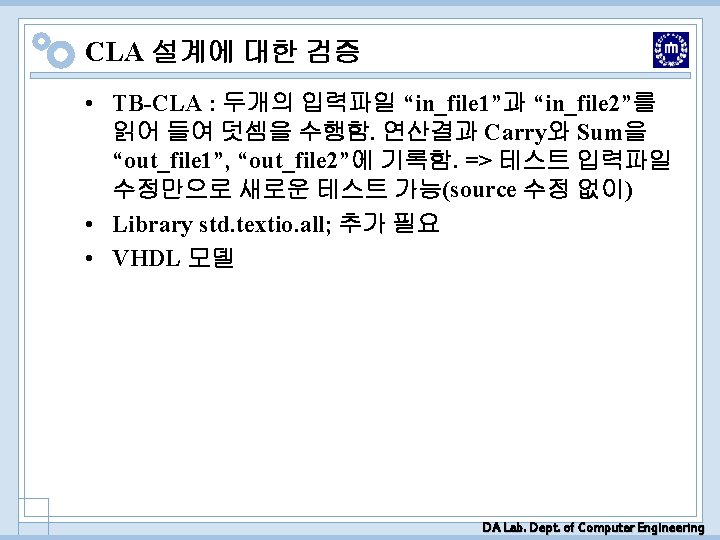

Cont’d DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

Cont’d DA Lab. Dept. of Computer Engineering

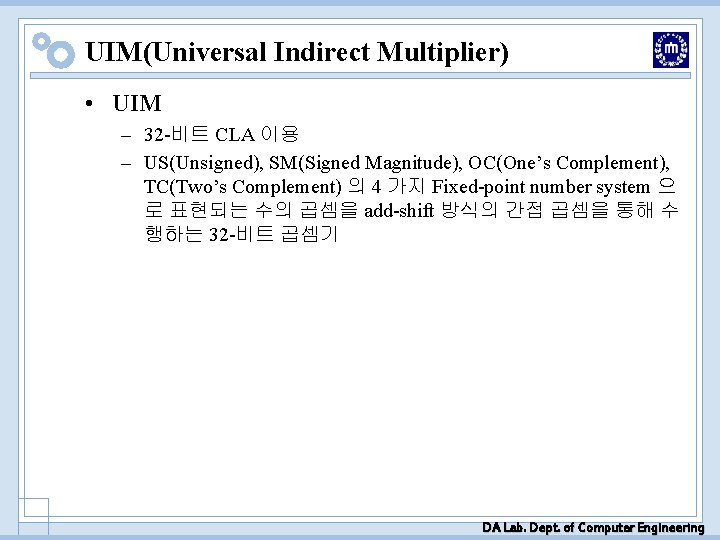

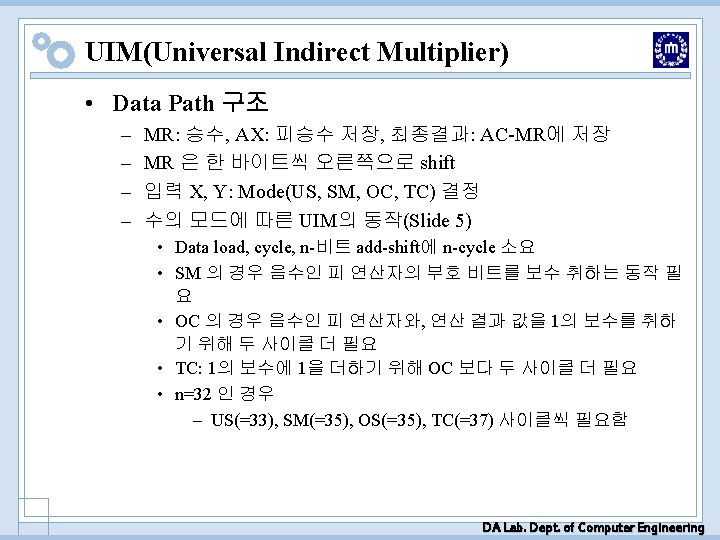

UIM(Universal Indirect Multiplier) • UIM – 32 -비트 CLA 이용 – US(Unsigned), SM(Signed Magnitude), OC(One’s Complement), TC(Two’s Complement) 의 4 가지 Fixed-point number system 으 로 표현되는 수의 곱셈을 add-shift 방식의 간접 곱셈을 통해 수 행하는 32 -비트 곱셈기 DA Lab. Dept. of Computer Engineering

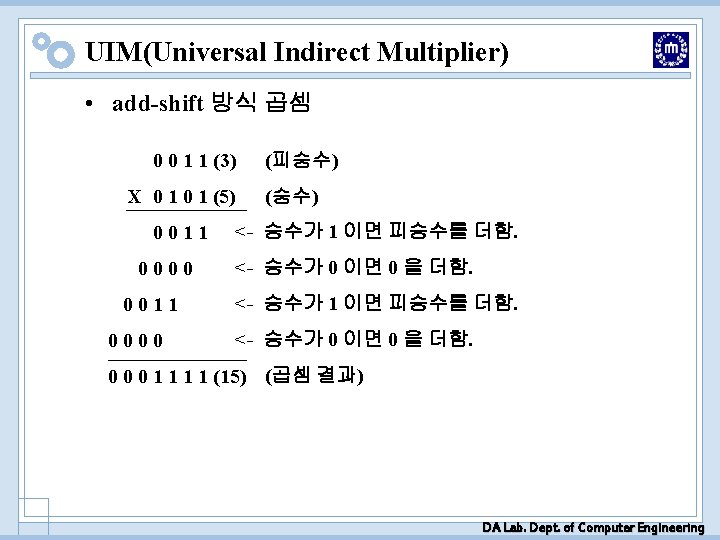

UIM(Universal Indirect Multiplier) • add-shift 방식 곱셈 0 0 1 1 (3) X 0 1 (5) 0011 0000 (피승수) (승수) <- 승수가 1 이면 피승수를 더함. <- 승수가 0 이면 0 을 더함. 0 0 0 1 1 (15) (곱셈 결과) DA Lab. Dept. of Computer Engineering

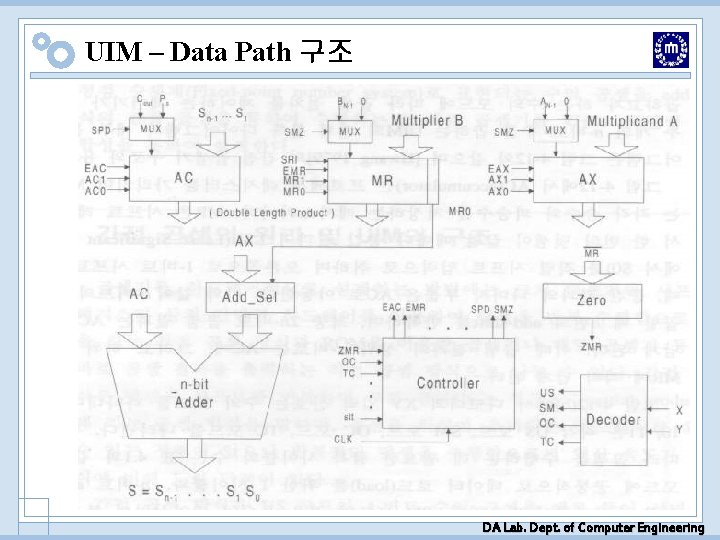

UIM – Data Path 구조 DA Lab. Dept. of Computer Engineering

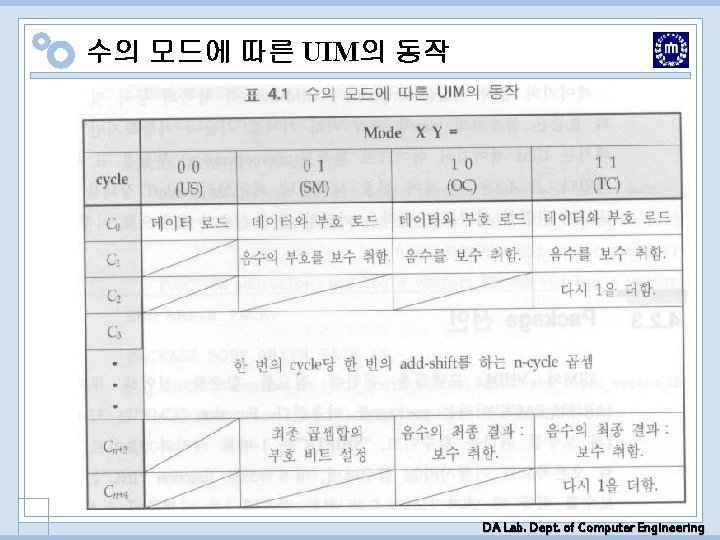

수의 모드에 따른 UIM의 동작 DA Lab. Dept. of Computer Engineering

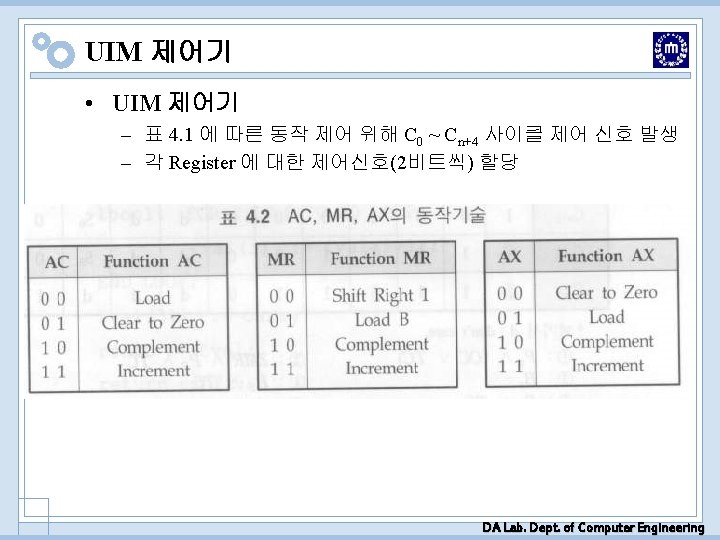

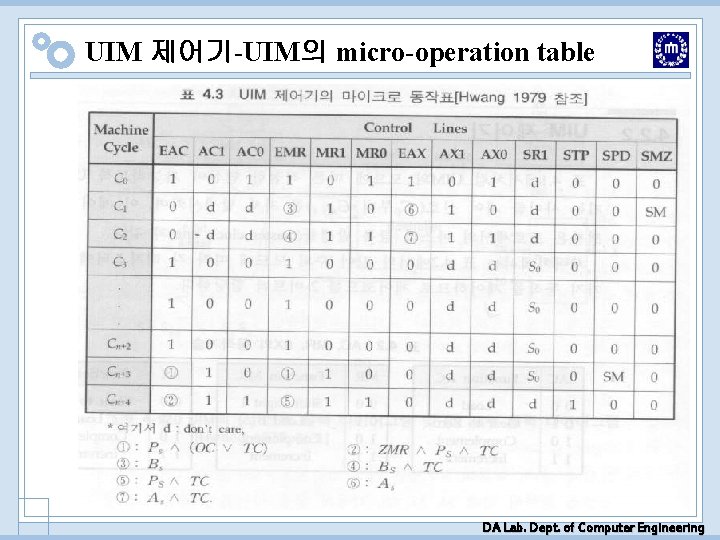

UIM 제어기-UIM의 micro-operation table DA Lab. Dept. of Computer Engineering

![Package 선언[VHDL 소스] DA Lab. Dept. of Computer Engineering Package 선언[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-37.jpg)

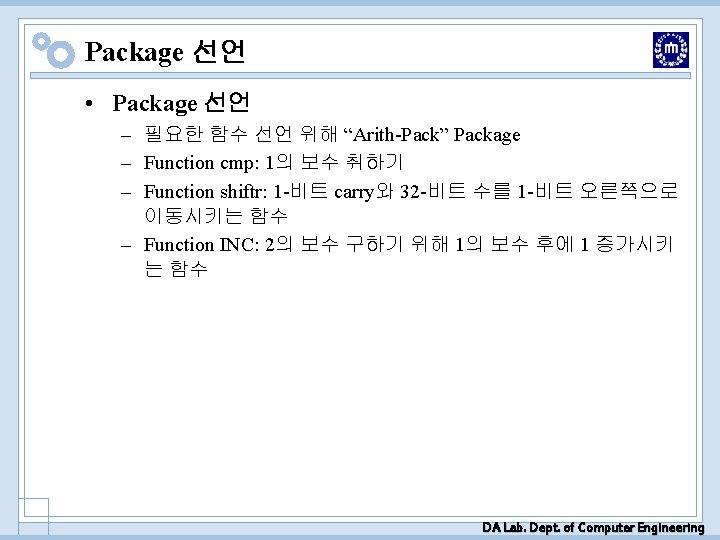

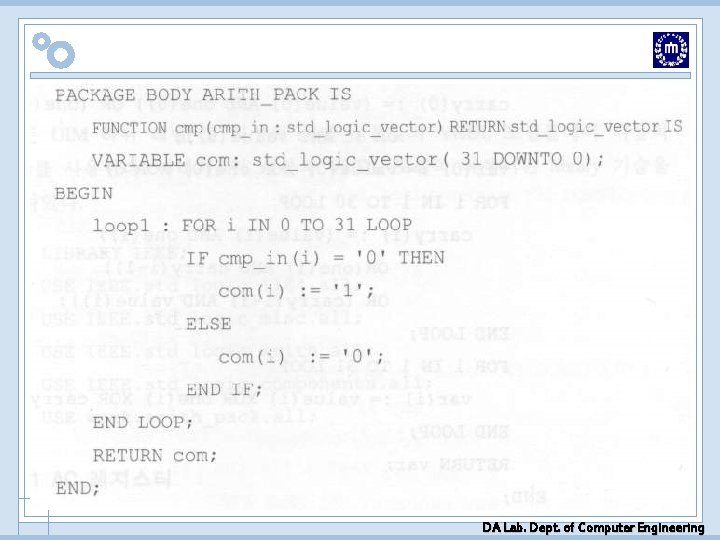

Package 선언[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

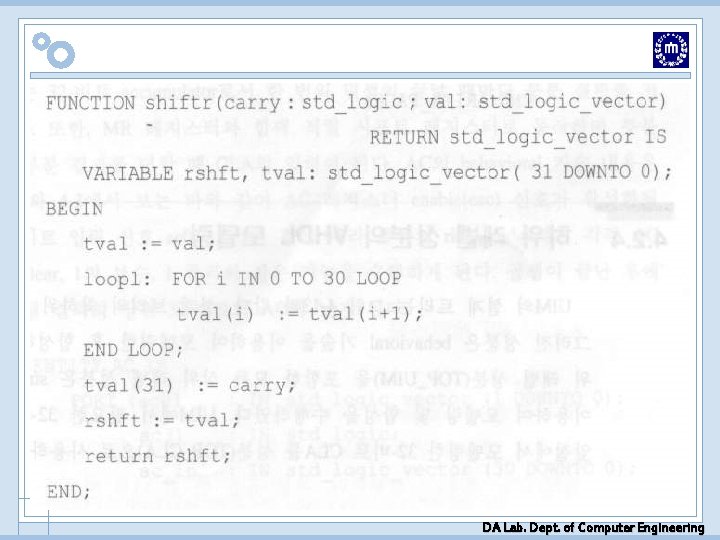

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

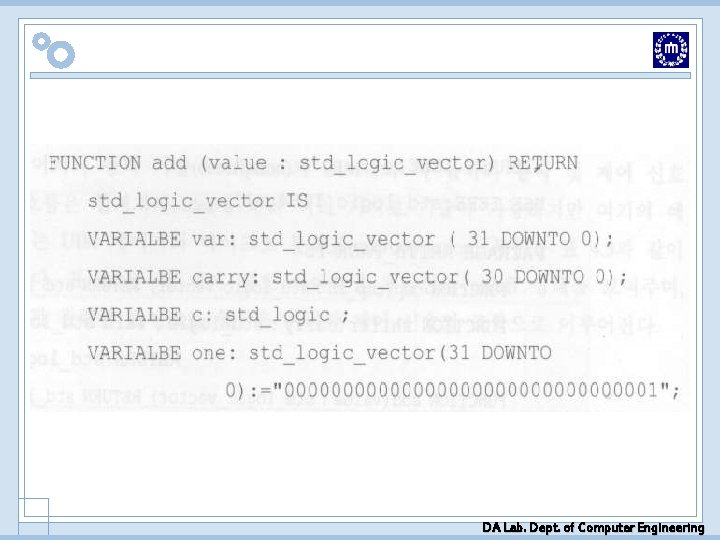

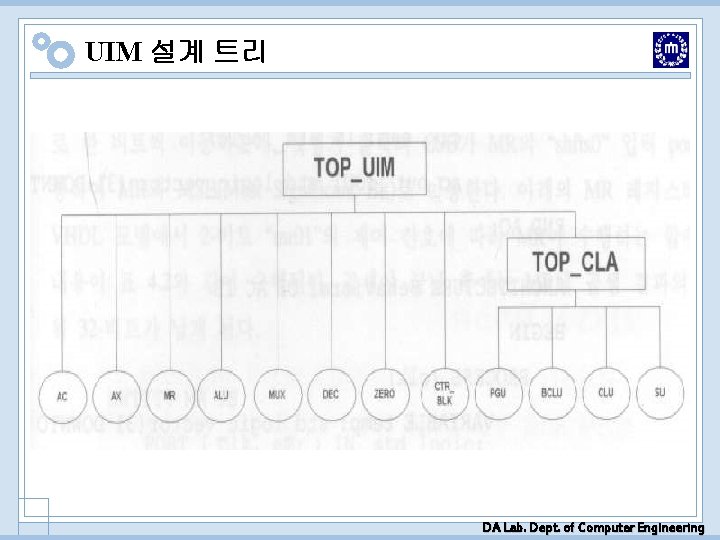

UIM 설계 트리 DA Lab. Dept. of Computer Engineering

![AC 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering AC 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-44.jpg)

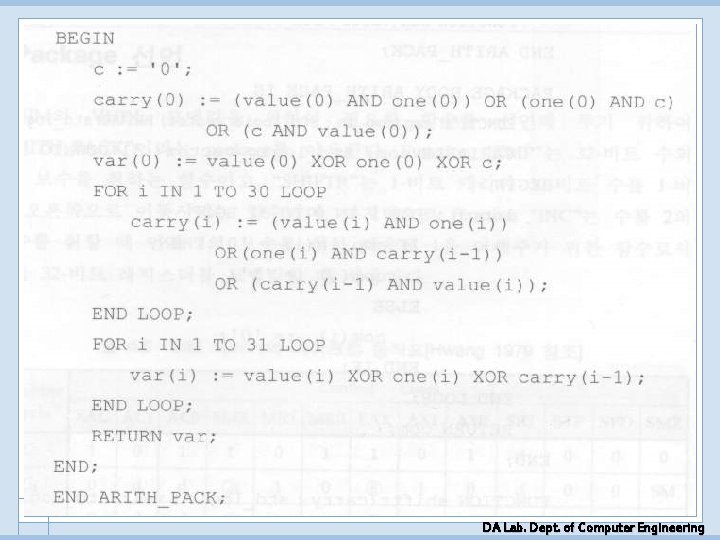

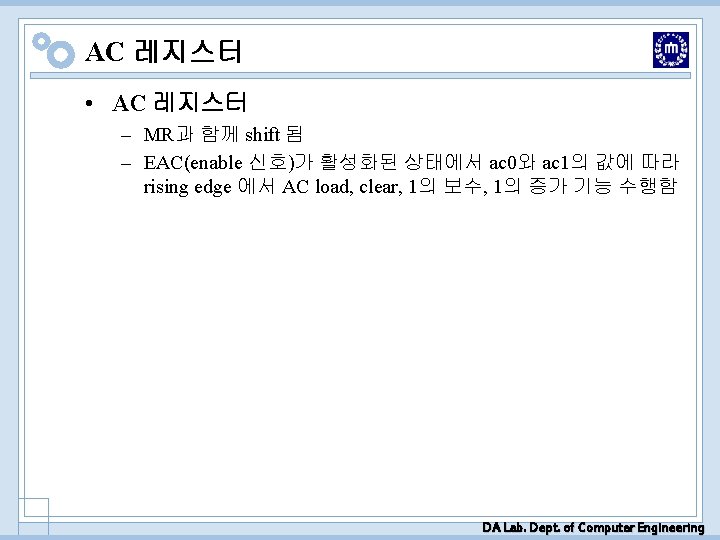

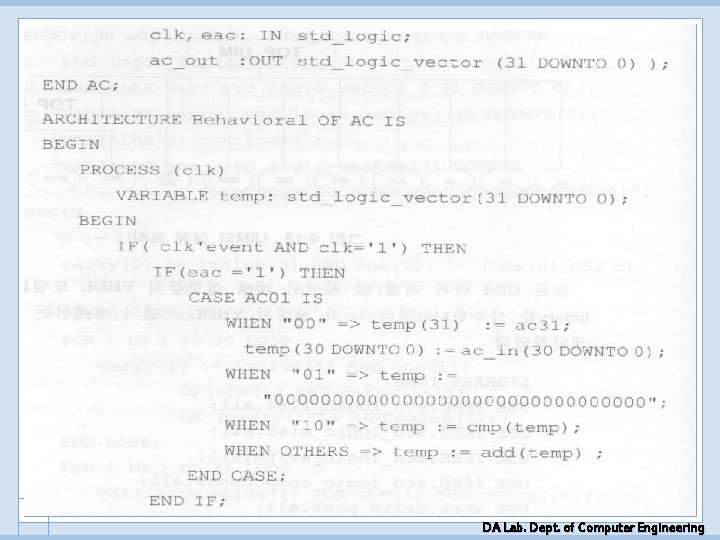

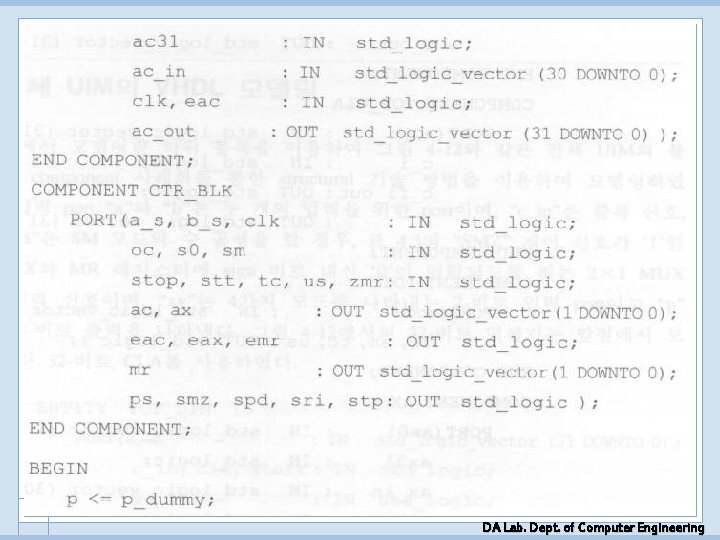

AC 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering

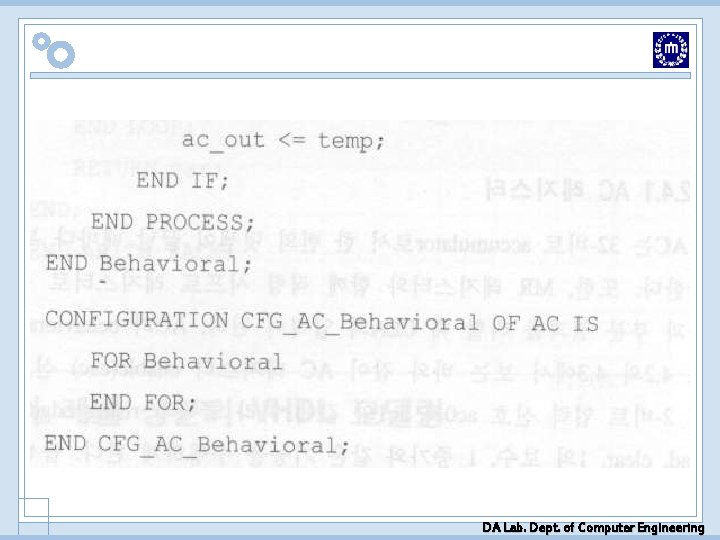

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![MR 레지스터: 승수저장, 부분 곱 하위 부분 저장[VHDL 소스] DA Lab. Dept. of Computer MR 레지스터: 승수저장, 부분 곱 하위 부분 저장[VHDL 소스] DA Lab. Dept. of Computer](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-47.jpg)

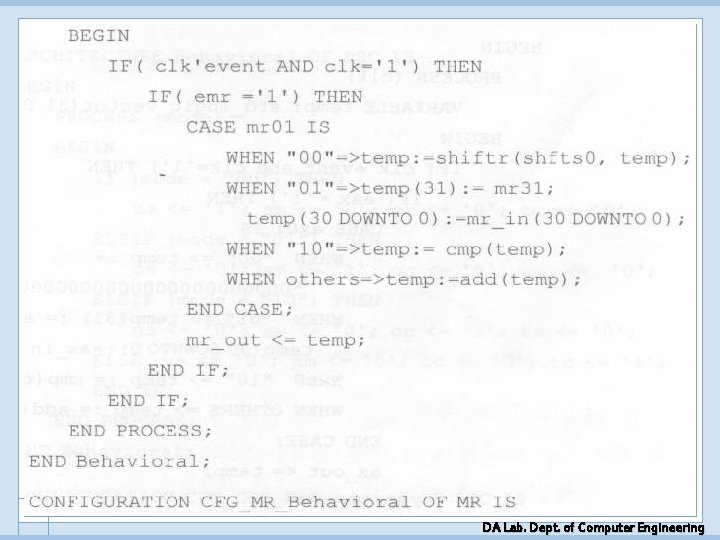

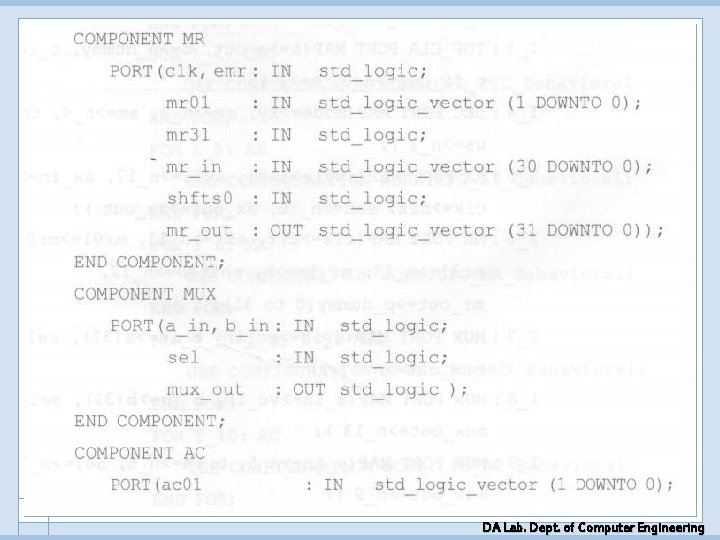

MR 레지스터: 승수저장, 부분 곱 하위 부분 저장[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![AX 레지스터: 피 승수 저장[VHDL 소스] DA Lab. Dept. of Computer Engineering AX 레지스터: 피 승수 저장[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-50.jpg)

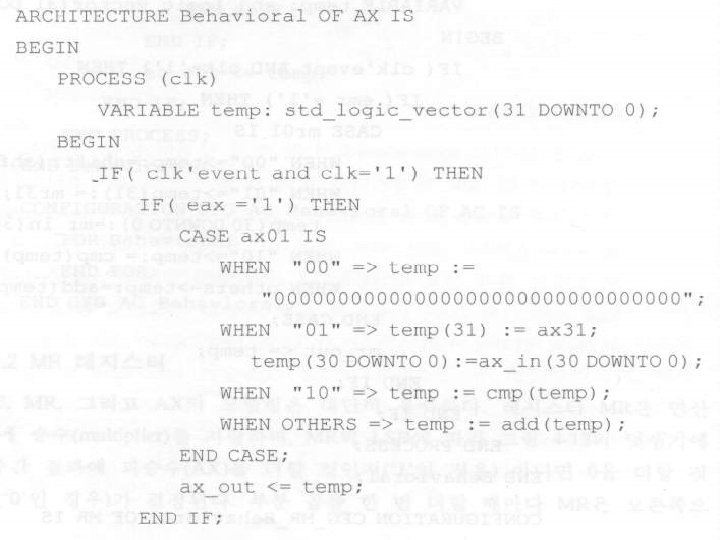

AX 레지스터: 피 승수 저장[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![DEC(디코더): mode(X, Y) -> US, SM, TC, OC 생성[VHDL 소스 ] DA Lab. Dept. DEC(디코더): mode(X, Y) -> US, SM, TC, OC 생성[VHDL 소스 ] DA Lab. Dept.](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-53.jpg)

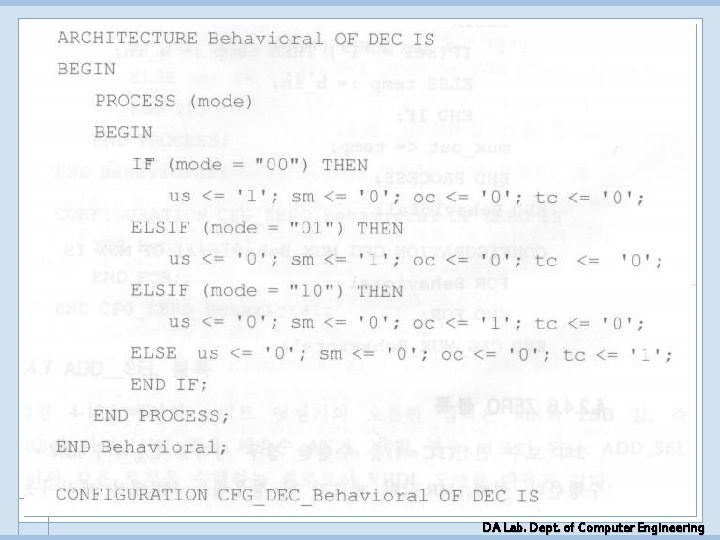

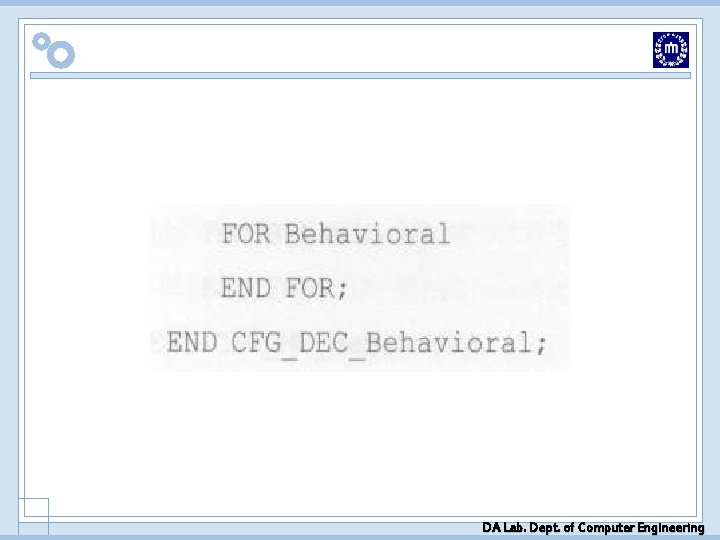

DEC(디코더): mode(X, Y) -> US, SM, TC, OC 생성[VHDL 소스 ] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![MUX(멀티 플렉서): 2 -to-1[VHDL 소스] DA Lab. Dept. of Computer Engineering MUX(멀티 플렉서): 2 -to-1[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-56.jpg)

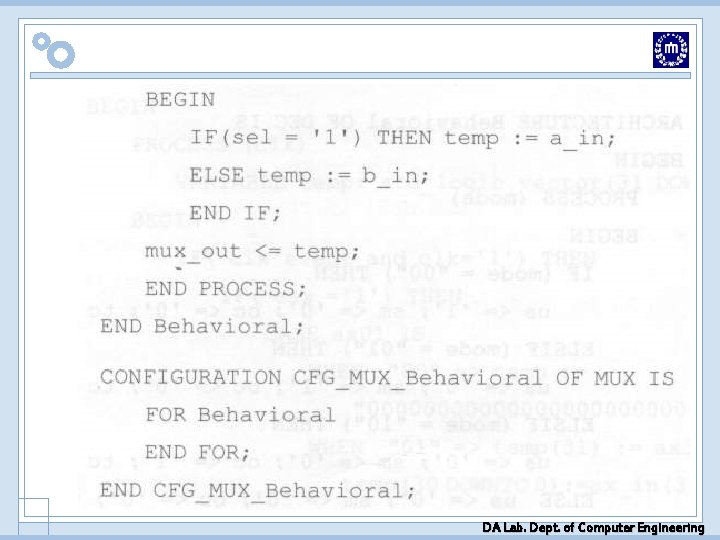

MUX(멀티 플렉서): 2 -to-1[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![ZERO 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering ZERO 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-59.jpg)

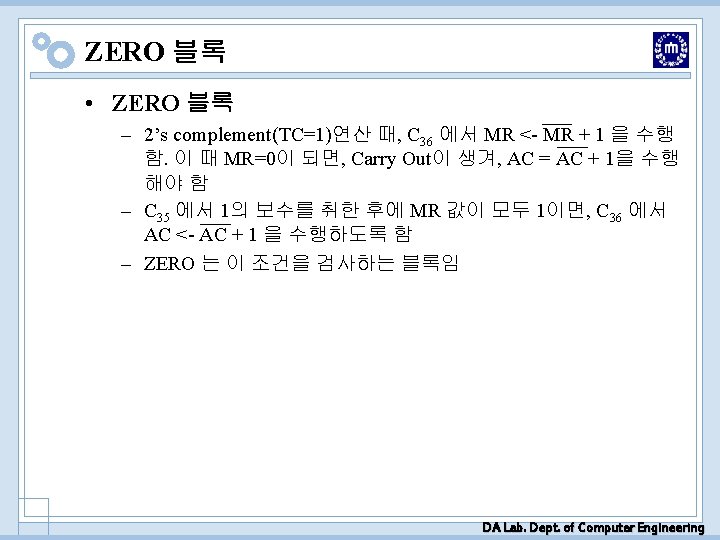

ZERO 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

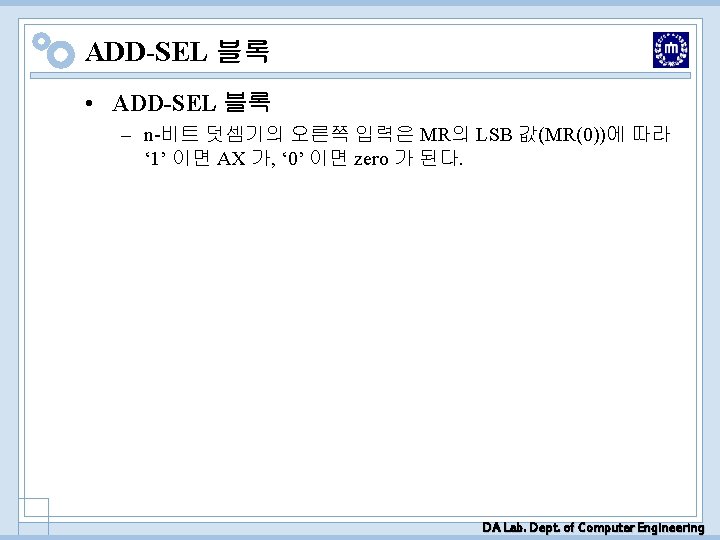

![ADD-SEL 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering ADD-SEL 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-62.jpg)

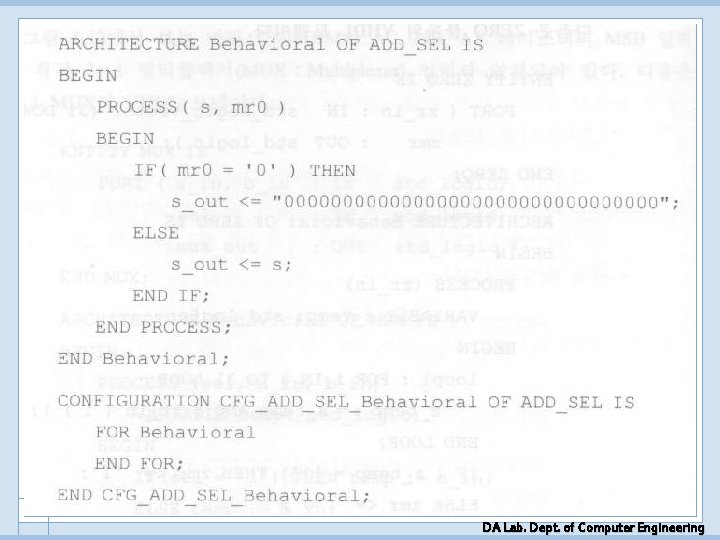

ADD-SEL 블록[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

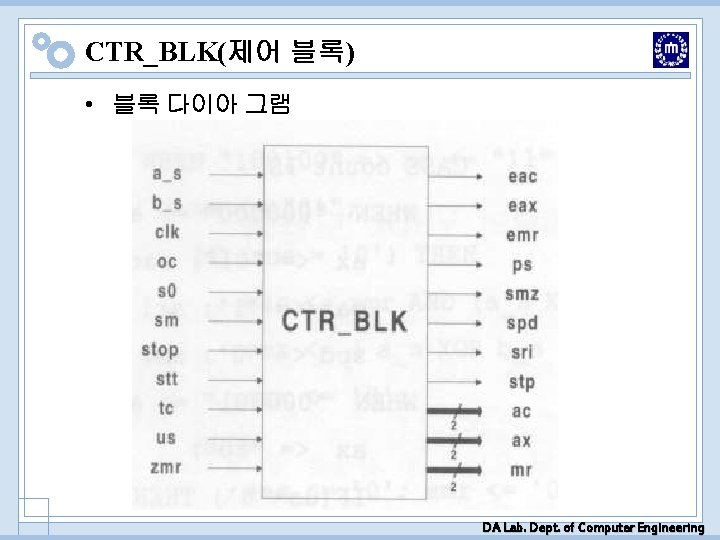

CTR_BLK(제어 블록) • 블록 다이아 그램 DA Lab. Dept. of Computer Engineering

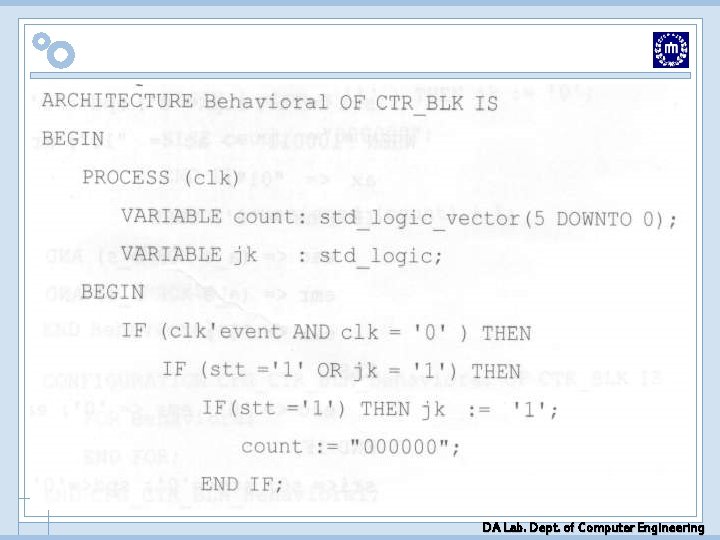

![CTR_BLK(제어 블록)[VHDL 모델] DA Lab. Dept. of Computer Engineering CTR_BLK(제어 블록)[VHDL 모델] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-65.jpg)

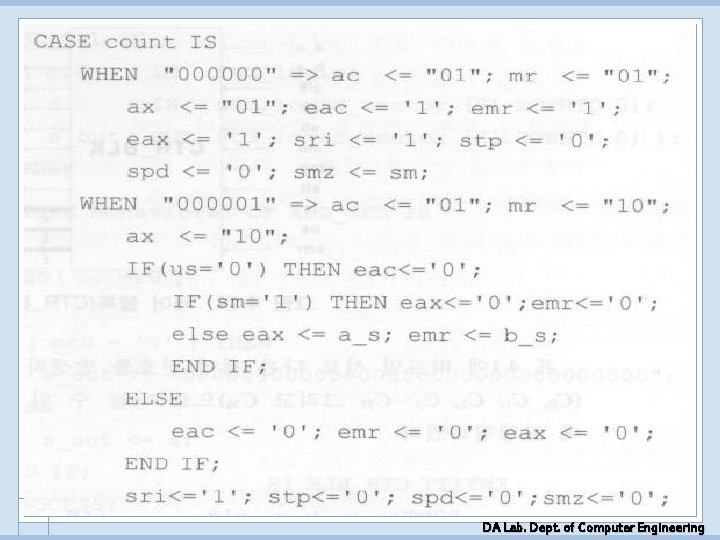

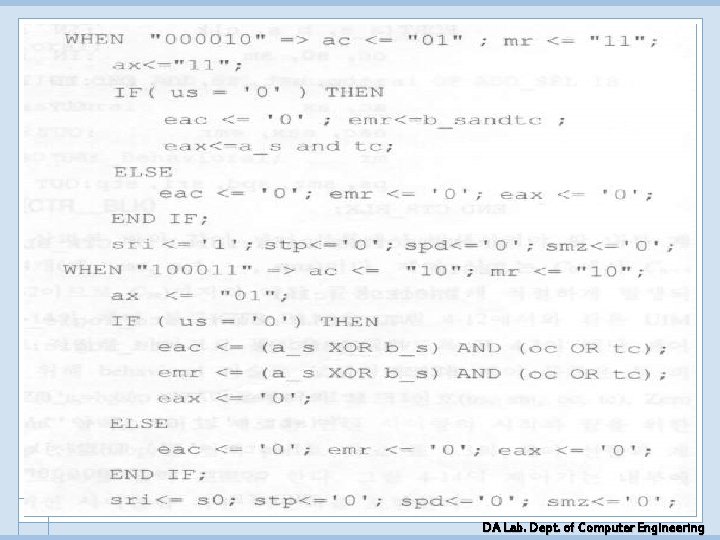

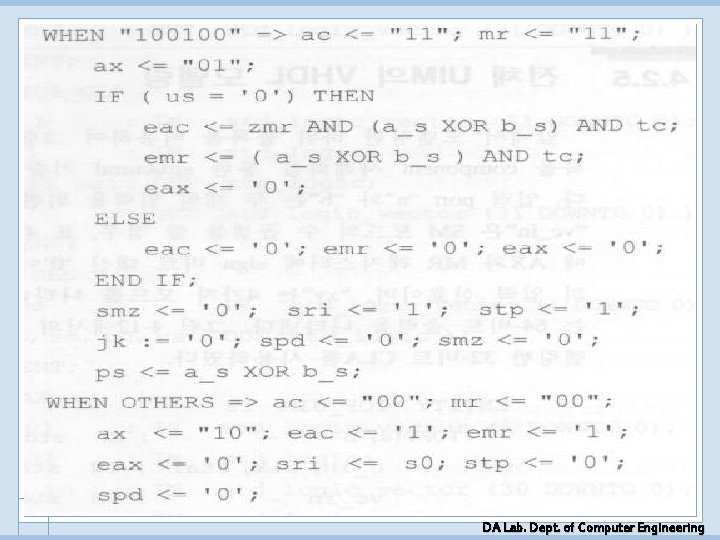

CTR_BLK(제어 블록)[VHDL 모델] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

![UIM 전체 VHDL 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering UIM 전체 VHDL 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering](http://slidetodoc.com/presentation_image_h/376a3d296eaff3c89bebda82f6c8eb7f/image-72.jpg)

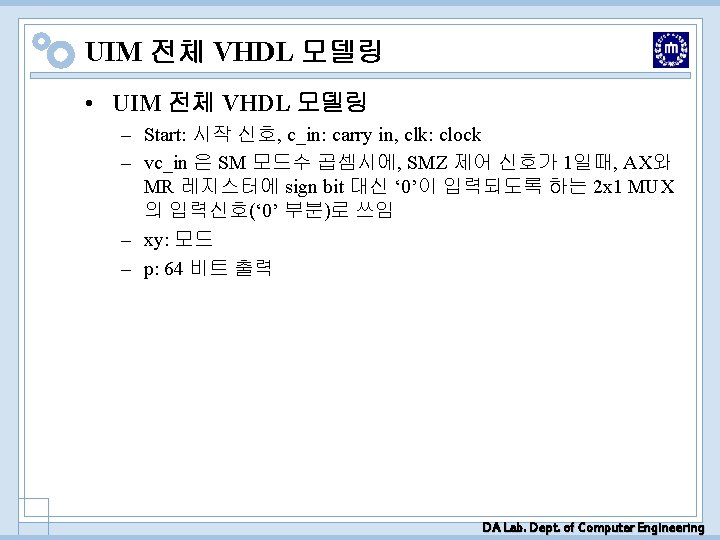

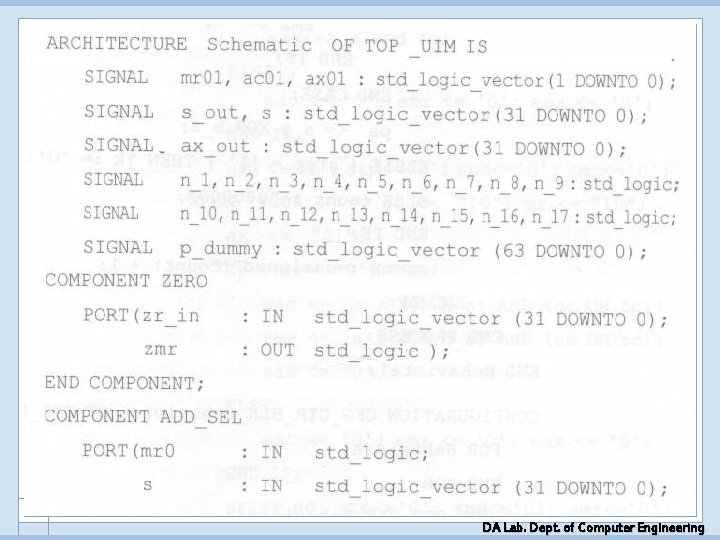

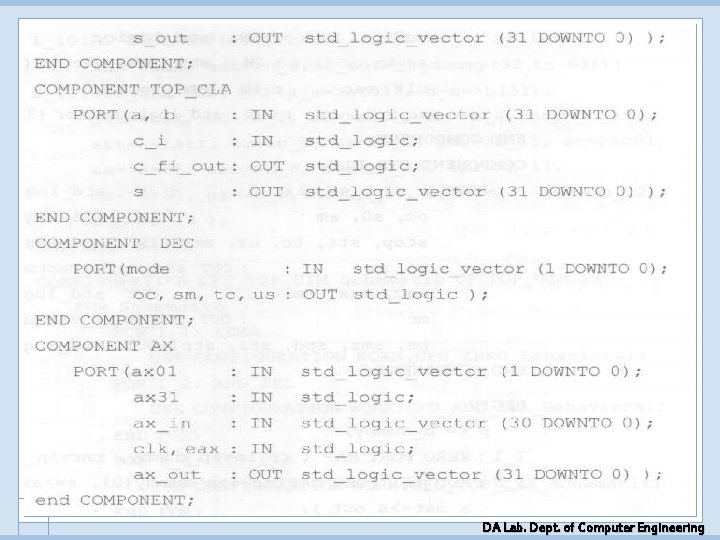

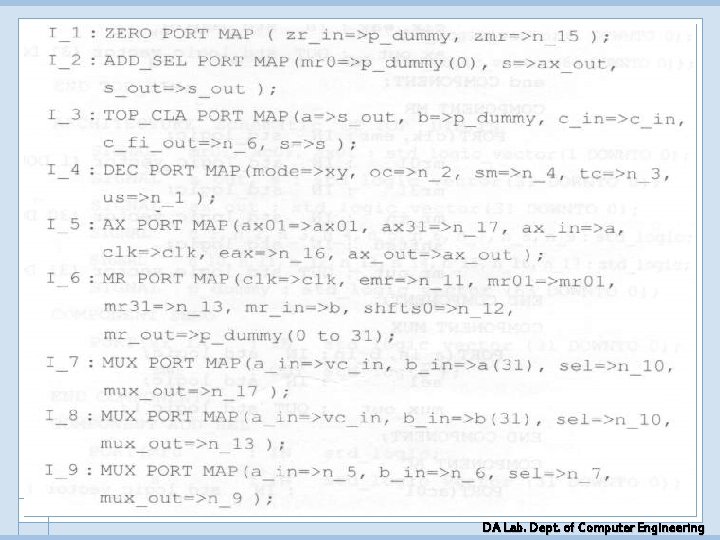

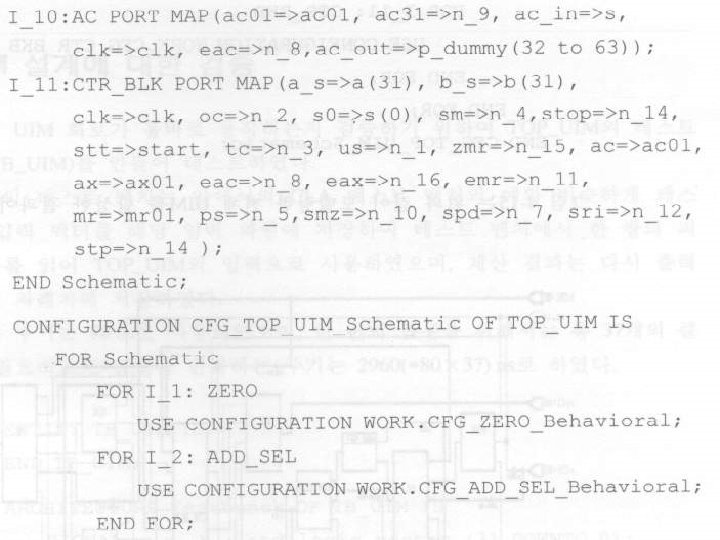

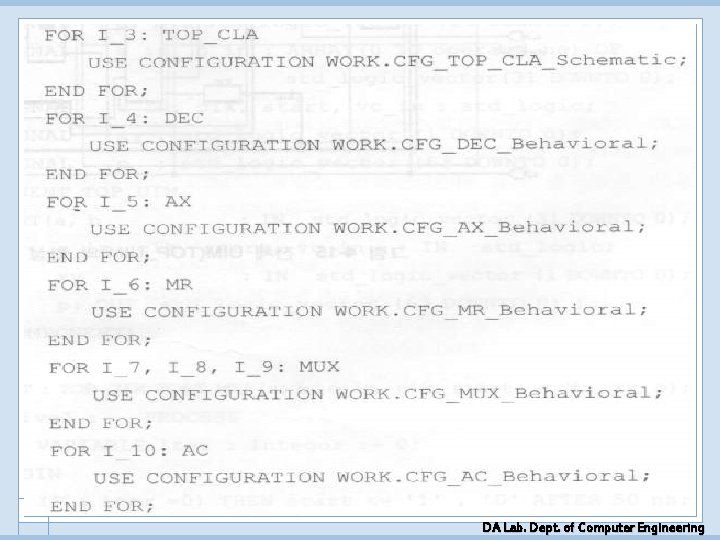

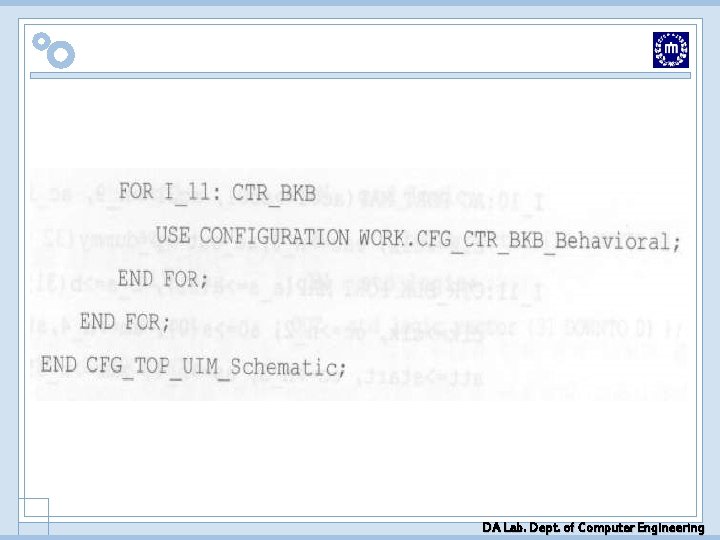

UIM 전체 VHDL 모델링[VHDL 소스] DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

DA Lab. Dept. of Computer Engineering

- Slides: 80