32 bitni mikrokontroleri i primena MS 1 BMP

32 -bitni mikrokontroleri i primena - MS 1 BMP 8. deo 2013 Nenad Jovičić

DMA � 12 kanala (7 za DMA 1 kontrler i 5 za DMA 2 kontroler) �SMT 32 F 100 ima jedan kontroler DMA 1 �Mogući su prenosi u u svim kombinacijama između meorije i periferija. �Podržan prenos za tajmere, ADC, SPI, I 2 Cs, USART i DAC �Podržan prenos 8, 16 i 32 -bitnih podataka. �Podržani cirkularni baferi!

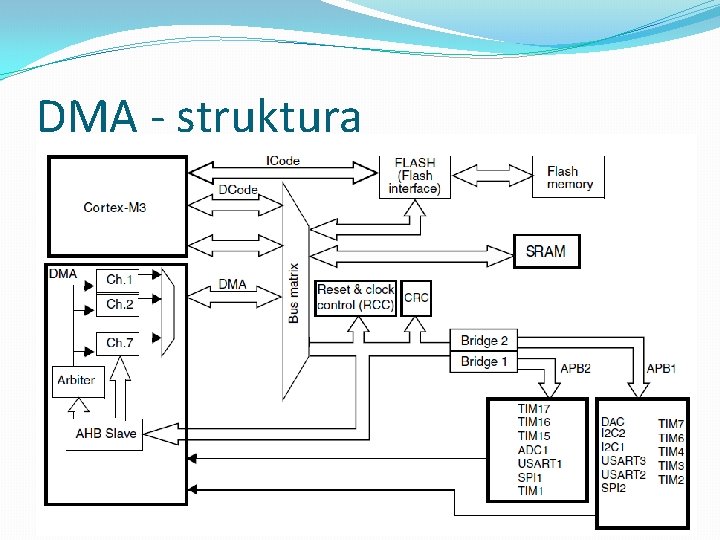

DMA - struktura

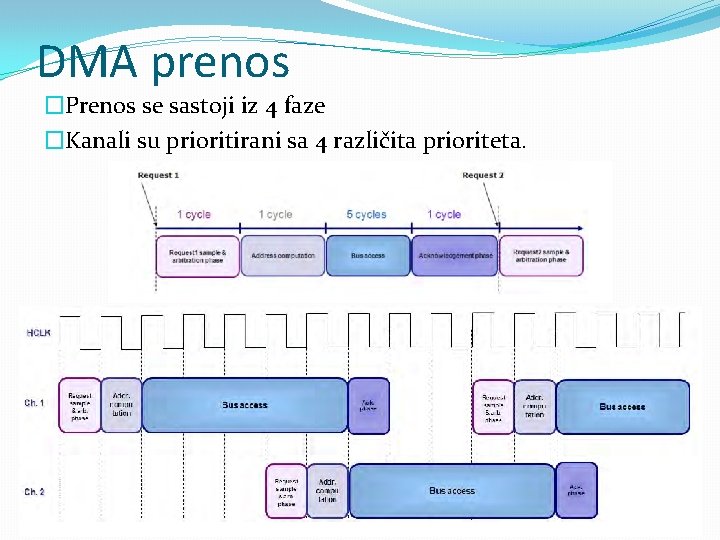

DMA prenos �Prenos se sastoji iz 4 faze �Kanali su prioritirani sa 4 različita prioriteta.

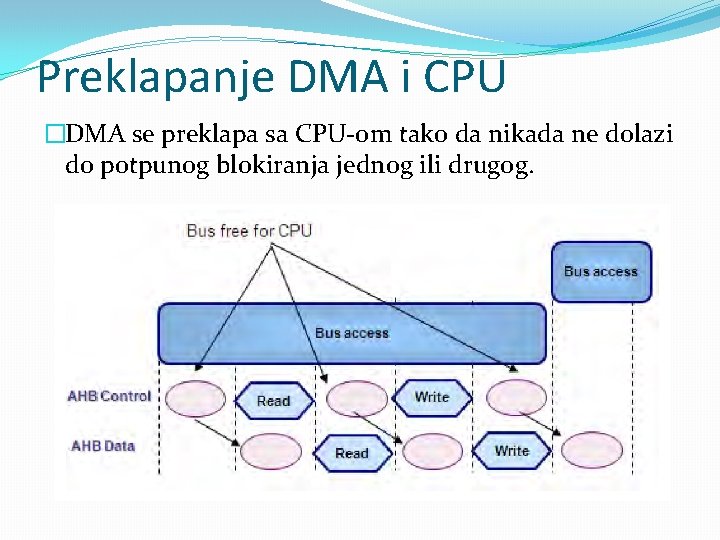

Preklapanje DMA i CPU �DMA se preklapa sa CPU-om tako da nikada ne dolazi do potpunog blokiranja jednog ili drugog.

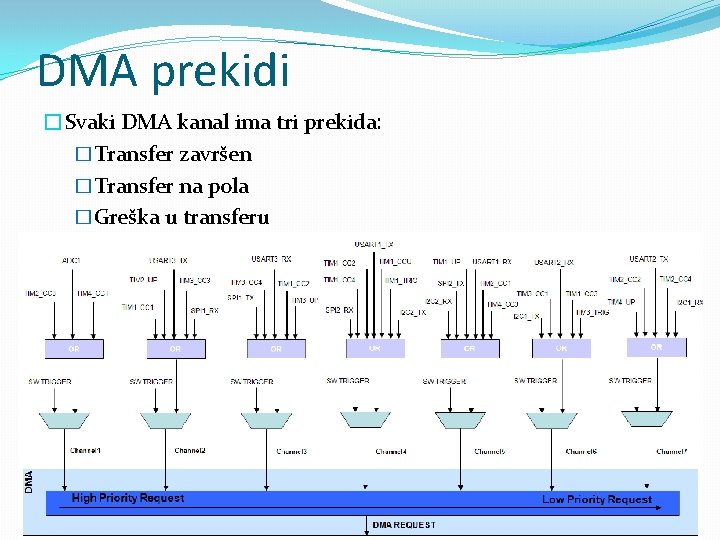

DMA prekidi �Svaki DMA kanal ima tri prekida: �Transfer završen �Transfer na pola �Greška u transferu �fe

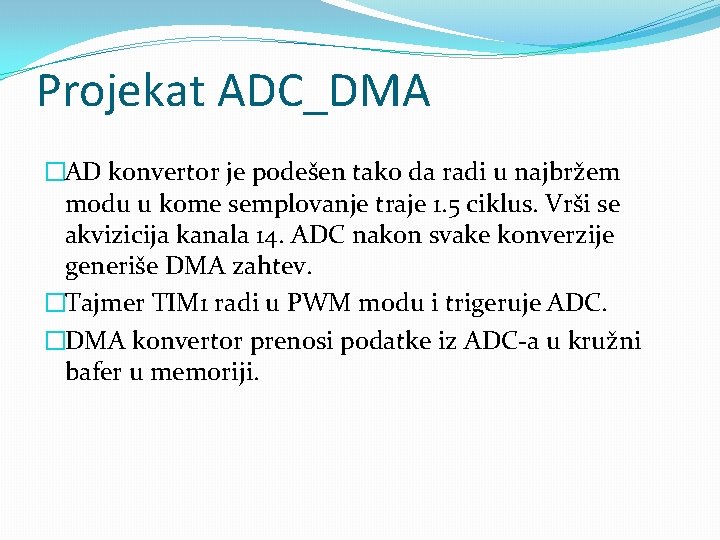

Projekat ADC_DMA �AD konvertor je podešen tako da radi u najbržem modu u kome semplovanje traje 1. 5 ciklus. Vrši se akvizicija kanala 14. ADC nakon svake konverzije generiše DMA zahtev. �Tajmer TIM 1 radi u PWM modu i trigeruje ADC. �DMA konvertor prenosi podatke iz ADC-a u kružni bafer u memoriji.

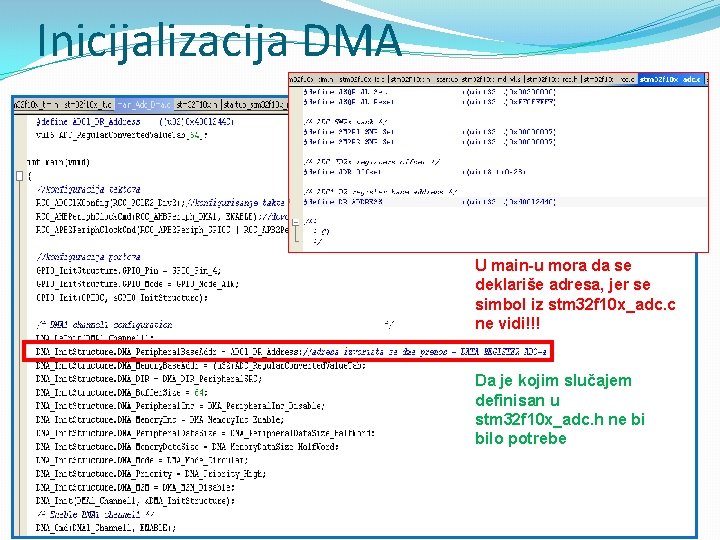

Inicijalizacija DMA U main-u mora da se deklariše adresa, jer se simbol iz stm 32 f 10 x_adc. c ne vidi!!! Da je kojim slučajem definisan u stm 32 f 10 x_adc. h ne bi bilo potrebe

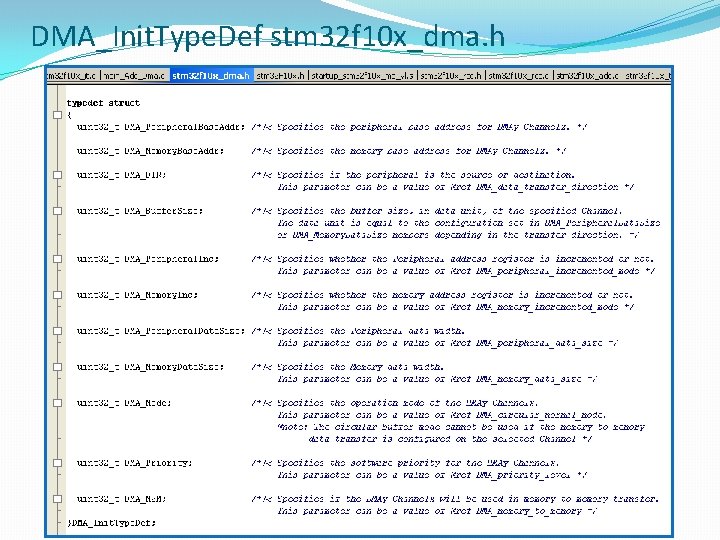

DMA_Init. Type. Def stm 32 f 10 x_dma. h

Inicijalizacija ADC-a

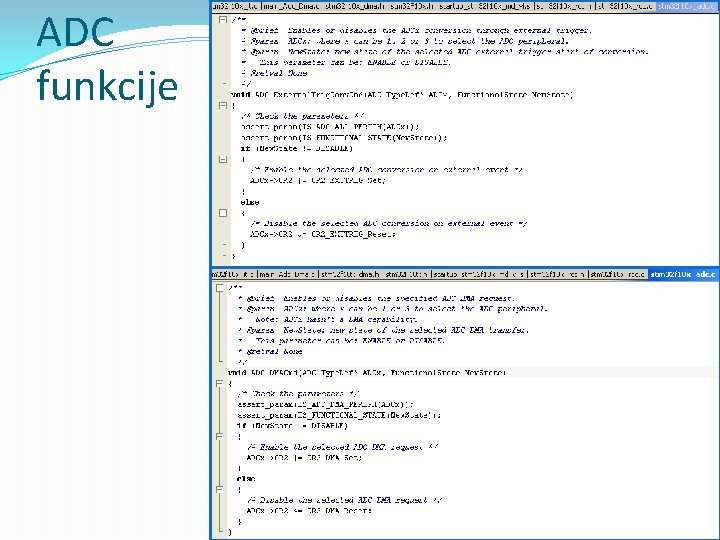

ADC funkcije

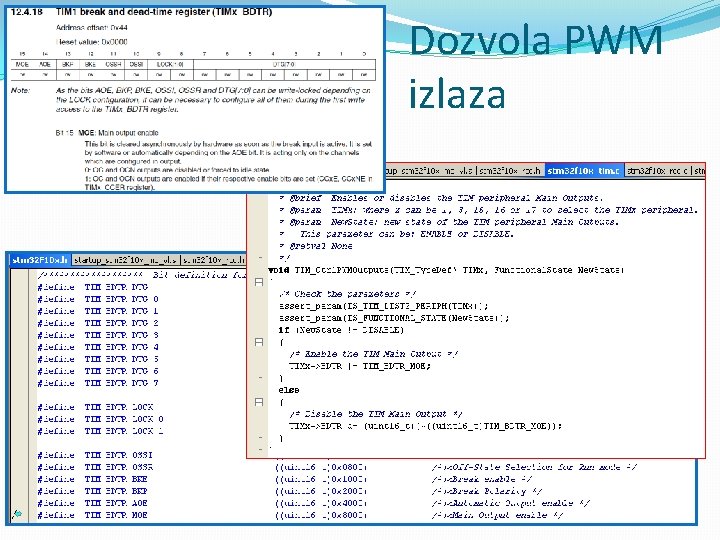

Dozvola PWM izlaza

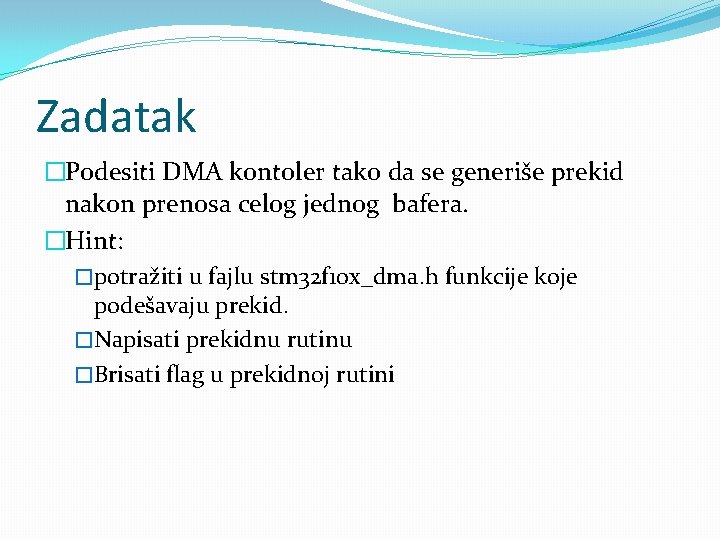

Zadatak �Podesiti DMA kontoler tako da se generiše prekid nakon prenosa celog jednog bafera. �Hint: �potražiti u fajlu stm 32 f 10 x_dma. h funkcije koje podešavaju prekid. �Napisati prekidnu rutinu �Brisati flag u prekidnoj rutini

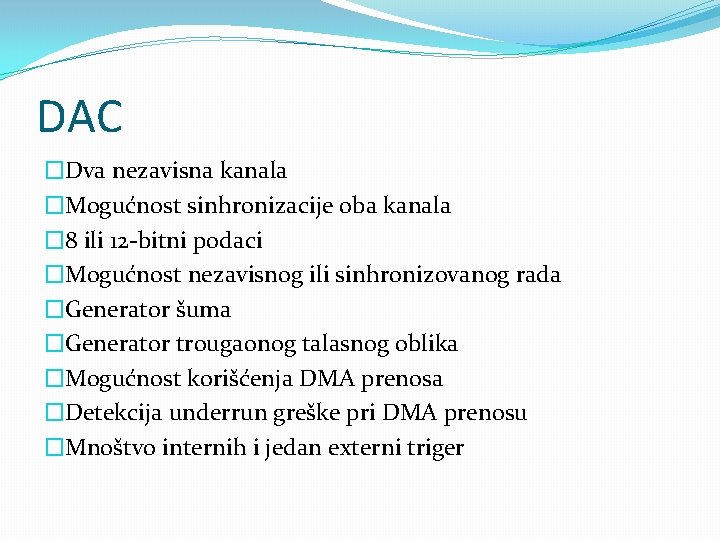

DAC �Dva nezavisna kanala �Mogućnost sinhronizacije oba kanala � 8 ili 12 -bitni podaci �Mogućnost nezavisnog ili sinhronizovanog rada �Generator šuma �Generator trougaonog talasnog oblika �Mogućnost korišćenja DMA prenosa �Detekcija underrun greške pri DMA prenosu �Mnoštvo internih i jedan externi triger

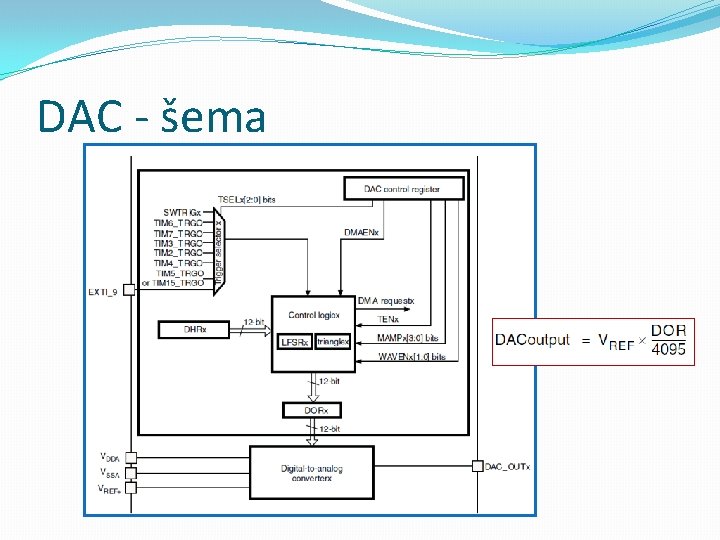

DAC - šema

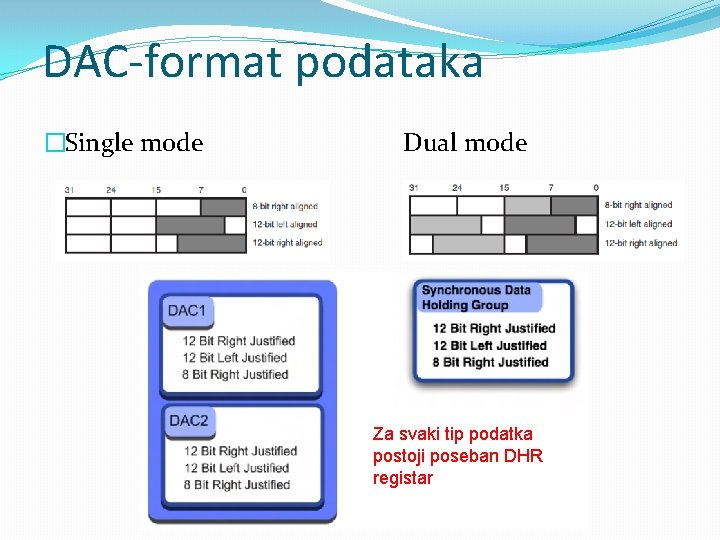

DAC-format podataka �Single mode Dual mode Za svaki tip podatka postoji poseban DHR registar

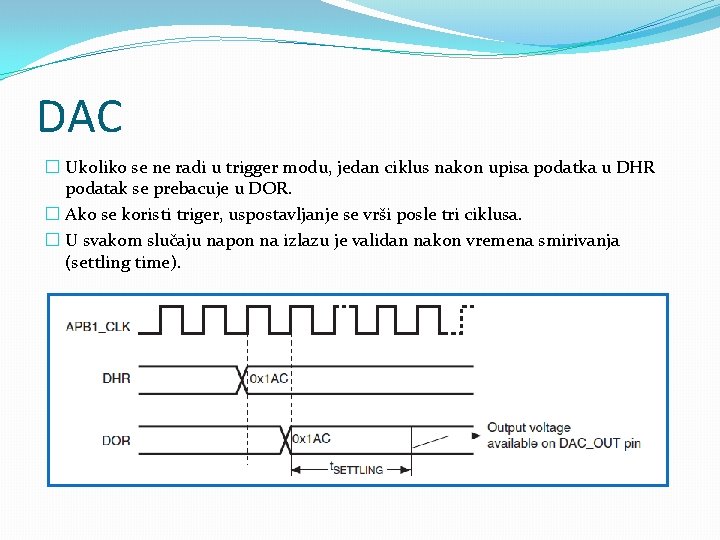

DAC � Ukoliko se ne radi u trigger modu, jedan ciklus nakon upisa podatka u DHR podatak se prebacuje u DOR. � Ako se koristi triger, uspostavljanje se vrši posle tri ciklusa. � U svakom slučaju napon na izlazu je validan nakon vremena smirivanja (settling time).

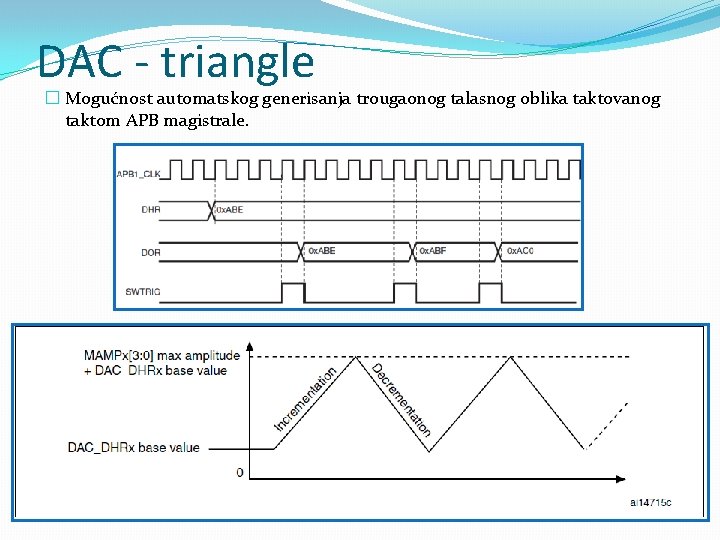

DAC - triangle � Mogućnost automatskog generisanja trougaonog talasnog oblika taktovanog taktom APB magistrale.

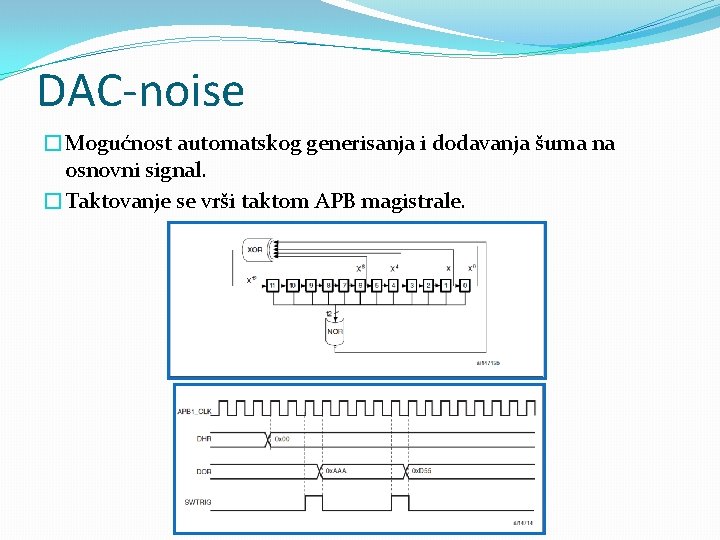

DAC-noise �Mogućnost automatskog generisanja i dodavanja šuma na osnovni signal. �Taktovanje se vrši taktom APB magistrale.

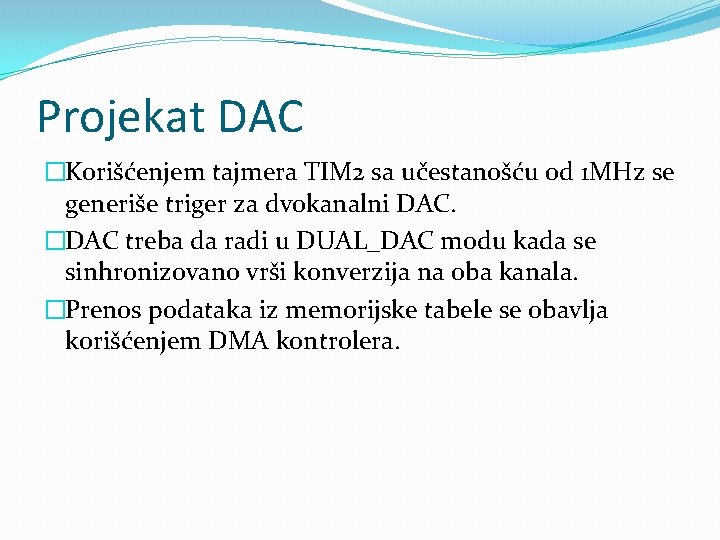

Projekat DAC �Korišćenjem tajmera TIM 2 sa učestanošću od 1 MHz se generiše triger za dvokanalni DAC. �DAC treba da radi u DUAL_DAC modu kada se sinhronizovano vrši konverzija na oba kanala. �Prenos podataka iz memorijske tabele se obavlja korišćenjem DMA kontrolera.

Inicijalizacija 1 Selekcija TRG 0 izlaza DAC Inicijalizacija Formiranje tabele

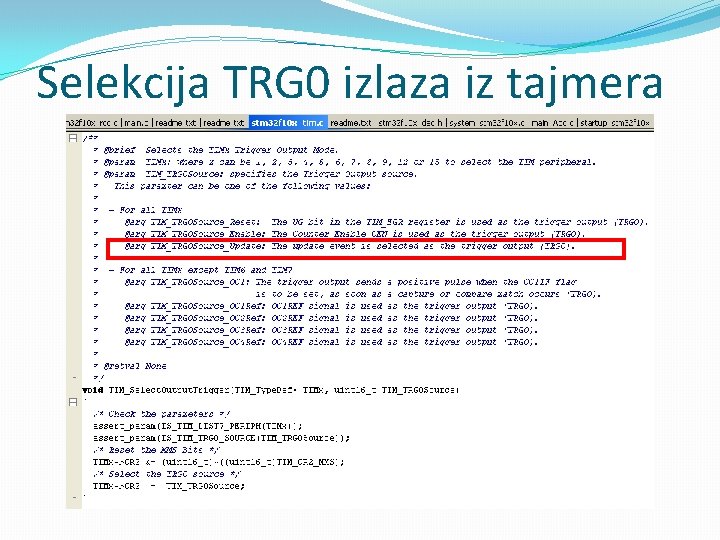

Selekcija TRG 0 izlaza iz tajmera

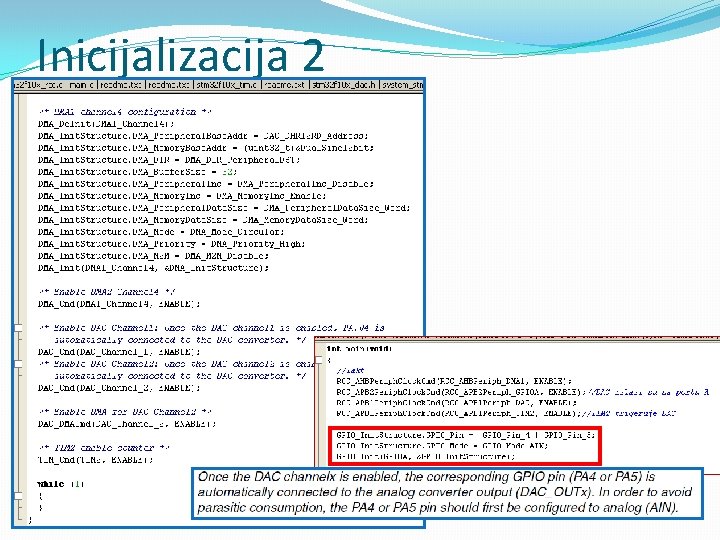

Inicijalizacija 2

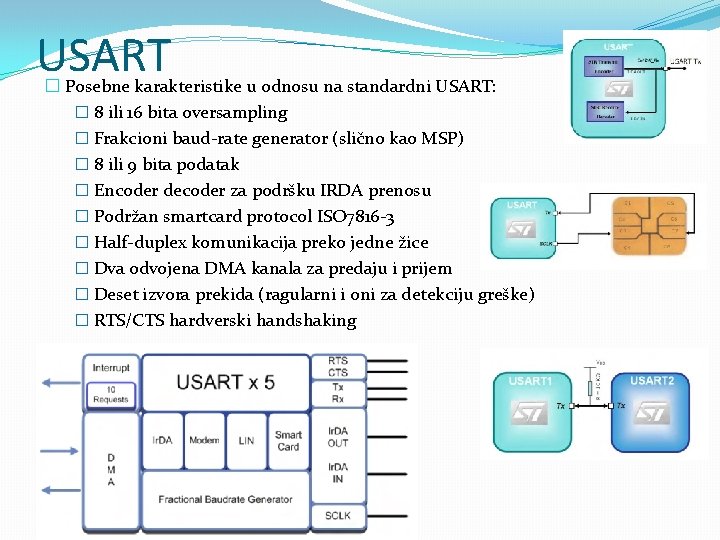

USART � Posebne karakteristike u odnosu na standardni USART: � 8 ili 16 bita oversampling � Frakcioni baud-rate generator (slično kao MSP) � 8 ili 9 bita podatak � Encoder decoder za podršku IRDA prenosu � Podržan smartcard protocol ISO 7816 -3 � Half-duplex komunikacija preko jedne žice � Dva odvojena DMA kanala za predaju i prijem � Deset izvora prekida (ragularni i oni za detekciju greške) � RTS/CTS hardverski handshaking

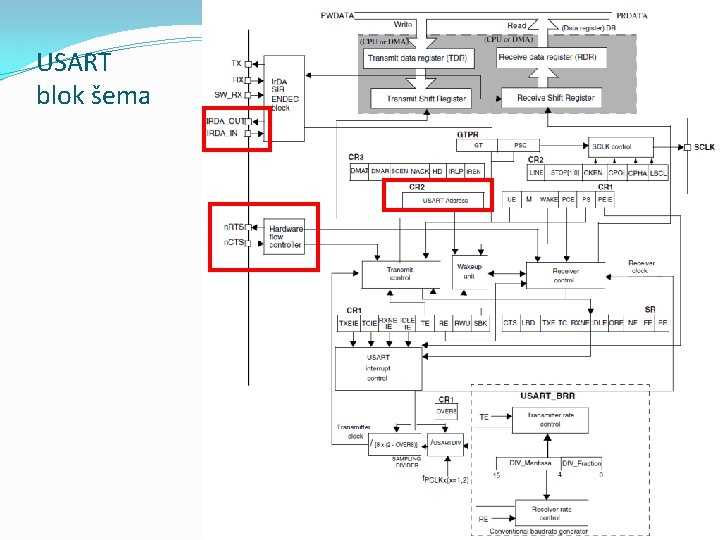

USART blok šema

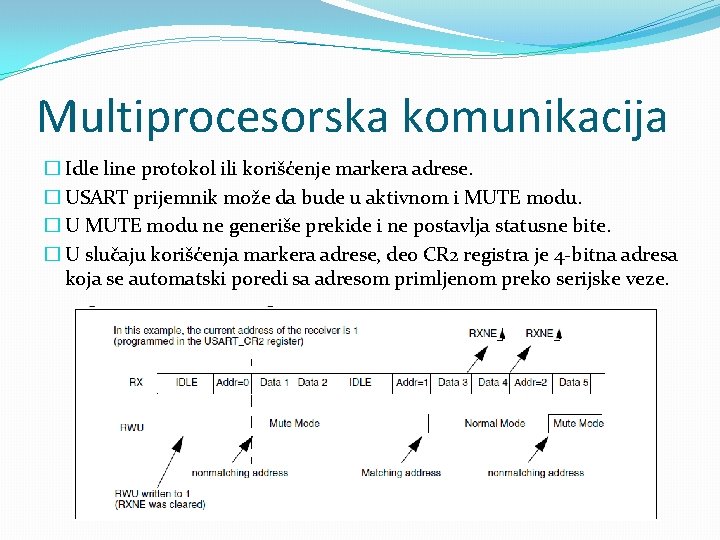

Multiprocesorska komunikacija � Idle line protokol ili korišćenje markera adrese. � USART prijemnik može da bude u aktivnom i MUTE modu. � U MUTE modu ne generiše prekide i ne postavlja statusne bite. � U slučaju korišćenja markera adrese, deo CR 2 registra je 4 -bitna adresa koja se automatski poredi sa adresom primljenom preko serijske veze.

The end

- Slides: 27