3 D FPGA MEANDER Abhishek Pandey Reconfigurable Computing

3 D FPGA- MEANDER Abhishek Pandey Reconfigurable Computing ECE 506

Outline: �Introduction �TPR Vs MEANDER �Methodology �Flowchart �Partitioning �Placement and routing � 3 D Power �Comparison of different 3 D tools �Results �Future Work

Introduction: �Better performance per unit area. Limited silicon area and chip size. �Improvement over existing 2 D technology �Need better CAD tools to exploit full benefit of 3 D FPGA. � 3 D as a improvement over FPGA and its limitation

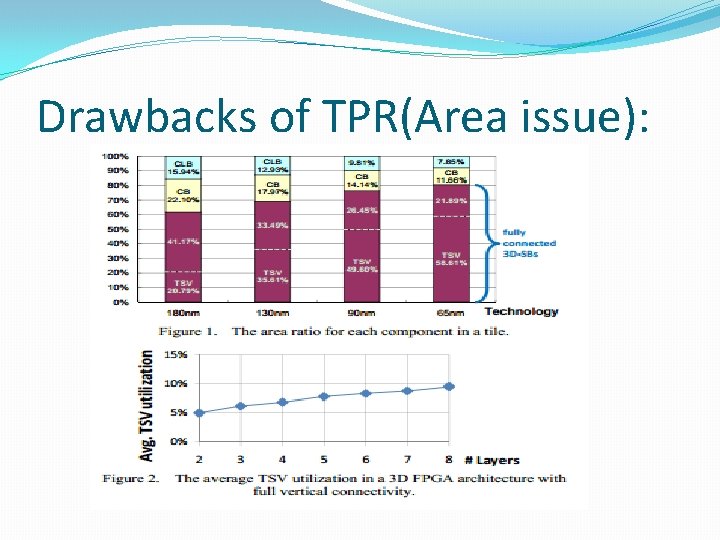

Drawbacks of TPR: �First Synthesizer of 3 D FPGA. �All SB’s are assumed 3 D �Number of available TSV’s are assumed unlimited. �Area situation becomes worse in 3 D FPGA.

Drawbacks of TPR(Area issue):

Alternative distribution scenarios for 3 D SBs:

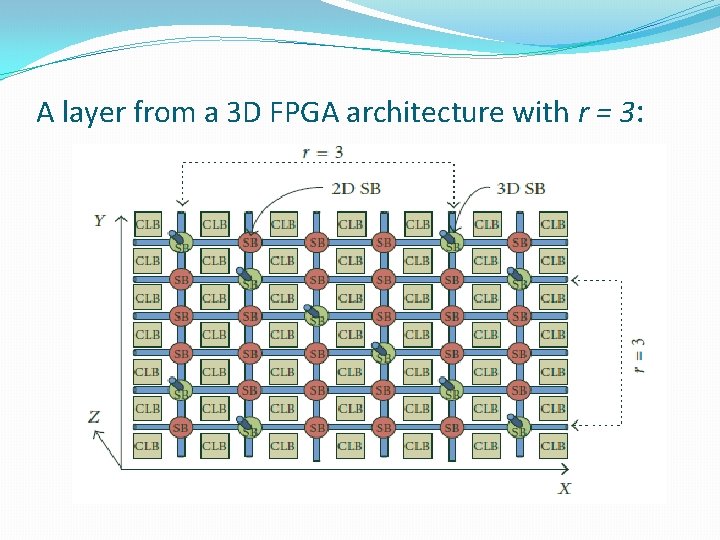

A layer from a 3 D FPGA architecture with r = 3:

Methodology(multisegment interconnection architecture. ):

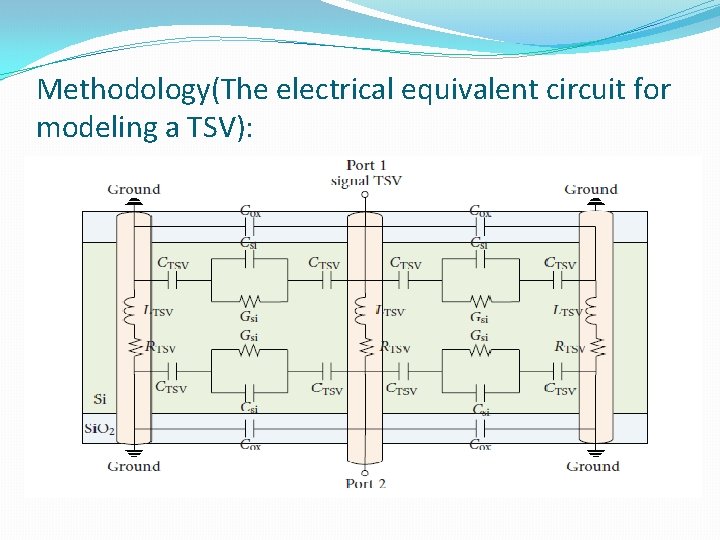

Methodology(The electrical equivalent circuit for modeling a TSV):

Methodology(Proposed method):

Flowchart(MEANDER framework):

Flowchart(MEANDER framework): � 3 D Partitioning ( 3 DPART) � 3 D Placement and Routing(3 DPRO) � 3 D Power( 3 DPOWER)

Partitioning( algorithm):

Partitioning( diagrammatic representation):

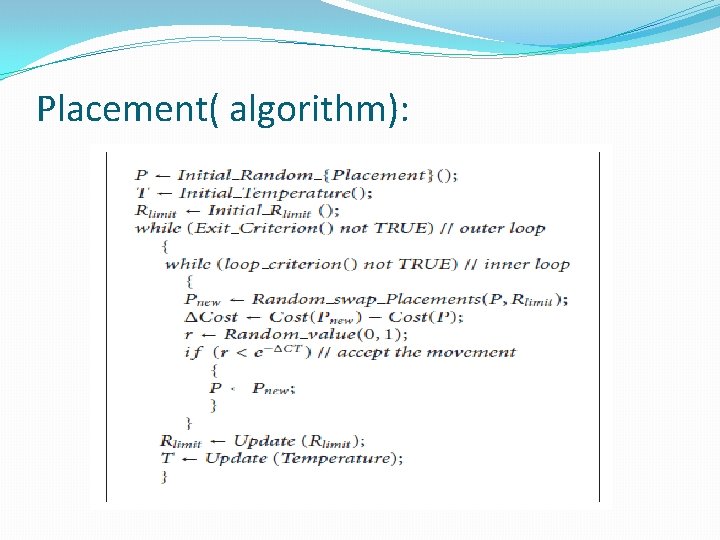

Placement( algorithm):

Placement( cost function):

Routing( cost function):

P & R ( Algorithm):

P & R ( Algorithm):

Power( algorithm):

Power( cost function):

Qualitative comparison between TPR and our proposed solution*: • S. Das, A. Chandrakasan and R. Reif, “Timing, Energy, and Thermal Performance of Three Dimensional Integrated Circuits”, Proceedings of the ACM Great Lakes Symposium on VLSI, (2004), pp. 338 -343. Developed at MIT • Kostas Siozios, Alexandros Bartzas, and Dimitrios Soudris, “Architecture-Level Exploration of Alternative Interconnection Schemes Targeting 3 D FPGAs: A Software-Supported Methodology, ” International Journal of Reconfigurable Computing, vol. 2008, Article ID 764942, 18 pages, 2008. doi: 10. 1155/2008/764942. Developed at National Technical University of Athens (NTUA)

Average variation of application’s delay for a number of layers and TSVs with different electric characteristics:

Average variation of power consumption for a number of layers and TSVs with different electric characteristics:

Experimental setup: �The 3 D architectures consist of up to five functional layers. �The hardware resources of each functional layer are identical. �The percentage of vertical interconnects (i. e. , TSVs) per functional layer ranges from 10% up to 100%, with a step of 10%. �Each 3 D SB realizes four vertical connections. �The electrical parameters for each TSV correspond to fabrication technologies for 3 D ICs found in relevant references

Experimental setup: �The 3 D architectures consist of up to five functional layers. �The hardware resources of each functional layer are identical. �The percentage of vertical interconnects (i. e. , TSVs) per functional layer ranges from 10% up to 100%, with a step of 10%. �Each 3 D SB realizes four vertical connections. �The electrical parameters for each TSV correspond to fabrication technologies for 3 D ICs found in relevant references

Experimental setup:

Results(Average Energy×Delay Product (EDP) for different number of functional layers and percentage of fabricated TSVs):

Results(Average wirelength over the MCNC benchmarks for different number of functional layers and percentage of fabricated TSVs):

Results(Average operation frequency over the MCNC benchmarks for different number of layers and percentages of fabricated TSVs):

Results(Average power consumption over the MCNC benchmarks for different number of functional layers and percentage of fabricated TSVs):

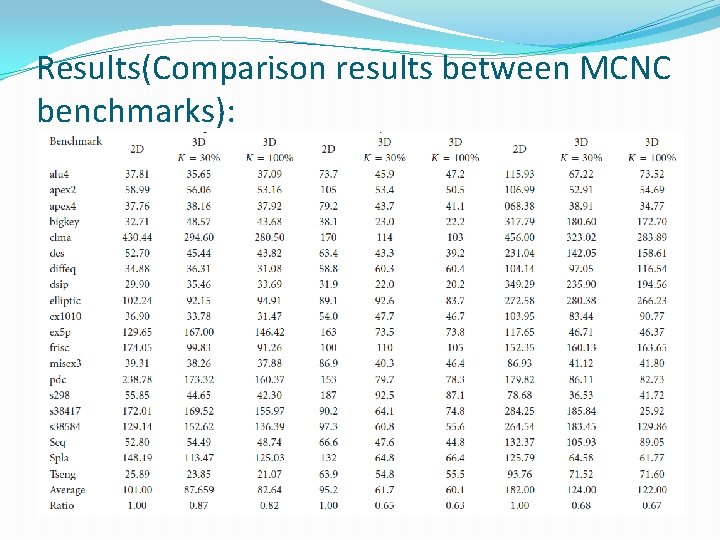

Results(Comparison results between MCNC benchmarks):

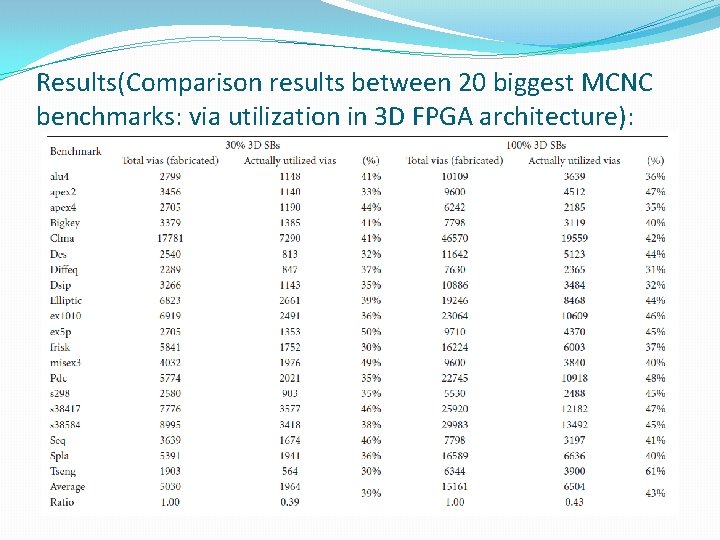

Results(Comparison results between 20 biggest MCNC benchmarks: via utilization in 3 D FPGA architecture):

Future work: �Experimenting on working with different technology on different layers. �Better CAD tools for 3 D FPGAs. �More work need to be done on switch box layout for combination of 2 D and 3 D switches. �More research need to be done on making better connection within a switch box. �Specialized 3 D P & R methods need to be researched.

Conclusion: �A systematic software-supported methodology for exploring and evaluating alternative interconnection schemes for 3 D FPGAs is presented. �The methodology is supported by three new CAD tools (part of the 3 D MEANDER Design Framework). �The evaluation results prove that it is possible to design 3 D FPGAs with limited number of vertical connections without any penalty in performance or power consumption. � More specifically, for the 20 biggest MCNC benchmarks, the average gains in operation frequency, total wirelength, and energy consumption are 35%, 13%, and 32%, respectively, compared to existing 2 D FPGAs with identical logic resources.

Q&A?

Thank You !!!

- Slides: 37