3 D CMOS monolithic 3 bit resolution pixel

3 D CMOS monolithic 3 -bit resolution pixel sensor with fast digital pipelined readout Olav Torheim, Yunan Fu, Christine Hu-Guo, Yann Hu, Marc Winter on behalf of IPHC (Strasbourg) Outline v 3 DIT improves MAPS performances v A 12 µm pitch pixel CMOS MAPS for the ILC vertex detector using 3 DIT v 3 D rolling shutter CMOS MAPS with fast digital pipelined readout v § Analog tier: sensor, preamplifier and pixel-level ADC § Digital tier : SRAMs and data sparsification circuitry Conclusions

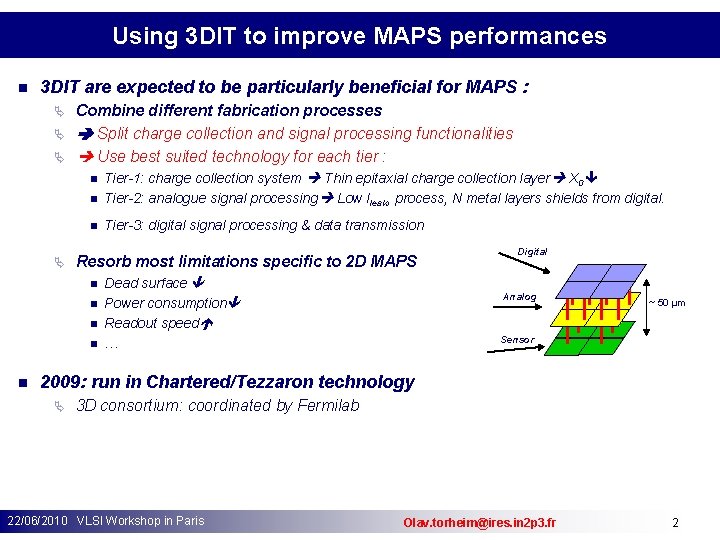

Using 3 DIT to improve MAPS performances n 3 DIT are expected to be particularly beneficial for MAPS : Combine different fabrication processes Ä Split charge collection and signal processing functionalities Ä Use best suited technology for each tier : Ä n Tier-1: charge collection system Thin epitaxial charge collection layer X 0 Tier-2: analogue signal processing Low Ileak, process, N metal layers shields from digital. n Tier-3: digital signal processing & data transmission n Ä Resorb most limitations specific to 2 D MAPS n n n Dead surface Power consumption Readout speed … Digital Analog ~ 50 µm Sensor 2009: run in Chartered/Tezzaron technology Ä 3 D consortium: coordinated by Fermilab 22/06/2010 VLSI Workshop in Paris Olav. torheim@ires. in 2 p 3. fr 2

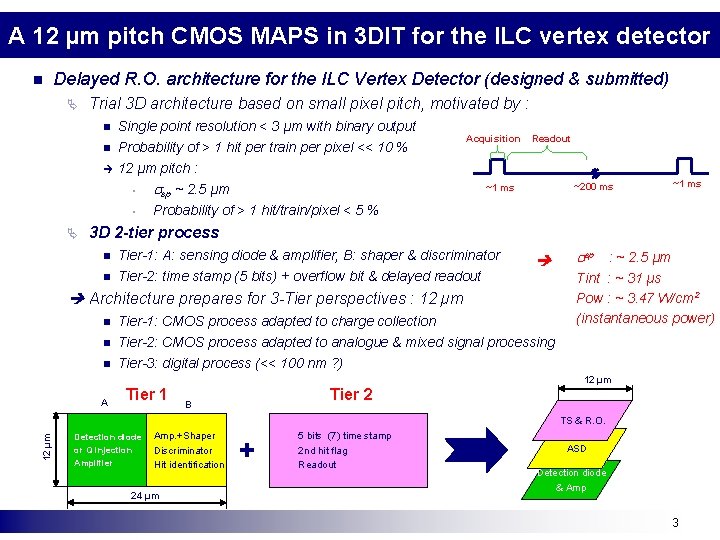

A 12 µm pitch CMOS MAPS in 3 DIT for the ILC vertex detector n Delayed R. O. architecture for the ILC Vertex Detector (designed & submitted) Ä Trial 3 D architecture based on small pixel pitch, motivated by : Single point resolution < 3 μm with binary output n Probability of > 1 hit per train per pixel << 10 % è 12 μm pitch : • sp ~ 2. 5 μm • Probability of > 1 hit/train/pixel < 5 % n Ä Acquisition Readout ~200 ms ~1 ms 3 D 2 -tier process n n Tier-1: A: sensing diode & amplifier, B: shaper & discriminator Tier-2: time stamp (5 bits) + overflow bit & delayed readout Architecture prepares for 3 -Tier perspectives : 12 µm n n n Tier-1: CMOS process adapted to charge collection Tier-2: CMOS process adapted to analogue & mixed signal processing Tier-3: digital process (<< 100 nm ? ) sp : ~ 2. 5 μm Tint : ~ 31 µs Pow : ~ 3. 47 W/cm 2 (instantaneous power) 12 µm A Tier 1 Tier 2 B 12 µm TS & R. O. Detection diode or Q injection Amplifier Amp. +Shaper Discriminator Hit identification 24 µm + 5 bits (7) time stamp 2 nd hit flag Readout ASD Detection diode & Amp 3

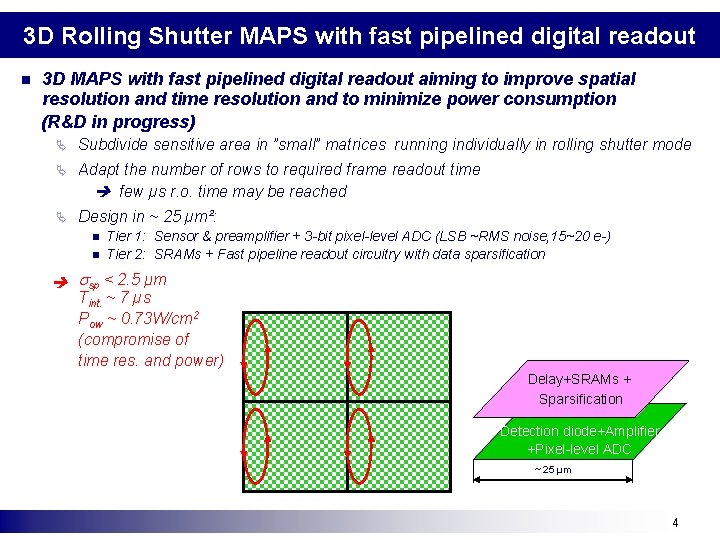

3 D Rolling Shutter MAPS with fast pipelined digital readout n 3 D MAPS with fast pipelined digital readout aiming to improve spatial resolution and time resolution and to minimize power consumption (R&D in progress) Ä Subdivide sensitive area in ”small” matrices running individually in rolling shutter mode Ä Adapt the number of rows to required frame readout time few µs r. o. time may be reached Ä Design in ~ 25 µm²: n n Tier 1: Sensor & preamplifier + 3 -bit pixel-level ADC (LSB ~RMS noise, 15~20 e-) Tier 2: SRAMs + Fast pipeline readout circuitry with data sparsification sp < 2. 5 μm Tint. ~ 7 µs Pow ~ 0. 73 W/cm 2 (compromise of time res. and power) Delay+SRAMs + Sparsification Detection diode+Amplifier +Pixel-level ADC ~ 25 µm 4

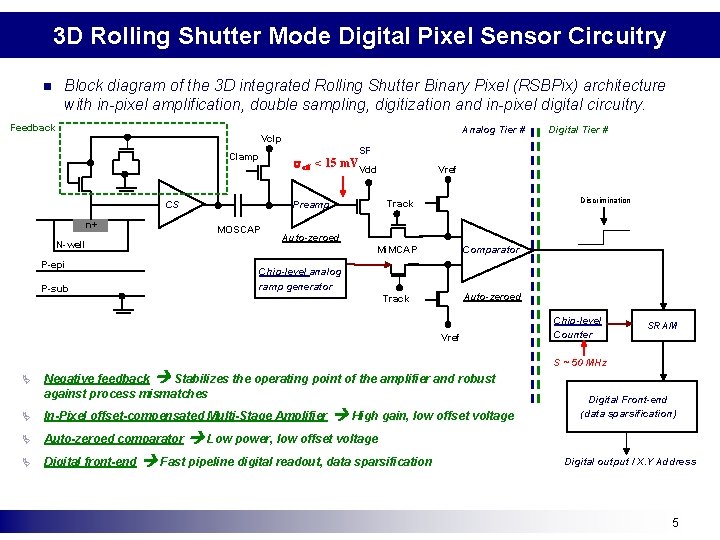

3 D Rolling Shutter Mode Digital Pixel Sensor Circuitry n Block diagram of the 3 D integrated Rolling Shutter Binary Pixel (RSBPix) architecture with in-pixel amplification, double sampling, digitization and in-pixel digital circuitry. Feedback Analog Tier # Vclp Clamp soff < 15 m. V n+ MOSCAP N-well P-epi SF Vdd Vref Discrimination Track Preamp CS Auto-zeroed Mi. MCAP Comparator Track Auto-zeroed Chip-level analog ramp generator P-sub Vref Ä Digital Tier # Negative feedback Stabilizes the operating point of the amplifier and robust against process mismatches Ä In-Pixel offset-compensated Multi-Stage Amplifier Ä Auto-zeroed comparator Ä Digital front-end High gain, low offset voltage Chip-level Counter SRAM S ~ 50 MHz Digital Front-end (data sparsification) Low power, low offset voltage Fast pipeline digital readout, data sparsification Digital output / X. Y Address 5

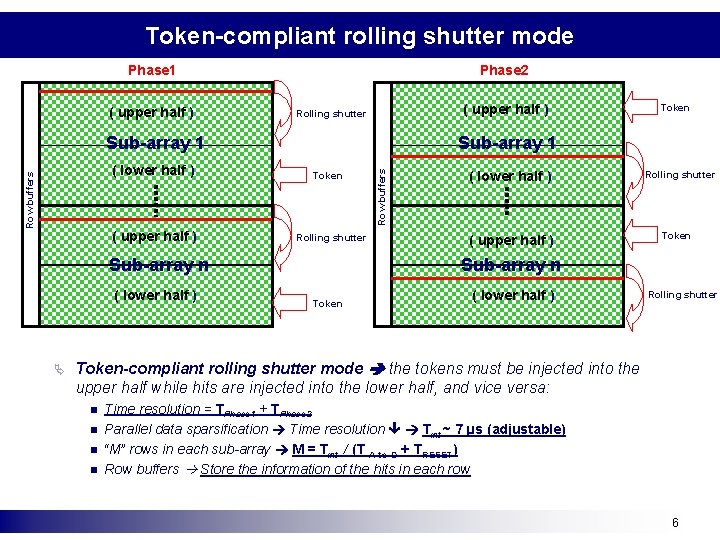

Token-compliant rolling shutter mode Phase 1 ( upper half ) Phase 2 ( upper half ) Rolling shutter Row buffers ( lower half ) ( upper half ) Sub-array 1 Token Rolling shutter Sub-array n ( lower half ) Ä Row buffers Sub-array 1 Token ( lower half ) ( upper half ) Rolling shutter Token Sub-array n Token ( lower half ) Rolling shutter Token-compliant rolling shutter mode the tokens must be injected into the upper half while hits are injected into the lower half, and vice versa: n n Time resolution = TPhase 1 + TPhase 2 Parallel data sparsification Time resolution Tint ~ 7 µs (adjustable) “M” rows in each sub-array M = Tint / (T A-to-D + TRESET) Row buffers Store the information of the hits in each row 6

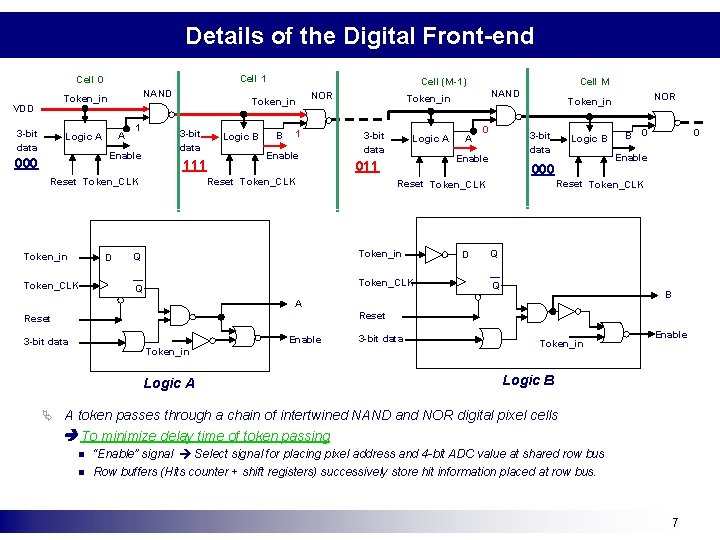

Details of the Digital Front-end Cell 1 Cell 0 NAND Token_in VDD 3 -bit data A Logic A 1 Enable 000 Token_in 3 -bit data 111 Reset Token_CLK Token_in D Token_CLK Cell (M-1) Logic B B NOR 1 Enable Token_in 3 -bit data Logic A 0 Token_CLK D NOR Token_in 3 -bit data Logic B B 0 0 Enable 000 Reset Token_CLK Token_in Q A Enable 011 Reset Token_CLK Q Cell M NAND Reset Token_CLK Q Q B A Reset Enable 3 -bit data Token_in Logic A 3 -bit data Token_in Enable Logic B Ä A token passes through a chain of intertwined NAND and NOR digital pixel cells To minimize delay time of token passing n n “Enable” signal Select signal for placing pixel address and 4 -bit ADC value at shared row bus Row buffers (Hits counter + shift registers) successively store hit information placed at row bus. 7

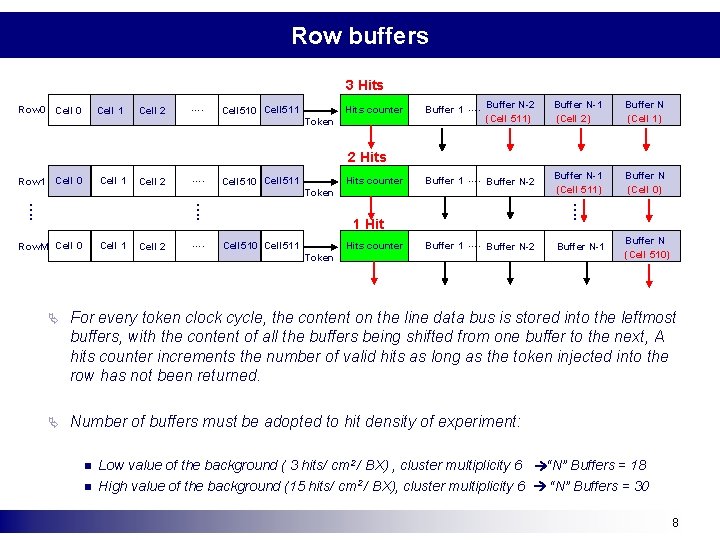

Row buffers 3 Hits Row 0 Cell 11 Cell 0 Cell 2 …. Hits counter Cell 510 Cell 511 Token Buffer N-2 Buffer 1 …. (Cell 511) Buffer N-1 (Cell 2) Buffer N (Cell 1) Buffer 1 …. Buffer N-2 Buffer N-1 (Cell 511) Buffer N (Cell 0) Buffer 1 …. Buffer N-2 Buffer N-1 2 Hits Row 1 Cell 0 Cell 1 Cell 2 …. Hits counter Cell 510 Cell 511 Row. M Cell 0 Cell 1 Cell 2 …. . … . … Token 1 Hits counter Cell 510 Cell 511 Token Buffer N (Cell 510) Ä For every token clock cycle, the content on the line data bus is stored into the leftmost buffers, with the content of all the buffers being shifted from one buffer to the next, A hits counter increments the number of valid hits as long as the token injected into the row has not been returned. Ä Number of buffers must be adopted to hit density of experiment: n n Low value of the background ( 3 hits/ cm 2 / BX) , cluster multiplicity 6 “N” Buffers = 18 High value of the background (15 hits/ cm 2 / BX), cluster multiplicity 6 “N” Buffers = 30 8

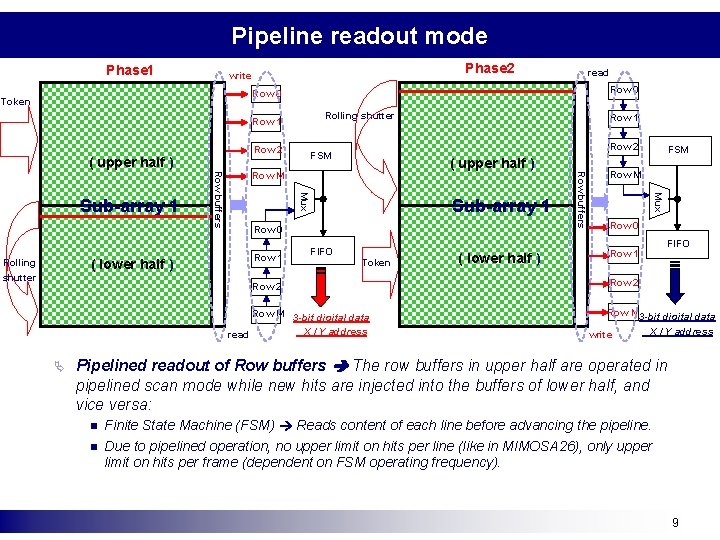

Pipeline readout mode Phase 1 Phase 2 write read Row 0 Token Rolling shutter Row 1 Row 2 ( upper half ) Row 2 FSM ( upper half ) Row 0 Row 1 FIFO Token Row 2 Row M 3 -bit digital data X / Y address read Ä ( lower half ) FSM Row M Mux Sub-array 1 Row buffers Row M Mux ( lower half ) Rolling shutter Row buffers Sub-array 1 Row 0 FIFO Row 1 Row 2 Row M 3 -bit digital data write X / Y address Pipelined readout of Row buffers The row buffers in upper half are operated in pipelined scan mode while new hits are injected into the buffers of lower half, and vice versa: n n Finite State Machine (FSM) Reads content of each line before advancing the pipeline. Due to pipelined operation, no upper limit on hits per line (like in MIMOSA 26), only upper limit on hits per frame (dependent on FSM operating frequency). 9

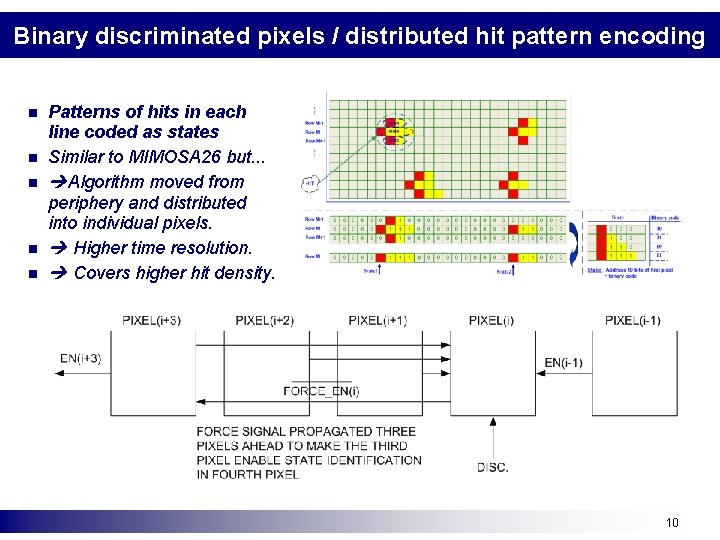

Binary discriminated pixels / distributed hit pattern encoding n n n Patterns of hits in each line coded as states Similar to MIMOSA 26 but. . . Algorithm moved from periphery and distributed into individual pixels. Higher time resolution. Covers higher hit density. 10

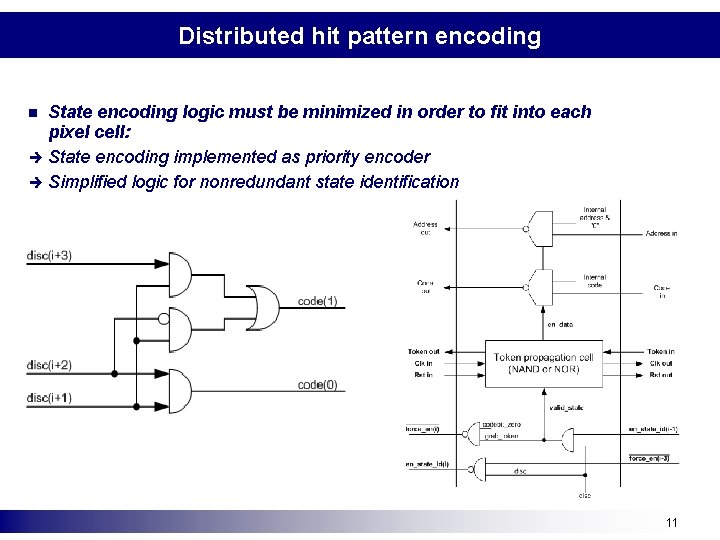

Distributed hit pattern encoding n è è State encoding logic must be minimized in order to fit into each pixel cell: State encoding implemented as priority encoder Simplified logic for nonredundant state identification 11

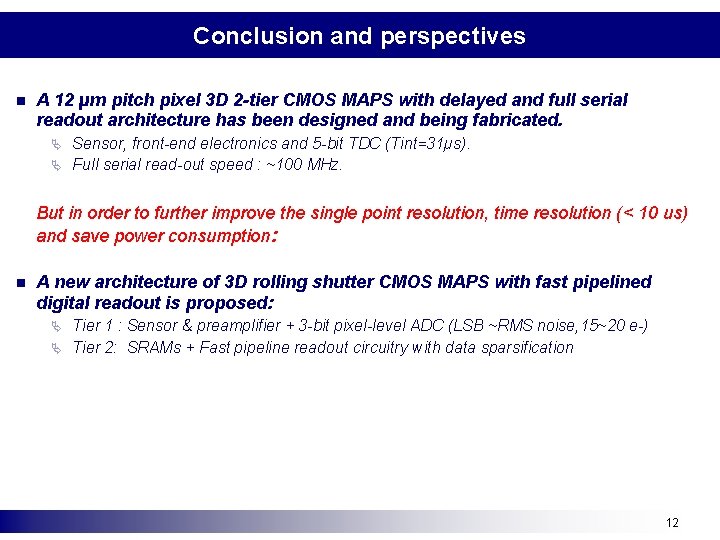

Conclusion and perspectives n A 12 µm pitch pixel 3 D 2 -tier CMOS MAPS with delayed and full serial readout architecture has been designed and being fabricated. Sensor, front-end electronics and 5 -bit TDC (Tint=31µs). Ä Full serial read-out speed : ~100 MHz. Ä But in order to further improve the single point resolution, time resolution (< 10 us) and save power consumption: n A new architecture of 3 D rolling shutter CMOS MAPS with fast pipelined digital readout is proposed: Tier 1 : Sensor & preamplifier + 3 -bit pixel-level ADC (LSB ~RMS noise, 15~20 e-) Ä Tier 2: SRAMs + Fast pipeline readout circuitry with data sparsification Ä 12

- Slides: 12