3 1 ALU CPU AND OR XOR NOT

- Slides: 74

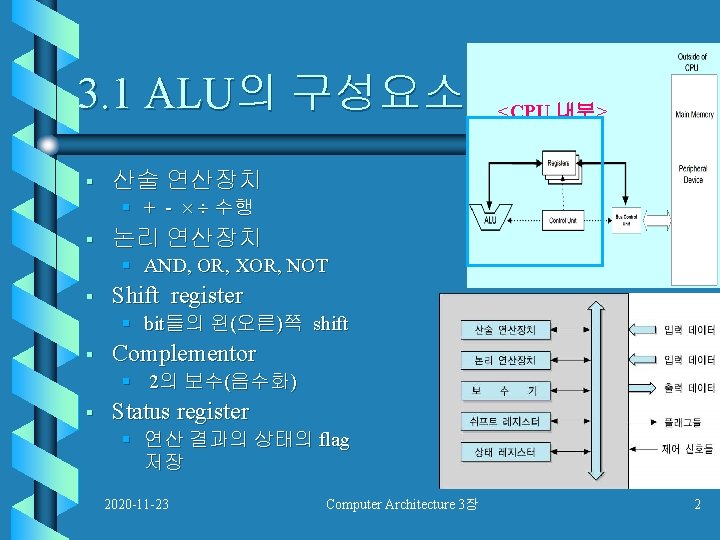

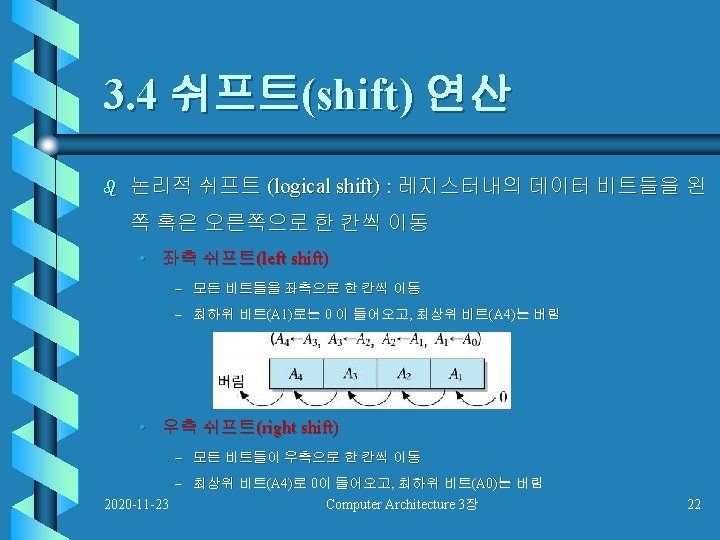

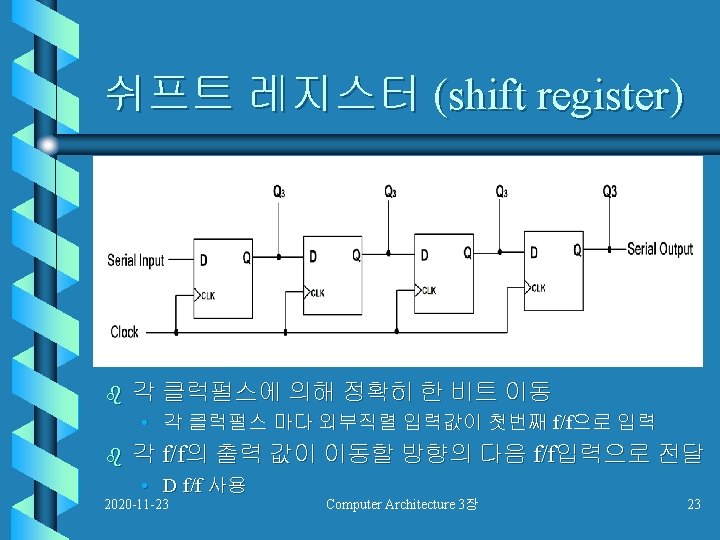

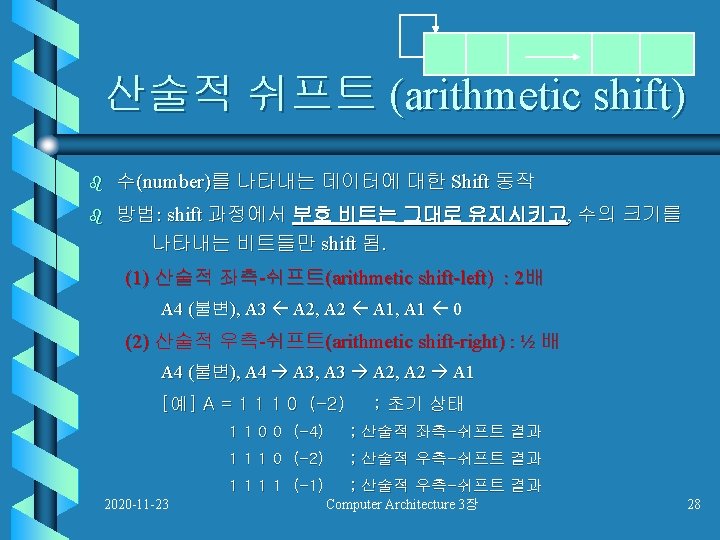

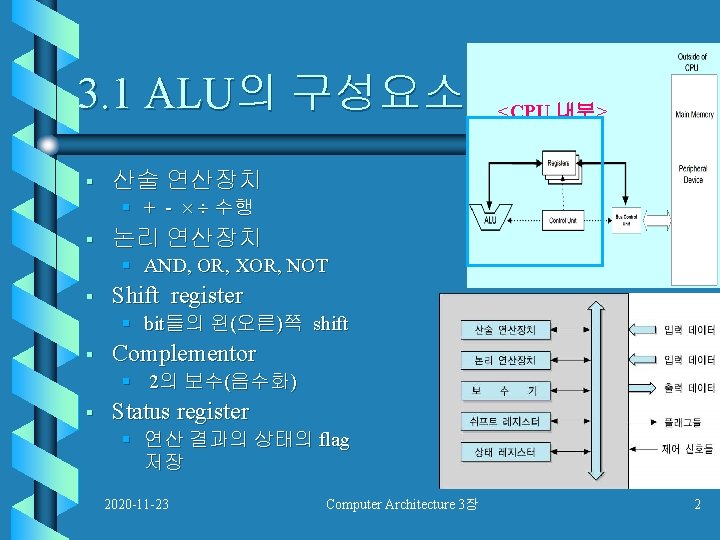

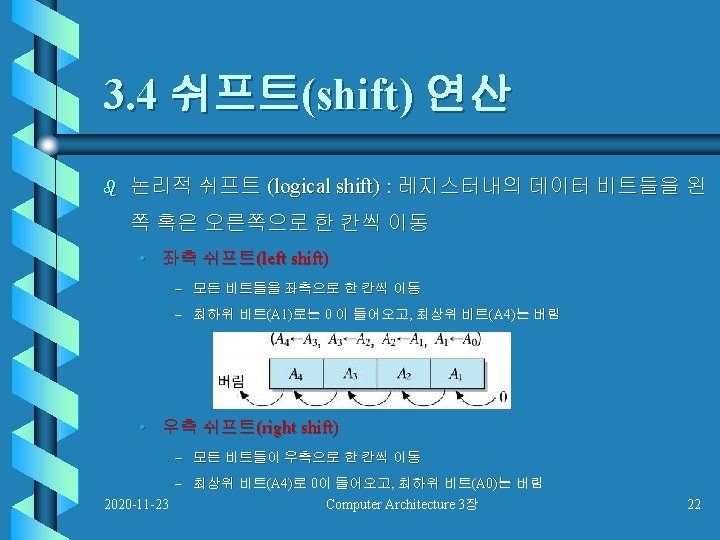

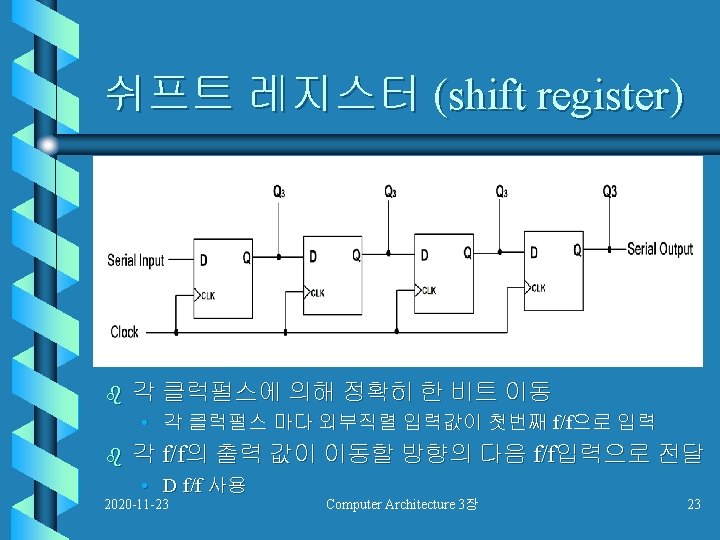

3. 1 ALU의 구성요소 § <CPU 내부> 산술 연산장치 § + - 수행 § 논리 연산장치 § AND, OR, XOR, NOT § Shift register § bit들의 왼(오른)쪽 shift § Complementor § 2의 보수(음수화) § Status register § 연산 결과의 상태의 flag 저장 2020 -11 -23 Computer Architecture 3장 2

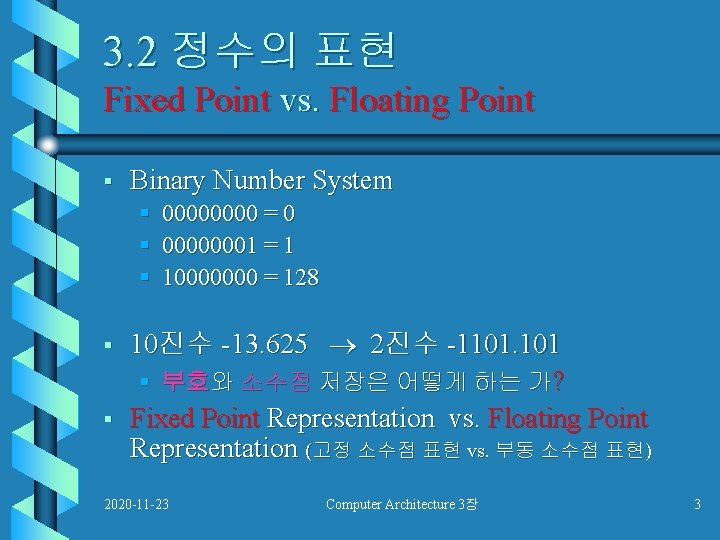

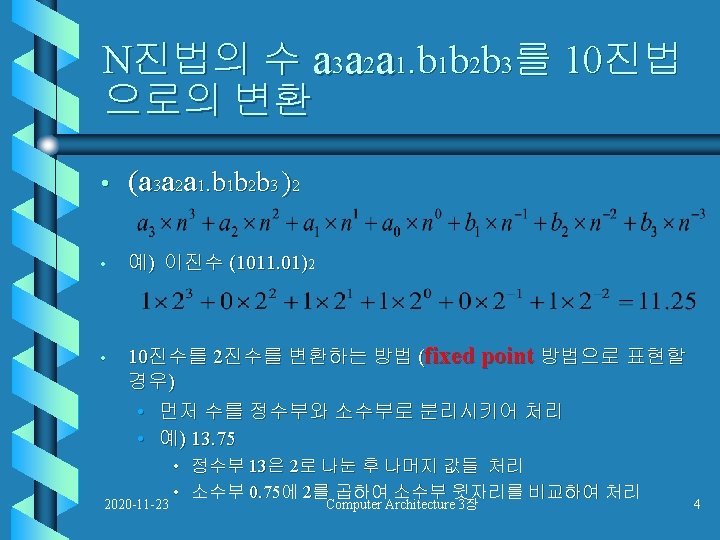

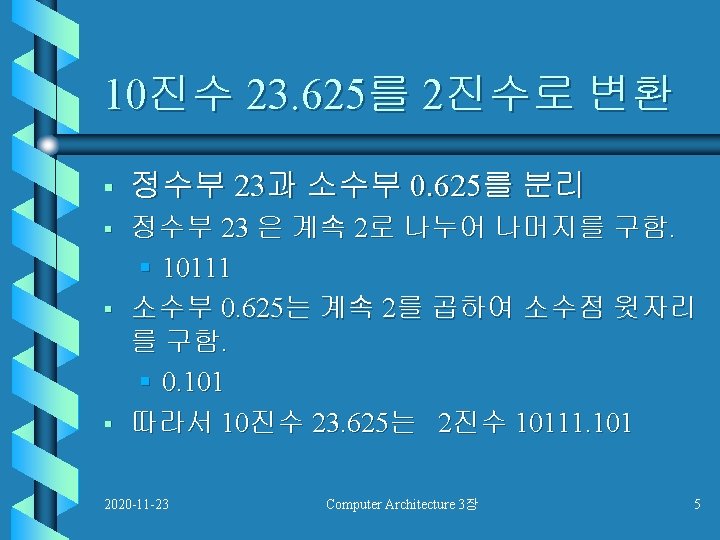

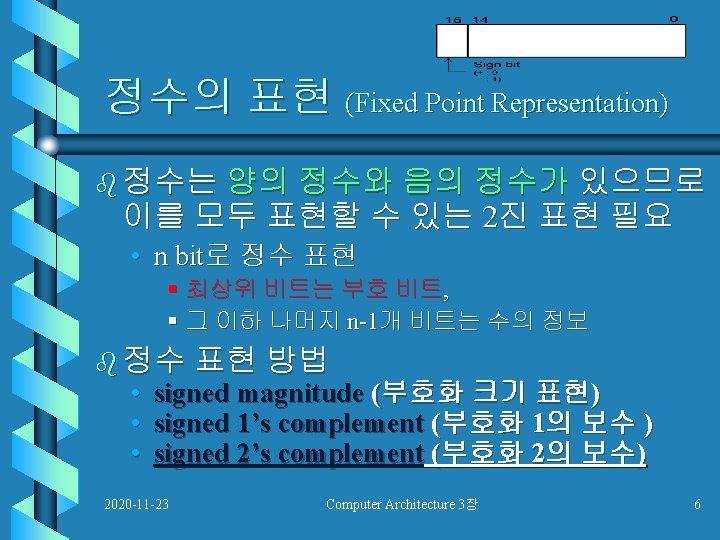

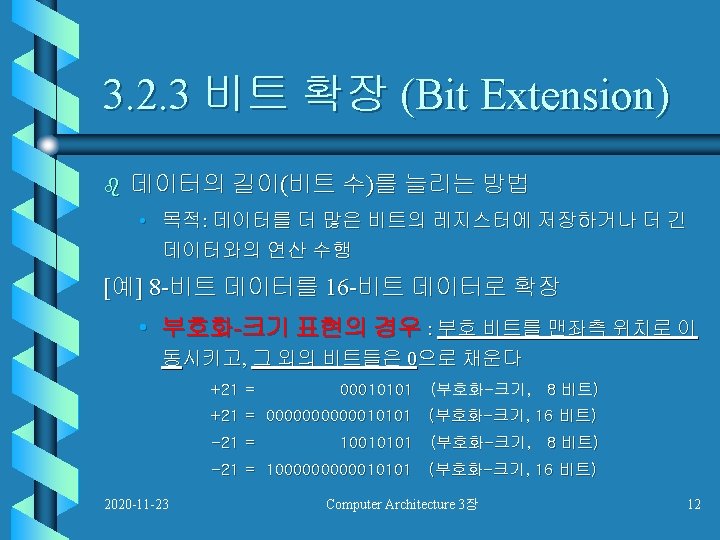

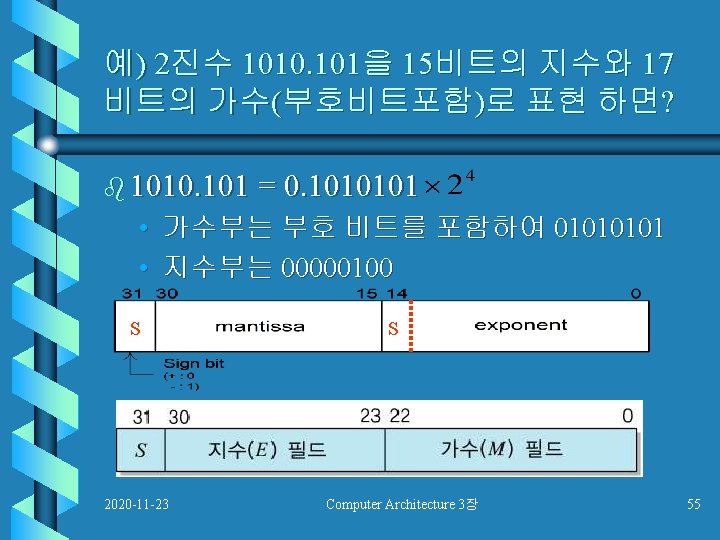

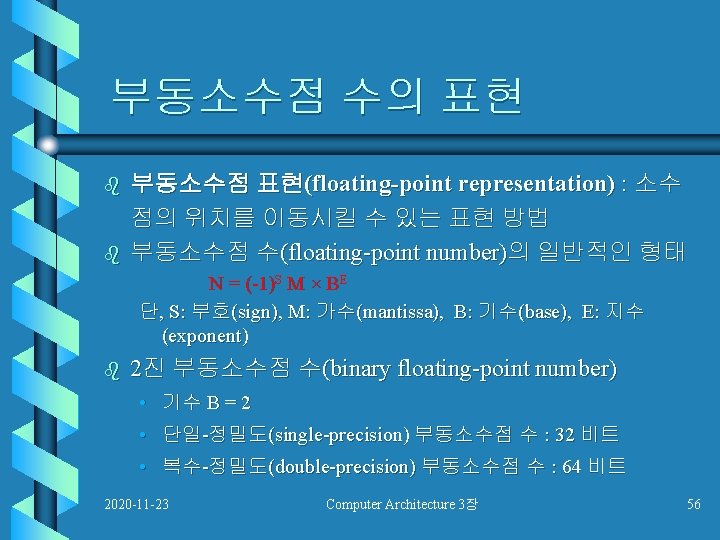

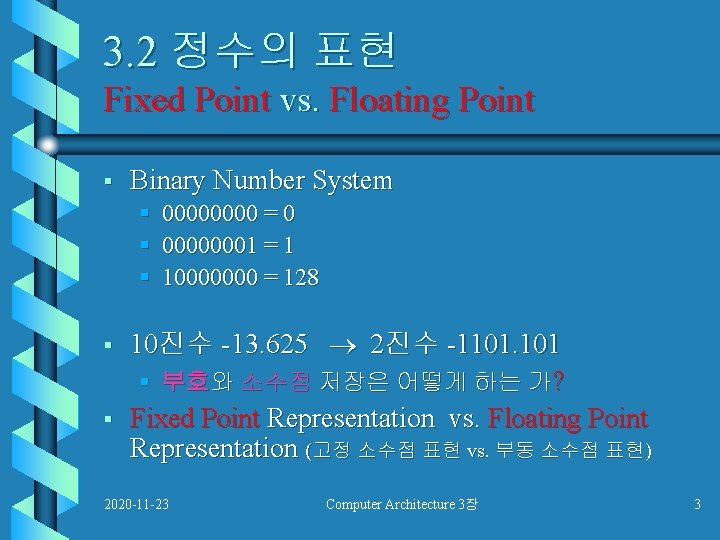

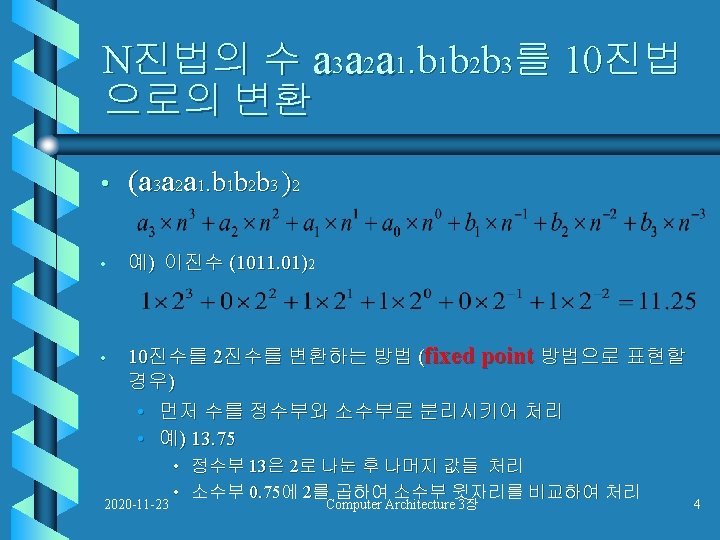

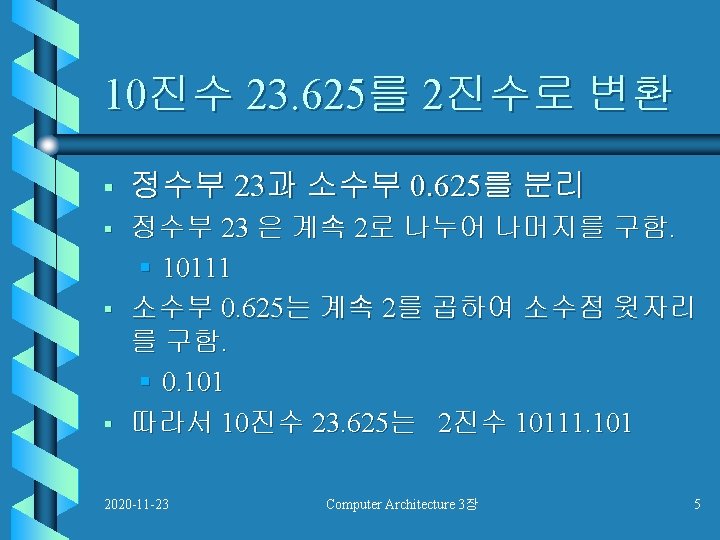

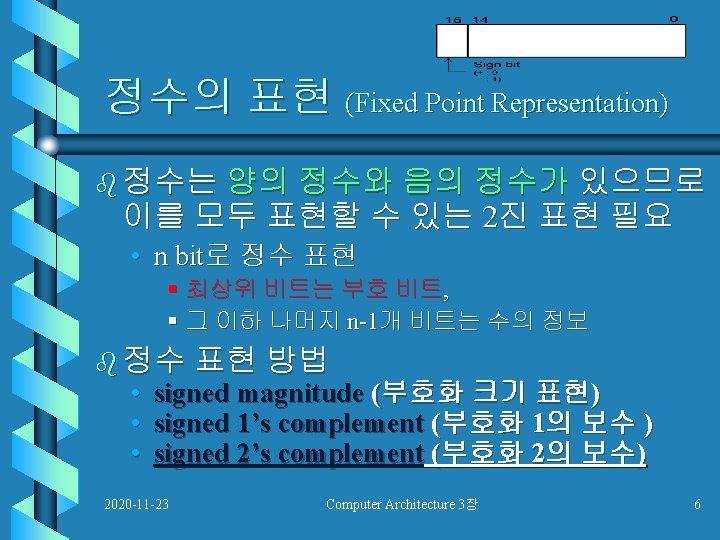

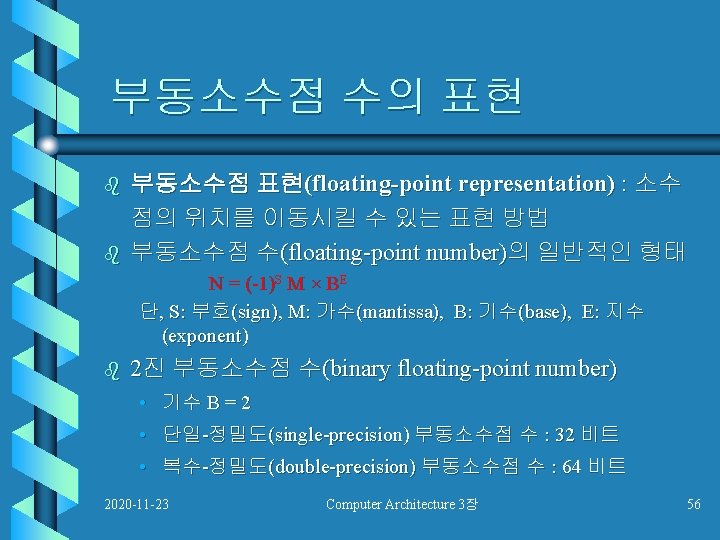

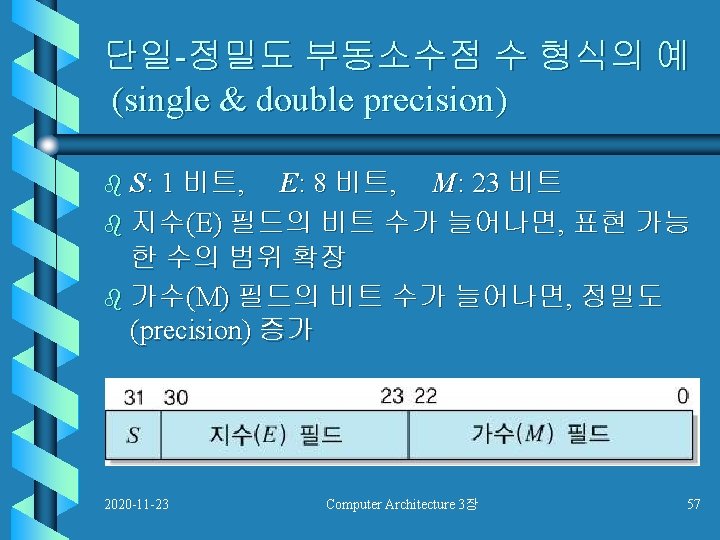

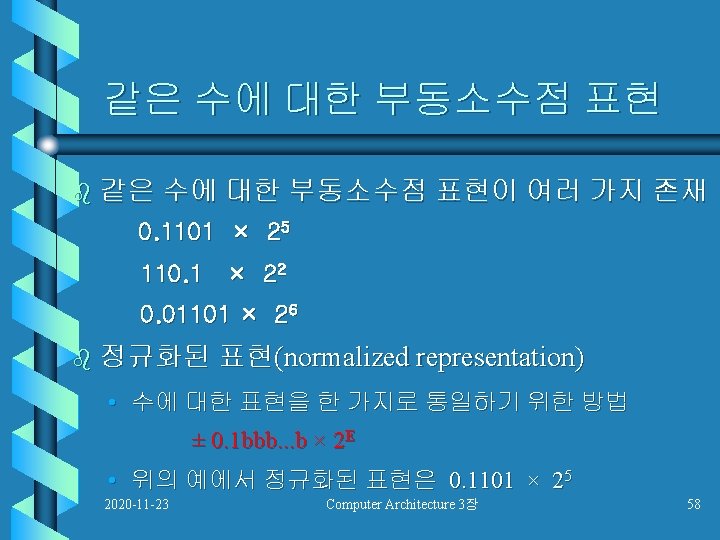

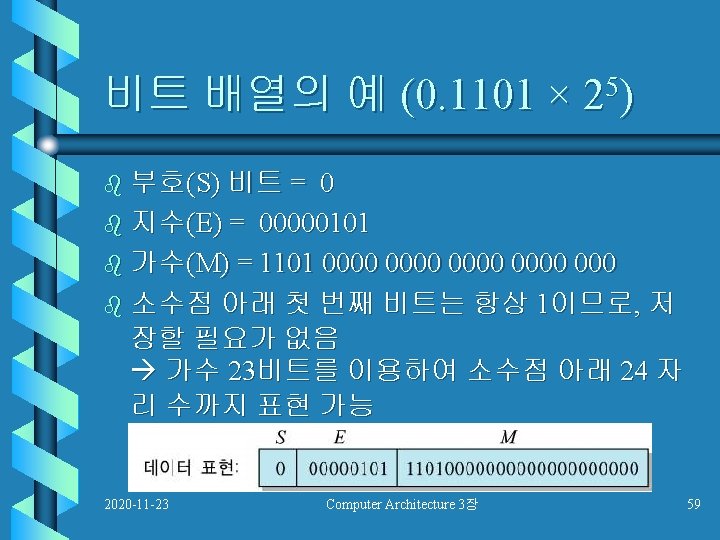

3. 2 정수의 표현 Fixed Point vs. Floating Point § Binary Number System § 0000 = 0 § 00000001 = 1 § 10000000 = 128 § § 10진수 -13. 625 2진수 -1101. 101 § 부호와 소수점 저장은 어떻게 하는 가? Fixed Point Representation vs. Floating Point Representation (고정 소수점 표현 vs. 부동 소수점 표현) 2020 -11 -23 Computer Architecture 3장 3

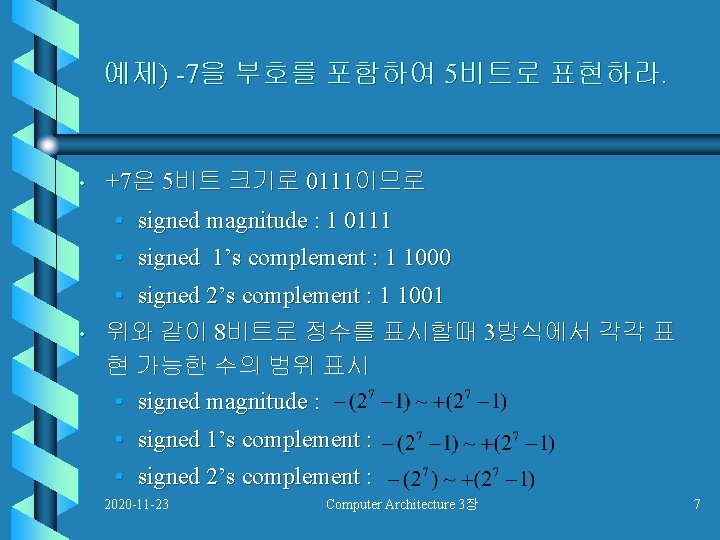

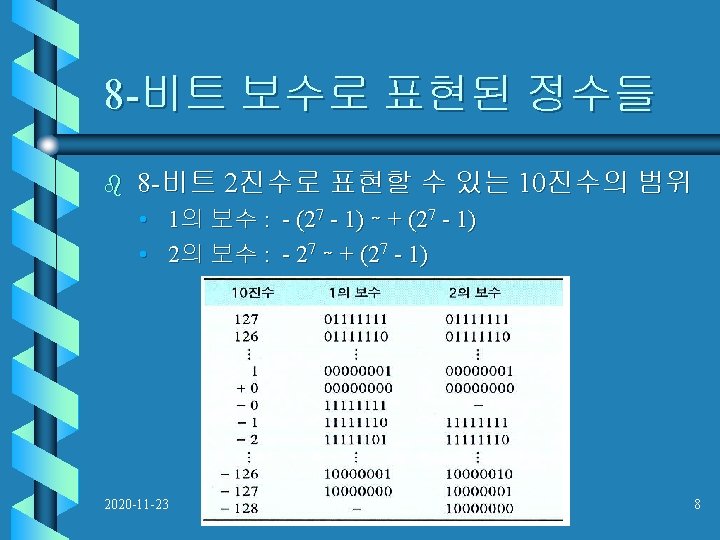

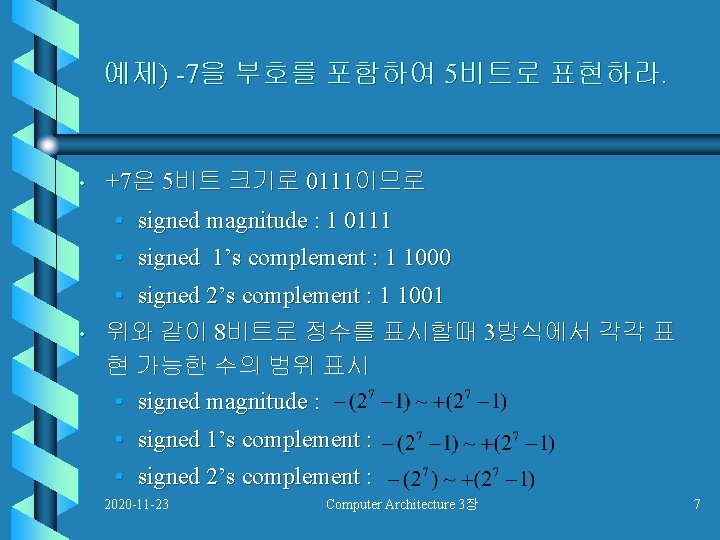

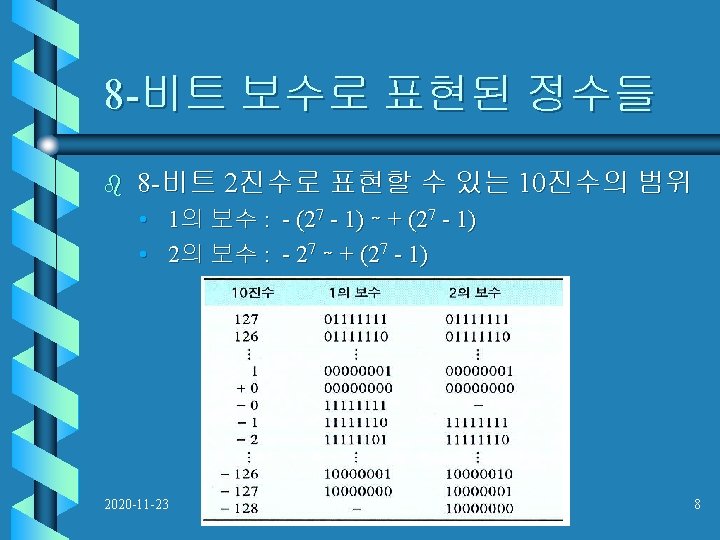

예제) -7을 부호를 포함하여 5비트로 표현하라. • +7은 5비트 크기로 0111이므로 • signed magnitude : 1 0111 • signed 1’s complement : 1 1000 • signed 2’s complement : 1 1001 • 위와 같이 8비트로 정수를 표시할때 3방식에서 각각 표 현 가능한 수의 범위 표시 • signed magnitude : • signed 1’s complement : • signed 2’s complement : 2020 -11 -23 Computer Architecture 3장 7

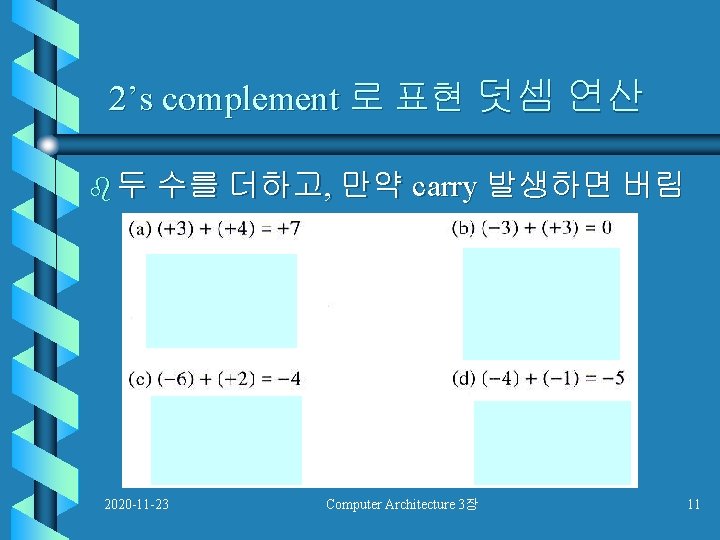

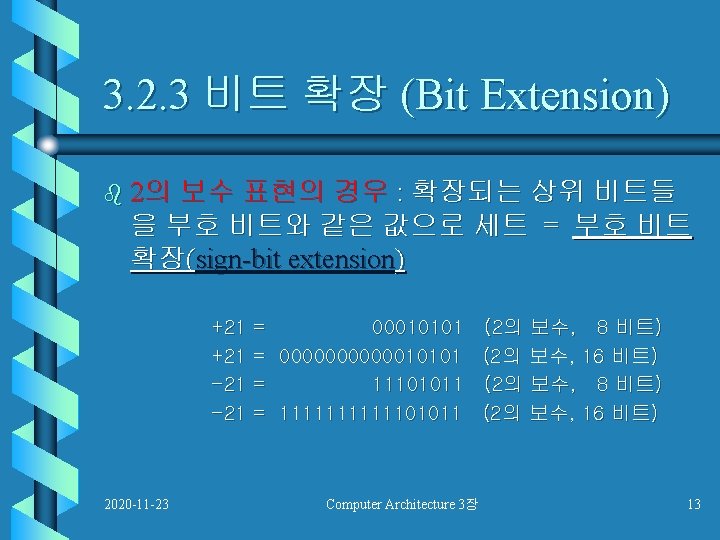

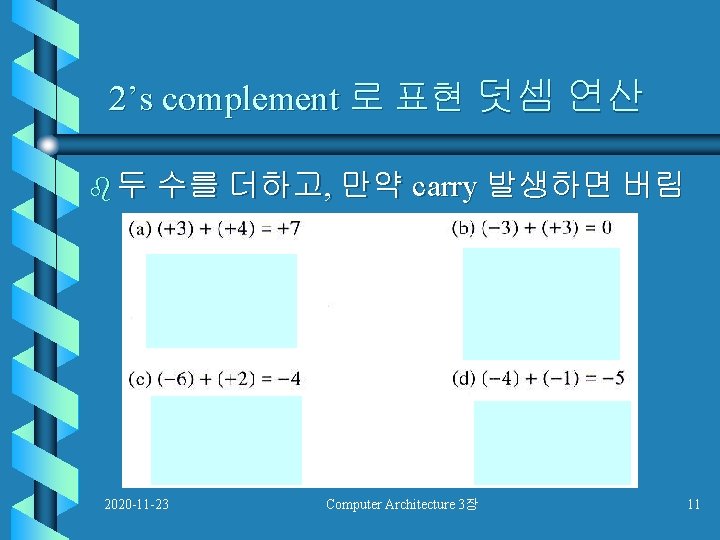

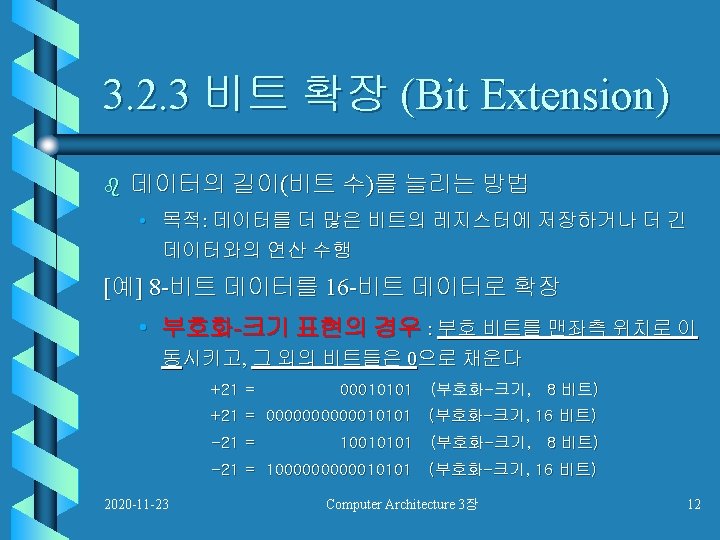

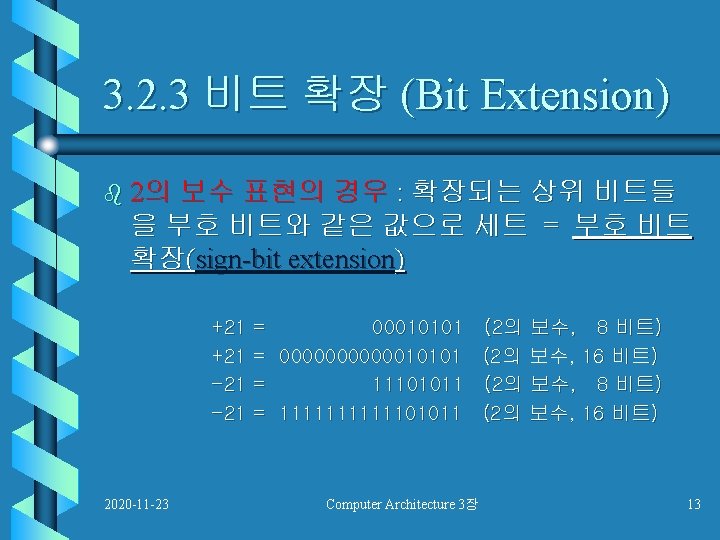

2’s complement 로 표현 덧셈 연산 b 두 수를 더하고, 만약 carry 발생하면 버림 2020 -11 -23 Computer Architecture 3장 11

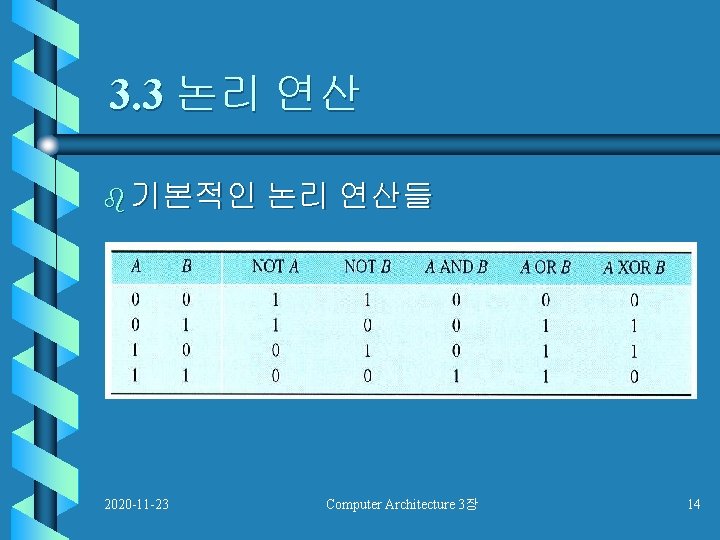

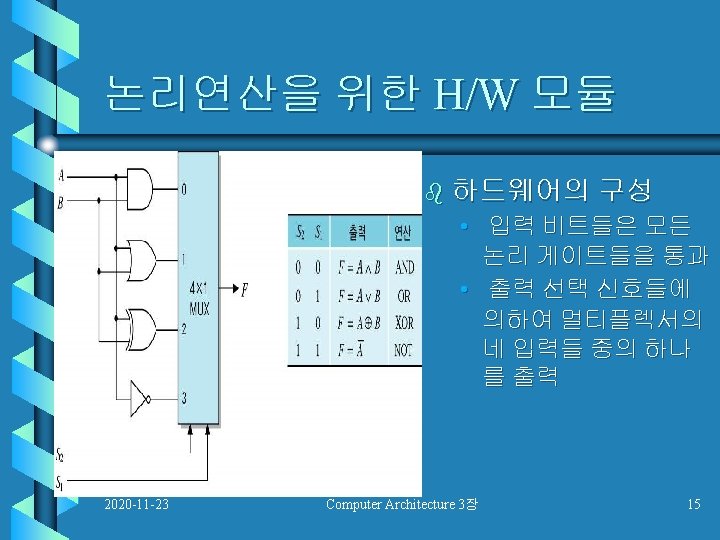

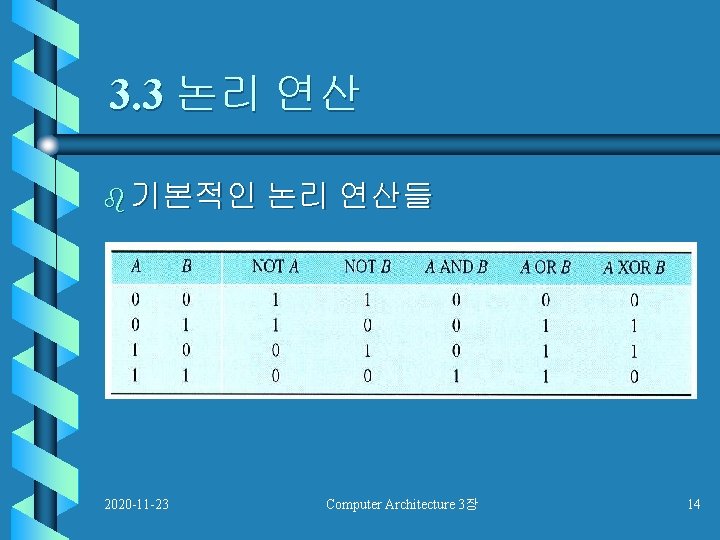

3. 3 논리 연산 b 기본적인 논리 연산들 2020 -11 -23 Computer Architecture 3장 14

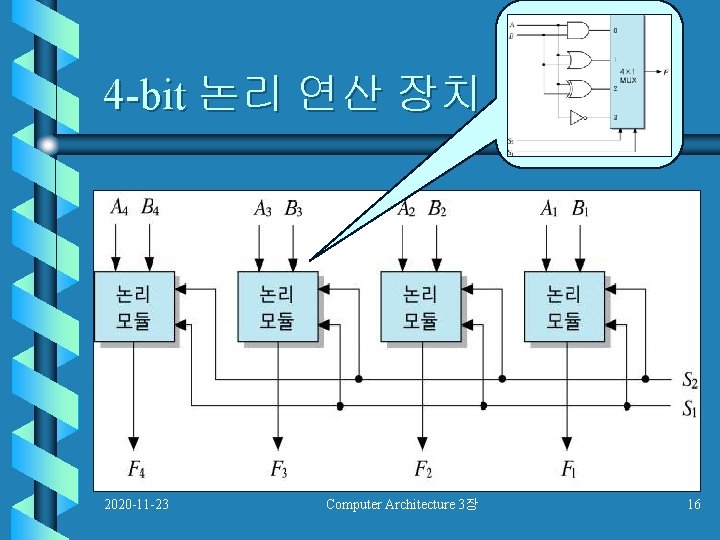

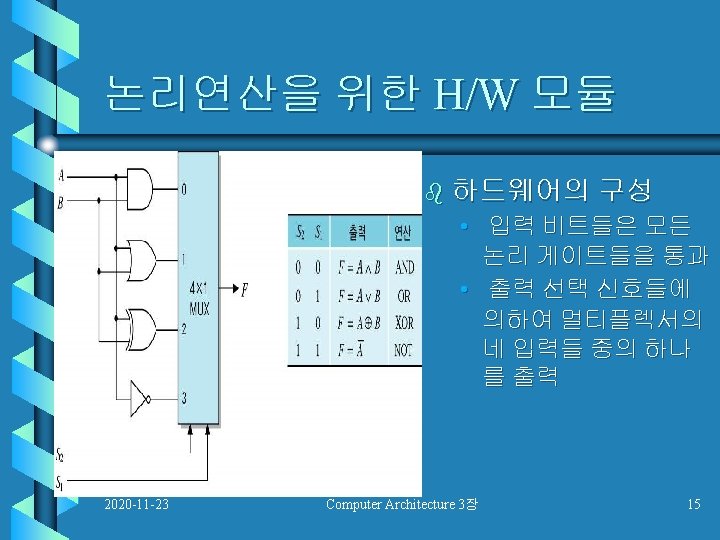

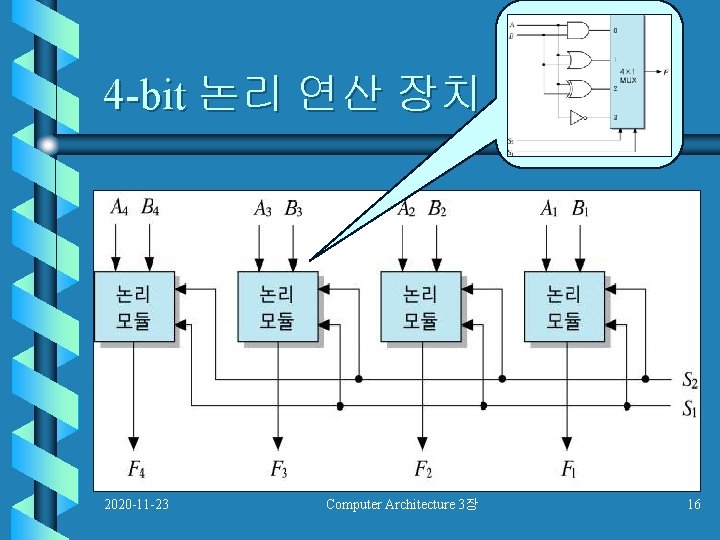

4 -bit 논리 연산 장치 2020 -11 -23 Computer Architecture 3장 16

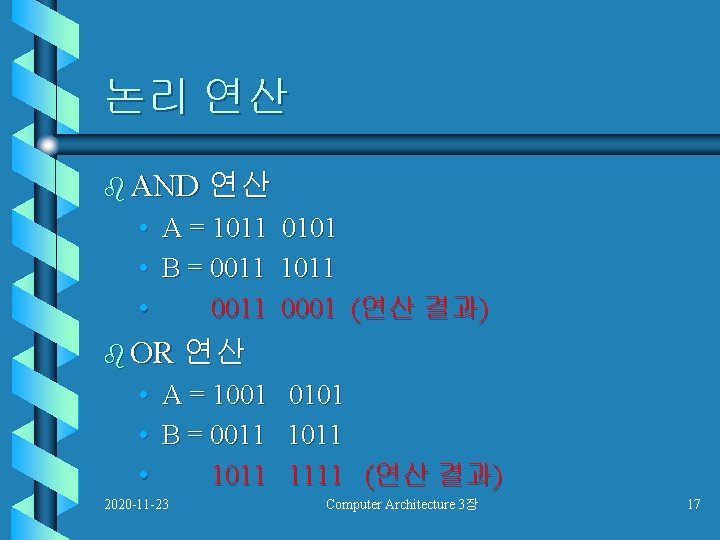

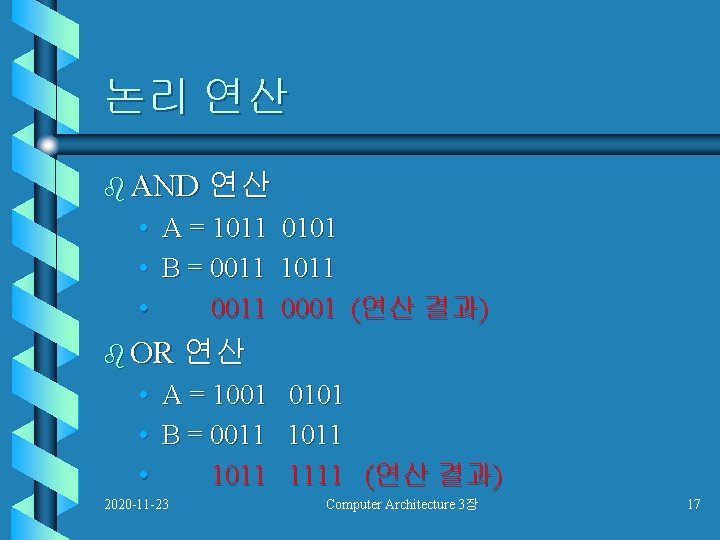

논리 연산 b AND 연산 • A = 1011 0101 • B = 0011 1011 • 0011 0001 (연산 결과) b OR 연산 • A = 1001 0101 • B = 0011 1011 • 1011 1111 (연산 결과) 2020 -11 -23 Computer Architecture 3장 17

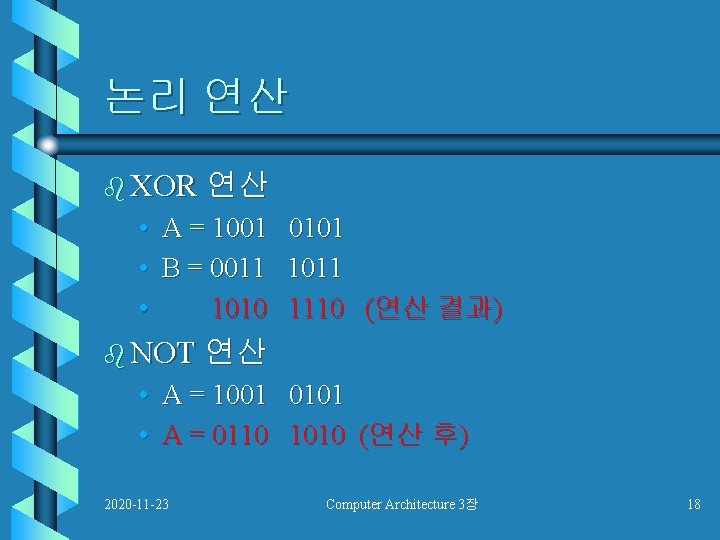

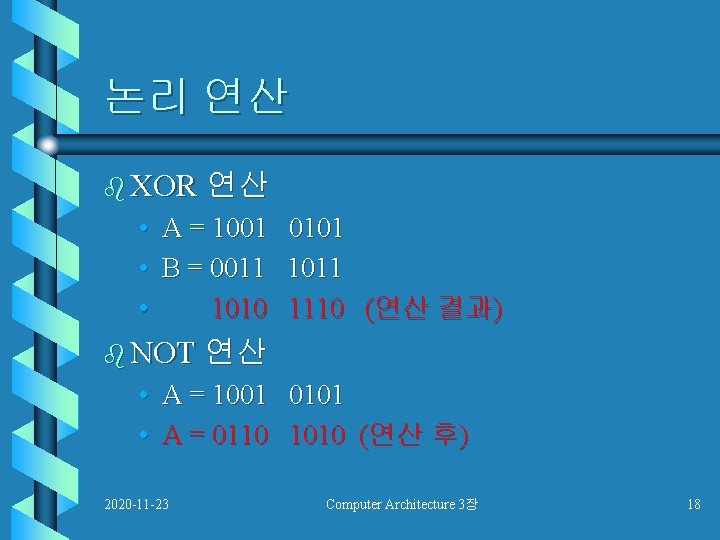

논리 연산 b XOR 연산 • A = 1001 0101 • B = 0011 1011 • 1010 1110 (연산 결과) b NOT 연산 • A = 1001 0101 • A = 0110 1010 (연산 후) 2020 -11 -23 Computer Architecture 3장 18

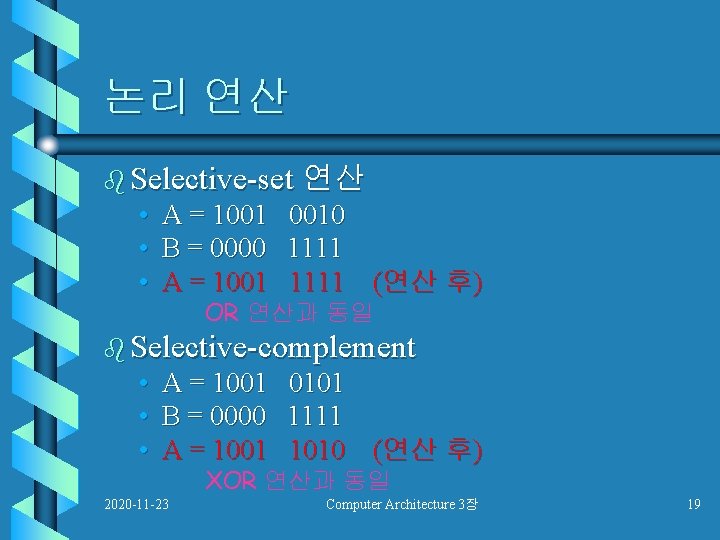

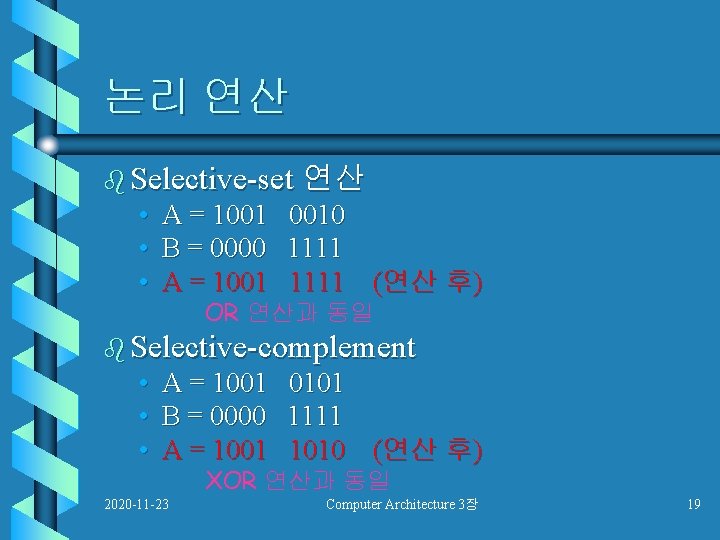

논리 연산 b Selective-set 연산 • • • A = 1001 B = 0000 A = 1001 0010 1111 (연산 후) OR 연산과 동일 b Selective-complement • • • A = 1001 B = 0000 A = 1001 2020 -11 -23 0101 1111 1010 (연산 후) XOR 연산과 동일 Computer Architecture 3장 19

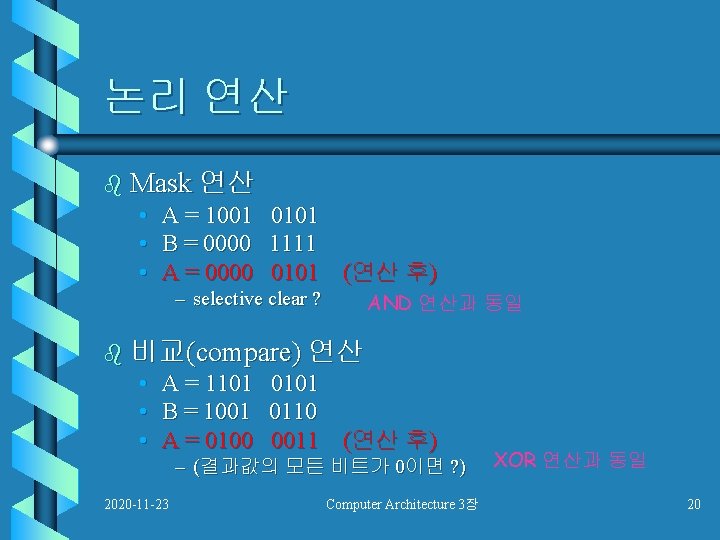

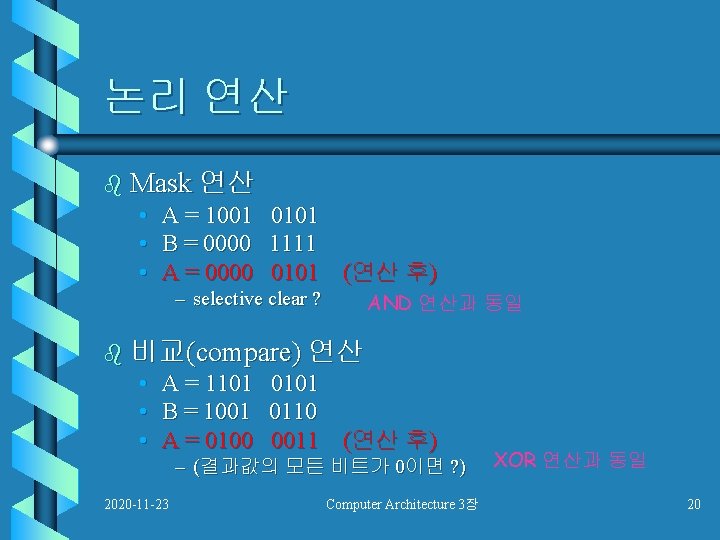

논리 연산 b Mask 연산 • • • A = 1001 B = 0000 A = 0000 0101 1111 0101 (연산 후) – selective clear ? AND 연산과 동일 b 비교(compare) 연산 • • • A = 1101 B = 1001 A = 0100 0101 0110 0011 (연산 후) – (결과값의 모든 비트가 0이면 ? ) 2020 -11 -23 Computer Architecture 3장 XOR 연산과 동일 20

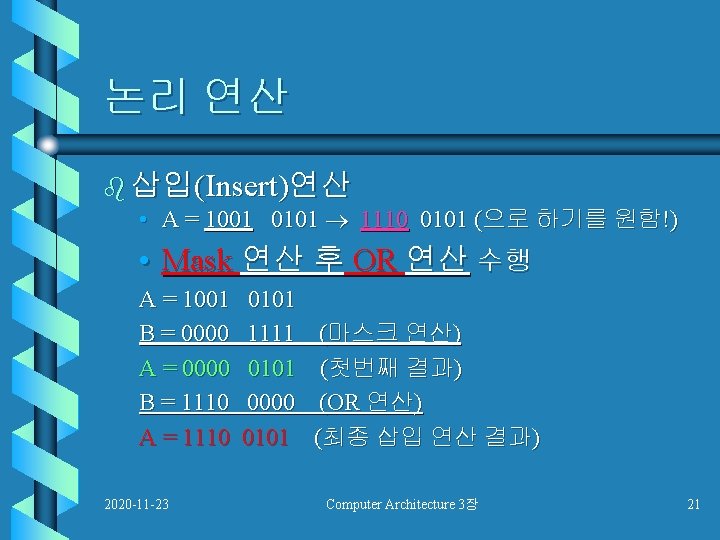

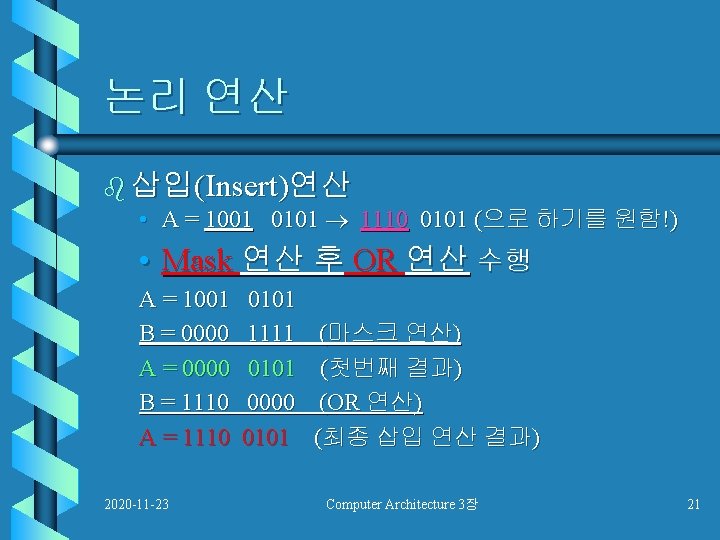

논리 연산 b 삽입(Insert)연산 • A = 1001 0101 1110 0101 (으로 하기를 원함!) • Mask 연산 후 OR 연산 수행 A = 1001 B = 0000 A = 0000 B = 1110 A = 1110 2020 -11 -23 0101 1111 0101 0000 0101 (마스크 연산) (첫번째 결과) (OR 연산) (최종 삽입 연산 결과) Computer Architecture 3장 21

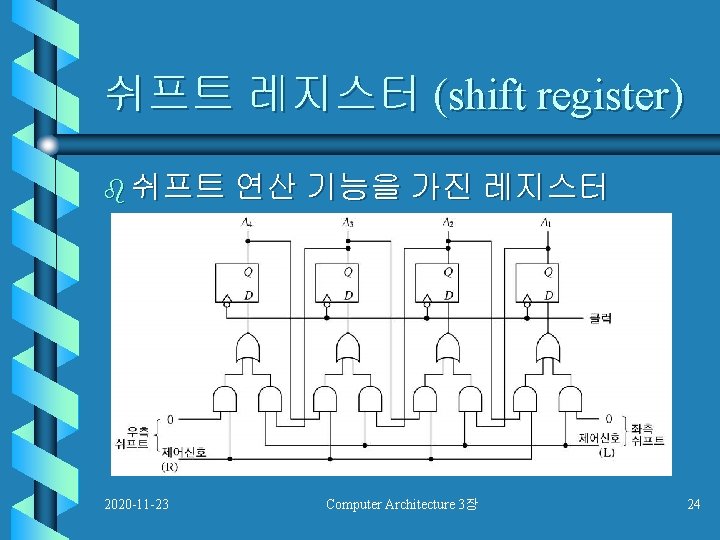

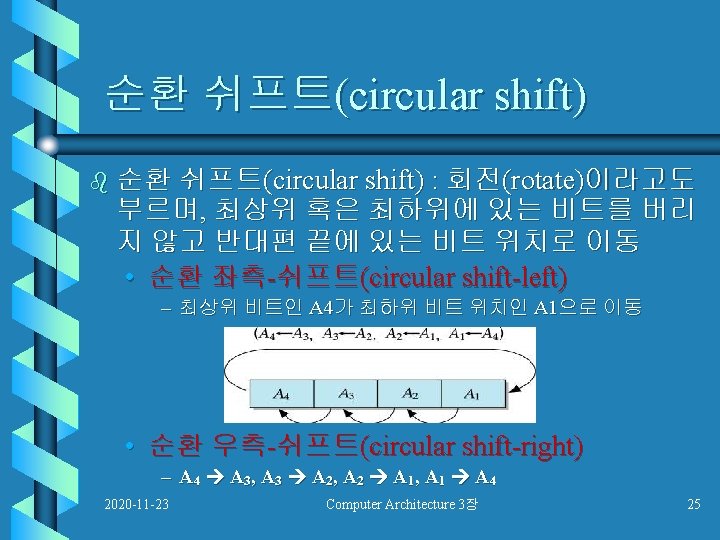

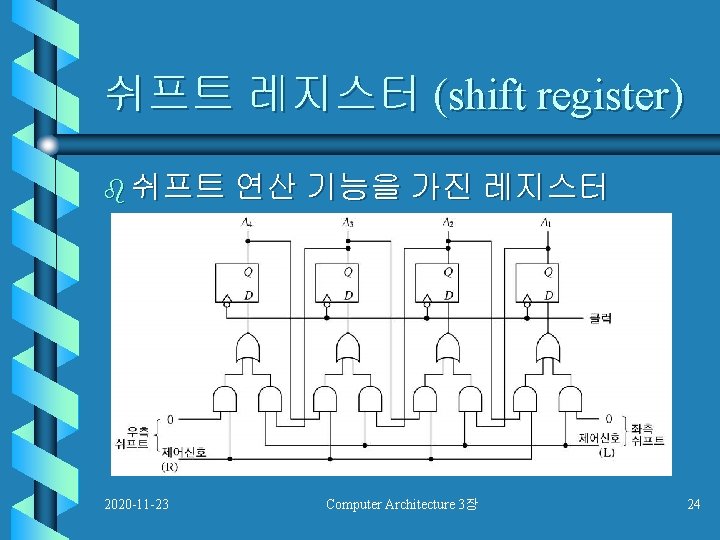

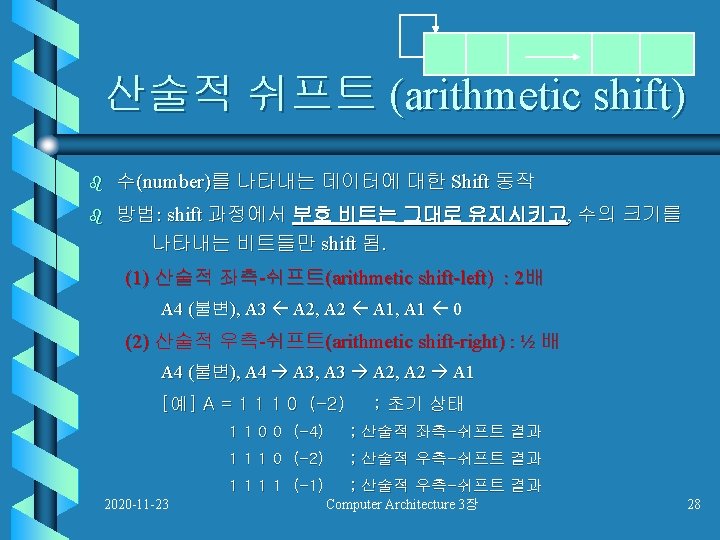

쉬프트 레지스터 (shift register) b 쉬프트 연산 기능을 가진 레지스터 2020 -11 -23 Computer Architecture 3장 24

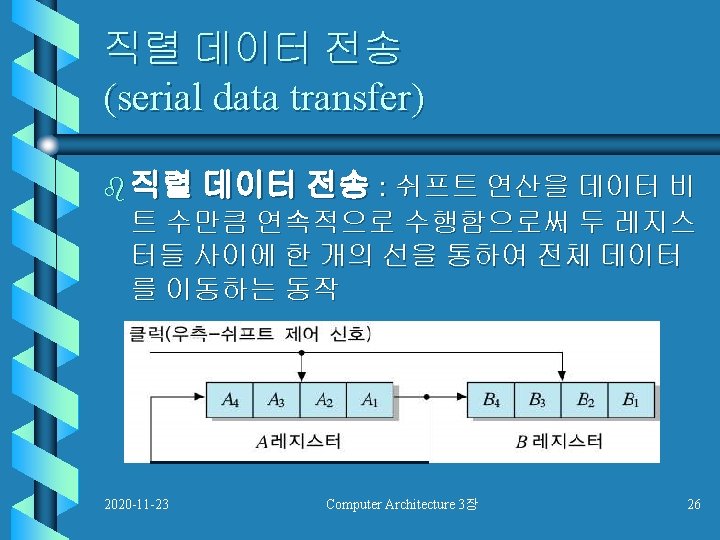

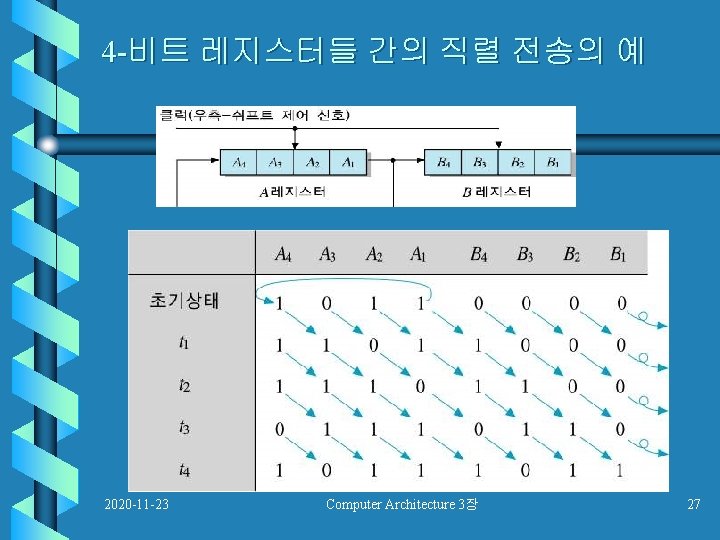

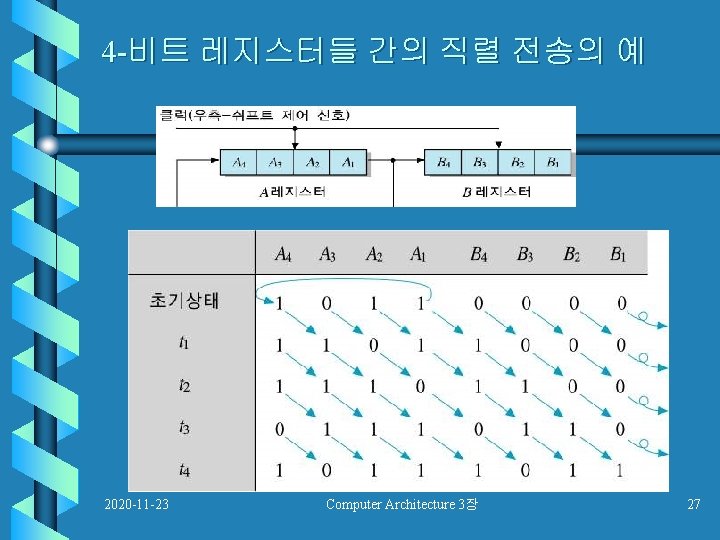

4 -비트 레지스터들 간의 직렬 전송의 예 2020 -11 -23 Computer Architecture 3장 27

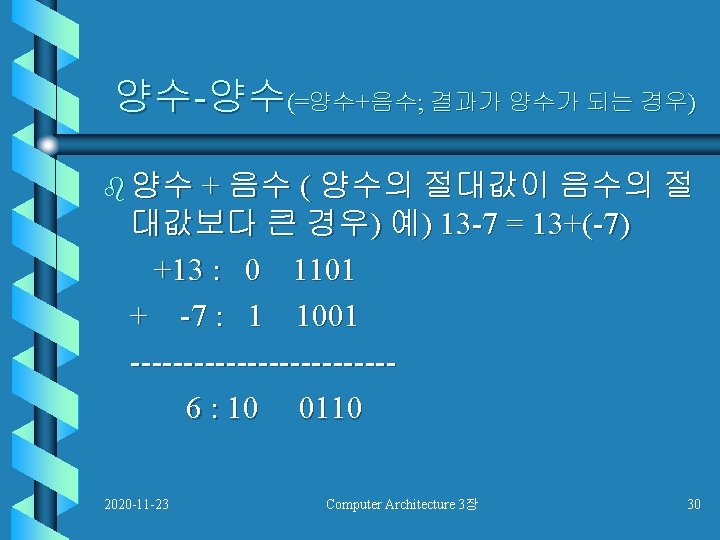

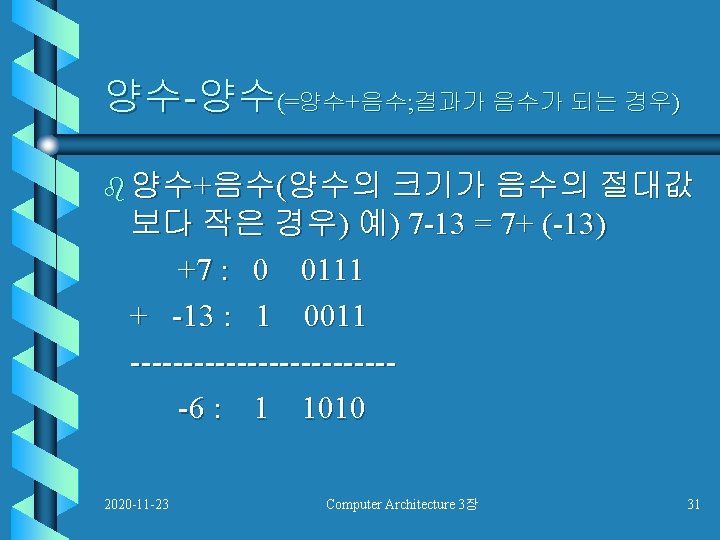

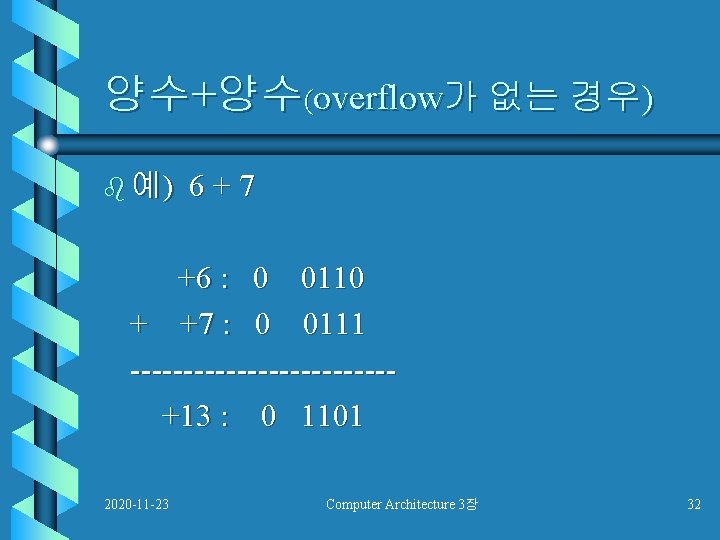

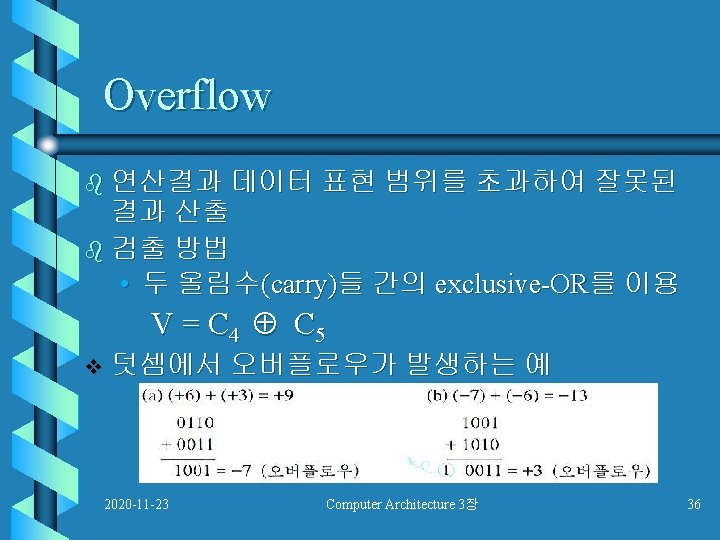

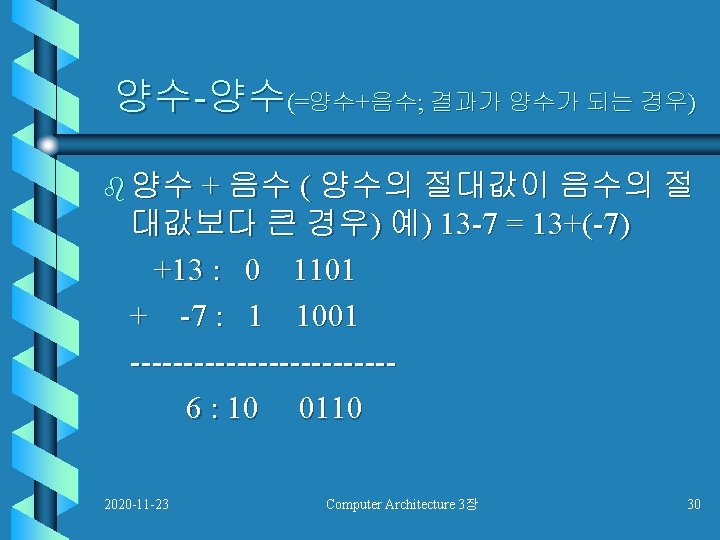

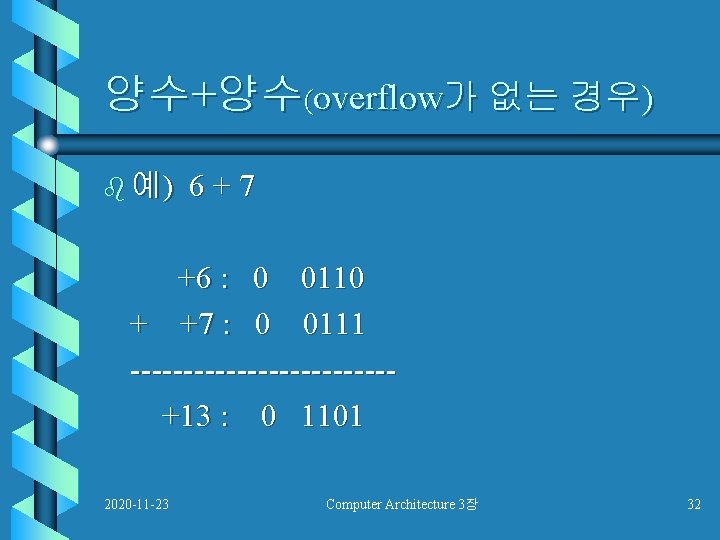

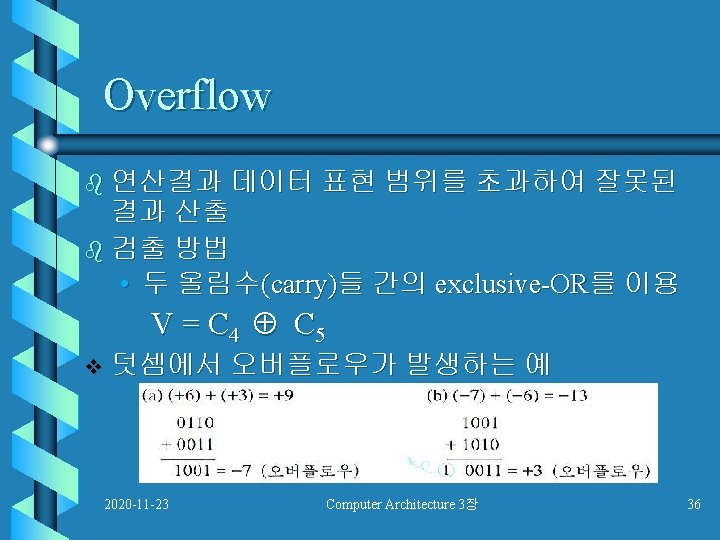

양수+양수(overflow가 없는 경우) b 예) 6+7 +6 : 0 0110 + +7 : 0 0111 ------------+13 : 0 1101 2020 -11 -23 Computer Architecture 3장 32

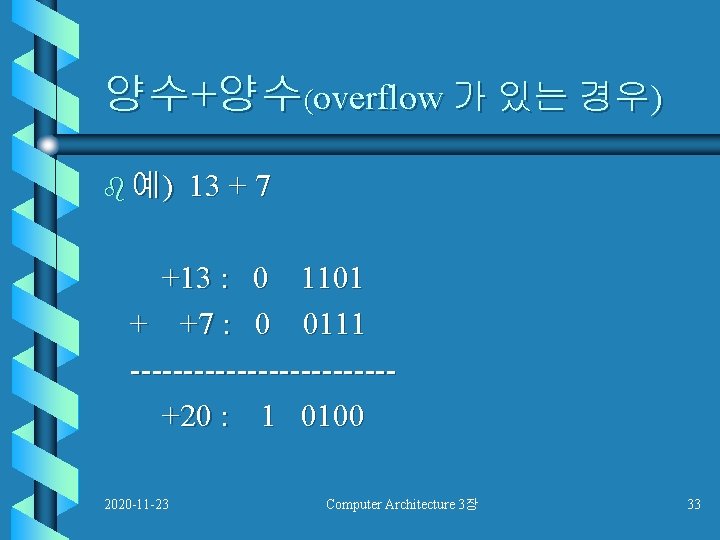

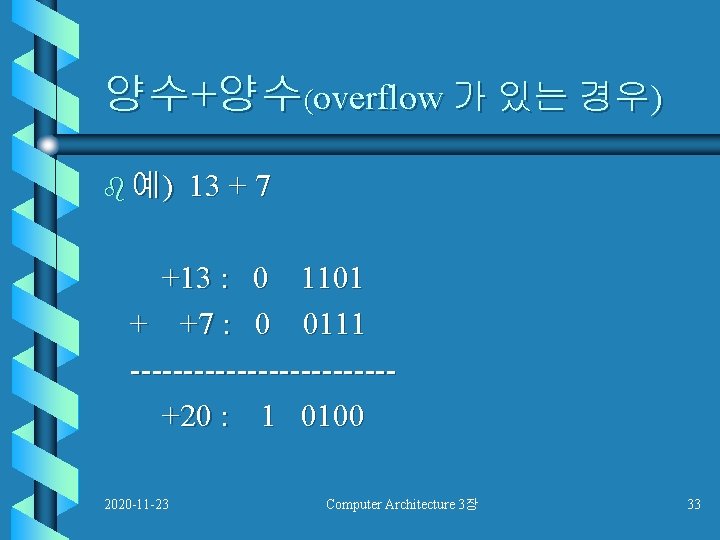

양수+양수(overflow 가 있는 경우) b 예) 13 + 7 +13 : 0 1101 + +7 : 0 0111 ------------+20 : 1 0100 2020 -11 -23 Computer Architecture 3장 33

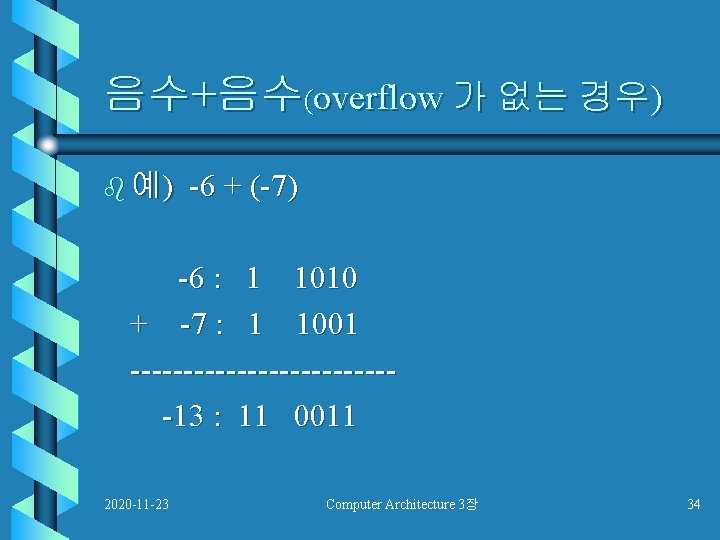

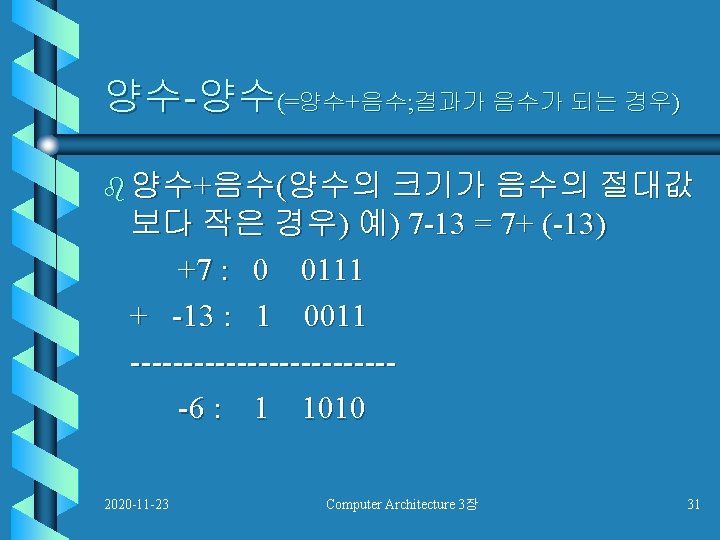

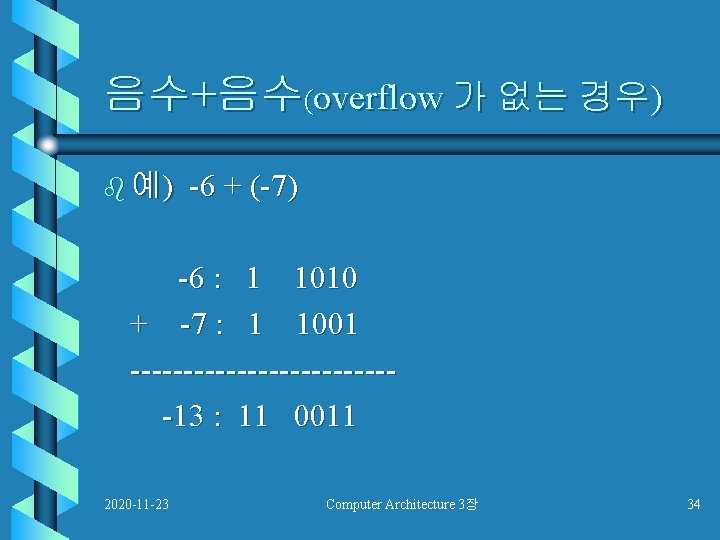

음수+음수(overflow 가 없는 경우) b 예) -6 + (-7) -6 : 1 1010 + -7 : 1 1001 -------------13 : 11 0011 2020 -11 -23 Computer Architecture 3장 34

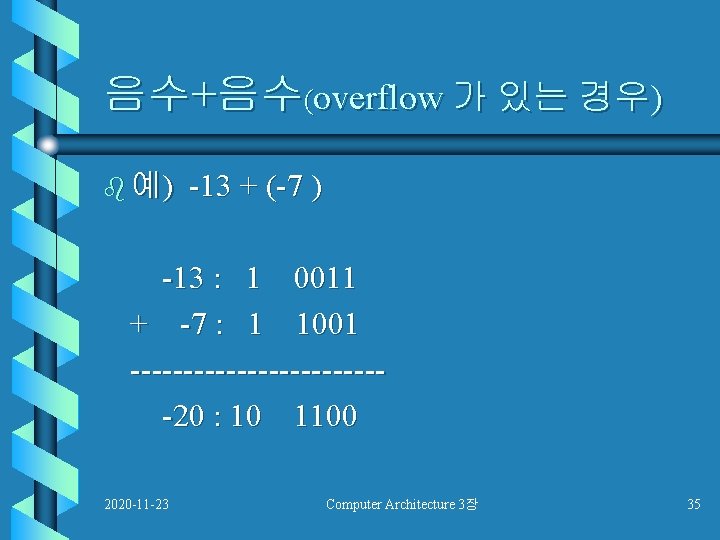

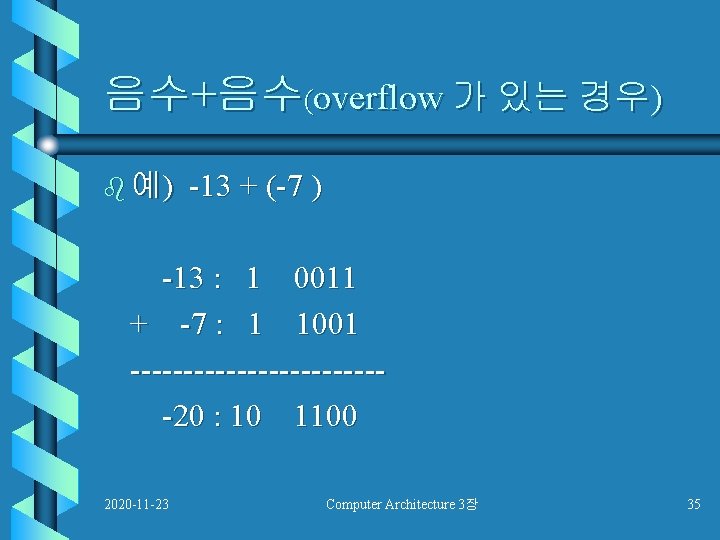

음수+음수(overflow 가 있는 경우) b 예) -13 + (-7 ) -13 : 1 0011 + -7 : 1 1001 ------------20 : 10 1100 2020 -11 -23 Computer Architecture 3장 35

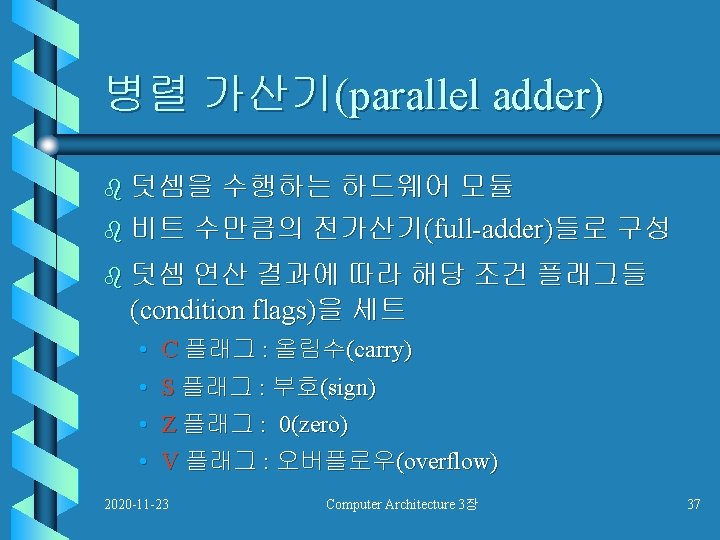

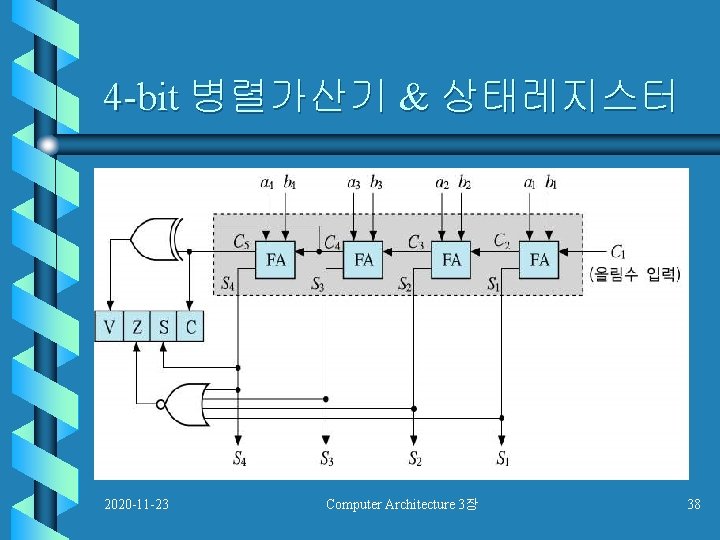

4 -bit 병렬가산기 & 상태레지스터 2020 -11 -23 Computer Architecture 3장 38

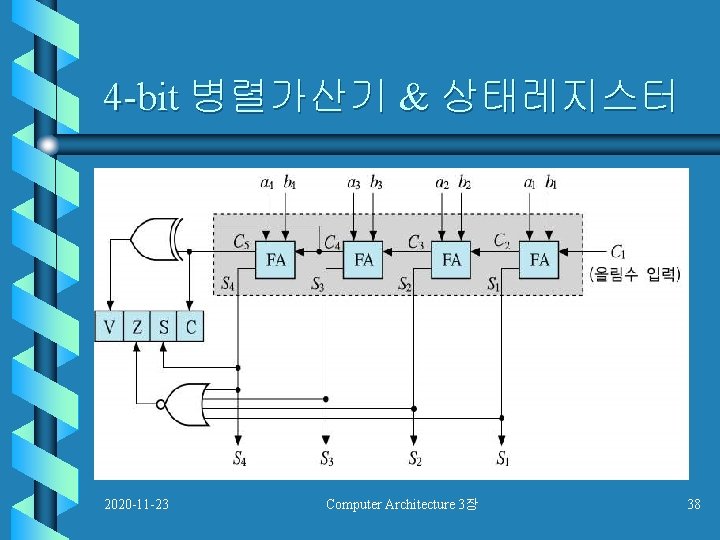

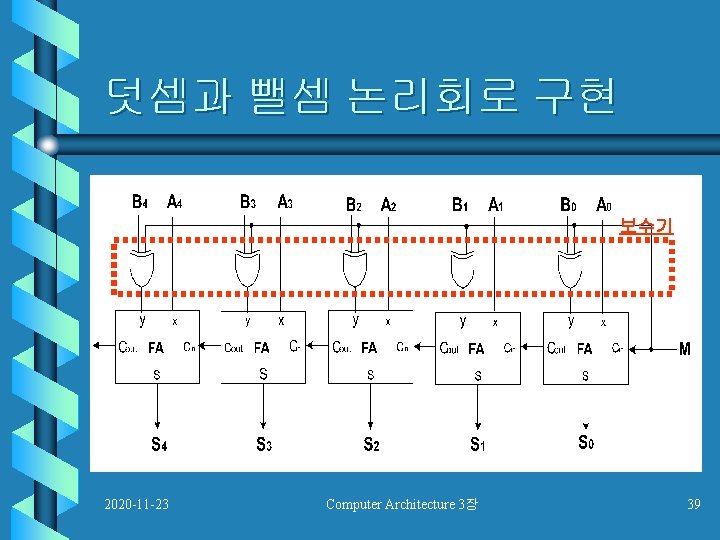

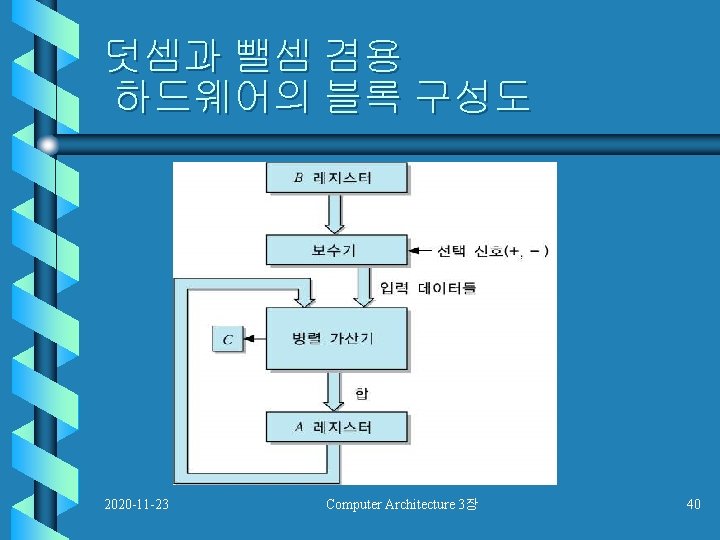

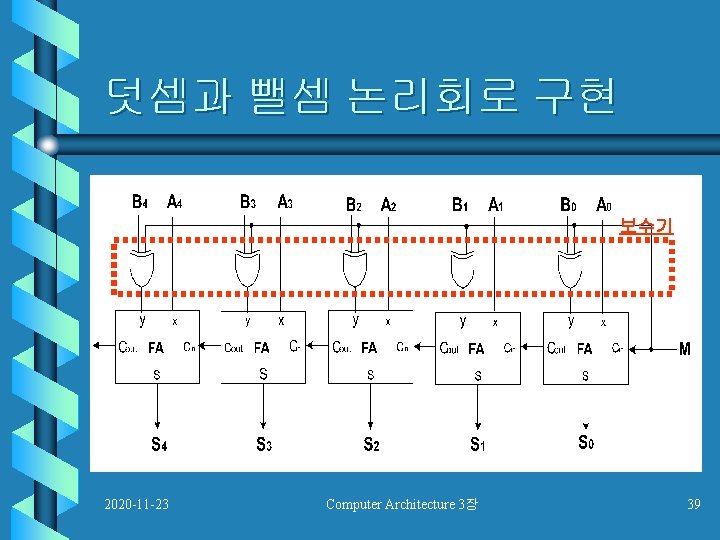

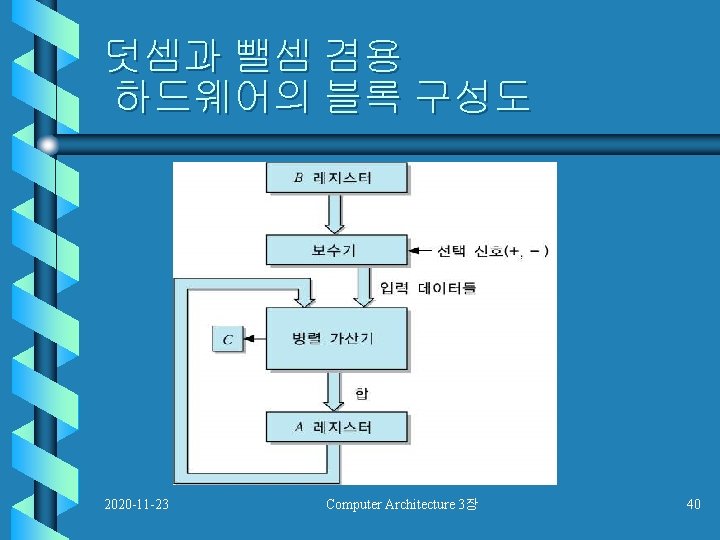

덧셈과 뺄셈 논리회로 구현 보수기 2020 -11 -23 Computer Architecture 3장 39

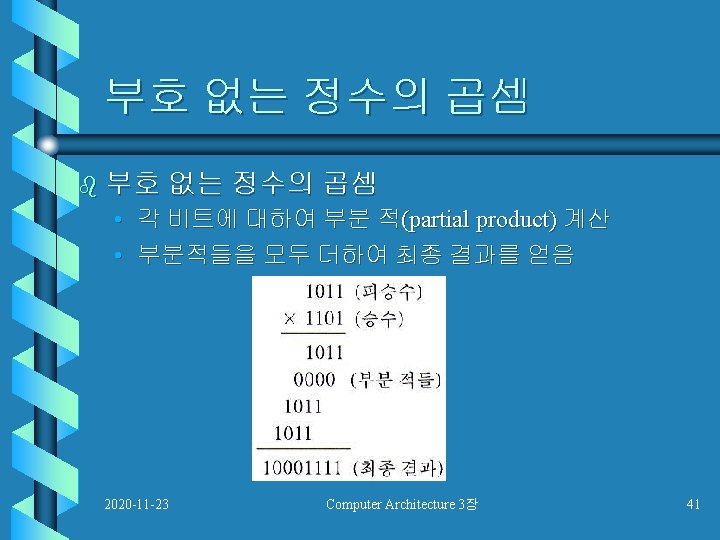

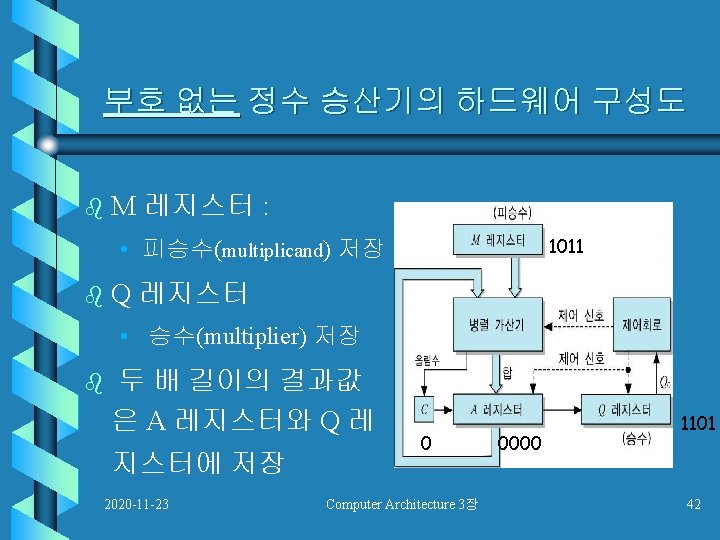

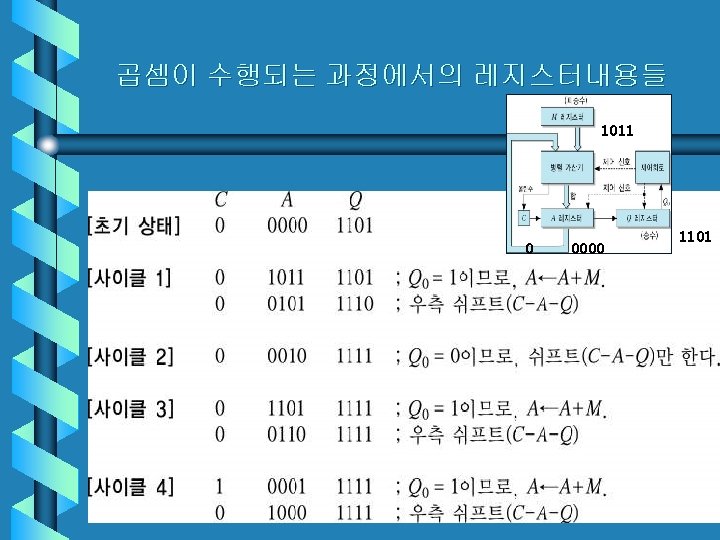

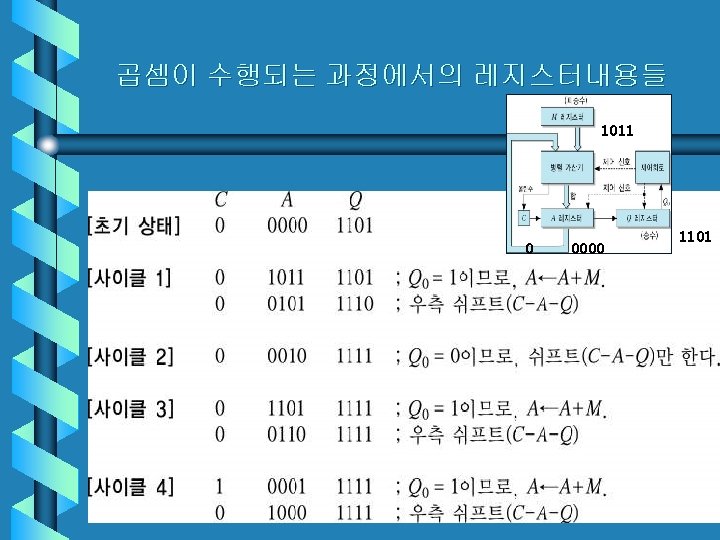

곱셈이 수행되는 과정에서의 레지스터내용들 1011 0 2020 -11 -23 Computer Architecture 3장 0000 1101 43

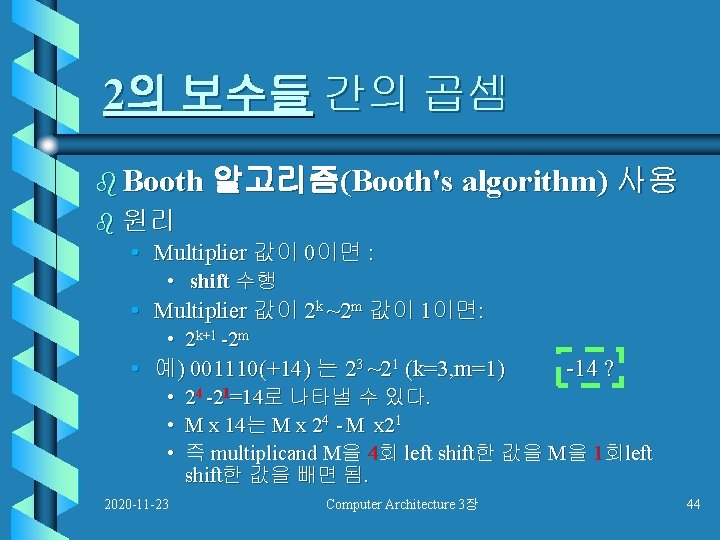

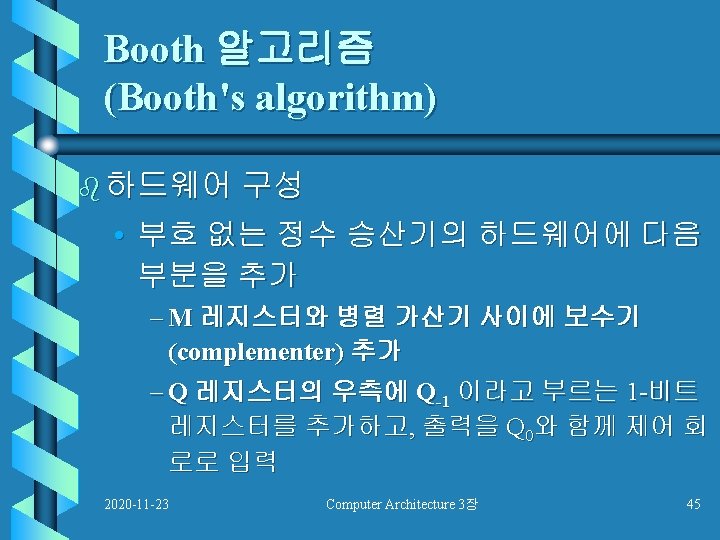

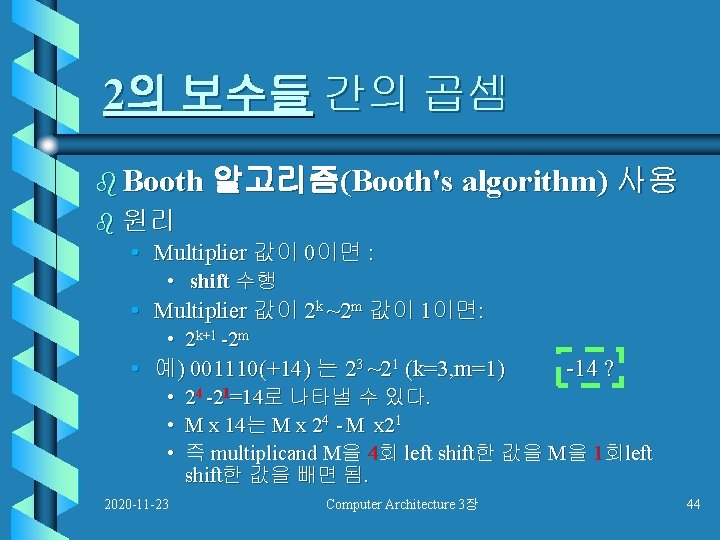

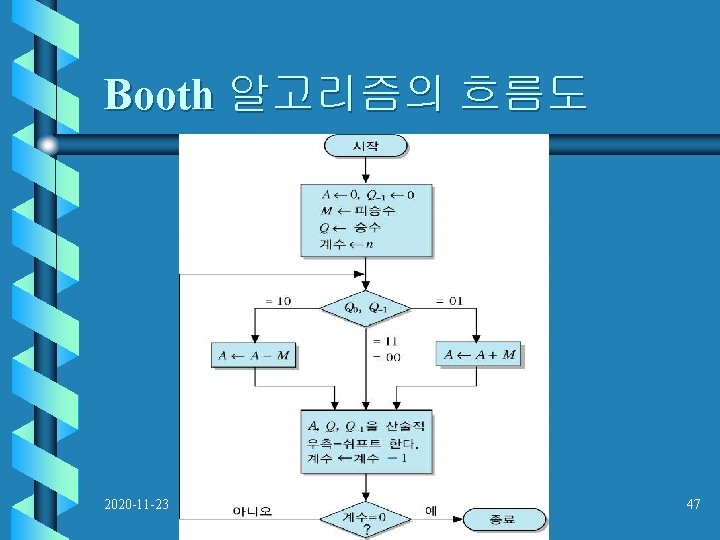

2의 보수들 간의 곱셈 b Booth 알고리즘(Booth's algorithm) 사용 b 원리 • Multiplier 값이 0이면 : • shift 수행 • Multiplier 값이 2 k ~2 m 값이 1이면: • 2 k+1 -2 m • 예) 001110(+14) 는 23 ~21 (k=3, m=1) • • • 2020 -11 -23 -14 ? 24 -21=14로 나타낼 수 있다. M x 14는 M x 24 - M x 21 즉 multiplicand M을 4회 left shift한 값을 M을 1회left shift한 값을 빼면 됨. Computer Architecture 3장 44

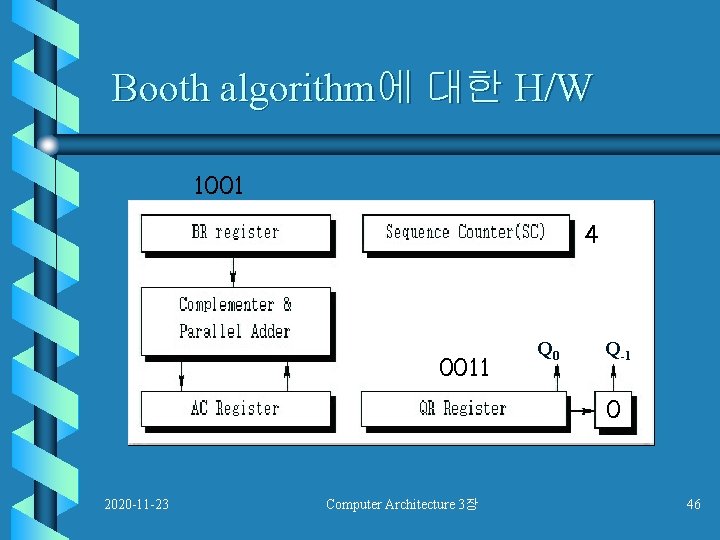

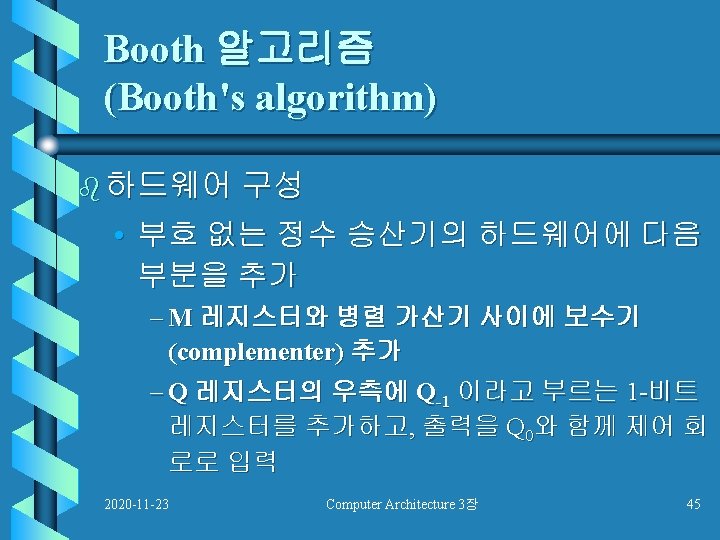

Booth algorithm에 대한 H/W 1001 4 0011 Q 0 Q-1 0 2020 -11 -23 Computer Architecture 3장 46

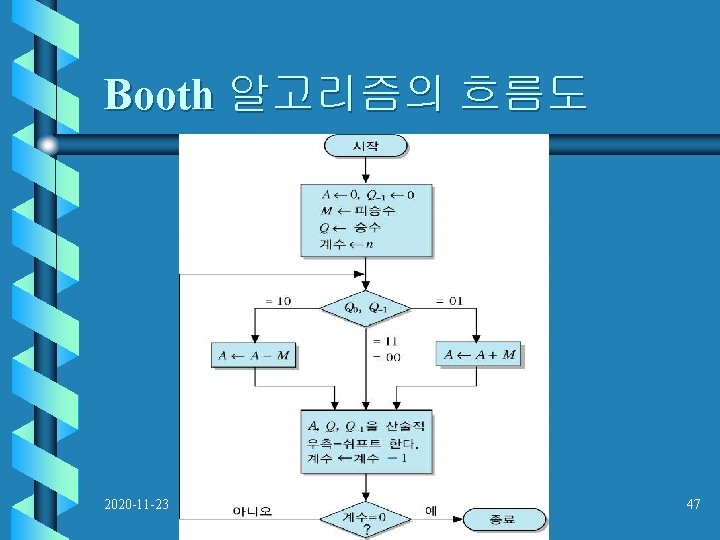

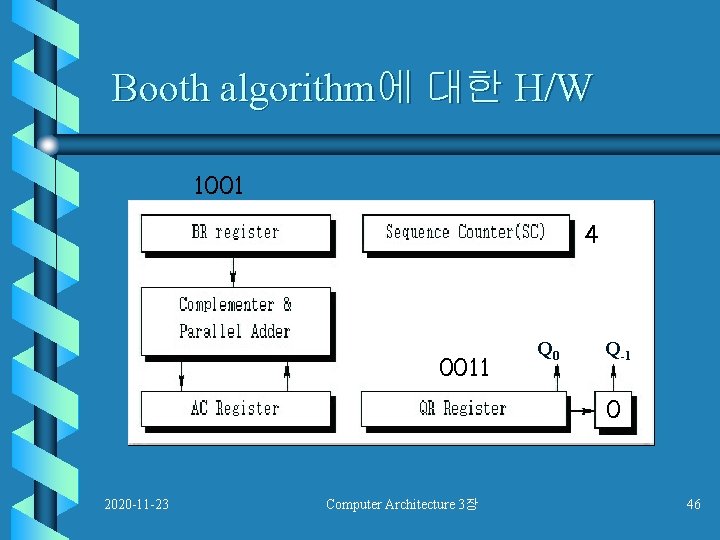

Booth 알고리즘의 흐름도 2020 -11 -23 Computer Architecture 3장 47

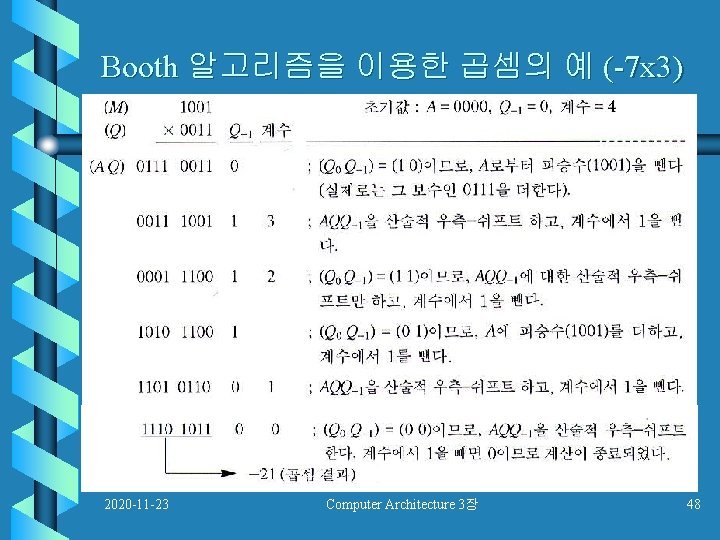

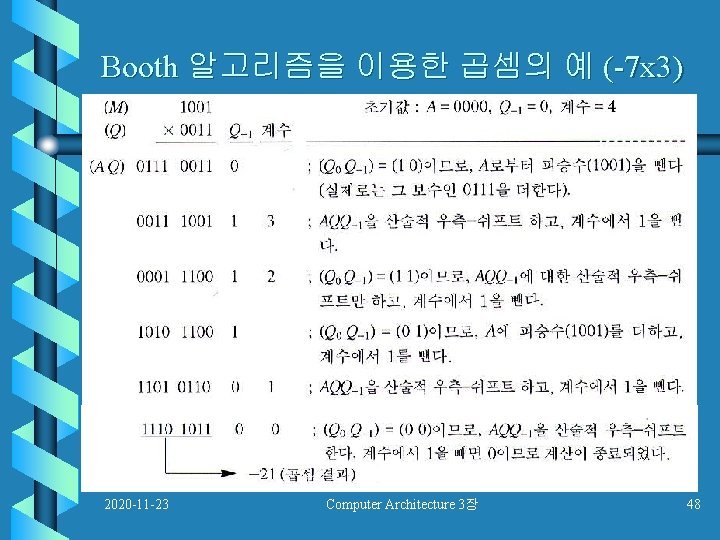

Booth 알고리즘을 이용한 곱셈의 예 (-7 x 3) 2020 -11 -23 Computer Architecture 3장 48

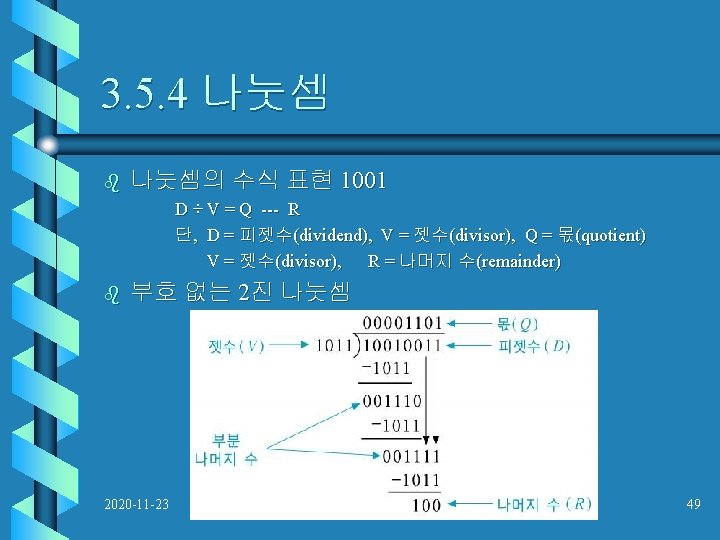

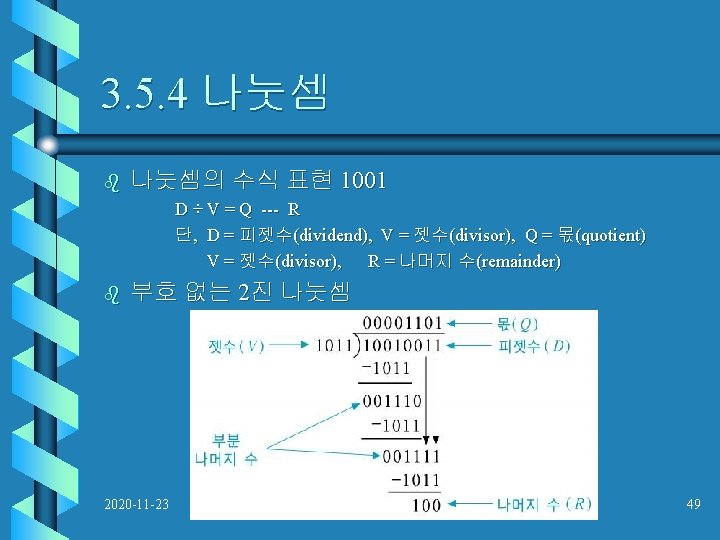

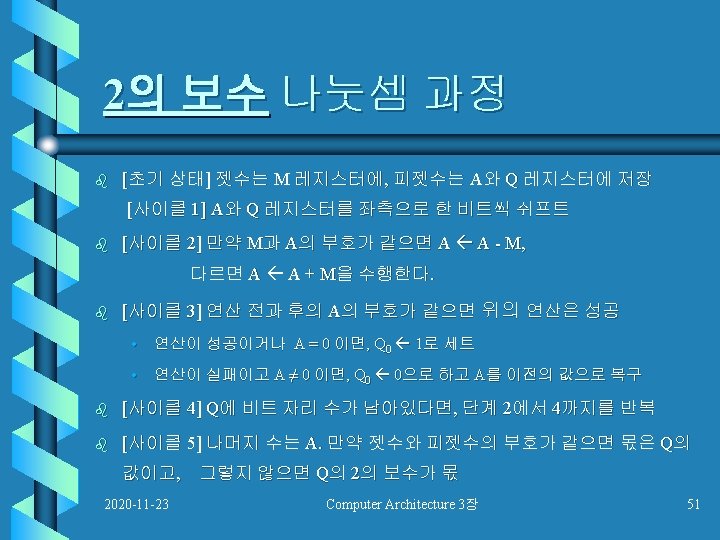

3. 5. 4 나눗셈 b 나눗셈의 수식 표현 1001 D ÷ V = Q --- R 단, D = 피젯수(dividend), V = 젯수(divisor), Q = 몫(quotient) V = 젯수(divisor), R = 나머지 수(remainder) b 부호 없는 2진 나눗셈 2020 -11 -23 Computer Architecture 3장 49

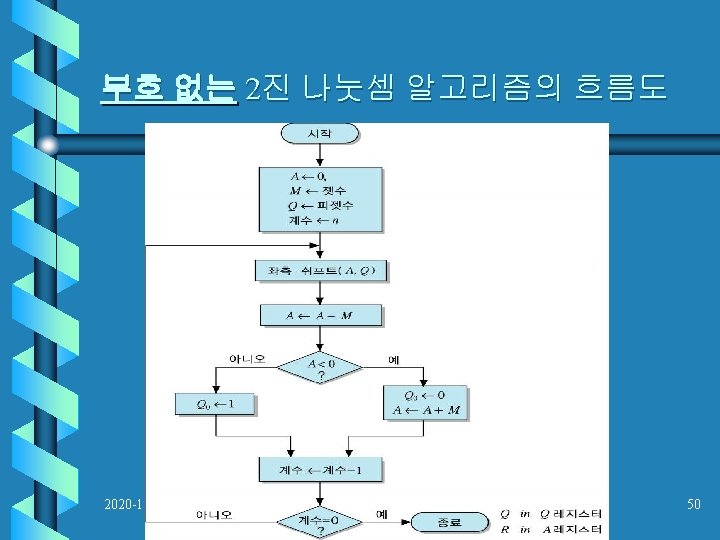

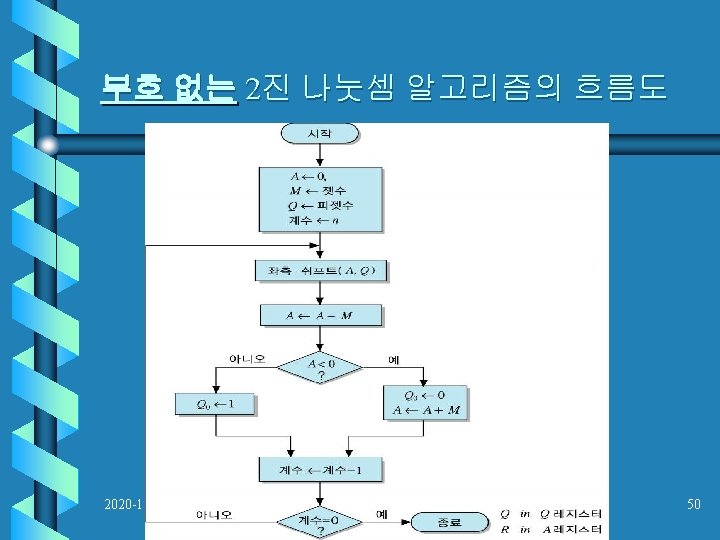

부호 없는 2진 나눗셈 알고리즘의 흐름도 2020 -11 -23 Computer Architecture 3장 50

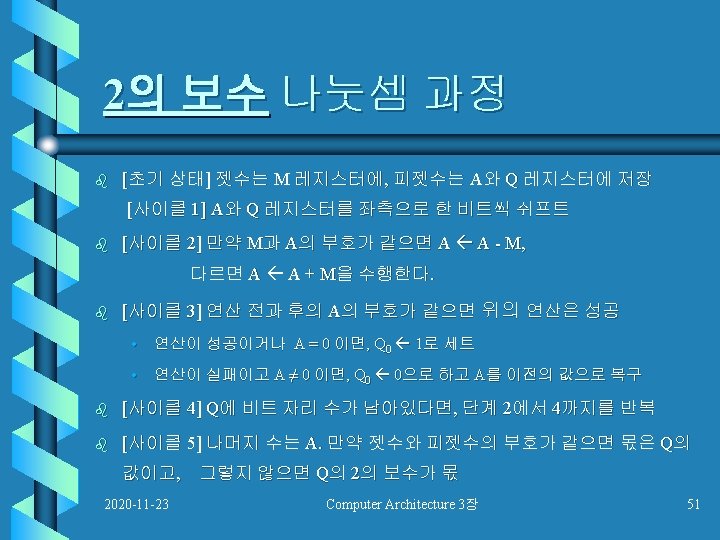

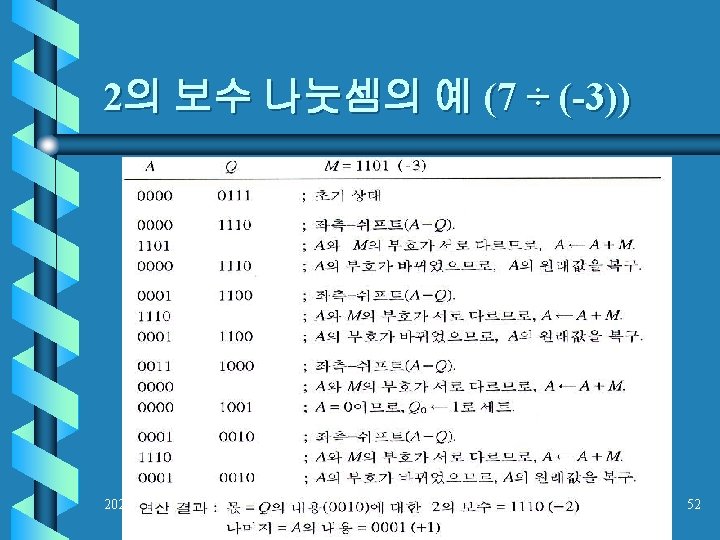

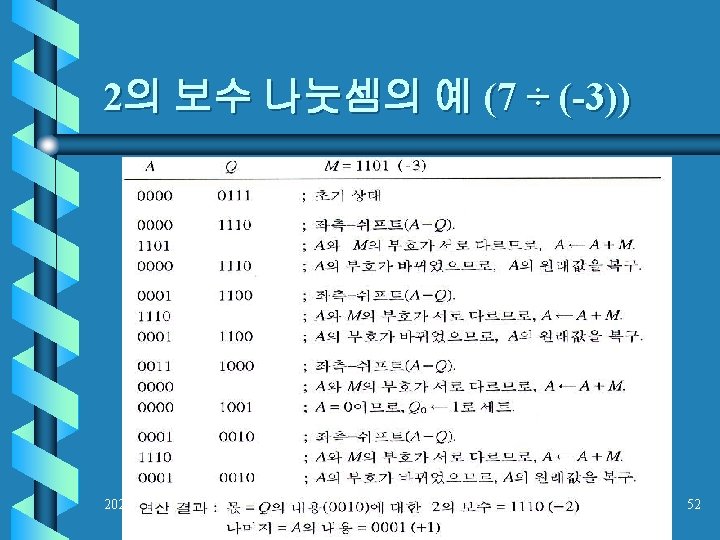

2의 보수 나눗셈의 예 (7 ÷ (-3)) 2020 -11 -23 Computer Architecture 3장 52

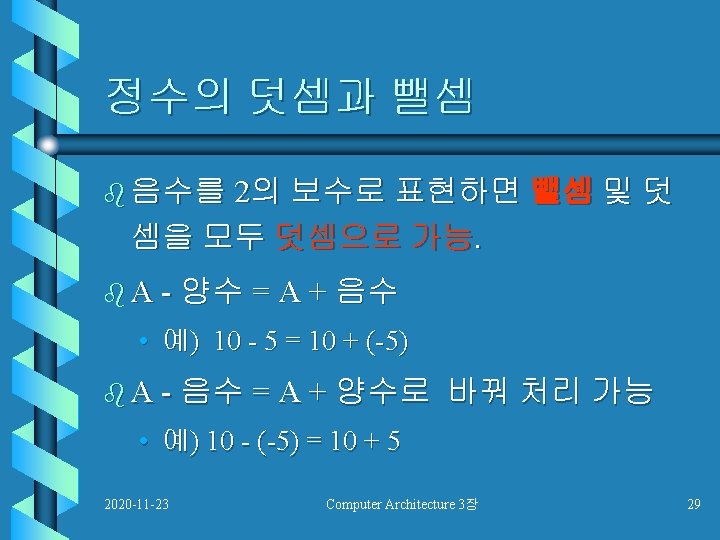

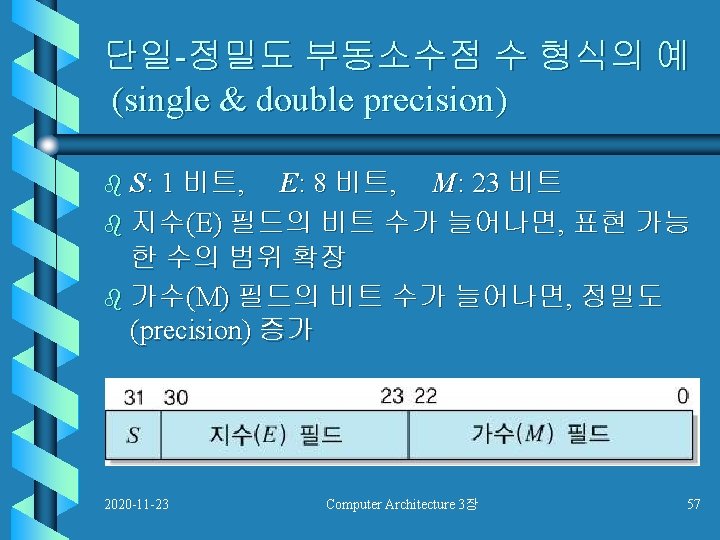

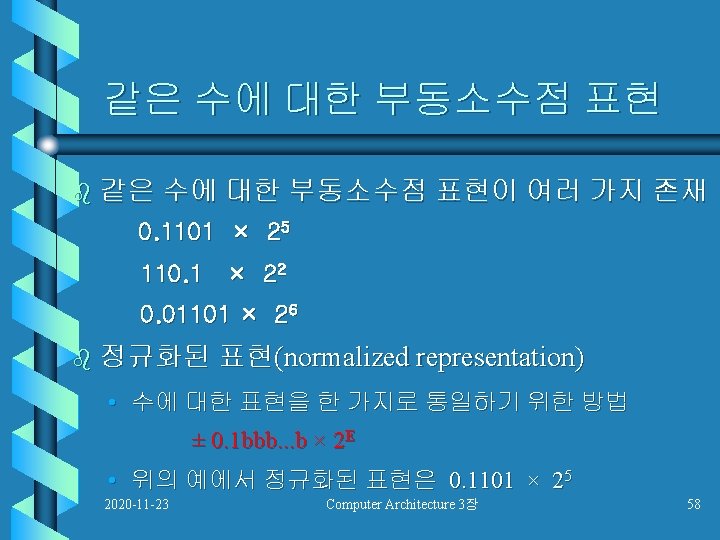

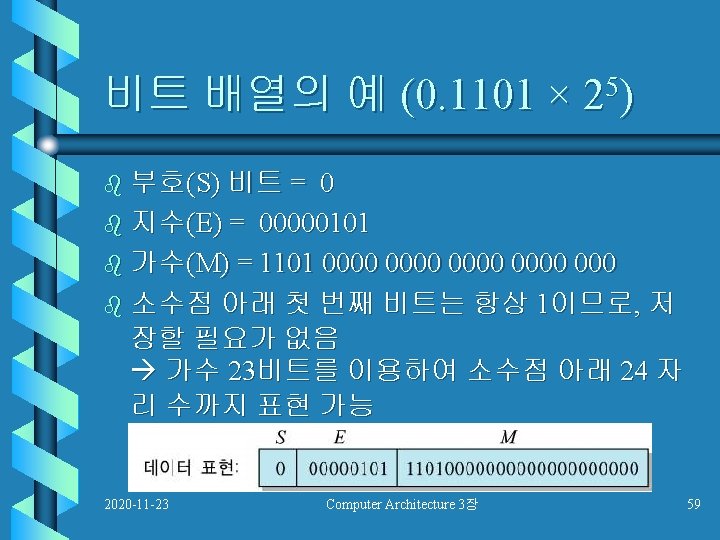

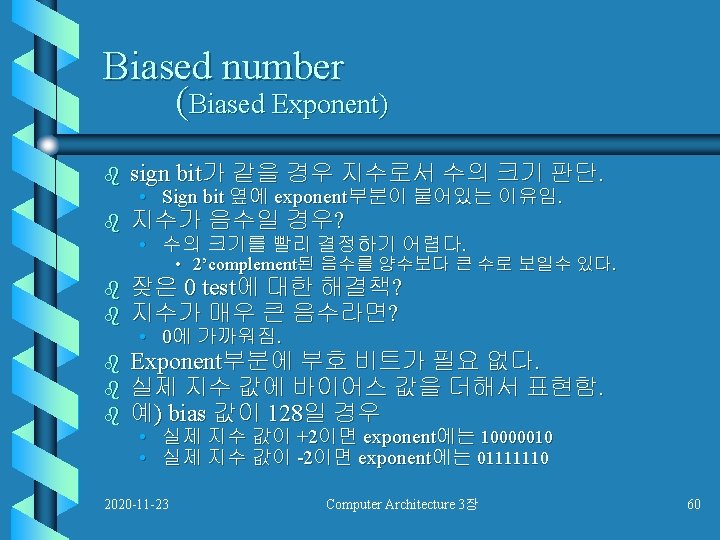

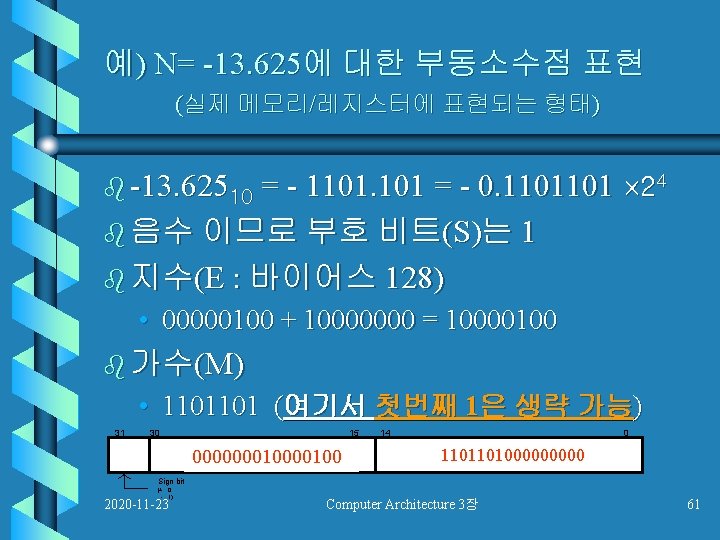

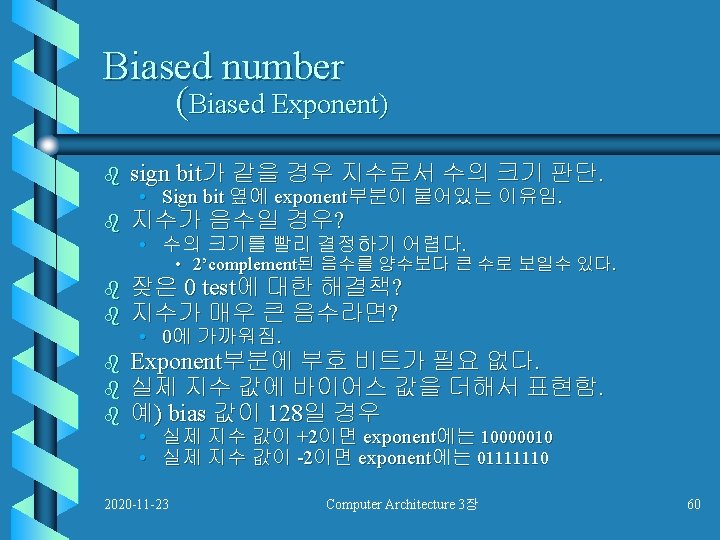

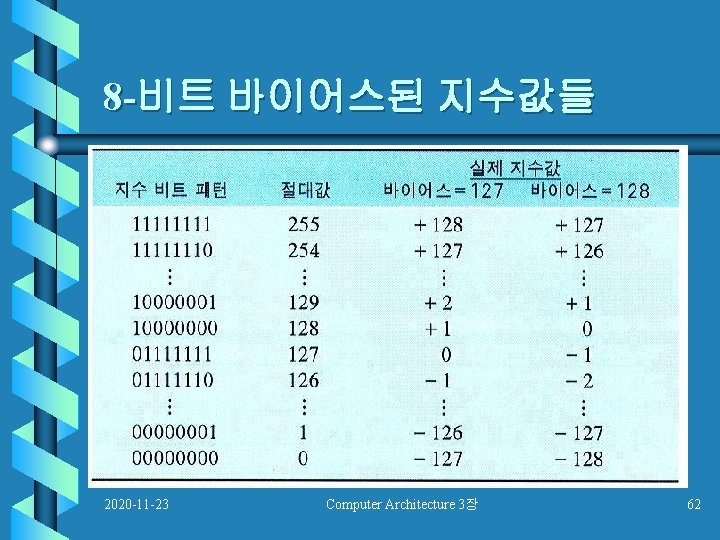

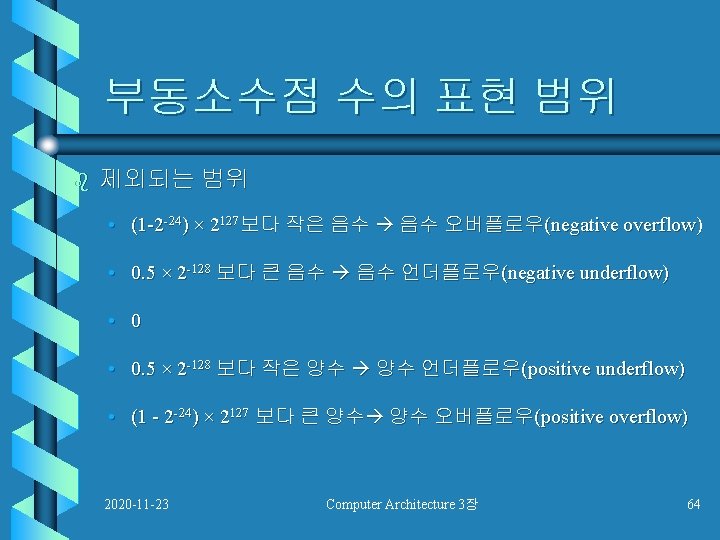

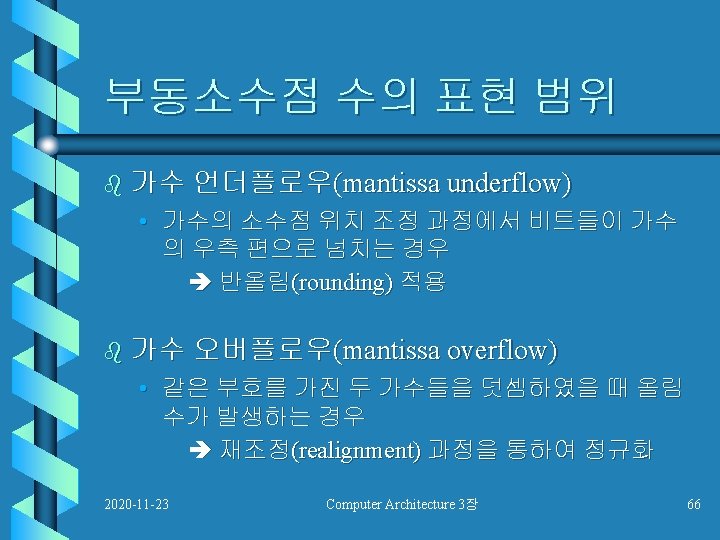

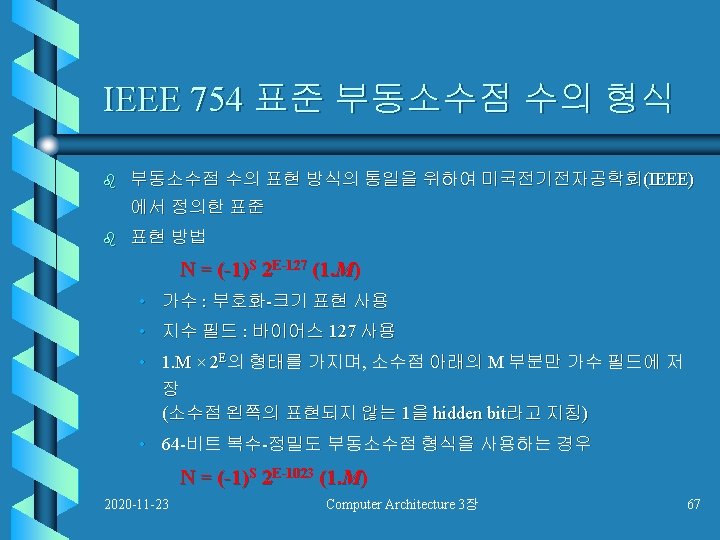

예) N= -13. 625에 대한 부동소수점 표현 (실제 메모리/레지스터에 표현되는 형태) b -13. 62510 = - 1101. 101 = - 0. 1101101 24 b 음수 이므로 부호 비트(S)는 1 b 지수(E : 바이어스 128) • 00000100 + 10000000 = 10000100 b 가수(M) • 1101101 (여기서 첫번째 1은 생략 가능) 31 30 15 0000000100 Exponent 1 14 0 110110100000 Mantissa Sign bit (+ : 0 - : 1) 2020 -11 -23 Computer Architecture 3장 61

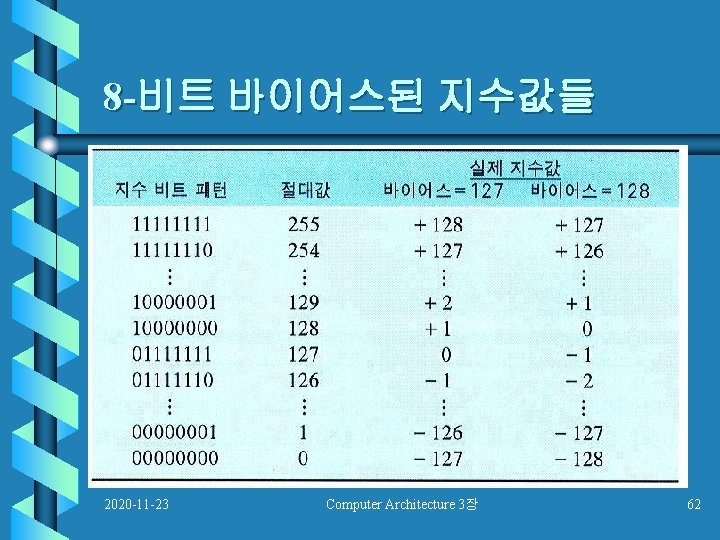

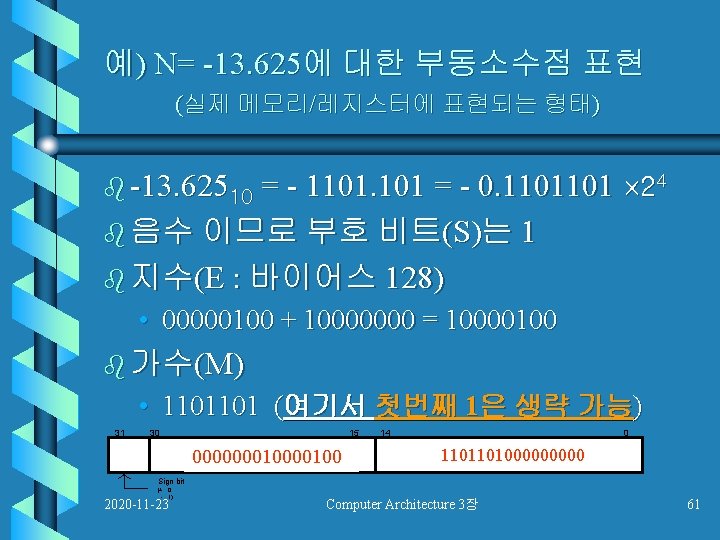

8 -비트 바이어스된 지수값들 2020 -11 -23 Computer Architecture 3장 62

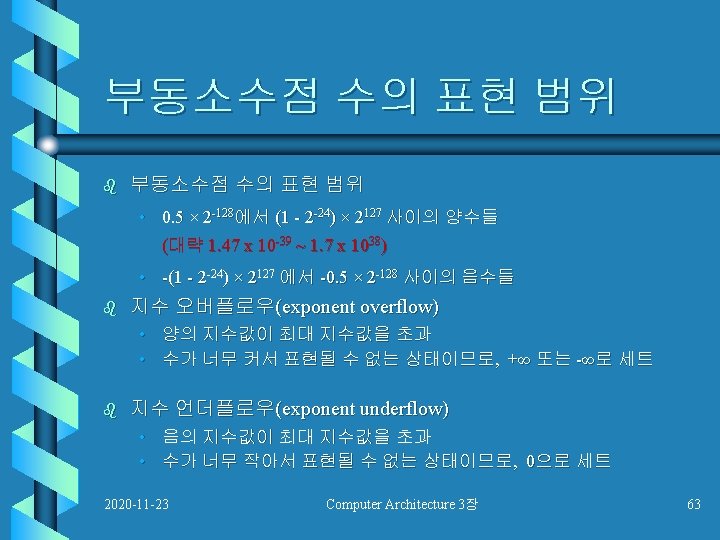

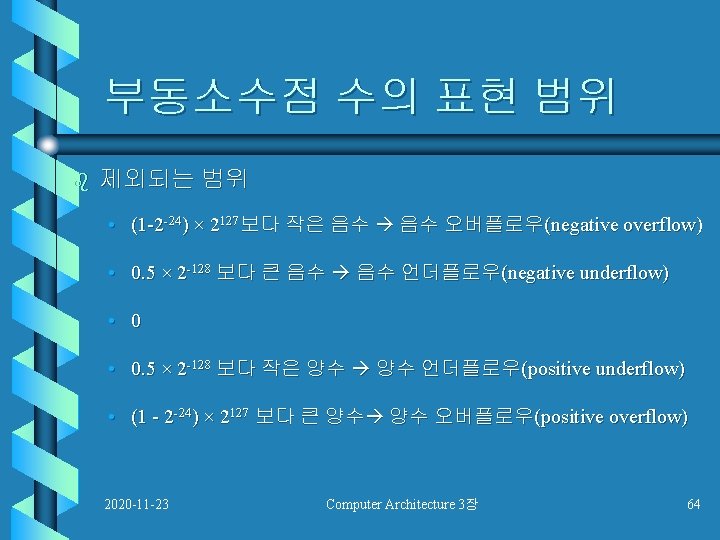

32 -비트 데이터 형식의 표현 가능한 수의 범위 2020 -11 -23 Computer Architecture 3장 65

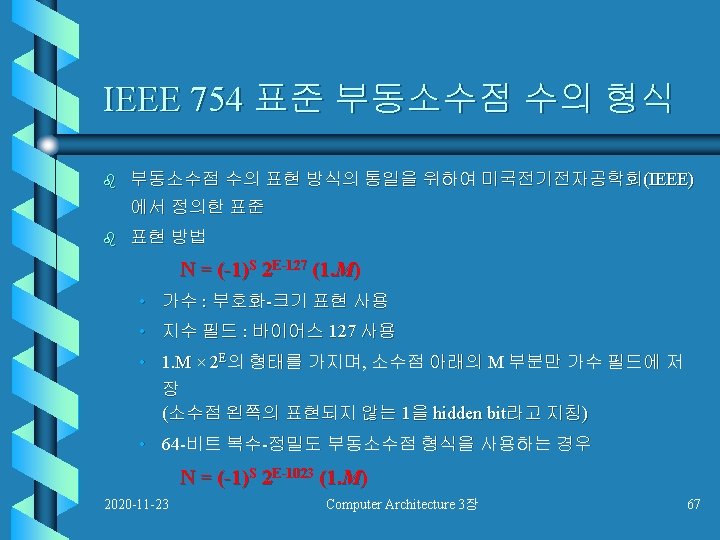

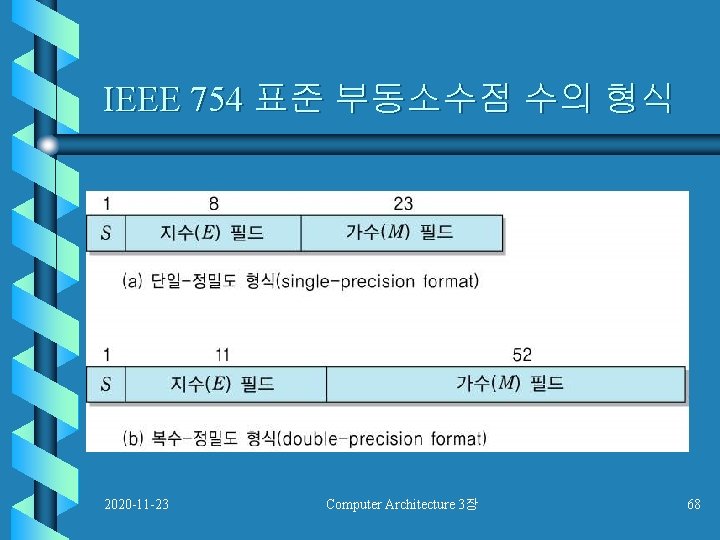

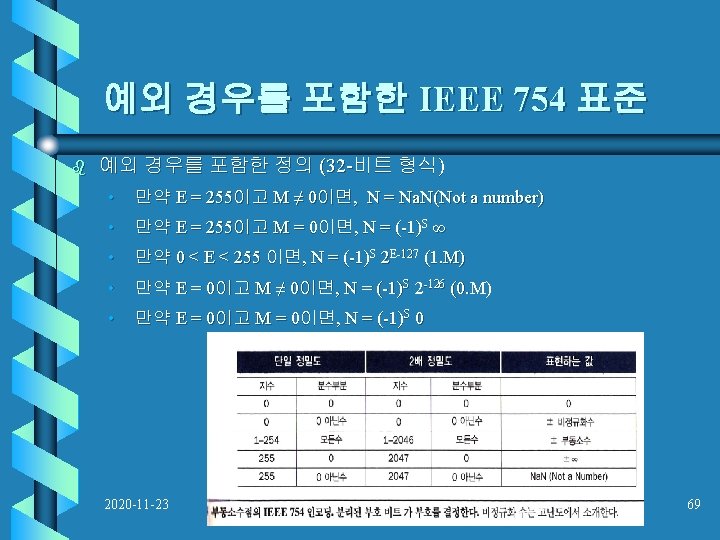

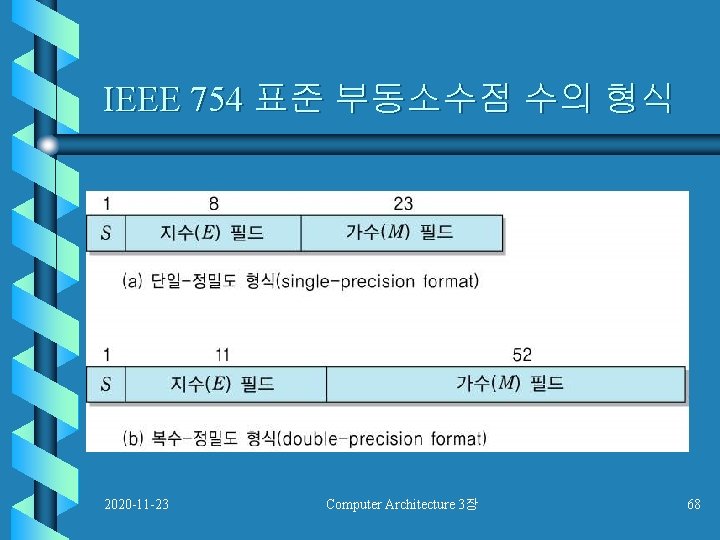

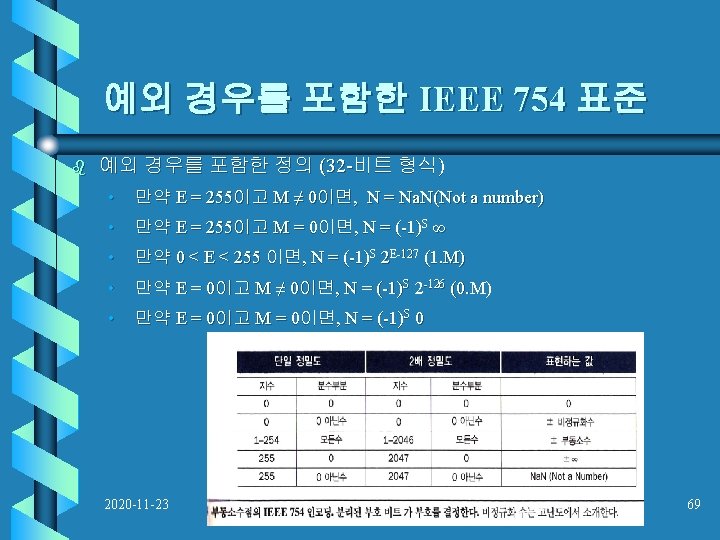

IEEE 754 표준 부동소수점 수의 형식 2020 -11 -23 Computer Architecture 3장 68

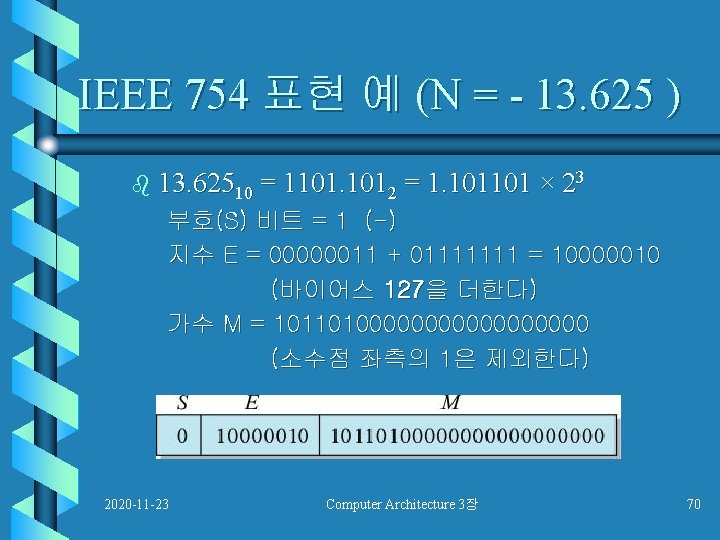

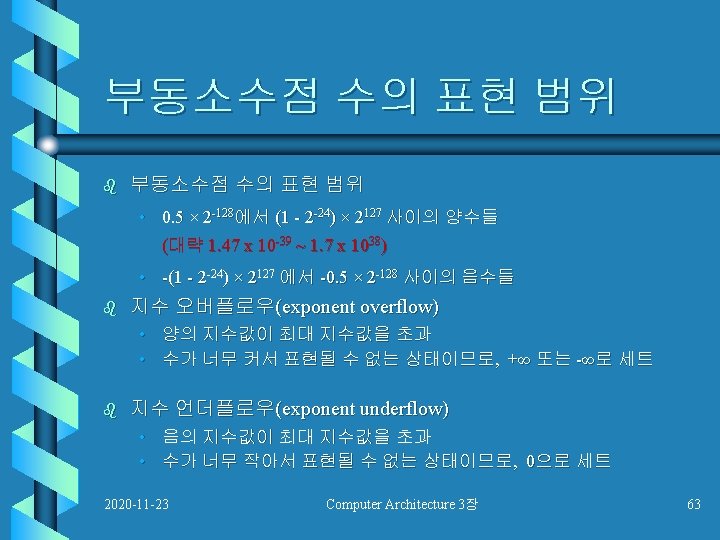

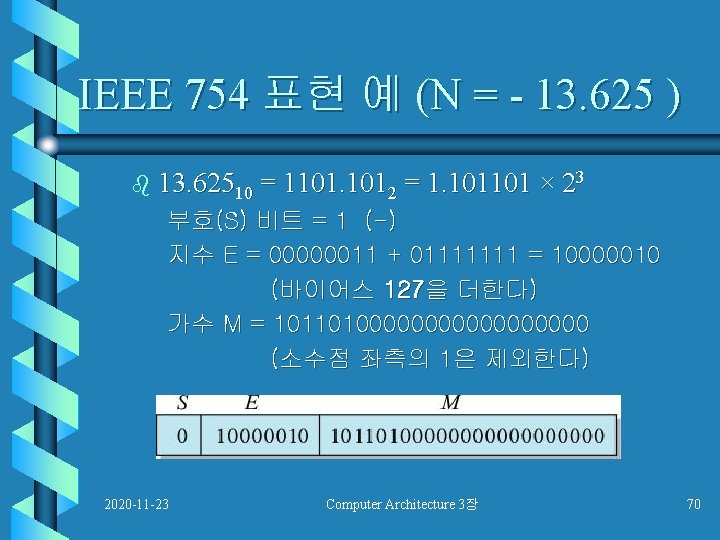

IEEE 754 표현 예 (N = - 13. 625 ) b 13. 62510 = 1101. 1012 = 1. 101101 × 23 부호(S) 비트 = 1 (-) 지수 E = 00000011 + 01111111 = 10000010 (바이어스 127을 더한다) 가수 M = 101101000000000 (소수점 좌측의 1은 제외한다) 2020 -11 -23 Computer Architecture 3장 70

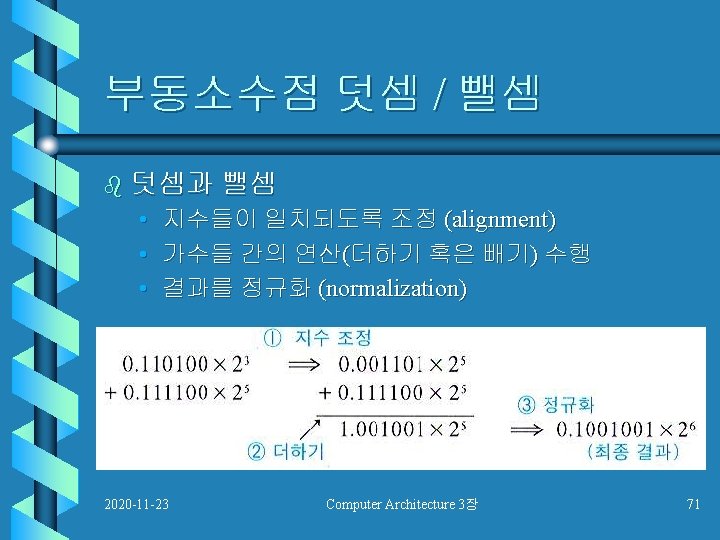

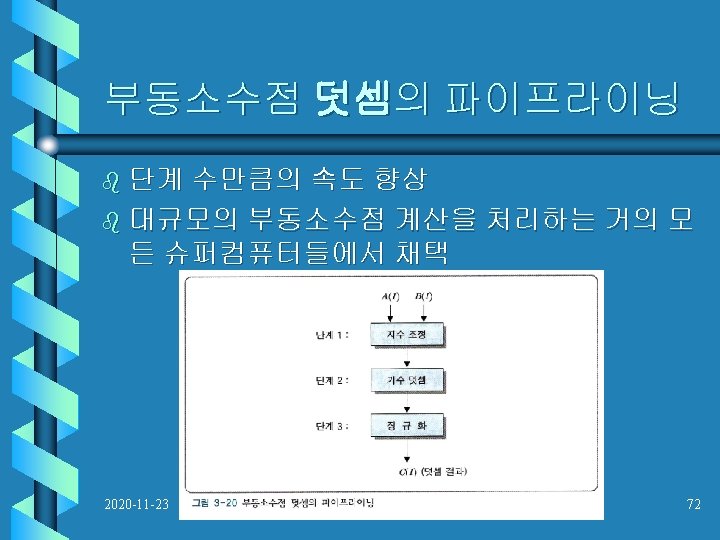

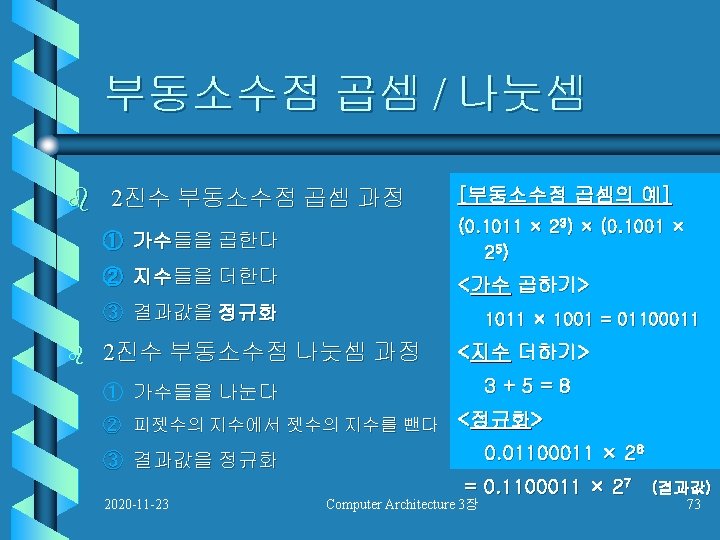

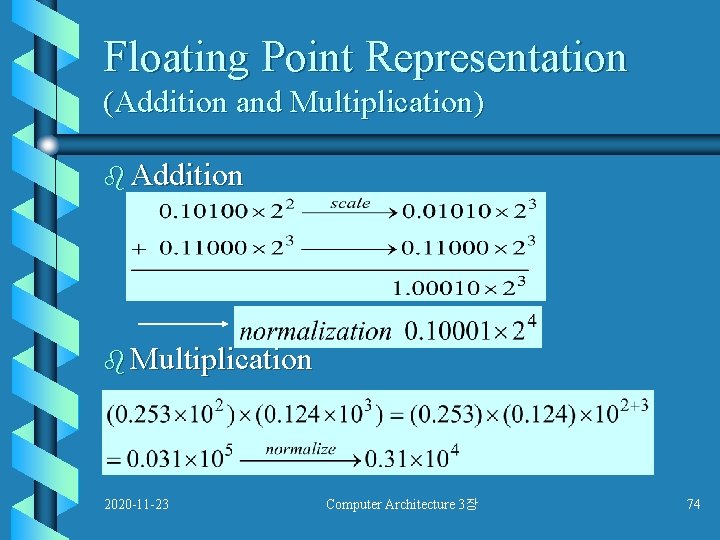

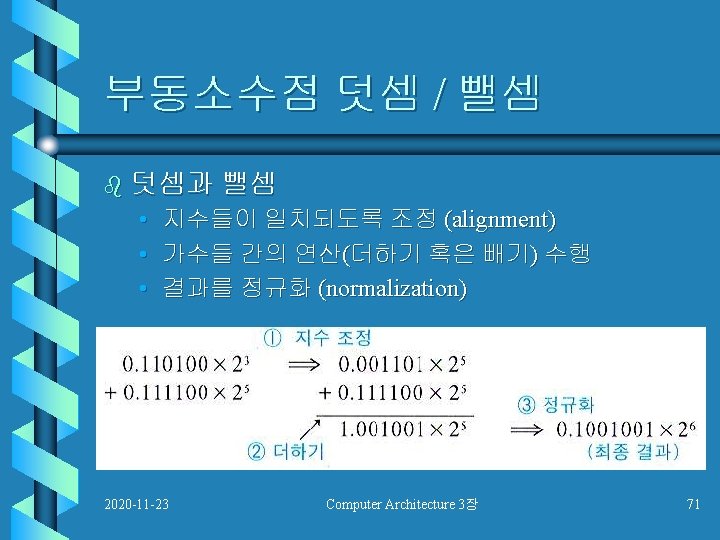

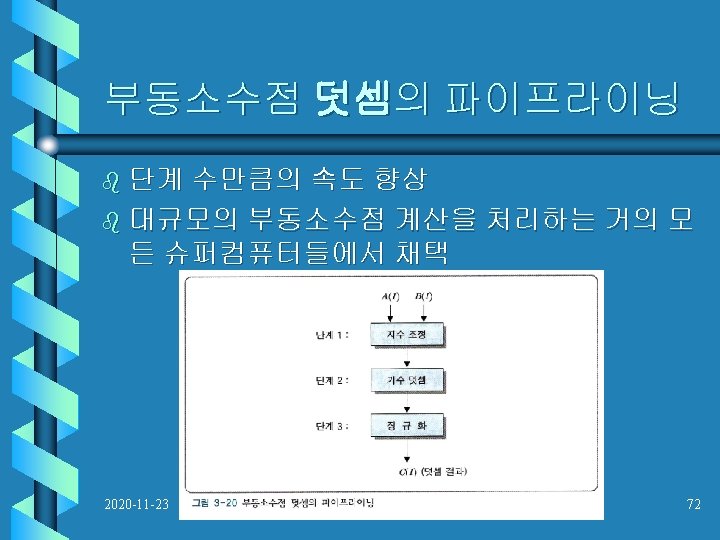

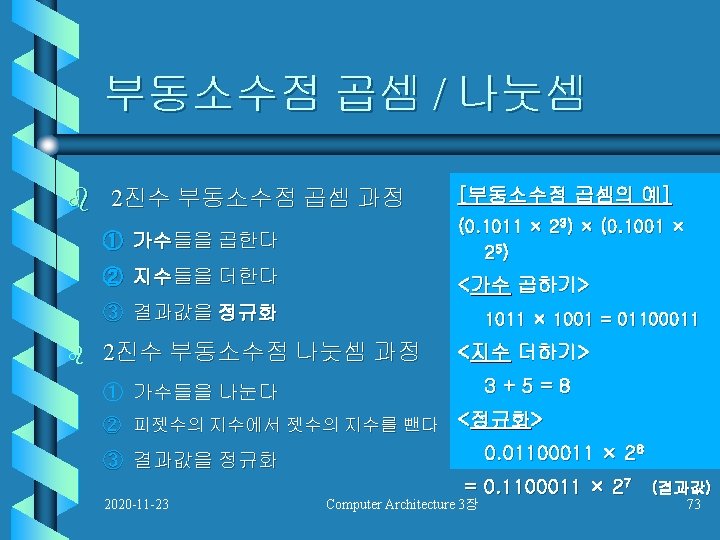

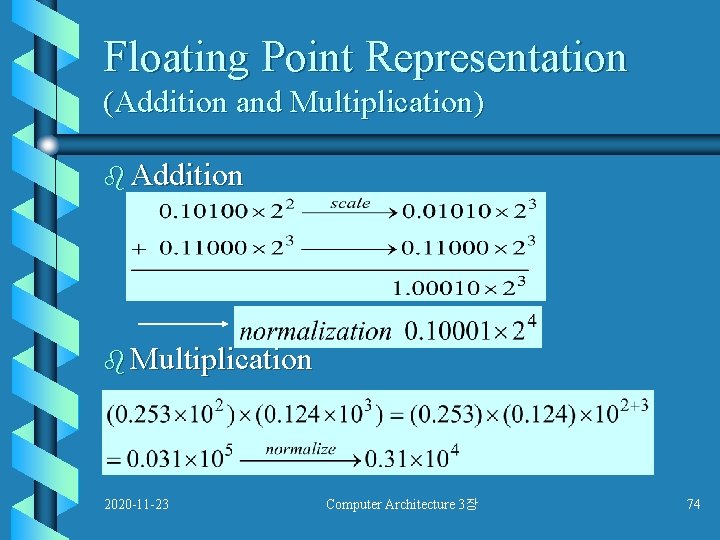

Floating Point Representation (Addition and Multiplication) b Addition b Multiplication 2020 -11 -23 Computer Architecture 3장 74