2012 Free Space Optical Communication Integrated Circuit IC

- Slides: 1

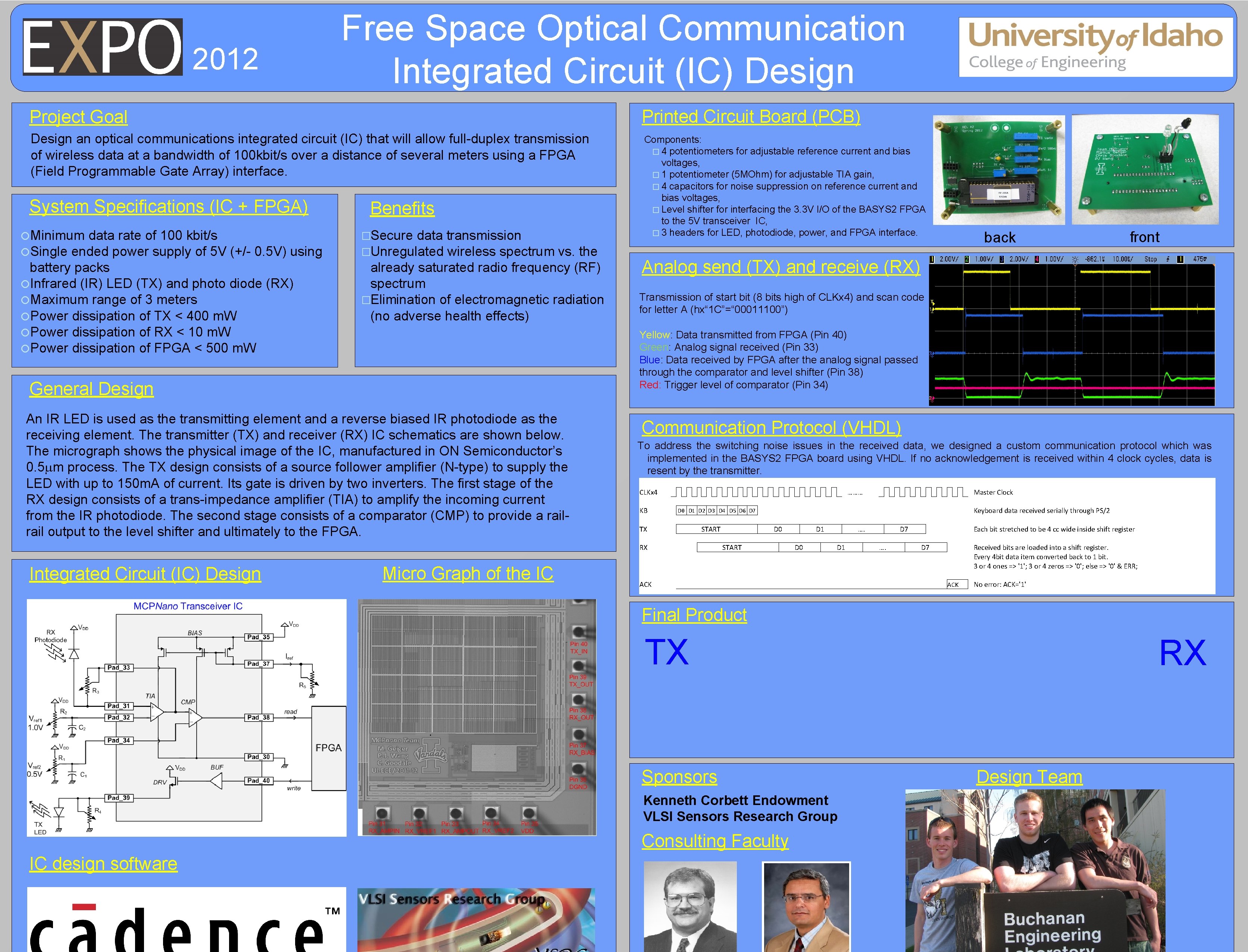

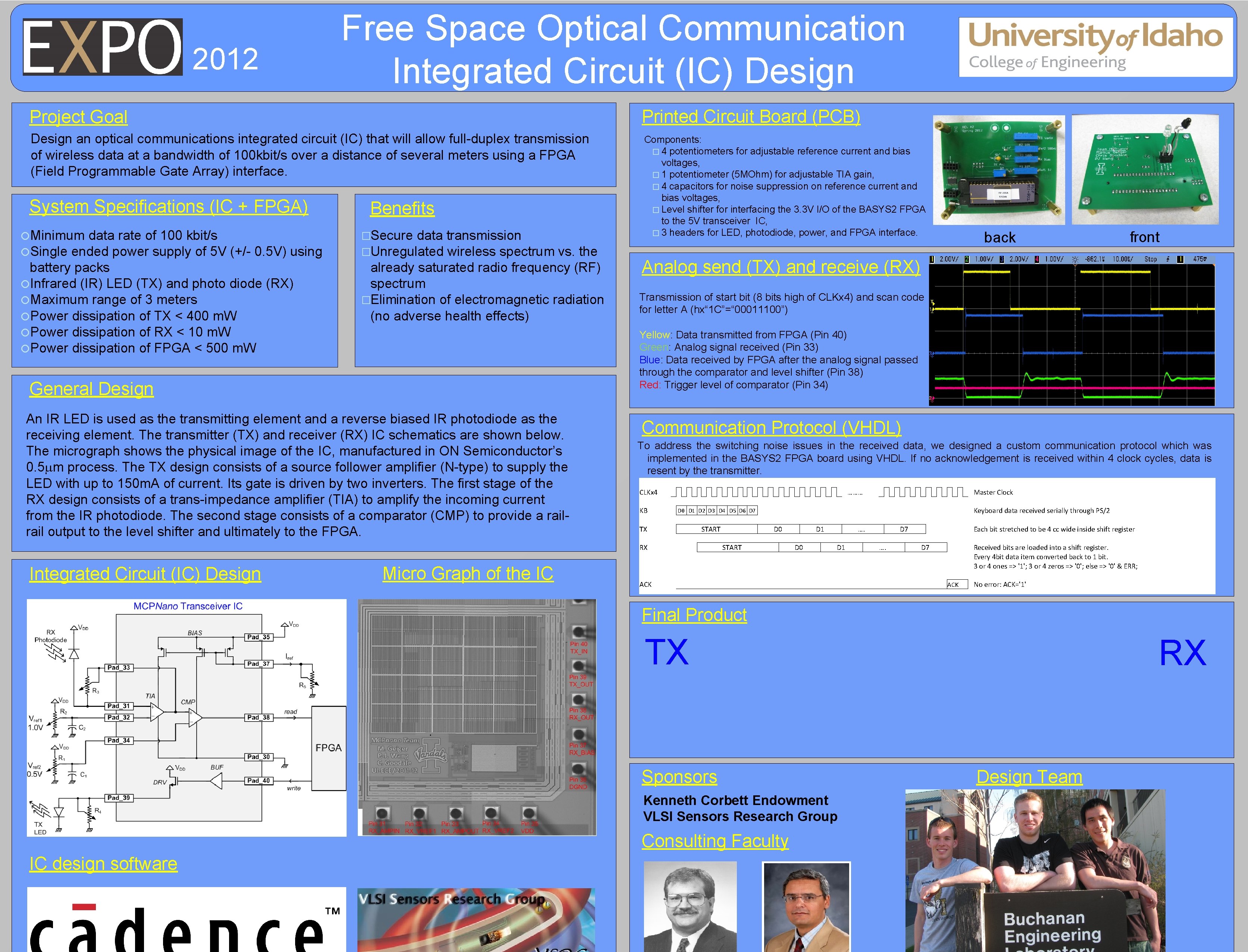

2012 Free Space Optical Communication Integrated Circuit (IC) Design Project Goal Printed Circuit Board (PCB) Design an optical communications integrated circuit (IC) that will allow full-duplex transmission of wireless data at a bandwidth of 100 kbit/s over a distance of several meters using a FPGA (Field Programmable Gate Array) interface. Components: � 4 potentiometers for adjustable reference current and bias voltages, � 1 potentiometer (5 MOhm) for adjustable TIA gain, � 4 capacitors for noise suppression on reference current and bias voltages, � Level shifter for interfacing the 3. 3 V I/O of the BASYS 2 FPGA to the 5 V transceiver IC, � 3 headers for LED, photodiode, power, and FPGA interface. System Specifications (IC + FPGA) Minimum data rate of 100 kbit/s Single ended power supply of 5 V (+/- 0. 5 V) using battery packs Infrared (IR) LED (TX) and photo diode (RX) Maximum range of 3 meters Power dissipation of TX < 400 m. W Power dissipation of RX < 10 m. W Power dissipation of FPGA < 500 m. W Benefits �Secure data transmission �Unregulated wireless spectrum vs. the already saturated radio frequency (RF) spectrum �Elimination of electromagnetic radiation (no adverse health effects) front Analog send (TX) and receive (RX) Transmission of start bit (8 bits high of CLKx 4) and scan code for letter A (hx“ 1 C”=“ 00011100”) Yellow: Data transmitted from FPGA (Pin 40) Green: Analog signal received (Pin 33) Blue: Data received by FPGA after the analog signal passed through the comparator and level shifter (Pin 38) Red: Trigger level of comparator (Pin 34) General Design An IR LED is used as the transmitting element and a reverse biased IR photodiode as the receiving element. The transmitter (TX) and receiver (RX) IC schematics are shown below. The micrograph shows the physical image of the IC, manufactured in ON Semiconductor’s 0. 5 mm process. The TX design consists of a source follower amplifier (N-type) to supply the LED with up to 150 m. A of current. Its gate is driven by two inverters. The first stage of the RX design consists of a trans-impedance amplifier (TIA) to amplify the incoming current from the IR photodiode. The second stage consists of a comparator (CMP) to provide a rail output to the level shifter and ultimately to the FPGA. Communication Protocol (VHDL) To address the switching noise issues in the received data, we designed a custom communication protocol which was implemented in the BASYS 2 FPGA board using VHDL. If no acknowledgement is received within 4 clock cycles, data is resent by the transmitter. CLKx 4 KB ……… Micro Graph of the IC Master Clock Keyboard data received serially through PS/2 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 TX START RX Integrated Circuit (IC) Design back D 0 START D 1 D 0 …. D 1 ACK D 7 …. Each bit stretched to be 4 cc wide inside shift register D 7 Received bits are loaded into a shift register. Every 4 bit data item converted back to 1 bit. 3 or 4 ones => '1'; 3 or 4 zeros => '0'; else => '0' & ERR; ACK No error: ACK='1' Final Product TX Sponsors Kenneth Corbett Endowment VLSI Sensors Research Group Consulting Faculty IC design software RX Design Team