2004 IEEE Compound Semiconductor IC Symposium October Monterey

2004 IEEE Compound Semiconductor IC Symposium, October, Monterey Transistor and Circuit Design for 100 -200 GHz ICs Mark Rodwell University of California, Santa Barbara V. Paidi, Z. Griffith, D. Scott, Y. Dong, M. Dahlström, Y. Wei, N. Parthasarathy University of California, Santa Barbara Lorene Samoska, Andy Fung Jet Propulsion Laboratories M. Urteaga, R. Pierson , P. Rowell, B. Brar Rockwell Scientific Company S. Lee, N. Nguyen, and C. Nguyen Global Communication Semiconductors rodwell@ece. ucsb. edu 805 -893 -3244, 805 -893 -5705 fax

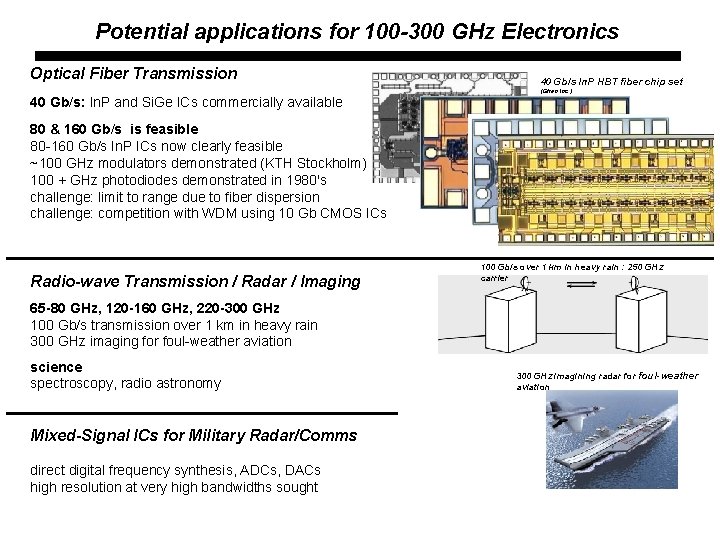

Potential applications for 100 -300 GHz Electronics Optical Fiber Transmission 40 Gb/s: In. P and Si. Ge ICs commercially available 40 Gb/s In. P HBT fiber chip set (Gtran Inc. ) 80 & 160 Gb/s is feasible 80 -160 Gb/s In. P ICs now clearly feasible ~100 GHz modulators demonstrated (KTH Stockholm) 100 + GHz photodiodes demonstrated in 1980's challenge: limit to range due to fiber dispersion challenge: competition with WDM using 10 Gb CMOS ICs Radio-wave Transmission / Radar / Imaging 100 Gb/s over 1 km in heavy rain : 250 GHz carrier 65 -80 GHz, 120 -160 GHz, 220 -300 GHz 100 Gb/s transmission over 1 km in heavy rain 300 GHz imaging for foul-weather aviation science spectroscopy, radio astronomy Mixed-Signal ICs for Military Radar/Comms direct digital frequency synthesis, ADCs, DACs high resolution at very high bandwidths sought 300 GHz imagining radar foul-weather aviation

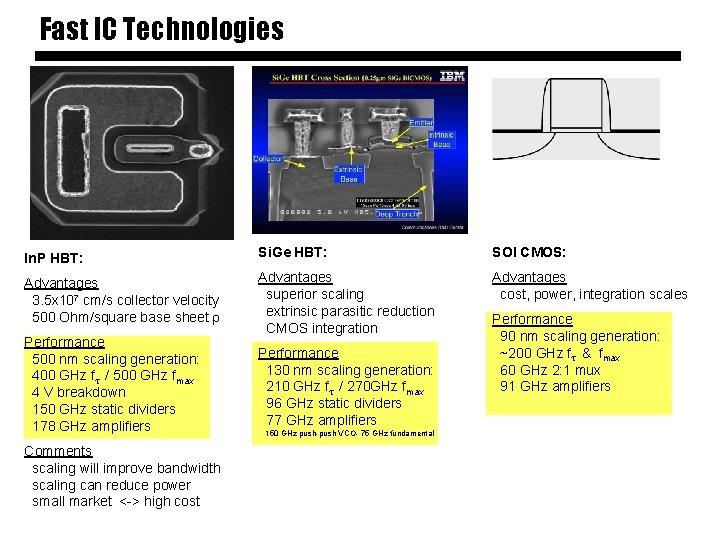

Fast IC Technologies In. P HBT: Si. Ge HBT: SOI CMOS: Advantages 3. 5 x 107 cm/s collector velocity 500 Ohm/square base sheet r Advantages superior scaling extrinsic parasitic reduction CMOS integration Advantages cost, power, integration scales Performance 500 nm scaling generation: 400 GHz ft / 500 GHz fmax 4 V breakdown 150 GHz static dividers 178 GHz amplifiers Comments scaling will improve bandwidth scaling can reduce power small market <-> high cost Performance 130 nm scaling generation: 210 GHz ft / 270 GHz fmax 96 GHz static dividers 77 GHz amplifiers 150 GHz push-push VCO- 75 GHz fundamental Performance 90 nm scaling generation: ~200 GHz ft & fmax 60 GHz 2: 1 mux 91 GHz amplifiers

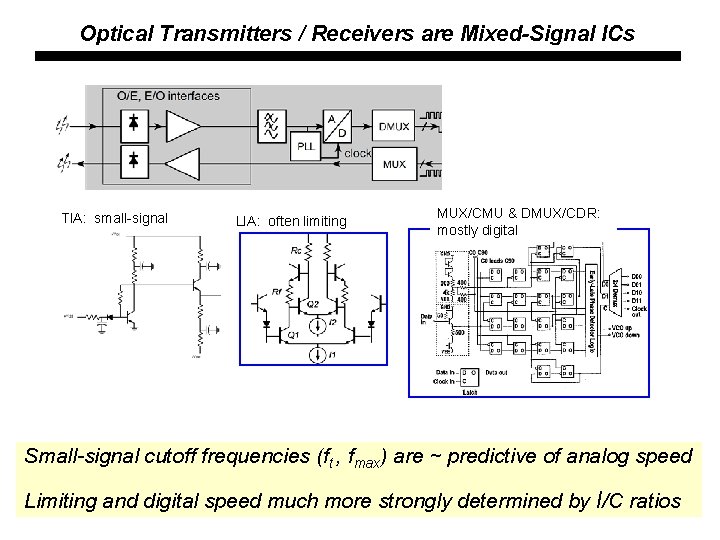

Optical Transmitters / Receivers are Mixed-Signal ICs TIA: small-signal LIA: often limiting MUX/CMU & DMUX/CDR: mostly digital Small-signal cutoff frequencies (ft , fmax) are ~ predictive of analog speed Limiting and digital speed much more strongly determined by I/C ratios

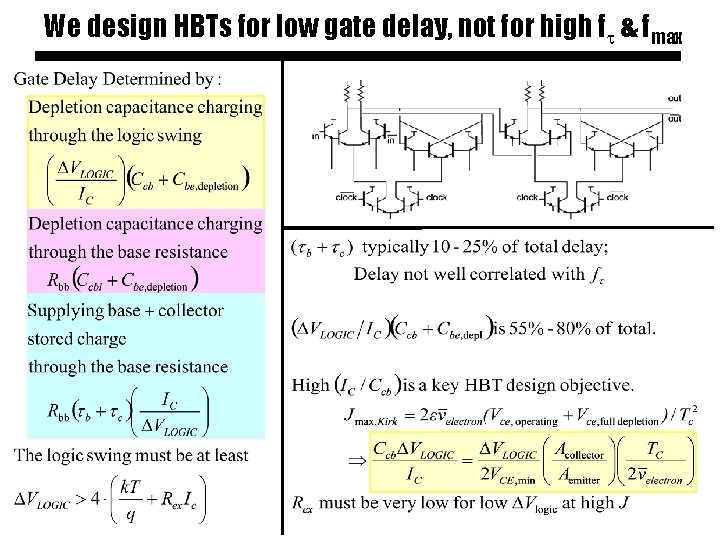

We design HBTs for low gate delay, not for high ft & fmax

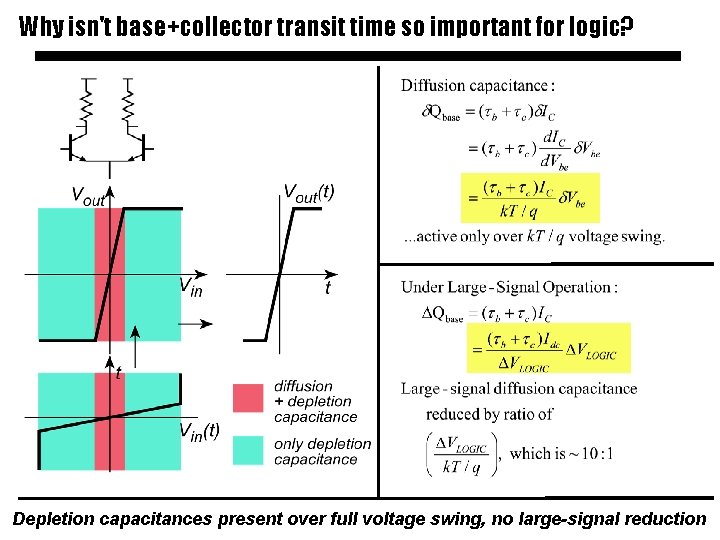

Why isn't base+collector transit time so important for logic? Depletion capacitances present over full voltage swing, no large-signal reduction

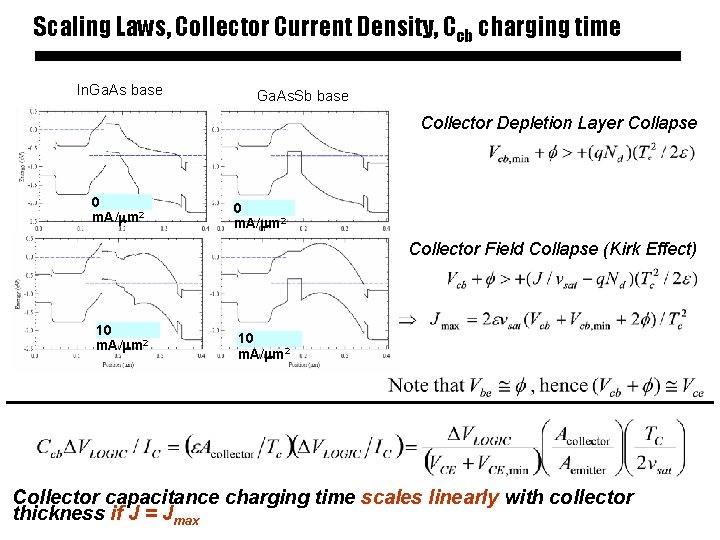

Scaling Laws, Collector Current Density, Ccb charging time In. Ga. As base Ga. As. Sb base Collector Depletion Layer Collapse 0 m. A/mm 2 Collector Field Collapse (Kirk Effect) 10 m. A/mm 2 Collector capacitance charging time scales linearly with collector thickness if J = Jmax

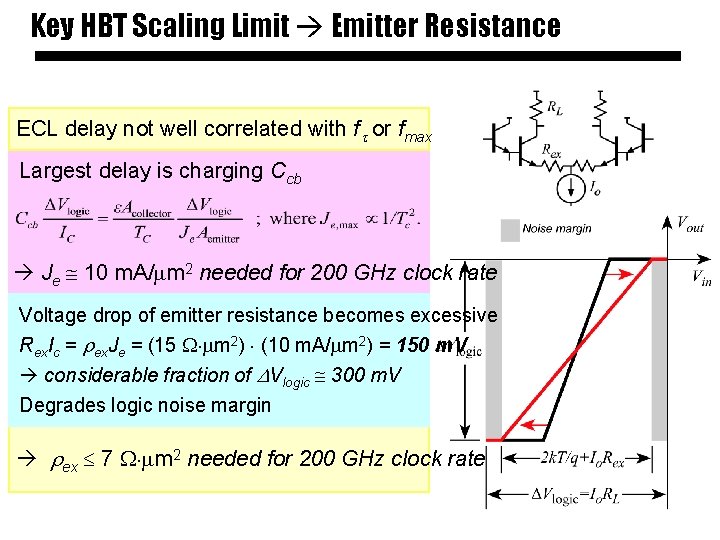

Key HBT Scaling Limit Emitter Resistance ECL delay not well correlated with f or fmax Largest delay is charging Ccb Je 10 m. A/ m 2 needed for 200 GHz clock rate Voltage drop of emitter resistance becomes excessive Rex. Ic = ex. Je = (15 m 2) (10 m. A/ m 2) = 150 m. V considerable fraction of Vlogic 300 m. V Degrades logic noise margin ex 7 m 2 needed for 200 GHz clock rate

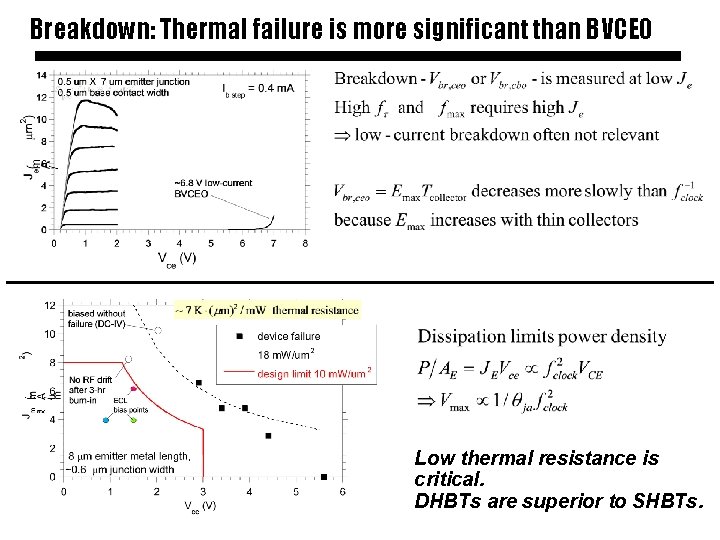

Breakdown: Thermal failure is more significant than BVCEO Low thermal resistance is critical. DHBTs are superior to SHBTs.

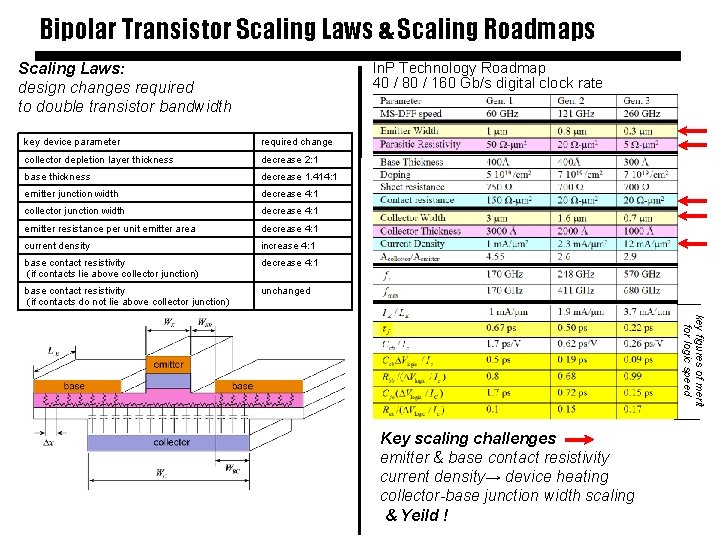

Bipolar Transistor Scaling Laws & Scaling Roadmaps Scaling Laws: design changes required to double transistor bandwidth In. P Technology Roadmap 40 / 80 / 160 Gb/s digital clock rate key device parameter required change collector depletion layer thickness decrease 2: 1 base thickness decrease 1. 414: 1 emitter junction width decrease 4: 1 collector junction width decrease 4: 1 emitter resistance per unit emitter area decrease 4: 1 current density increase 4: 1 base contact resistivity (if contacts lie above collector junction) decrease 4: 1 base contact resistivity (if contacts do not lie above collector junction) unchanged key figures of merit for logic speed Key scaling challenges emitter & base contact resistivity current density→ device heating collector-base junction width scaling & Yeild !

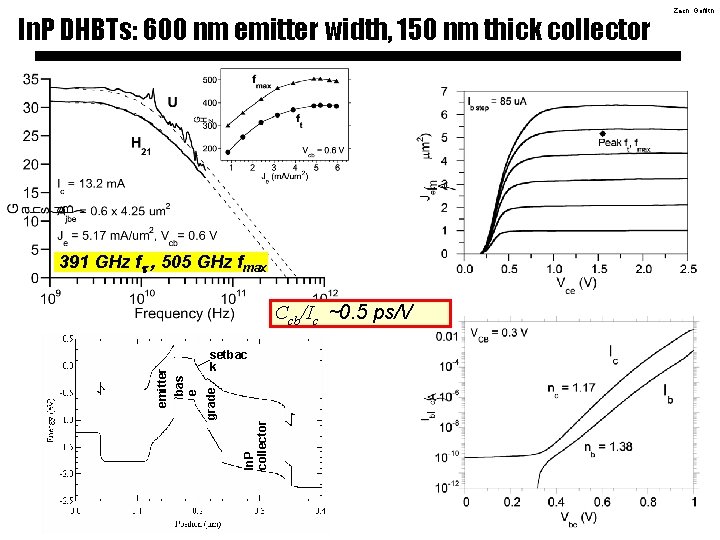

In. P DHBTs: 600 nm emitter width, 150 nm thick collector 391 GHz f , 505 GHz fmax In. P collector setbac k grade emitter bas e Ccb/Ic ~0. 5 ps/V Zach Griffith

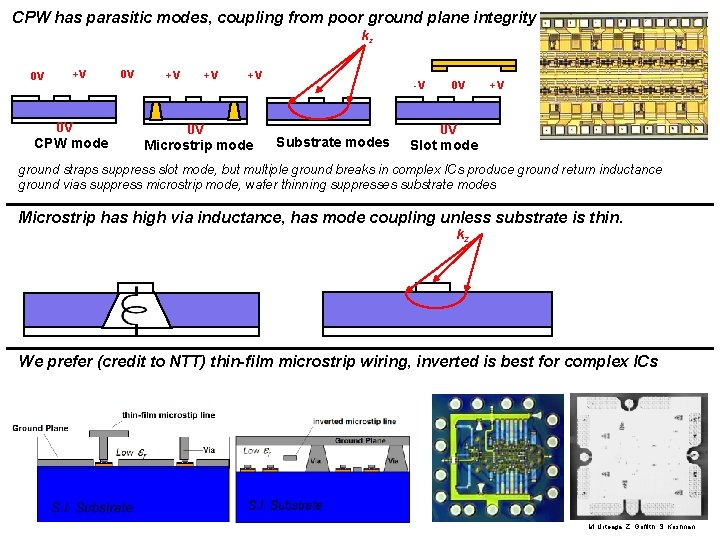

CPW has parasitic modes, coupling from poor ground plane integrity kz +V 0 V 0 V CPW mode 0 V +V +V +V 0 V Microstrip mode -V Substrate modes 0 V +V 0 V Slot mode ground straps suppress slot mode, but multiple ground breaks in complex ICs produce ground return inductance ground vias suppress microstrip mode, wafer thinning suppresses substrate modes Microstrip has high via inductance, has mode coupling unless substrate is thin. kz We prefer (credit to NTT) thin-film microstrip wiring, inverted is best for complex ICs M. Urteaga, Z. Griffith, S. Krishnan

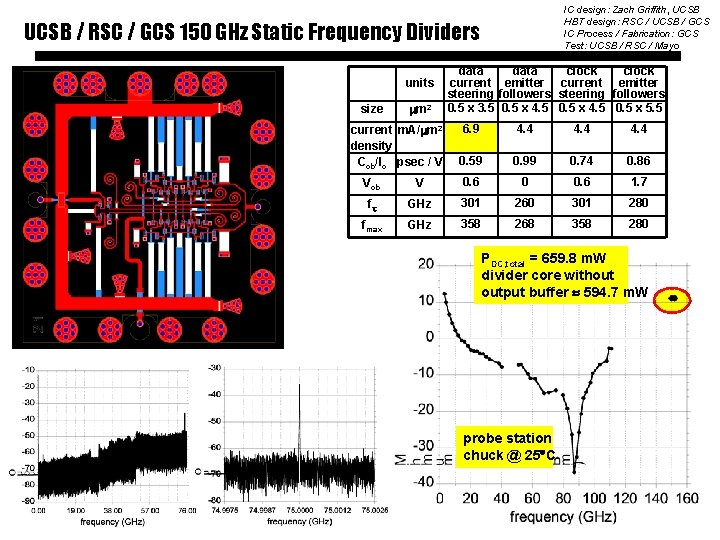

IC design: Zach Griffith, UCSB HBT design: RSC / UCSB / GCS IC Process / Fabrication: GCS Test: UCSB / RSC / Mayo UCSB / RSC / GCS 150 GHz Static Frequency Dividers units size mm 2 current m. A/mm 2 density Ccb/Ic psec / V data clock current emitter steering followers 0. 5 x 3. 5 0. 5 x 4. 5 0. 5 x 5. 5 6. 9 4. 4 0. 59 0. 99 0. 74 0. 86 Vcb V 0. 6 0 0. 6 1. 7 ft GHz 301 260 301 280 fmax GHz 358 268 358 280 PDC, total = 659. 8 m. W divider core without output buffer 594. 7 m. W probe station chuck @ 25 C

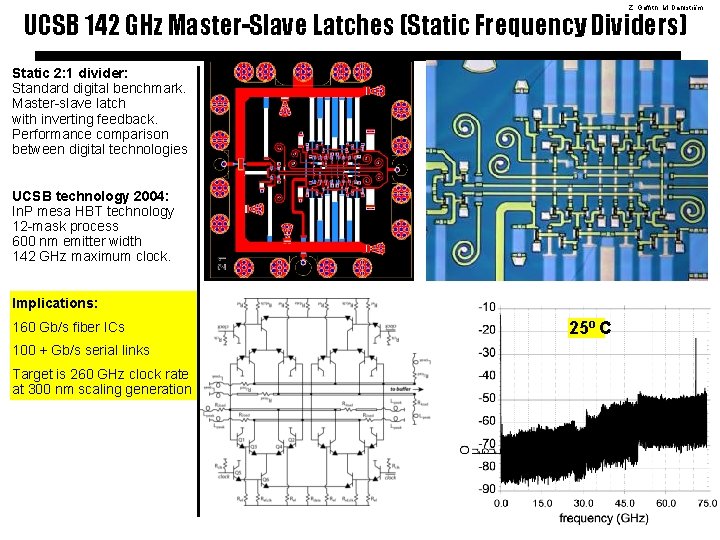

Z. Griffith, M. Dahlström UCSB 142 GHz Master-Slave Latches (Static Frequency Dividers) Static 2: 1 divider: Standard digital benchmark. Master-slave latch with inverting feedback. Performance comparison between digital technologies UCSB technology 2004: In. P mesa HBT technology 12 -mask process 600 nm emitter width 142 GHz maximum clock. Implications: 160 Gb/s fiber ICs 100 + Gb/s serial links Target is 260 GHz clock rate at 300 nm scaling generation 25 o C

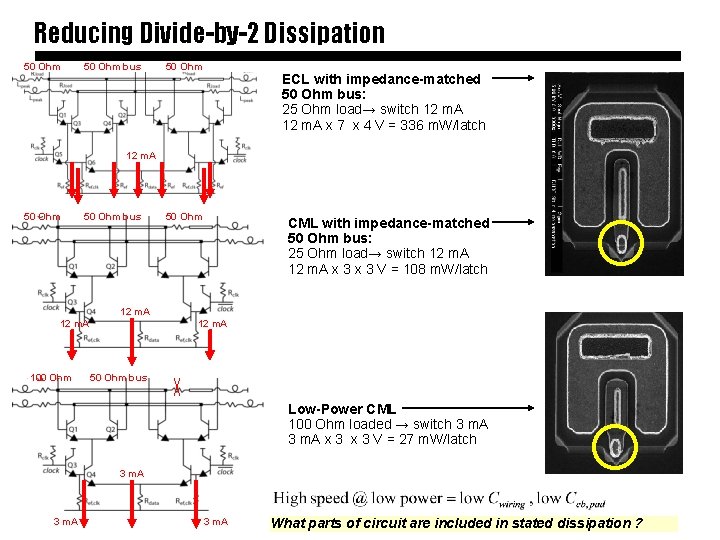

Reducing Divide-by-2 Dissipation 50 Ohm bus 50 Ohm ECL with impedance-matched 50 Ohm bus: 25 Ohm load→ switch 12 m. A x 7 x 4 V = 336 m. W/latch 12 m. A 50 Ohm bus 50 Ohm CML with impedance-matched 50 Ohm bus: 25 Ohm load→ switch 12 m. A x 3 V = 108 m. W/latch 12 m. A 100 Ohm 12 m. A 50 Ohm bus Low-Power CML 100 Ohm loaded → switch 3 m. A x 3 V = 27 m. W/latch 3 m. A What parts of circuit are included in stated dissipation ?

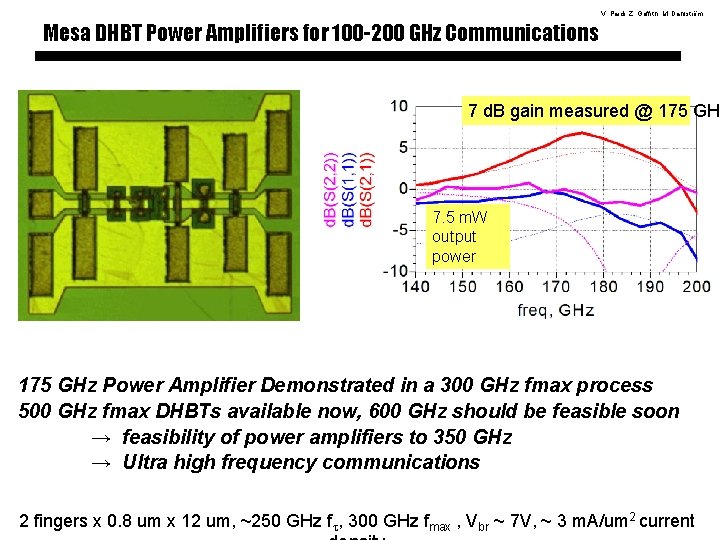

V. Paidi, Z. Griffith, M. Dahlström Mesa DHBT Power Amplifiers for 100 -200 GHz Communications 7 d. B gain measured @ 175 GHz 7. 5 m. W output power 175 GHz Power Amplifier Demonstrated in a 300 GHz fmax process 500 GHz fmax DHBTs available now, 600 GHz should be feasible soon → feasibility of power amplifiers to 350 GHz → Ultra high frequency communications 2 fingers x 0. 8 um x 12 um, ~250 GHz ft, 300 GHz fmax , Vbr ~ 7 V, ~ 3 m. A/um 2 current

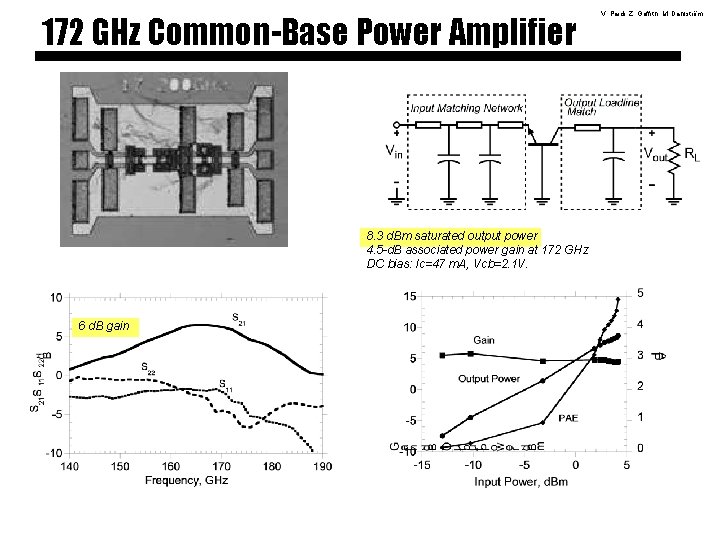

172 GHz Common-Base Power Amplifier 8. 3 d. Bm saturated output power 4. 5 -d. B associated power gain at 172 GHz DC bias: Ic=47 m. A, Vcb=2. 1 V. 6 d. B gain V. Paidi, Z. Griffith, M. Dahlström

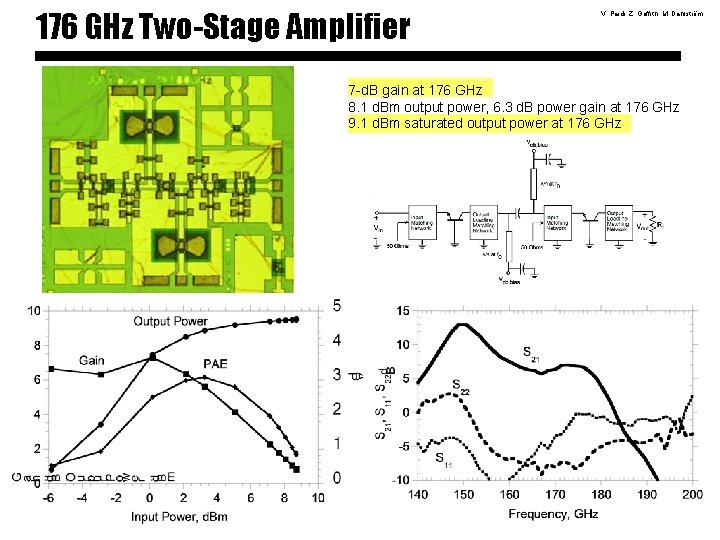

176 GHz Two-Stage Amplifier V. Paidi, Z. Griffith, M. Dahlström 7 -d. B gain at 176 GHz 8. 1 d. Bm output power, 6. 3 d. B power gain at 176 GHz 9. 1 d. Bm saturated output power at 176 GHz

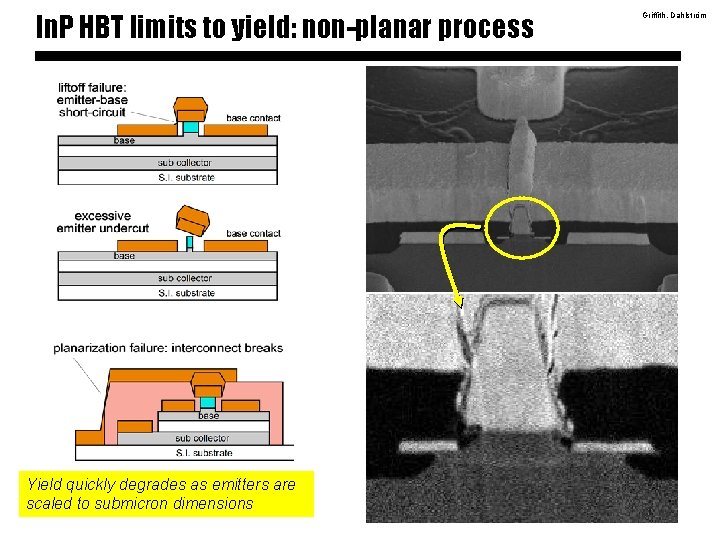

In. P HBT limits to yield: non-planar process Yield quickly degrades as emitters are scaled to submicron dimensions Griffith, Dahlström

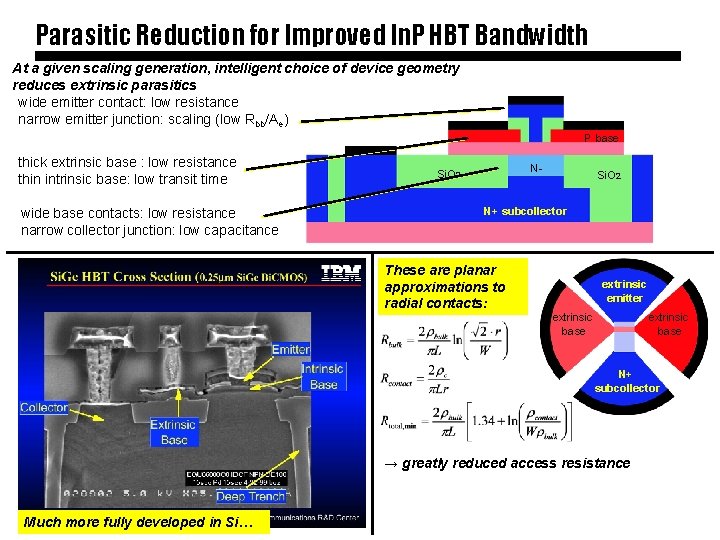

Parasitic Reduction for Improved In. P HBT Bandwidth At a given scaling generation, intelligent choice of device geometry reduces extrinsic parasitics wide emitter contact: low resistance narrow emitter junction: scaling (low Rbb/Ae) P base thick extrinsic base : low resistance thin intrinsic base: low transit time wide base contacts: low resistance narrow collector junction: low capacitance N- Si. O 2 N+ subcollector These are planar approximations to radial contacts: extrinsic emitter extrinsic base N+ subcollector → greatly reduced access resistance Much more fully developed in Si…

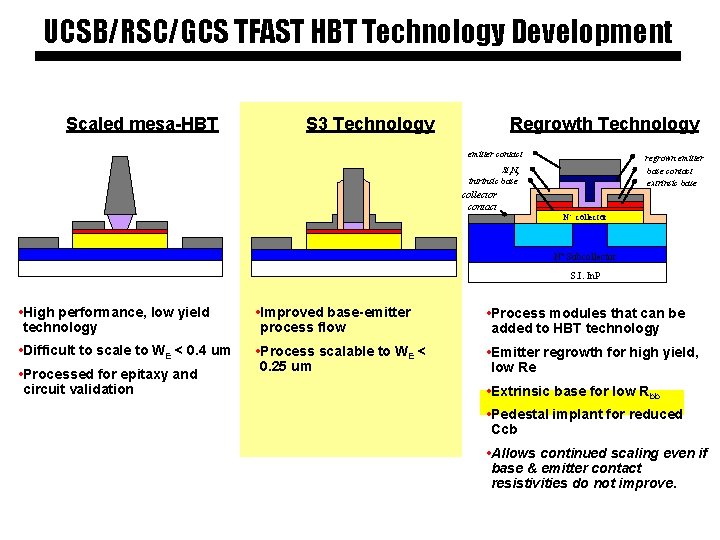

UCSB/RSC/GCS TFAST HBT Technology Development Scaled mesa-HBT S 3 Technology Regrowth Technology emitter contact regrown emitter base contact extrinsic base Six. Ny intrinsic base collector contact N- collector N+ Subcollector S. I. In. P • High performance, low yield technology • Improved base-emitter process flow • Process modules that can be added to HBT technology • Difficult to scale to WE < 0. 4 um • Process scalable to WE < 0. 25 um • Emitter regrowth for high yield, low Re • Processed for epitaxy and circuit validation • Extrinsic base for low Rbb • Pedestal implant for reduced Ccb • Allows continued scaling even if base & emitter contact resistivities do not improve.

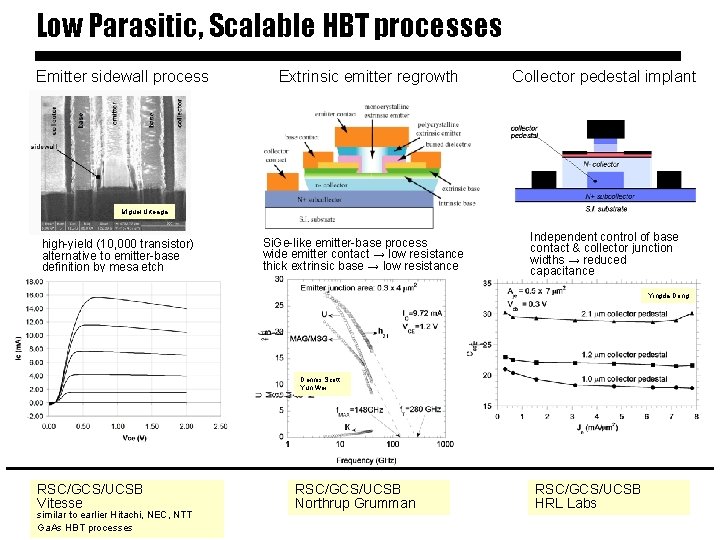

Low Parasitic, Scalable HBT processes Emitter sidewall process Extrinsic emitter regrowth Collector pedestal implant Miguel Urteaga high-yield (10, 000 transistor) alternative to emitter-base definition by mesa etch Si. Ge-like emitter-base process wide emitter contact → low resistance thick extrinsic base → low resistance Independent control of base contact & collector junction widths → reduced capacitance Yingda Dong Dennis Scott, Yun Wei RSC/GCS/UCSB Vitesse similar to earlier Hitachi, NEC, NTT Ga. As HBT processes RSC/GCS/UCSB Northrup Grumman RSC/GCS/UCSB HRL Labs

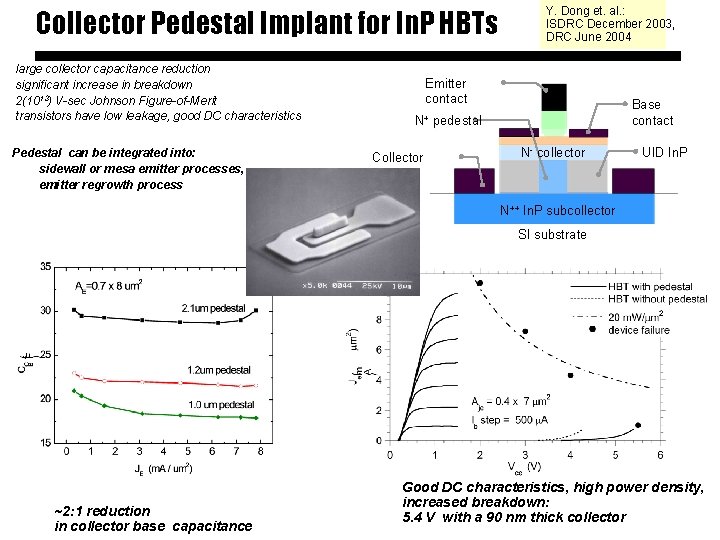

Collector Pedestal Implant for In. P HBTs large collector capacitance reduction significant increase in breakdown 2(1013) V-sec Johnson Figure-of-Merit transistors have low leakage, good DC characteristics Pedestal can be integrated into: sidewall or mesa emitter processes, emitter regrowth process Y. Dong et. al. : ISDRC December 2003, DRC June 2004 Emitter contact N+ Collector contact Base contact pedestal N- collector UID In. P N++ In. P subcollector SI substrate ~2: 1 reduction in collector base capacitance Good DC characteristics, high power density, increased breakdown: 5. 4 V with a 90 nm thick collector

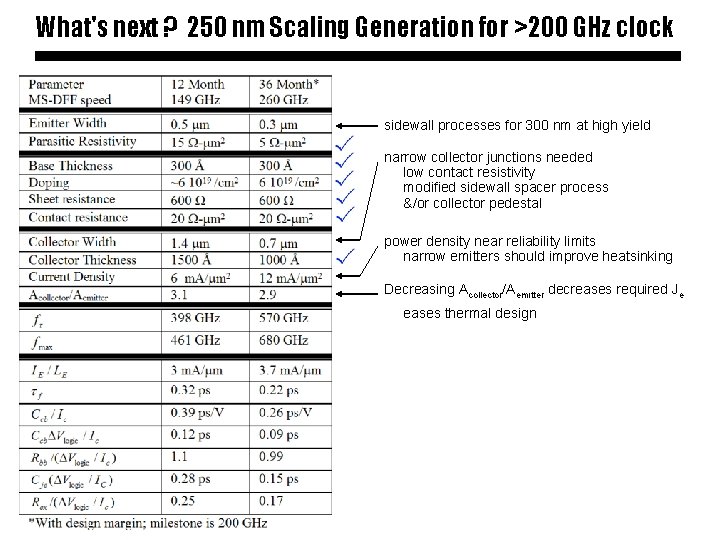

What's next ? 250 nm Scaling Generation for >200 GHz clock sidewall processes for 300 nm at high yield narrow collector junctions needed low contact resistivity modified sidewall spacer process &/or collector pedestal power density near reliability limits narrow emitters should improve heatsinking Decreasing Acollector/Aemitter decreases required Je eases thermal design

Indium Phosphide HBTs for 100 -200 GHz ICs In. P HBT: high speed & room left to scale 150 GHz digital clock (static divider) at 500 nm scaling generation 210 GHz clock should soon be feasible at 250 nm scaling. low NRE; low mask cost Applications feasible soon: 160 Gb fiber ICs, 300 GHz MIMICs for communications & radar GHz mixed-signal ICs for radar & communications Planar processes address yield limitations emitter-base junction: liftoff-free dielectric sidewall process base-collector junction: planar implanted process Volume markets are needed to drive down cost Ga. As HBT power amplifier processes are cheap Why can't In. P HBT be inexpensive ? In. P HBT can be scaled at high yield Key to survival of the technology are emergence of singificant markets progress relative to CMOS & In. P

- Slides: 25