2003 ITRS Factory Integration Chapter Factory Operations Backup

2003 ITRS Factory Integration Chapter Factory Operations Backup Section Details and Assumptions for Technology Requirements and Potential Solutions 2020/9/17 ITRS Factory Integration TWG 1

Factory Operations Backup Outline 1. 2. 3. 4. 5. 6. 7. 8. 9. 2020/9/17 Scope of the Section Contributors How Metrics were Selected SEMATECH and ITRS Metrics Alignment X-Factor Details High Mix Potential Solutions Other Potential Solutions Factory Operations Research Center (FORCe) Suggested University and Industry Research for 2004+ ITRS Factory Integration TWG 2

Contributors to Factory Operations ¬ ¬ ¬ 2020/9/17 Don Martin (IBM) Mani Janakiram (Intel) Martin Haller (Infineon) John Fowler (ASU) Donald Hicks (UT-Dallas) Mike Schwartz (ISMT) Shantha Mohan (Consultant) Raja Sunkara (National) Eric Christensen (AMD) John Plummer (Consultant) Abol Taghizadeh (Tefen) ¬ ¬ ¬ Hiromi Yajima (Toshiba) Ashwin Ghatalia (Phillips) Dev Pillai (Intel) Arieh Greenberg (Infineon) Arnie Steinman (ION Systems) Court Skinner (Consultant) Eric Englhardt (AMAT) Shige Kobayashi (Renesas) Jeff Pettinato (Intel) Junji Iwasaki (Renesas) Michio Honma (NEC Electronics) ITRS Factory Integration TWG 3

How Metrics were selected ¬ Almost every metric is a best in class or close to best in class F Sources are: Rob Leachman’s published 200 mm benchmarking data, Individual IC maker feedback, and I 300 I Factory Guidelines for 300 mm tool productivity ¬ It is likely a factory will not achieve all the metrics outlined in the roadmap concurrently F Individual business models will dictate which metric is more important than others F It is likely certain metrics may be sacrificed (periodically) for attaining other metrics (Example: OEE/Utilization versus Cycle time) ¬ The Factory Integration metrics are not as tightly tied to technology nodes as in other chapters such as Lithography F However, nodes offer convenient interception points to bring in new capability, tools, software and other operational potential solutions ¬ Inclusion of each metric is dependent on consensus agreement We think the metrics provide a good summary of stretch goals for most companies in today’s challenging environment. 2020/9/17 ITRS Factory Integration TWG 4

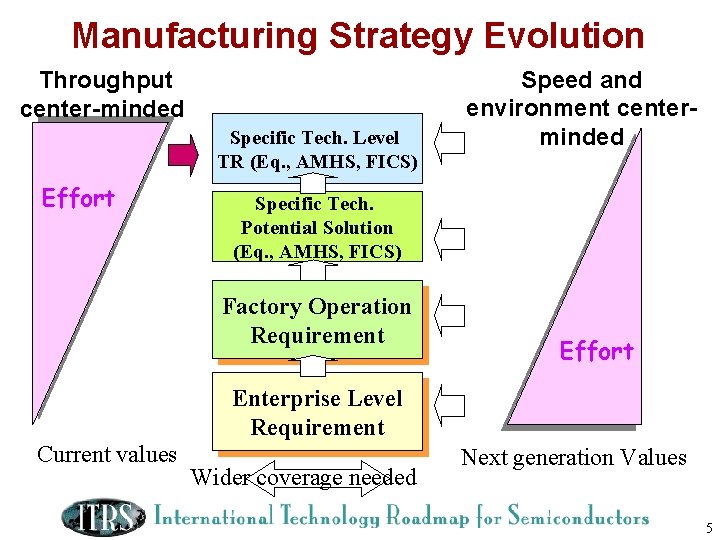

Manufacturing Strategy Evolution Throughput center-minded Specific Tech. Level TR (Eq. , AMHS, FICS) Effort Speed and environment centerminded Specific Tech. Potential Solution (Eq. , AMHS, FICS) Factory Operation Requirement Effort Enterprise Level Requirement Current values Wider coverage needed Next generation Values 5

International SEMATECH Metrics Alignment Rev 1 09/06/03 6

ITRS/ISMT Metrics Alignment Objective & Status § Align 300 mm metrics definitions that are collected for ISMT with those for the ITRS for consistency l Status: Done and Agreed for 37 metrics by ISMT. ITRS sync on production equipment in progress. Expect to complete the alignment by the end of the 2003 ITRS roadmap year in September § Long term objective (2004+) is to develop a process where best in class metrics can be collected globally by SIA or an independent equivalent and used for ITRS synchronization l l 09/06/03 Industry Best in Class (BIC) Data sharing proposal will not occur in 2003 and will be contingent on number of global 300 mm Fabs for 2004 JEITA (Japan) is ok with the concept, however, since there is only 1 300 mm Fab (Renesas/Trecenti), all of their values will be lined to that fab. Timing is key for them Taiwan TSIA has agreed to discuss, but Ft. F has been pushed to August due to SARS Need to close on SIA willingness to manage cross regional data – AR for Jeff to close by September Ft. F 7

300 mm Metrics Sync Agreement with ITRS Summary of Approvals from MMC/PAG/Council Ft. F Meetings § ISMT has agreed to definitions for 36 combined operations, production equipment and AMHS metrics (see slide xx for summary) § ISMT will use three process technology nodes for 300 mm Fabs: l l 1) >130 nm, 2) =130 nm and 3) < 130 nm ITRS defines current node as 90 nm and this will be the focus for future BIC calculations § Use minimum printed image on a process recipe to define technology nodes l Example: Use minimum printed image on Poly, Contacts or Isolation (DRAM) layers § ITRS defines 130 nm node as having 24 layers § Please direct any questions or comments to l l 09/06/03 Mike Schwartz -> (512) 356 -3926; mike. schwartz@sematech. org Jeff Pettinato -> (480) 554 -4077; jeffrey. s. pettinato@intel. com 8

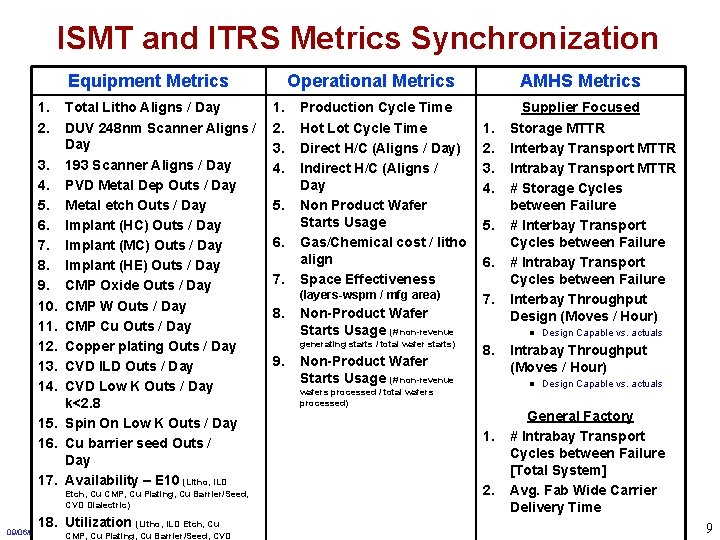

ISMT and ITRS Metrics Synchronization Equipment Metrics 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. Total Litho Aligns / Day DUV 248 nm Scanner Aligns / Day 193 Scanner Aligns / Day PVD Metal Dep Outs / Day Metal etch Outs / Day Implant (HC) Outs / Day Implant (MC) Outs / Day Implant (HE) Outs / Day CMP Oxide Outs / Day CMP W Outs / Day CMP Cu Outs / Day Copper plating Outs / Day CVD ILD Outs / Day CVD Low K Outs / Day k<2. 8 Spin On Low K Outs / Day Cu barrier seed Outs / Day Availability – E 10 (Litho, ILD Etch, Cu CMP, Cu Plating, Cu Barrier/Seed, CVD Dialectric) 18. Utilization (Litho, ILD Etch, Cu 09/06/03 CMP, Cu Plating, Cu Barrier/Seed, CVD Operational Metrics 1. 2. 3. 4. 5. 6. 7. Production Cycle Time Hot Lot Cycle Time Direct H/C (Aligns / Day) Indirect H/C (Aligns / Day Non Product Wafer Starts Usage Gas/Chemical cost / litho align Space Effectiveness (layers-wspm / mfg area) 8. Non-Product Wafer Starts Usage (# non-revenue generating starts / total wafer starts) 9. Non-Product Wafer Starts Usage (# non-revenue AMHS Metrics 1. 2. 3. 4. 5. 6. 7. Supplier Focused Storage MTTR Interbay Transport MTTR Intrabay Transport MTTR # Storage Cycles between Failure # Interbay Transport Cycles between Failure # Intrabay Transport Cycles between Failure Interbay Throughput Design (Moves / Hour) l 8. Intrabay Throughput (Moves / Hour) l wafers processed / total wafers processed) 1. 2. Design Capable vs. actuals General Factory # Intrabay Transport Cycles between Failure [Total System] Avg. Fab Wide Carrier Delivery Time 9

Production Lot Cycle Time § Average Cycle Time Per Layer for all Production Lots § Average duration, expressed in fractional working days, consumed only by production lots of wafers from time of release into the fab until time of exit from the fab: Exit includes final parametric test and wafer processes after final parametric test up to die probe/sort, divided by the number of photo wafer layers in the process flow. § Notes: l l l 09/06/03 Note capacity loading percentage on data entry template Weighted average by volume Number of photo layers is a volume weighted average 10

Hot Lot Cycle Time § Average Cycle Time Per Layer for Hot Lots § Average duration, expressed in fractional working days, consumed only by fastest class of full flow priority lots of wafers from time of release into the fab until time of exit from the fab: Exit includes final parametric test and wafer processes after final parametric test up to die probe/sort, divided by the number of photo wafer layers in the process flow. § Notes: l l l 09/06/03 Hot Lot = Top 5% of lots in the Fab from a priority perspective Note capacity loading percentage on data entry template Weighted average by volume Number of photo layers is a volume weighted average Does not include partial flow lots (i. e. wafers released from mid-flow wafer banks or engineering experiments) 11

Direct H/C Productivity (Aligns / Day) § Photo Alignments Completed Per Non-exempt Hour § Total number of photo alignments completed, divided by hours worked by: l l Operators (ALL operators in wafer fab including final parametric test) Maintenance Techs (internal/external) Process Technicians Sustaining Supplier Technicians ( including on call) § Notes: l l l 09/06/03 Include temporary/contract employees Rework not included Include production wafers, engineering wafers (optional), but no monitor wafers 12

Indirect H/C Productivity (Aligns / Day) § Photo Alignments Completed Per Total Exempt Headcount Per Day § Total number of photo alignments completed, divided by total exempt fab headcount. Total exempt headcount includes all personnel and only personnel from the following groups: l l Operations Managers/Supervisors Process Engineers/Managers Equipment Engineers/Managers Dedicated Engineering Support from Equipment Suppliers § Notes: l l l 09/06/03 Do not include Probe Test, Yield analysis, CIM/IS, development, production control etc. ) Rework not included Include production wafers, engineering wafers – (optional) No monitor wafers Exempt H/C should include central or support group personnel working in the factory for the areas listed above 13

Floor Space Effectiveness § Floor Space Effectiveness Weighted average number of mask layers x WSPM Floor space area § Includes the following items: l l Traditional clean room areas (bay/chase, ballroom areas, and other clean areas) Additional areas where equipment is installed including clean tool interface areas and non-clean space for the physical tool footprint (including associated maintenance spaces) § Does not include the following items: l Sub-fab areas where equipment is not installed § Notes: l l 09/06/03 WSPM = actual production starts per month- not FAB capacity Proposed as a yearly benchmark 14

A. Non Product Wafer Starts Usage § Overall factory non-product wafer starts usage # non-revenue generating wafers started Total number of wafers started § Notes: l l 09/06/03 Non-Revenue wafers include controls, monitor, and engineering wafers not sold Do not count new technology development node wafers (e. g. 90 nm or 65 nm TD) processed in either numerator or denominator 15

B. Non Product Wafer Activity Usage § Overall factory non-product wafer activity usage # non-revenue wafers processed through equipment Total number of wafers processed through equipment § Notes: l l 09/06/03 Non-Revenue wafers include controls, monitor, and engineering wafers not sold Do not count new technology development node wafers (e. g. 90 nm or 65 nm TD) processed in either numerator or denominator 16

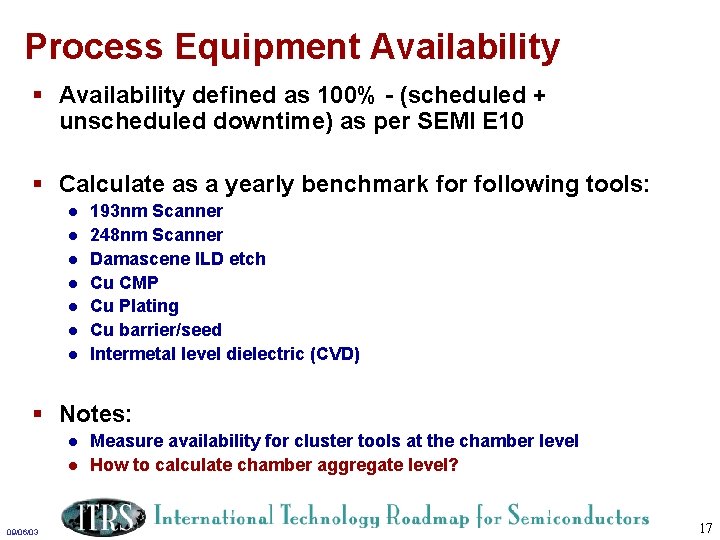

Process Equipment Availability § Availability defined as 100% - (scheduled + unscheduled downtime) as per SEMI E 10 § Calculate as a yearly benchmark for following tools: l l l l 193 nm Scanner 248 nm Scanner Damascene ILD etch Cu CMP Cu Plating Cu barrier/seed Intermetal level dielectric (CVD) § Notes: l l 09/06/03 Measure availability for cluster tools at the chamber level How to calculate chamber aggregate level? 17

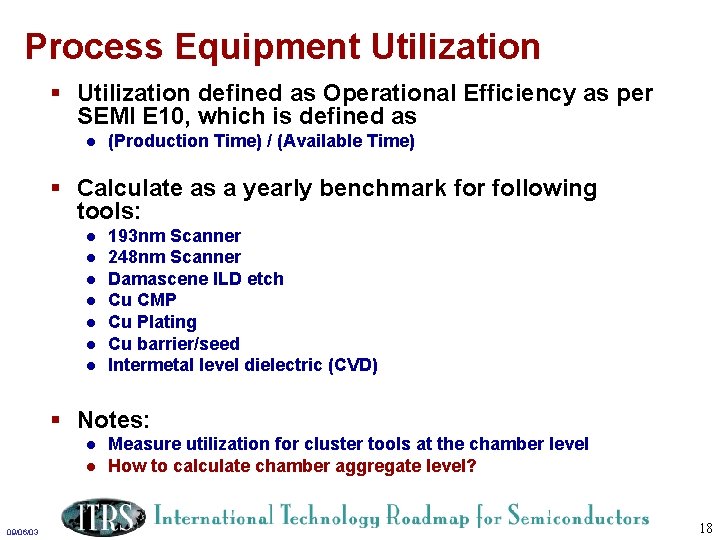

Process Equipment Utilization § Utilization defined as Operational Efficiency as per SEMI E 10, which is defined as l (Production Time) / (Available Time) § Calculate as a yearly benchmark for following tools: l l l l 193 nm Scanner 248 nm Scanner Damascene ILD etch Cu CMP Cu Plating Cu barrier/seed Intermetal level dielectric (CVD) § Notes: l l 09/06/03 Measure utilization for cluster tools at the chamber level How to calculate chamber aggregate level? 18

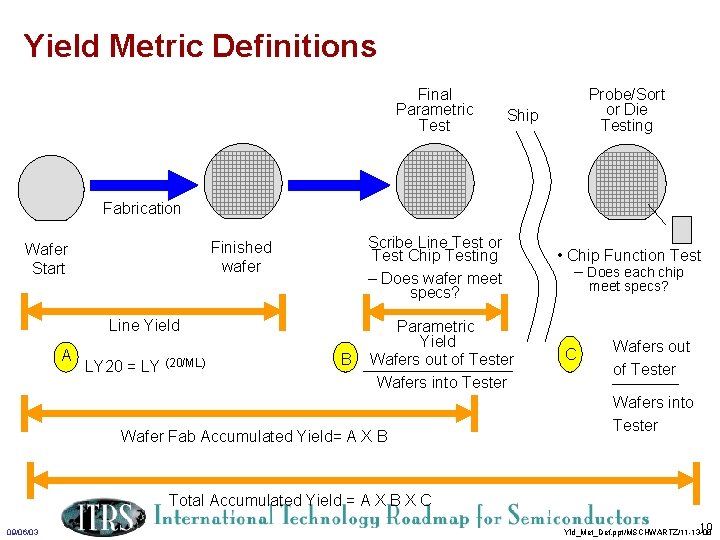

Yield Metric Definitions Final Parametric Test Probe/Sort or Die Testing Ship Fabrication Scribe Line Test or Test Chip Testing – Does wafer meet specs? Finished wafer Wafer Start Line Yield A LY 20 = LY (20/ML) B Parametric Yield Wafers out of Tester Wafers into Tester Wafer Fab Accumulated Yield= A X B • Chip Function Test – Does each chip meet specs? C Wafers out of Tester Wafers into Tester Total Accumulated Yield = A X B X C 09/06/03 19 Yld_Met_Def. ppt/MSCHWARTZ/11 -13 -00

X-Factor Background & Definitions Rev 1 09/06/03 20

09/06/03 21

09/06/03 22

09/06/03 23

09/06/03 24

09/06/03 25

09/06/03 26

09/06/03 27

09/06/03 28

09/06/03 29

09/06/03 30

09/06/03 31

ITRS Factory Integration Integrated Potential Solutions for High Mix Production Discussed at 12 July 2003 Ft. F Meeting at SEMICON West 09/06/03 32

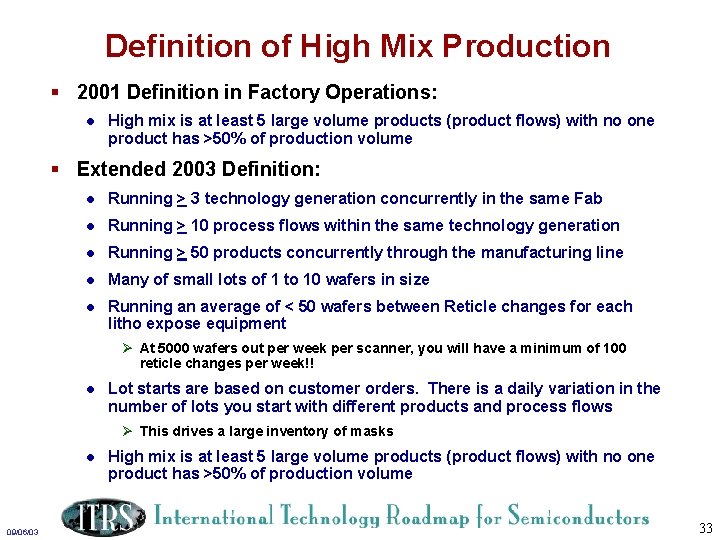

Definition of High Mix Production § 2001 Definition in Factory Operations: l High mix is at least 5 large volume products (product flows) with no one product has >50% of production volume § Extended 2003 Definition: l Running > 3 technology generation concurrently in the same Fab l Running > 10 process flows within the same technology generation l Running > 50 products concurrently through the manufacturing line l Many of small lots of 1 to 10 wafers in size l Running an average of < 50 wafers between Reticle changes for each litho expose equipment Ø At 5000 wafers out per week per scanner, you will have a minimum of 100 reticle changes per week!! l Lot starts are based on customer orders. There is a daily variation in the number of lots you start with different products and process flows Ø This drives a large inventory of masks l 09/06/03 High mix is at least 5 large volume products (product flows) with no one product has >50% of production volume 33

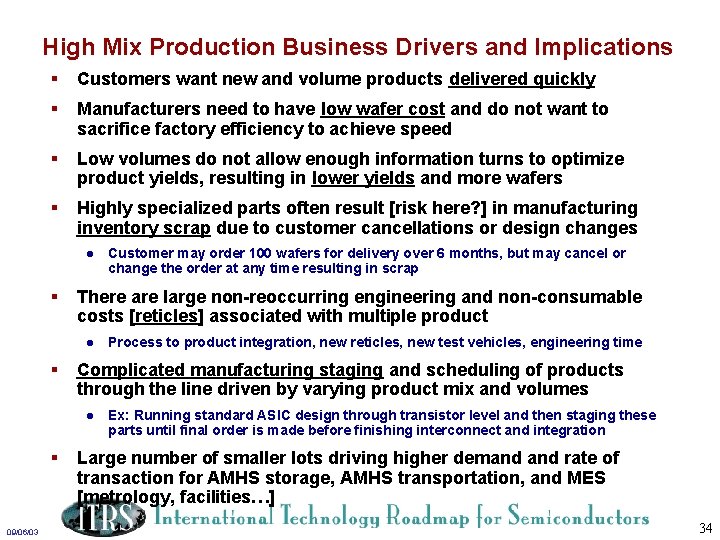

High Mix Production Business Drivers and Implications § Customers want new and volume products delivered quickly § Manufacturers need to have low wafer cost and do not want to sacrifice factory efficiency to achieve speed § Low volumes do not allow enough information turns to optimize product yields, resulting in lower yields and more wafers § Highly specialized parts often result [risk here? ] in manufacturing inventory scrap due to customer cancellations or design changes l § There are large non-reoccurring engineering and non-consumable costs [reticles] associated with multiple product l § 09/06/03 Process to product integration, new reticles, new test vehicles, engineering time Complicated manufacturing staging and scheduling of products through the line driven by varying product mix and volumes l § Customer may order 100 wafers for delivery over 6 months, but may cancel or change the order at any time resulting in scrap Ex: Running standard ASIC design through transistor level and then staging these parts until final order is made before finishing interconnect and integration Large number of smaller lots driving higher demand rate of transaction for AMHS storage, AMHS transportation, and MES [metrology, facilities…] 34

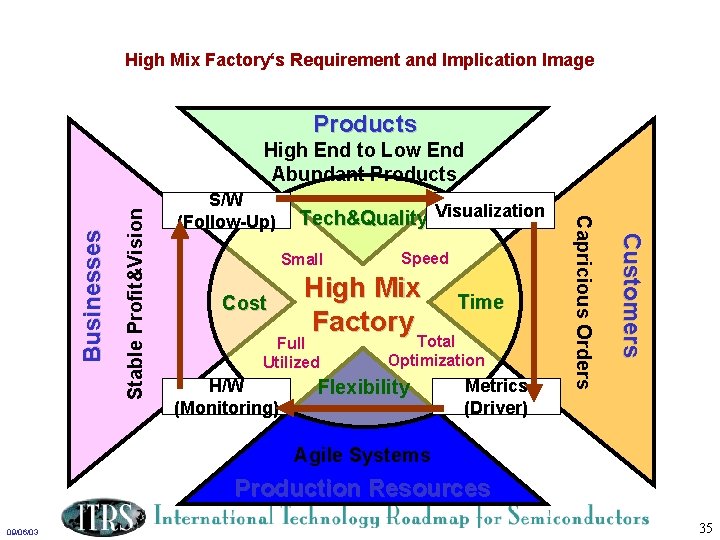

High Mix Factory‘s Requirement and Implication Image Products Tech&Quality Visualization Small Cost High Mix Factory Full Utilized H/W (Monitoring) Speed Time Total Optimization Flexibility Metrics (Driver) Customers Stable Profit&Vision S/W (Follow-Up) Capricious Orders Businesses High End to Low End Abundant Products Agile Systems Production Resources 09/06/03 35

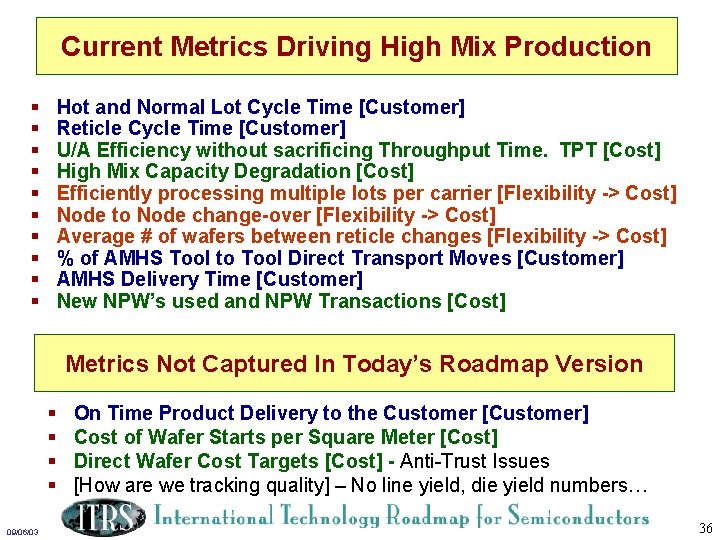

Current Metrics Driving High Mix Production § § § § § Hot and Normal Lot Cycle Time [Customer] Reticle Cycle Time [Customer] U/A Efficiency without sacrificing Throughput Time. TPT [Cost] High Mix Capacity Degradation [Cost] Efficiently processing multiple lots per carrier [Flexibility -> Cost] Node to Node change-over [Flexibility -> Cost] Average # of wafers between reticle changes [Flexibility -> Cost] % of AMHS Tool to Tool Direct Transport Moves [Customer] AMHS Delivery Time [Customer] New NPW’s used and NPW Transactions [Cost] Metrics Not Captured In Today’s Roadmap Version § § 09/06/03 On Time Product Delivery to the Customer [Customer] Cost of Wafer Starts per Square Meter [Cost] Direct Wafer Cost Targets [Cost] - Anti-Trust Issues [How are we tracking quality] – No line yield, die yield numbers… 36

Factors to Mitigate High Mix Issues § Use of Field Programmability vs. ASIC l Reduces the amount of separate and distinct products that are required by leveraging programmable vs. hard coded logic § Use of System in a Package (SIP) vs. System on a Chip (SOC) to reduce cycle time, improve yield, lower cost l 09/06/03 Customer may not get exactly what they want with SIP since this implies use of standard parts in the package and possible performance loss, but they will get lower cost and cycle times… 37

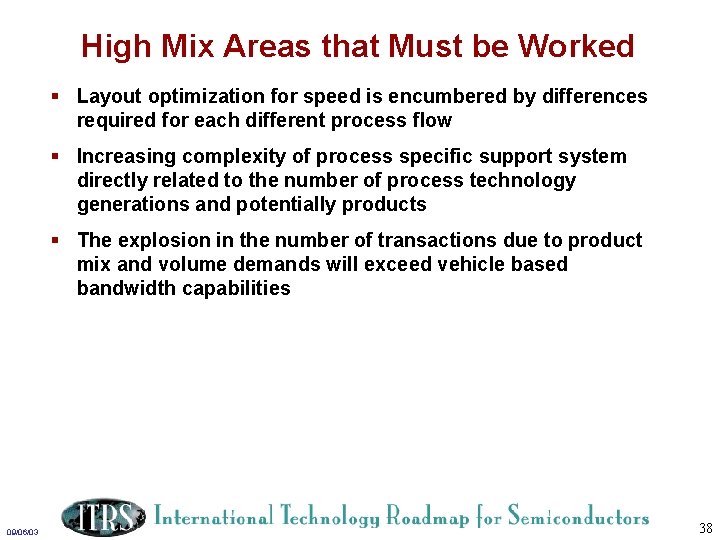

High Mix Areas that Must be Worked § Layout optimization for speed is encumbered by differences required for each different process flow § Increasing complexity of process specific support system directly related to the number of process technology generations and potentially products § The explosion in the number of transactions due to product mix and volume demands will exceed vehicle based bandwidth capabilities 09/06/03 38

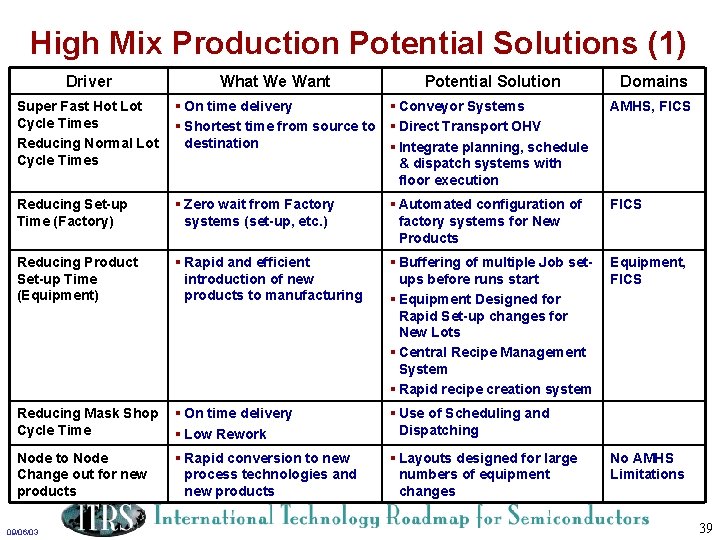

High Mix Production Potential Solutions (1) Driver What We Want Potential Solution Domains Super Fast Hot Lot Cycle Times Reducing Normal Lot Cycle Times § On time delivery § Conveyor Systems § Shortest time from source to § Direct Transport OHV destination § Integrate planning, schedule & dispatch systems with floor execution AMHS, FICS Reducing Set-up Time (Factory) § Zero wait from Factory systems (set-up, etc. ) § Automated configuration of factory systems for New Products FICS Reducing Product Set-up Time (Equipment) § Rapid and efficient introduction of new products to manufacturing § Buffering of multiple Job setups before runs start § Equipment Designed for Rapid Set-up changes for New Lots § Central Recipe Management System § Rapid recipe creation system Equipment, FICS Reducing Mask Shop Cycle Time § On time delivery § Low Rework § Use of Scheduling and Dispatching Node to Node Change out for new products § Rapid conversion to new process technologies and new products § Layouts designed for large numbers of equipment changes 09/06/03 No AMHS Limitations 39

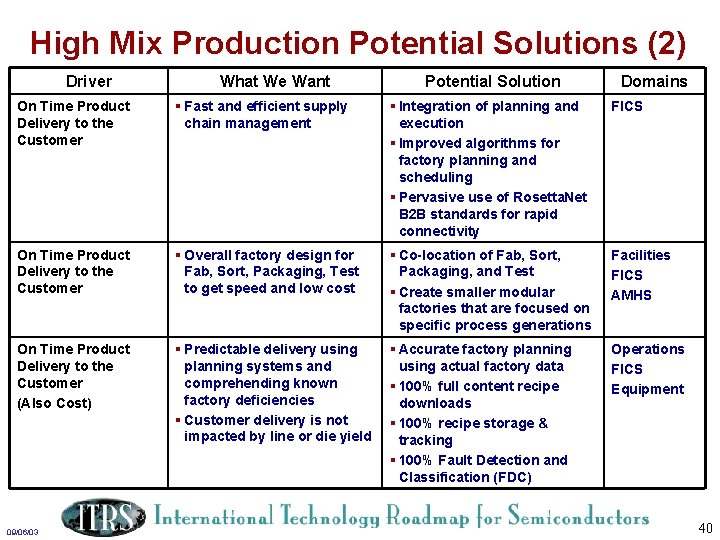

High Mix Production Potential Solutions (2) Driver What We Want Potential Solution Domains On Time Product Delivery to the Customer § Fast and efficient supply chain management § Integration of planning and execution § Improved algorithms for factory planning and scheduling § Pervasive use of Rosetta. Net B 2 B standards for rapid connectivity FICS On Time Product Delivery to the Customer § Overall factory design for Fab, Sort, Packaging, Test to get speed and low cost § Co-location of Fab, Sort, Packaging, and Test § Create smaller modular factories that are focused on specific process generations Facilities FICS AMHS On Time Product Delivery to the Customer (Also Cost) § Predictable delivery using planning systems and comprehending known factory deficiencies § Customer delivery is not impacted by line or die yield § Accurate factory planning using actual factory data § 100% full content recipe downloads § 100% recipe storage & tracking § 100% Fault Detection and Classification (FDC) Operations FICS Equipment 09/06/03 40

High Mix Production Potential Solutions (3) Driver What We Want Potential Solution Cost Reduction § Reduce the cost of large factories Cost Reduction § Reduce the cost of the § Create smaller modular Facility factory to manageable levels factories that are focused on specific process generations 09/06/03 § Segregated functional areas (ex. CMP, C 4, Sort, E-Test) to alternate areas on the site and place these in low cost environments § Reuse of existing facilities Domains Facility 41

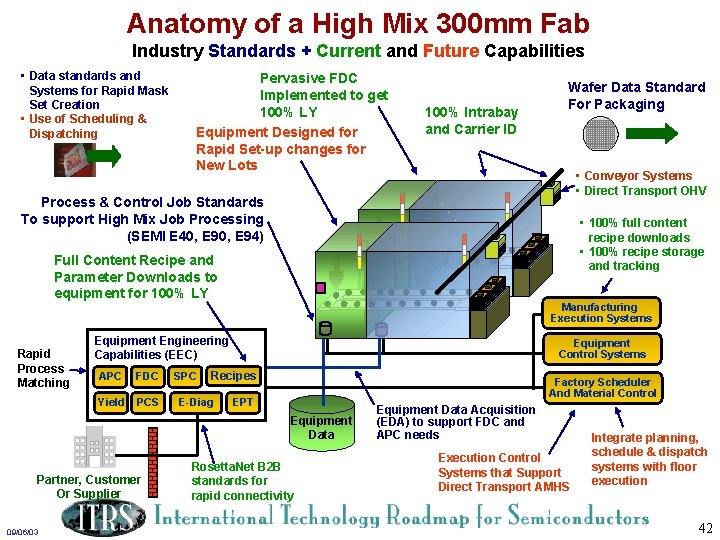

Anatomy of a High Mix 300 mm Fab Industry Standards + Current and Future Capabilities • Data standards and Systems for Rapid Mask Set Creation • Use of Scheduling & Dispatching Pervasive FDC Implemented to get 100% LY Equipment Designed for Rapid Set-up changes for New Lots 100% Intrabay and Carrier ID Wafer Data Standard For Packaging • Conveyor Systems • Direct Transport OHV Process & Control Job Standards To support High Mix Job Processing (SEMI E 40, E 94) • 100% full content recipe downloads • 100% recipe storage and tracking Full Content Recipe and Parameter Downloads to equipment for 100% LY Rapid Process Matching Manufacturing Execution Systems Equipment Engineering Capabilities (EEC) APC FDC Yield PCS SPC Equipment Control Systems Recipes E-Diag Factory Scheduler And Material Control EPT Equipment Data Partner, Customer Or Supplier 09/06/03 Rosetta. Net B 2 B standards for rapid connectivity Equipment Data Acquisition (EDA) to support FDC and APC needs Execution Control Systems that Support Direct Transport AMHS Integrate planning, schedule & dispatch systems with floor execution 42

Other Potential Solutions 09/06/03 43

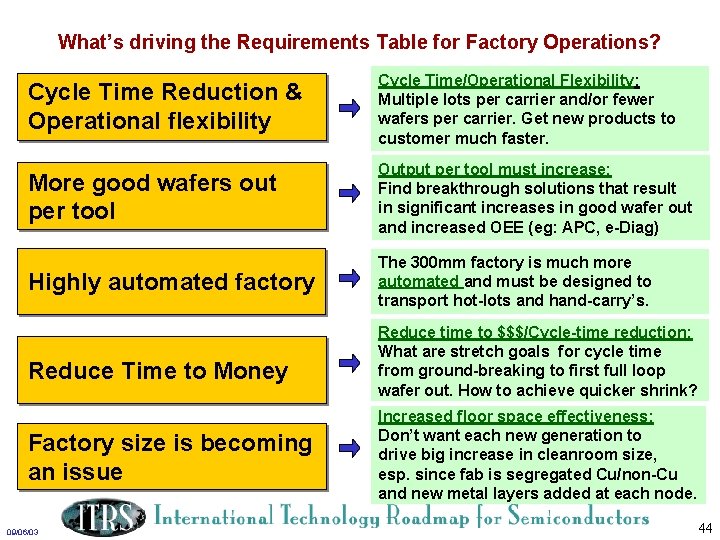

What’s driving the Requirements Table for Factory Operations? Cycle Time Reduction & Operational flexibility Cycle Time/Operational Flexibility: Multiple lots per carrier and/or fewer wafers per carrier. Get new products to customer much faster. More good wafers out per tool Output per tool must increase: Find breakthrough solutions that result in significant increases in good wafer out and increased OEE (eg: APC, e-Diag) Highly automated factory The 300 mm factory is much more automated and must be designed to transport hot-lots and hand-carry’s. Reduce Time to Money Factory size is becoming an issue 09/06/03 Reduce time to $$$/Cycle-time reduction: What are stretch goals for cycle time from ground-breaking to first full loop wafer out. How to achieve quicker shrink? Increased floor space effectiveness: Don’t want each new generation to drive big increase in cleanroom size, esp. since fab is segregated Cu/non-Cu and new metal layers added at each node. 44

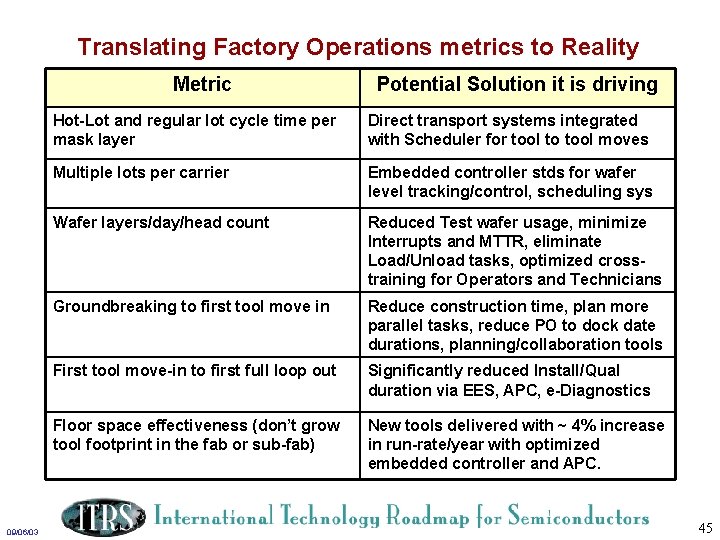

Translating Factory Operations metrics to Reality Metric 09/06/03 Potential Solution it is driving Hot-Lot and regular lot cycle time per mask layer Direct transport systems integrated with Scheduler for tool to tool moves Multiple lots per carrier Embedded controller stds for wafer level tracking/control, scheduling sys Wafer layers/day/head count Reduced Test wafer usage, minimize Interrupts and MTTR, eliminate Load/Unload tasks, optimized crosstraining for Operators and Technicians Groundbreaking to first tool move in Reduce construction time, plan more parallel tasks, reduce PO to dock date durations, planning/collaboration tools First tool move-in to first full loop out Significantly reduced Install/Qual duration via EES, APC, e-Diagnostics Floor space effectiveness (don’t grow tool footprint in the fab or sub-fab) New tools delivered with ~ 4% increase in run-rate/year with optimized embedded controller and APC. 45

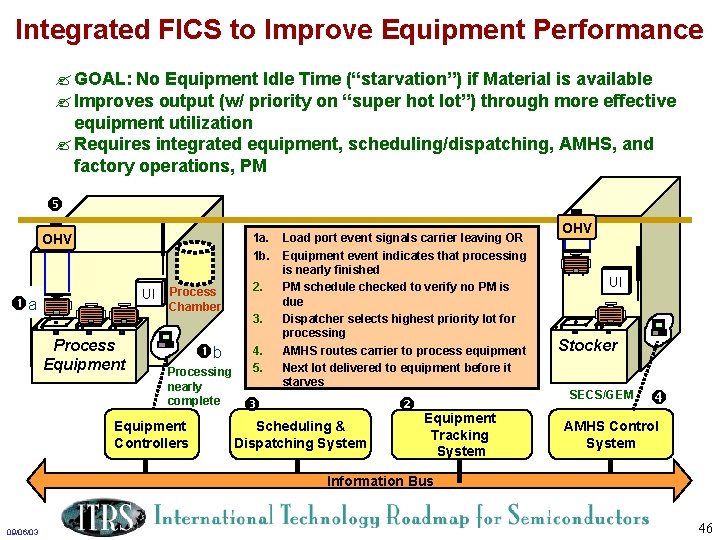

Integrated FICS to Improve Equipment Performance ? GOAL: No Equipment Idle Time (“starvation”) if Material is available ? Improves output (w/ priority on “super hot lot”) through more effective equipment utilization ? Requires integrated equipment, scheduling/dispatching, AMHS, and factory operations, PM 1 a. 1 b. OHV UI a Process Equipment Process Chamber 2. b 4. 5. Processing nearly complete Equipment Controllers 3. Load port event signals carrier leaving OR Equipment event indicates that processing is nearly finished PM schedule checked to verify no PM is due Dispatcher selects highest priority lot for processing AMHS routes carrier to process equipment Next lot delivered to equipment before it starves Scheduling & Dispatching System Equipment Tracking System OHV UI Stocker SECS/GEM AMHS Control System Information Bus 09/06/03 46

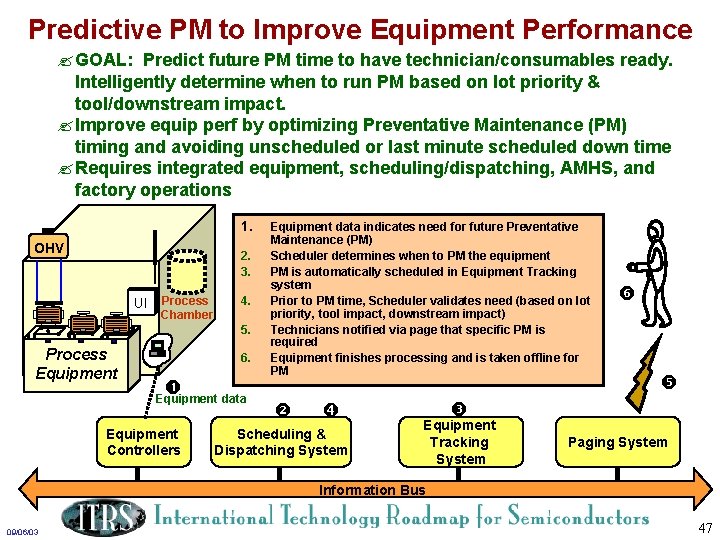

Predictive PM to Improve Equipment Performance ? GOAL: Predict future PM time to have technician/consumables ready. Intelligently determine when to run PM based on lot priority & tool/downstream impact. ? Improve equip perf by optimizing Preventative Maintenance (PM) timing and avoiding unscheduled or last minute scheduled down time ? Requires integrated equipment, scheduling/dispatching, AMHS, and factory operations 1. OHV 2. 3. UI Process Chamber 4. 5. Process Equipment 6. Equipment data Equipment Controllers Equipment data indicates need for future Preventative Maintenance (PM) Scheduler determines when to PM the equipment PM is automatically scheduled in Equipment Tracking system Prior to PM time, Scheduler validates need (based on lot priority, tool impact, downstream impact) Technicians notified via page that specific PM is required Equipment finishes processing and is taken offline for PM Scheduling & Dispatching System Equipment Tracking System Paging System Information Bus 09/06/03 47

Factory Operations Research Center (FORCe) Rev 1 09/06/03 48

FORCe Background and Deliverables Background/History: § § § FORCe is a program integrating the efforts of International Sematech (ISMT) and Semiconductor Research Corporation (SRC) factory systems into a unified strategy for factory science research. Member companies (MC) set the priorities for research efforts and determine how/where the ~$800 K/yr for 3 years (2001 -2003) should be utilized. International Technology Roadmap for Semiconductors (ITRS) provided overall direction for prioritization. Focus is on Fab productivity improvement Deliverables to Member Companies: § § § 09/06/03 Tools (S/W, Algorithms, Methods) Qualified students for MC hire (MS/Ph. D) (50+ students) Research results for MC implementation/adoption 49

Member company prioritized focus areas (2000) • Scheduling policies, and wafer release rules * • Fab cycle time reduction techniques, modeling cycle time reduction methods * • Factory labor modeling methods • Statistical operational control of cycle time and equipment utilization * • Intelligent preventive maintenance techniques * • Demand planning/modeling * • Goal driven modeling methods * • Financial/cost attributes in modeling * Focus areas addressed by FORCe projects 09/06/03 50

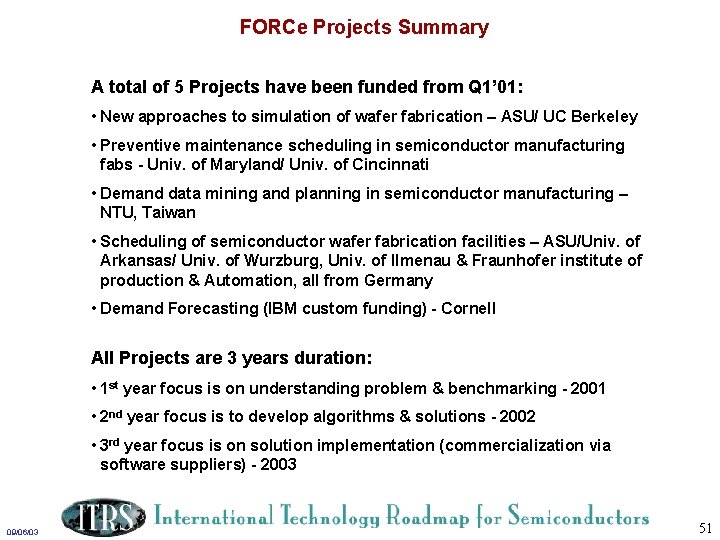

FORCe Projects Summary A total of 5 Projects have been funded from Q 1’ 01: • New approaches to simulation of wafer fabrication – ASU/ UC Berkeley • Preventive maintenance scheduling in semiconductor manufacturing fabs - Univ. of Maryland/ Univ. of Cincinnati • Demand data mining and planning in semiconductor manufacturing – NTU, Taiwan • Scheduling of semiconductor wafer fabrication facilities – ASU/Univ. of Arkansas/ Univ. of Wurzburg, Univ. of Ilmenau & Fraunhofer institute of production & Automation, all from Germany • Demand Forecasting (IBM custom funding) - Cornell All Projects are 3 years duration: • 1 st year focus is on understanding problem & benchmarking - 2001 • 2 nd year focus is to develop algorithms & solutions - 2002 • 3 rd year focus is on solution implementation (commercialization via software suppliers) - 2003 09/06/03 51

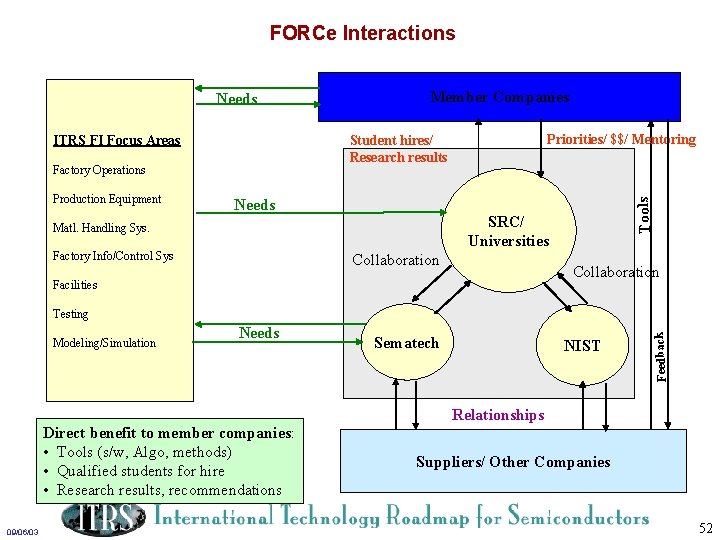

FORCe Interactions ITRS FI Focus Areas Priorities/ $$/ Mentoring Student hires/ Research results Factory Operations Production Equipment Member Companies Needs SRC/ Universities Matl. Handling Sys. Factory Info/Control Sys Tools Needs Collaboration Facilities Modeling/Simulation Needs Sematech NIST Feedback Testing Relationships Direct benefit to member companies: • Tools (s/w, Algo, methods) • Qualified students for hire • Research results, recommendations 09/06/03 Suppliers/ Other Companies 52

FORCe Participating Companies, Universities & Suppliers Companies & Organizations Intel Lucent Motorola TI C IBM R S & Conexant T M HP IS AMD LSI Logic Compaq Eastman Kodak NSI Northtrop PDF Solutions NIST ly NSF n o C UMC SR Intersil Hyundai Infineon y nl o Phillips T M STM IS TSMC 09/06/03 Potential Suppliers Brooks IBEX i 2 Technologies Adexa Wright Williams & Kelly Applied Materials Universities UC Berkeley ASU Univ. of Maryland Univ. of Arkansas Univ. of Cincinnati Cornell Univ. National Taiwan Univ. Not a complete list Univ. of Wurzburg, Germany Fraunhofer Institute, Germany Univ. of Ilmenau, Germany Research Focus Areas (based on ITRS & MC needs) 1. 2. 3. 4. 5. 6. 7. 8. Scheduling policies, and wafer release rules. Fab cycle time reduction techniques, modeling cycle time reduction methods. Factory labor modeling methods. Statistical operational control of cycle time and equip utilization. Intelligent preventive maint techniques Demand planning/modeling. Goal driven modeling methods. Financial/cost attributes in modeling 53

FORCe Project Statistics Notes: 1. Table needs updating 2. FORCe related publications in INFORMS is ~15 3. Funding/year does not show IBM custom funds 09/06/03 54

Research Opportunities 09/06/03 55

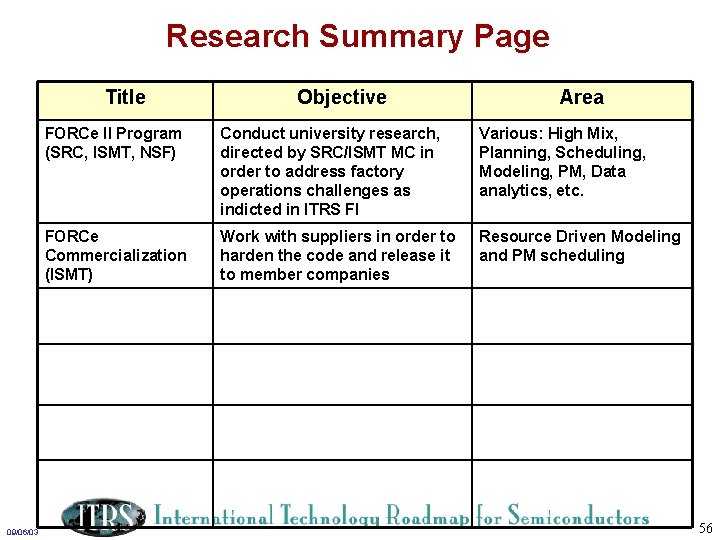

Research Summary Page Title 09/06/03 Objective Area FORCe II Program (SRC, ISMT, NSF) Conduct university research, directed by SRC/ISMT MC in order to address factory operations challenges as indicted in ITRS FI Various: High Mix, Planning, Scheduling, Modeling, PM, Data analytics, etc. FORCe Commercialization (ISMT) Work with suppliers in order to harden the code and release it to member companies Resource Driven Modeling and PM scheduling 56

Proposed Research Details § Title: FORCe II § Objective and Industry Benefit: Conduct university research, directed by SRC/ISMT MC in order to address factory operations challenges as indicted in ITRS FI § Key Deliverables: Solutions in the form of software tools, algorithm, commercialization and qualified students for hire § Timeline: 3 years, starting from 2004 § Resources and Funding Needed: $1 M per year for 3 years § Potential Funding Sources: NSF, SRC and ISMT will be funding this equally 09/06/03 57

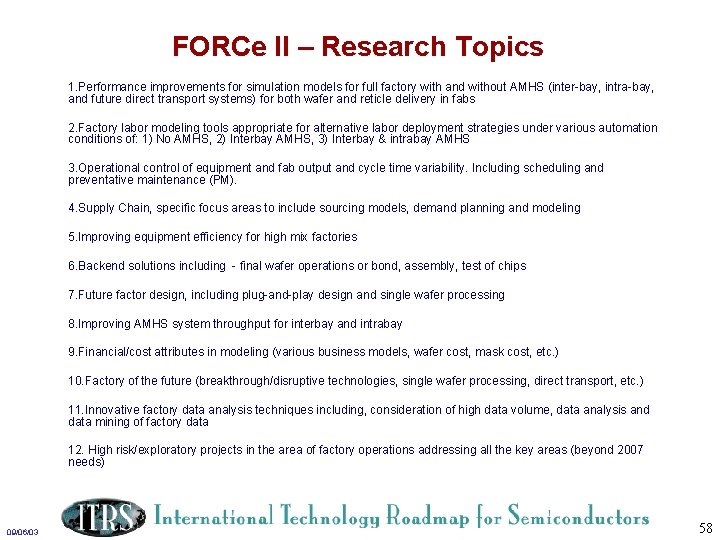

FORCe II – Research Topics 1. Performance improvements for simulation models for full factory with and without AMHS (inter-bay, intra-bay, and future direct transport systems) for both wafer and reticle delivery in fabs 2. Factory labor modeling tools appropriate for alternative labor deployment strategies under various automation conditions of: 1) No AMHS, 2) Interbay AMHS, 3) Interbay & intrabay AMHS 3. Operational control of equipment and fab output and cycle time variability. Including scheduling and preventative maintenance (PM). 4. Supply Chain, specific focus areas to include sourcing models, demand planning and modeling 5. Improving equipment efficiency for high mix factories 6. Backend solutions including - final wafer operations or bond, assembly, test of chips 7. Future factor design, including plug-and-play design and single wafer processing 8. Improving AMHS system throughput for interbay and intrabay 9. Financial/cost attributes in modeling (various business models, wafer cost, mask cost, etc. ) 10. Factory of the future (breakthrough/disruptive technologies, single wafer processing, direct transport, etc. ) 11. Innovative factory data analysis techniques including, consideration of high data volume, data analysis and data mining of factory data 12. High risk/exploratory projects in the area of factory operations addressing all the key areas (beyond 2007 needs) 09/06/03 58

- Slides: 58