2001 ISCS Conference October Tokyo High speed In

2001 ISCS Conference, October, Tokyo High speed In. P-based heterojunction bipolar transistors Mark Rodwell University of California, Santa Barbara rodwell@ece. ucsb. edu 805 -893 -3244, 805 -893 -3262 fax

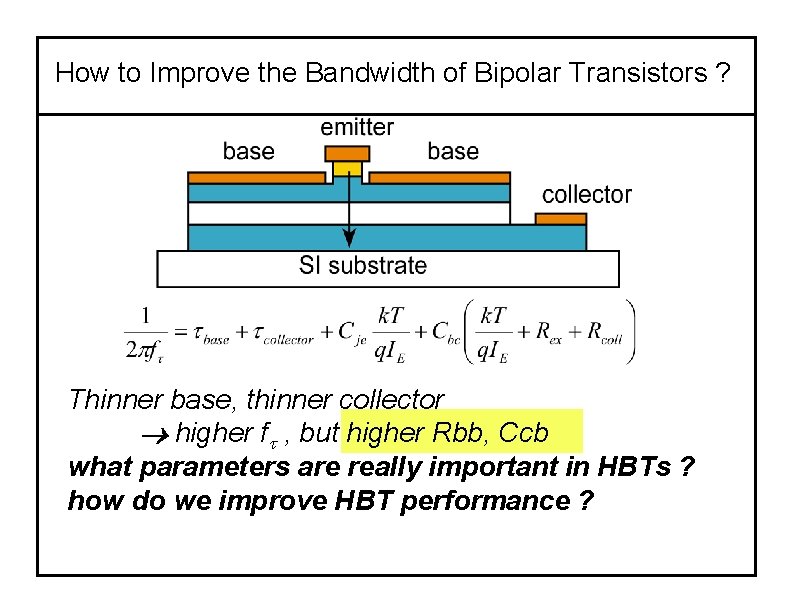

How to Improve the Bandwidth of Bipolar Transistors ? Thinner base, thinner collector ® higher ft , but higher Rbb, Ccb what parameters are really important in HBTs ? how do we improve HBT performance ?

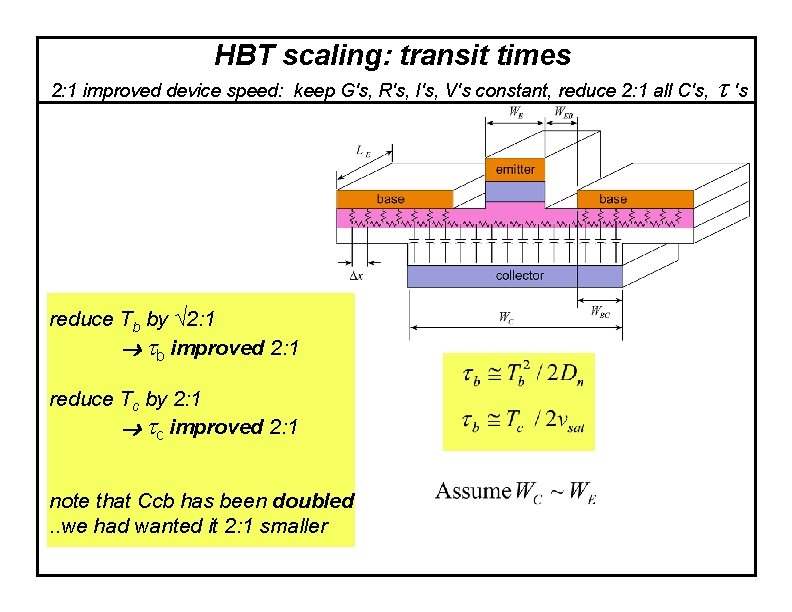

HBT scaling: transit times 2: 1 improved device speed: keep G's, R's, I's, V's constant, reduce 2: 1 all C's, reduce Tb by Ö 2: 1 ® tb improved 2: 1 reduce Tc by 2: 1 ® tc improved 2: 1 note that Ccb has been doubled. . we had wanted it 2: 1 smaller t 's

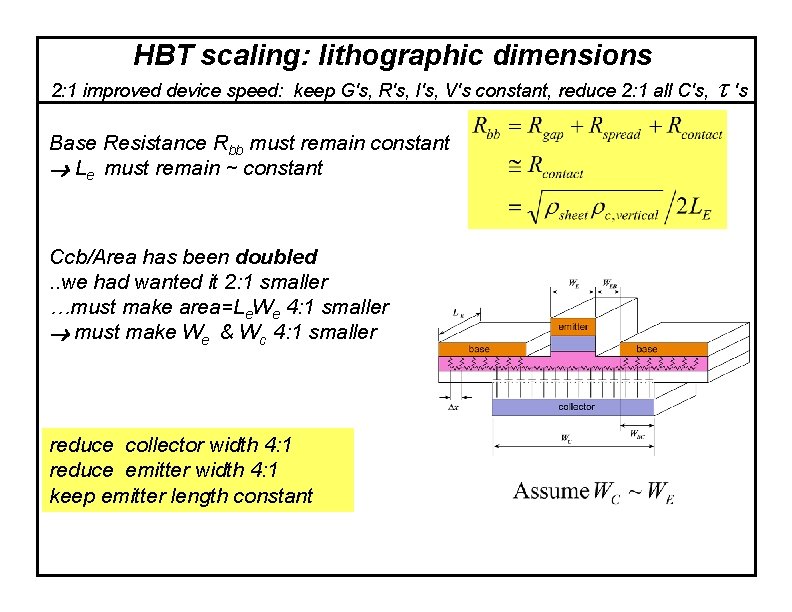

HBT scaling: lithographic dimensions 2: 1 improved device speed: keep G's, R's, I's, V's constant, reduce 2: 1 all C's, Base Resistance Rbb must remain constant ® Le must remain ~ constant Ccb/Area has been doubled. . we had wanted it 2: 1 smaller …must make area=Le. We 4: 1 smaller ® must make We & Wc 4: 1 smaller reduce collector width 4: 1 reduce emitter width 4: 1 keep emitter length constant t 's

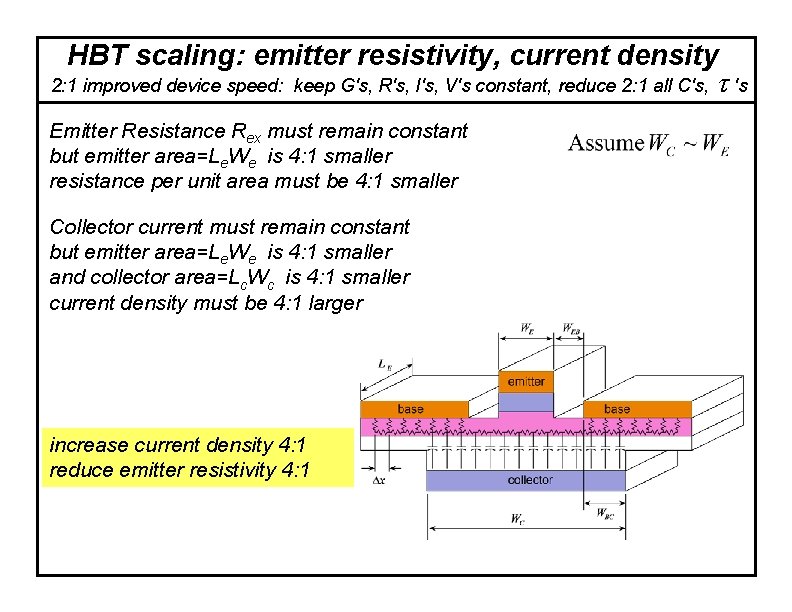

HBT scaling: emitter resistivity, current density 2: 1 improved device speed: keep G's, R's, I's, V's constant, reduce 2: 1 all C's, t 's Emitter Resistance Rex must remain constant but emitter area=Le. We is 4: 1 smaller resistance per unit area must be 4: 1 smaller Collector current must remain constant but emitter area=Le. We is 4: 1 smaller and collector area=Lc. Wc is 4: 1 smaller current density must be 4: 1 larger increase current density 4: 1 reduce emitter resistivity 4: 1

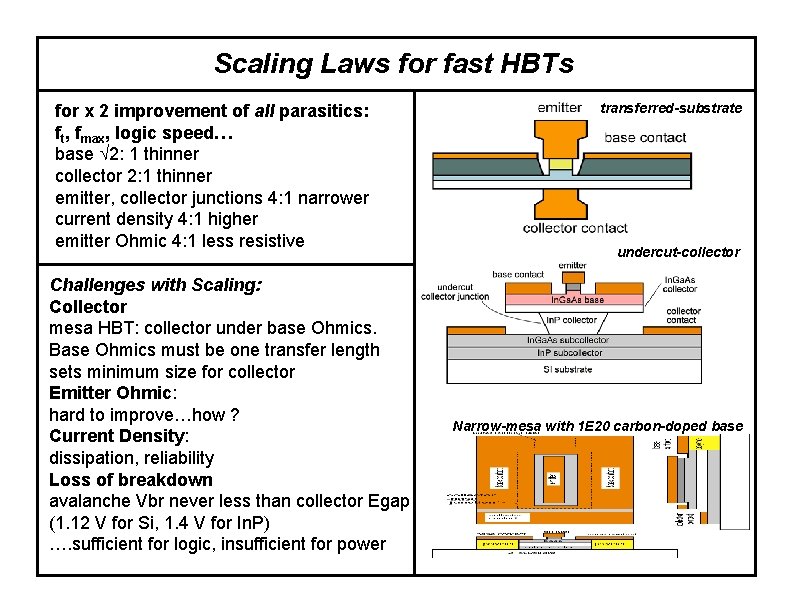

Scaling Laws for fast HBTs for x 2 improvement of all parasitics: ft, fmax, logic speed… base Ö 2: 1 thinner collector 2: 1 thinner emitter, collector junctions 4: 1 narrower current density 4: 1 higher emitter Ohmic 4: 1 less resistive Challenges with Scaling: Collector mesa HBT: collector under base Ohmics. Base Ohmics must be one transfer length sets minimum size for collector Emitter Ohmic: hard to improve…how ? Current Density: dissipation, reliability Loss of breakdown avalanche Vbr never less than collector Egap (1. 12 V for Si, 1. 4 V for In. P) …. sufficient for logic, insufficient for power transferred-substrate undercut-collector Narrow-mesa with 1 E 20 carbon-doped base

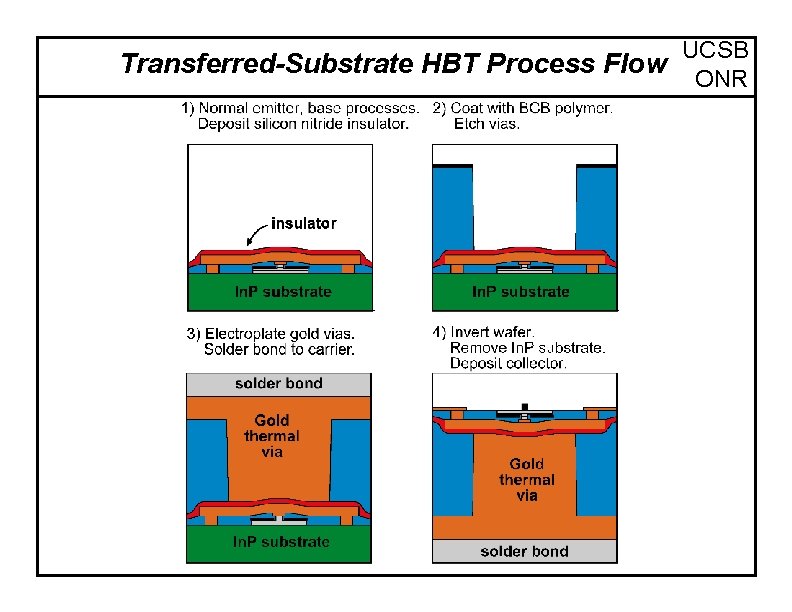

UCSB Transferred-Substrate HBT Process Flow ONR

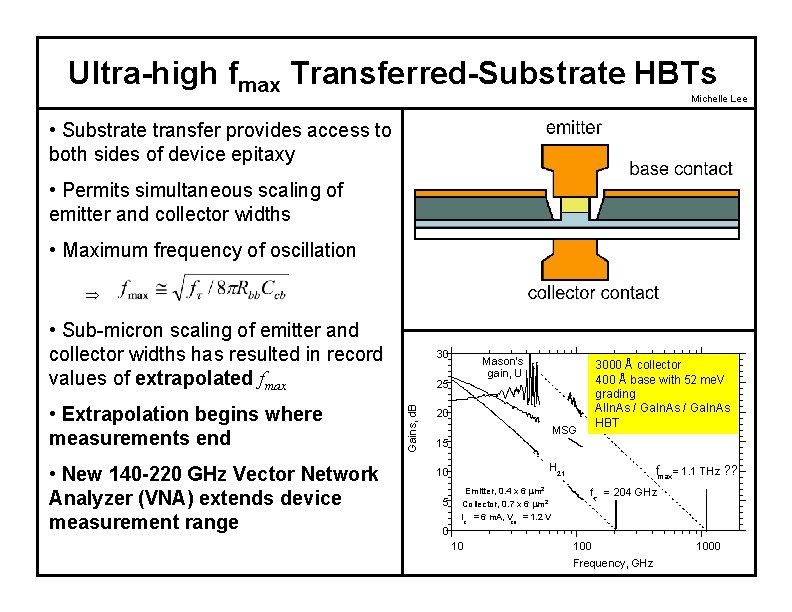

Ultra-high fmax Transferred-Substrate HBTs Michelle Lee • Substrate transfer provides access to both sides of device epitaxy • Permits simultaneous scaling of emitter and collector widths • Maximum frequency of oscillation Þ • Sub-micron scaling of emitter and collector widths has resulted in record values of extrapolated fmax • New 140 -220 GHz Vector Network Analyzer (VNA) extends device measurement range Mason's gain, U 25 Gains, d. B • Extrapolation begins where measurements end 30 3000 Å collector 400 Å base with 52 me. V grading Al. In. As / Ga. In. As HBT 20 MSG 15 H 21 10 5 0 Emitter, 0. 4 x 6 m 2 Collector, 0. 7 x 6 m 2 fmax = 1. 1 THz ? ? ft = 204 GHz Ic = 6 m. A, Vce = 1. 2 V 10 100 Frequency, GHz 1000

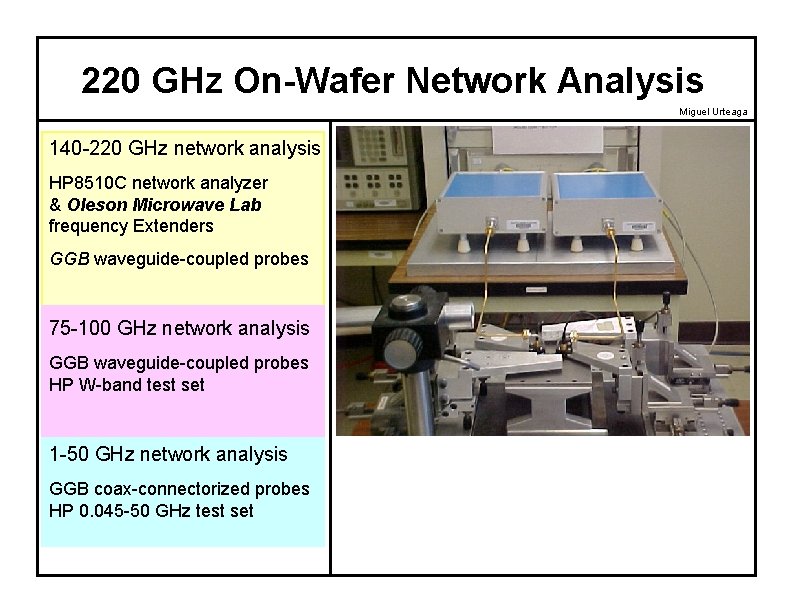

220 GHz On-Wafer Network Analysis Miguel Urteaga 140 -220 GHz network analysis HP 8510 C network analyzer & Oleson Microwave Lab frequency Extenders GGB waveguide-coupled probes 75 -100 GHz network analysis GGB waveguide-coupled probes HP W-band test set 1 -50 GHz network analysis GGB coax-connectorized probes HP 0. 045 -50 GHz test set

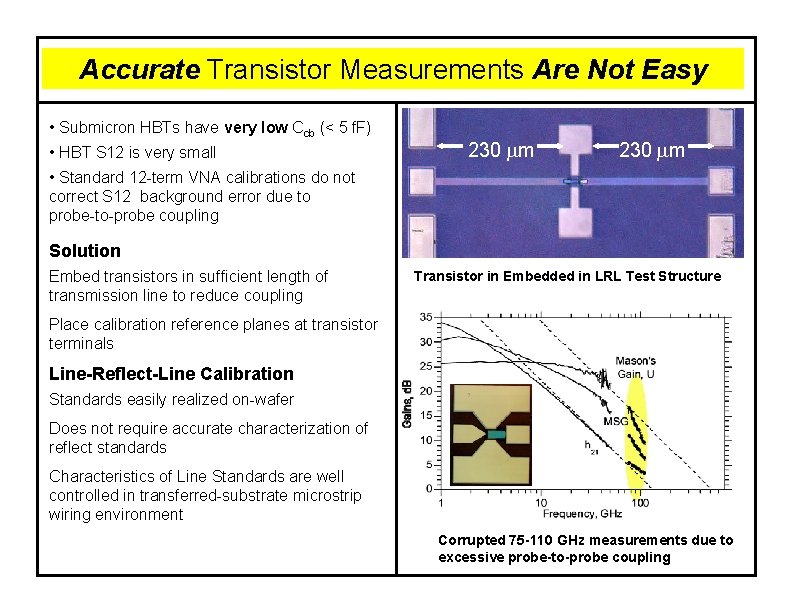

Accurate Transistor Measurements Are Not Easy • Submicron HBTs have very low Ccb (< 5 f. F) • HBT S 12 is very small 230 m • Standard 12 -term VNA calibrations do not correct S 12 background error due to probe-to-probe coupling Solution Embed transistors in sufficient length of transmission line to reduce coupling Transistor in Embedded in LRL Test Structure Place calibration reference planes at transistor terminals Line-Reflect-Line Calibration Standards easily realized on-wafer Does not require accurate characterization of reflect standards Characteristics of Line Standards are well controlled in transferred-substrate microstrip wiring environment Corrupted 75 -110 GHz measurements due to excessive probe-to-probe coupling

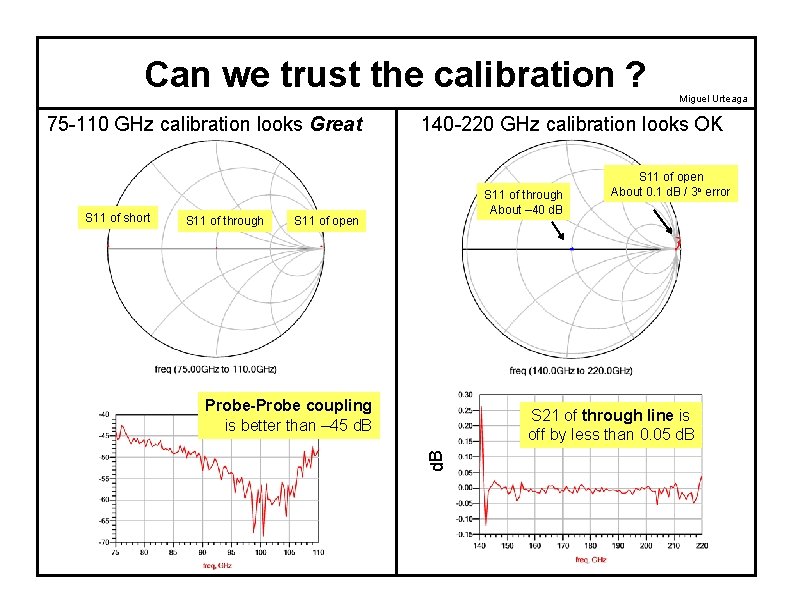

Can we trust the calibration ? 75 -110 GHz calibration looks Great S 11 of through 140 -220 GHz calibration looks OK S 11 of through About – 40 d. B S 11 of open Probe-Probe coupling is better than – 45 d. B S 11 of open About 0. 1 d. B / 3 o error S 21 of through line is off by less than 0. 05 d. B S 11 of short Miguel Urteaga

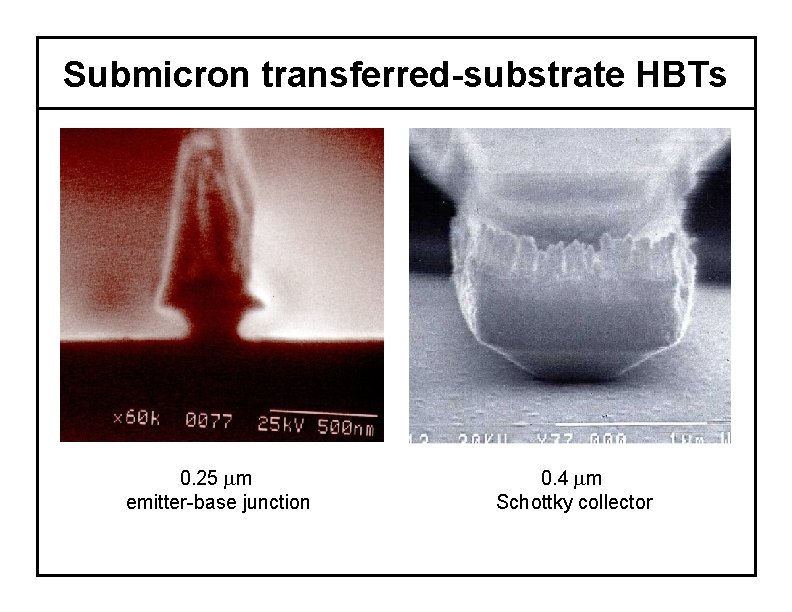

Submicron transferred-substrate HBTs 0. 25 m emitter-base junction 0. 4 m Schottky collector

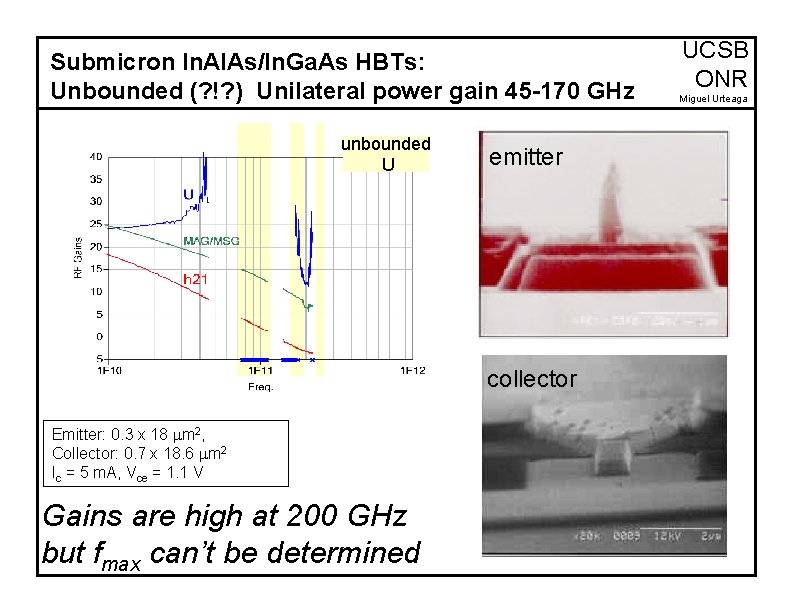

Submicron In. Al. As/In. Ga. As HBTs: Unbounded (? !? ) Unilateral power gain 45 -170 GHz unbounded U emitter collector Emitter: 0. 3 x 18 m 2, Collector: 0. 7 x 18. 6 m 2 Ic = 5 m. A, Vce = 1. 1 V Gains are high at 200 GHz but fmax can’t be determined UCSB ONR Miguel Urteaga

Negative Unilateral Power Gain ? ? ? Can U be Negative? YES, if denominator is negative This may occur for device with a negative output conductance (G 22) or some positive feedback (G 12) What Does Negative U Mean? Device with negative U will have infinite Unilateral Power Gain with the addition of a proper source or load impedance AFTER Unilateralization • Network would have negative output resistance • Can support one-port oscillation • Can provide infinite two-port power gain Select GL such that denominator is zero: Simple Hybrid- HBT model will NOT show negative U

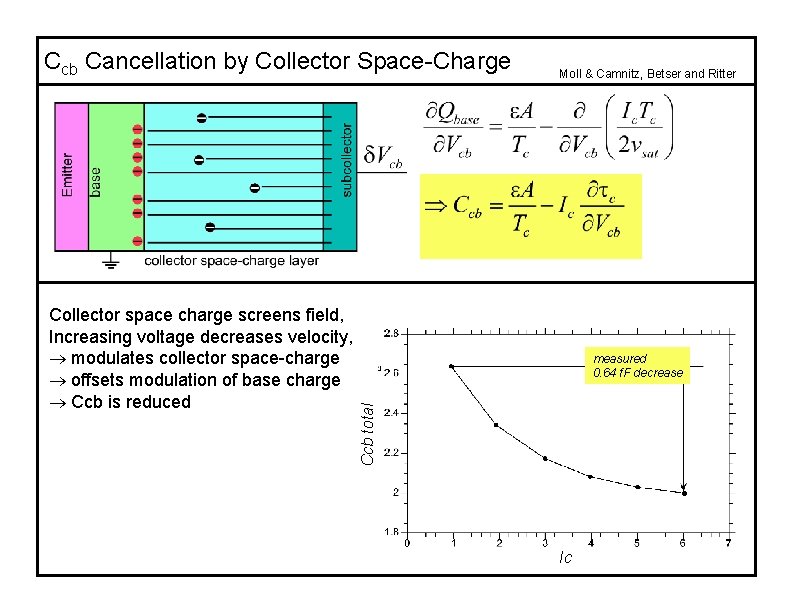

Ccb Cancellation by Collector Space-Charge measured 0. 64 f. F decrease Ccb total Collector space charge screens field, Increasing voltage decreases velocity, ® modulates collector space-charge ® offsets modulation of base charge ® Ccb is reduced Moll & Camnitz, Betser and Ritter Ic

175 GHz Single-Stage Amplifier Submicron HBT Program 6. 3 d. B gain at 175 GHz UCSB Miguel Urteaga

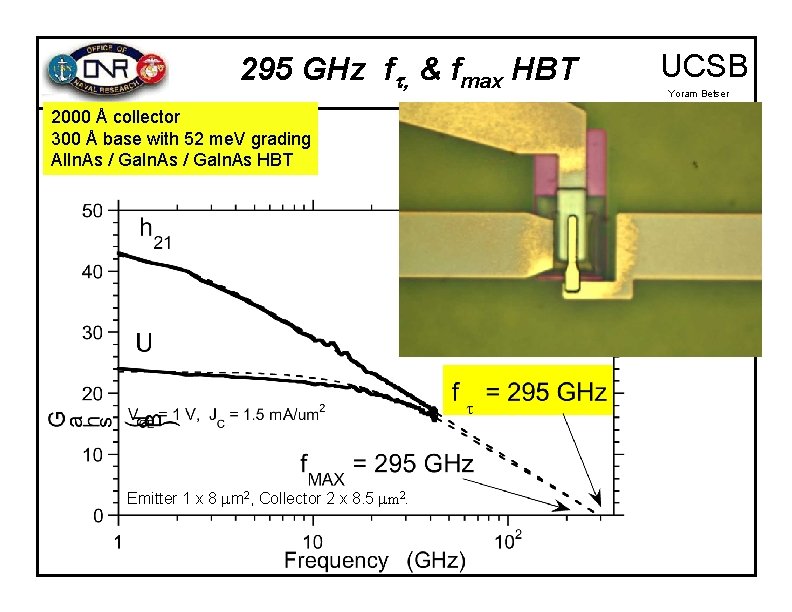

295 GHz f , & fmax HBT 2000 Å collector 300 Å base with 52 me. V grading Al. In. As / Ga. In. As HBT Emitter 1 x 8 m 2, Collector 2 x 8. 5 m 2. UCSB Yoram Betser

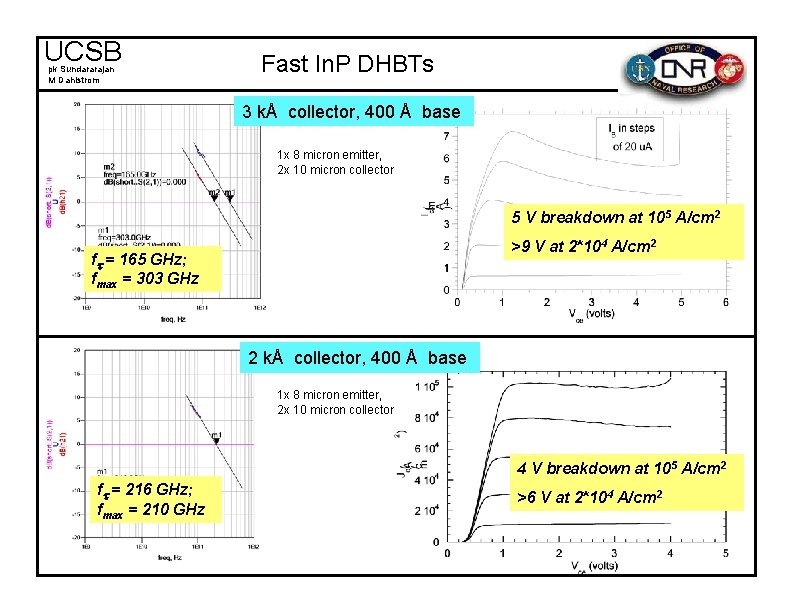

UCSB pk Sundararajan M Dahlstrom Fast In. P DHBTs 3 kÅ collector, 400 Å base 1 x 8 micron emitter, 2 x 10 micron collector 5 V breakdown at 105 A/cm 2 >9 V at 2*104 A/cm 2 f = 165 GHz; fmax = 303 GHz 2 kÅ collector, 400 Å base 1 x 8 micron emitter, 2 x 10 micron collector 4 V breakdown at 105 A/cm 2 f = 216 GHz; fmax = 210 GHz >6 V at 2*104 A/cm 2

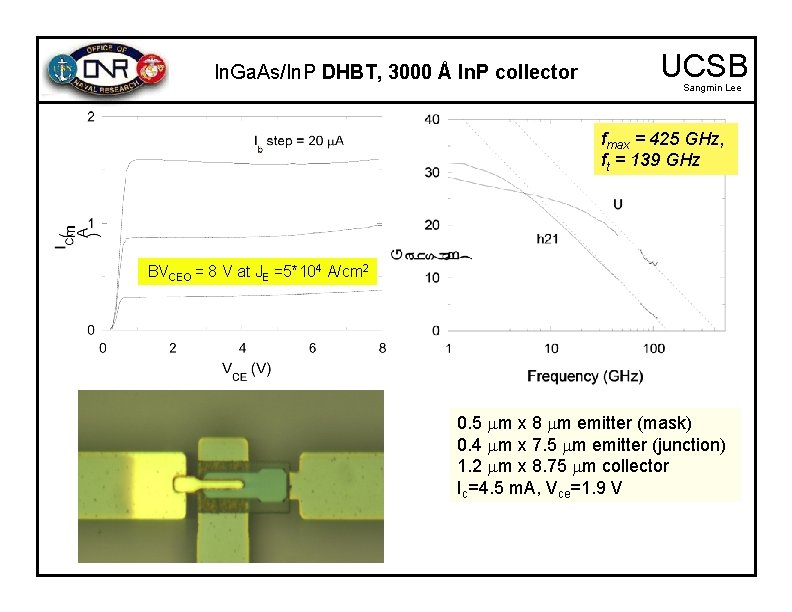

In. Ga. As/In. P DHBT, 3000 Å In. P collector UCSB Sangmin Lee fmax = 425 GHz, ft = 139 GHz BVCEO = 8 V at JE =5*104 A/cm 2 0. 5 m x 8 m emitter (mask) 0. 4 m x 7. 5 m emitter (junction) 1. 2 m x 8. 75 m collector Ic=4. 5 m. A, Vce=1. 9 V

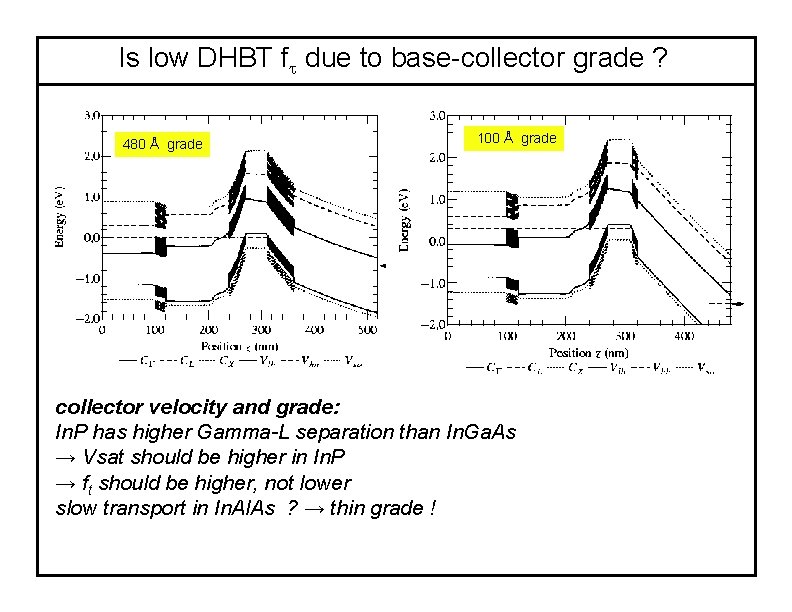

Is low DHBT ft due to base-collector grade ? 480 Å grade 100 Å grade collector velocity and grade: In. P has higher Gamma-L separation than In. Ga. As → Vsat should be higher in In. P → ft should be higher, not lower slow transport in In. Al. As ? → thin grade !

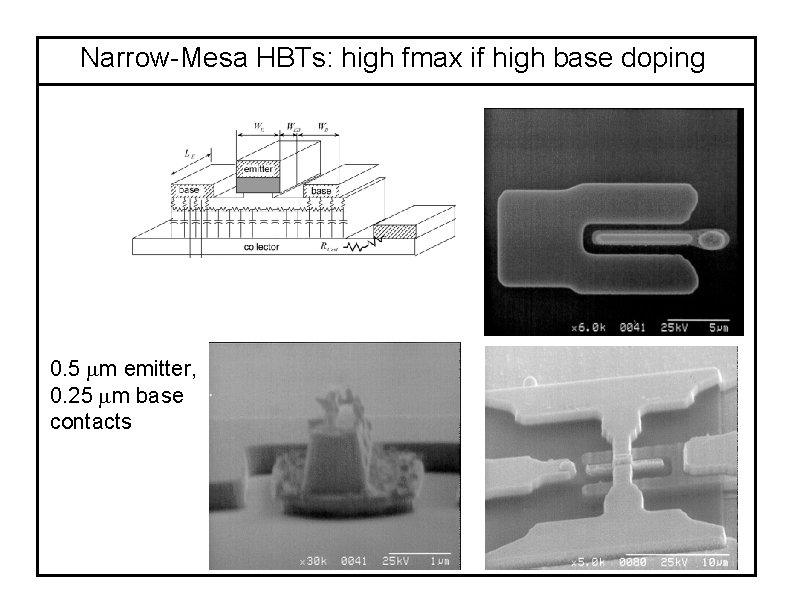

Narrow-Mesa HBTs: high fmax if high base doping 0. 5 m emitter, 0. 25 m base contacts

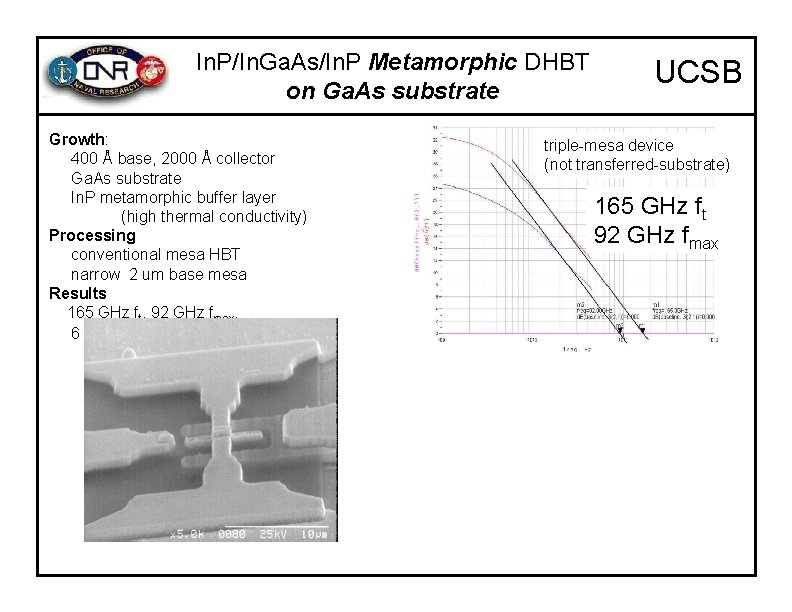

In. P/In. Ga. As/In. P Metamorphic DHBT on Ga. As substrate Growth: 400 Å base, 2000 Å collector Ga. As substrate In. P metamorphic buffer layer (high thermal conductivity) Processing conventional mesa HBT narrow 2 um base mesa Results 165 GHz ft, 92 GHz fmax, 6 Volt BVCEO, b=27 UCSB triple-mesa device (not transferred-substrate) 165 GHz ft 92 GHz fmax

High Speed Amplifiers 18 d. B, DC--50+ GHz >397 GHz gain x bandwidth from 2 HBTs S 21 S 11 S 22 8. 2 d. B, DC-80 GHz UCSB Dino Mensa PK Sundararajan

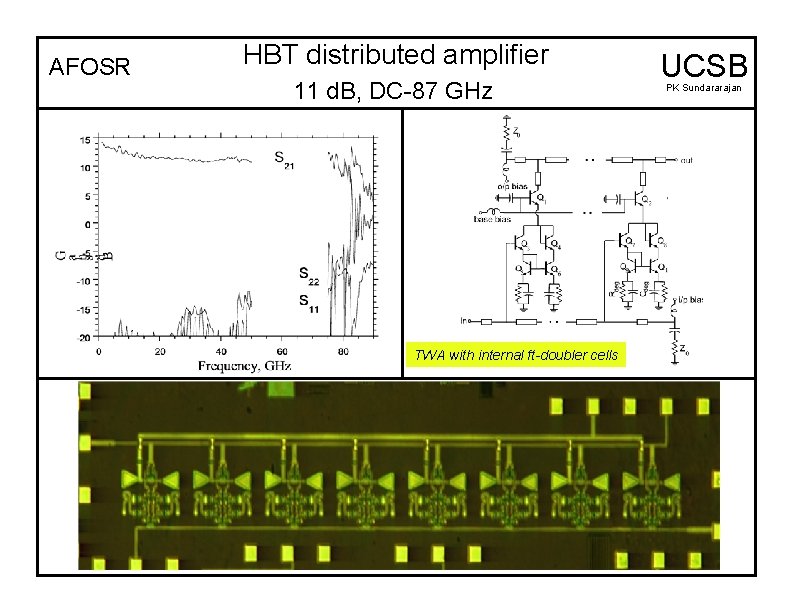

AFOSR HBT distributed amplifier 11 d. B, DC-87 GHz TWA with internal ft-doubler cells UCSB PK Sundararajan

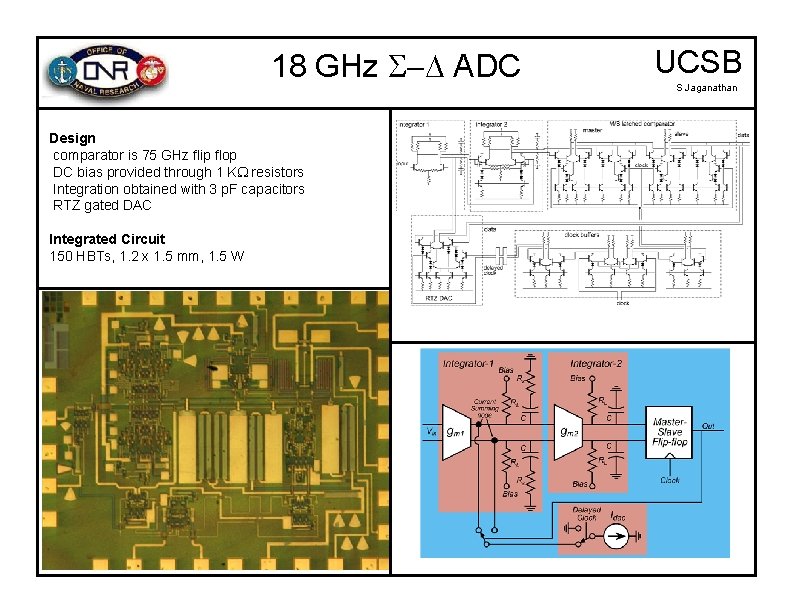

18 GHz S-D ADC Design comparator is 75 GHz flip flop DC bias provided through 1 K resistors Integration obtained with 3 p. F capacitors RTZ gated DAC Integrated Circuit 150 HBTs, 1. 2 x 1. 5 mm, 1. 5 W UCSB S Jaganathan

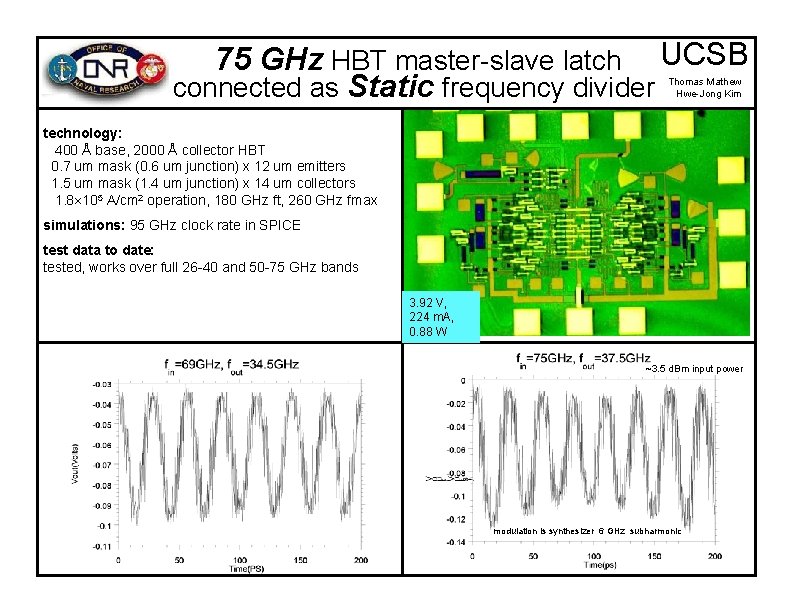

75 GHz HBT master-slave latch UCSB connected as Static frequency divider Thomas Mathew Hwe-Jong Kim technology: 400 Å base, 2000 Å collector HBT 0. 7 um mask (0. 6 um junction) x 12 um emitters 1. 5 um mask (1. 4 um junction) x 14 um collectors 1. 8´ 105 A/cm 2 operation, 180 GHz ft, 260 GHz fmax simulations: 95 GHz clock rate in SPICE test data to date: tested, works over full 26 -40 and 50 -75 GHz bands 3. 92 V, 224 m. A, 0. 88 W ~3. 5 d. Bm input power modulation is synthesizer 6 GHz subharmonic

MHBT slide

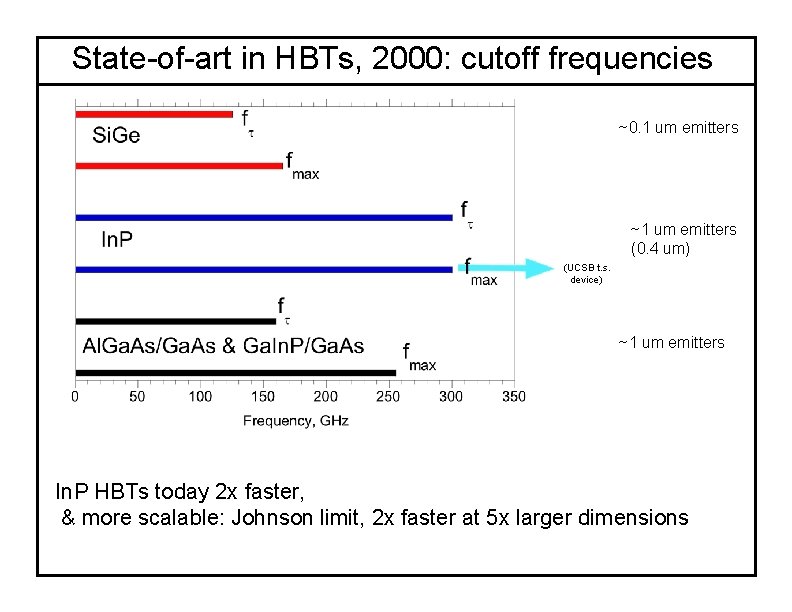

State-of-art in HBTs, 2000: cutoff frequencies ~0. 1 um emitters ~1 um emitters (0. 4 um) (UCSB t. s. device) ~1 um emitters In. P HBTs today 2 x faster, & more scalable: Johnson limit, 2 x faster at 5 x larger dimensions

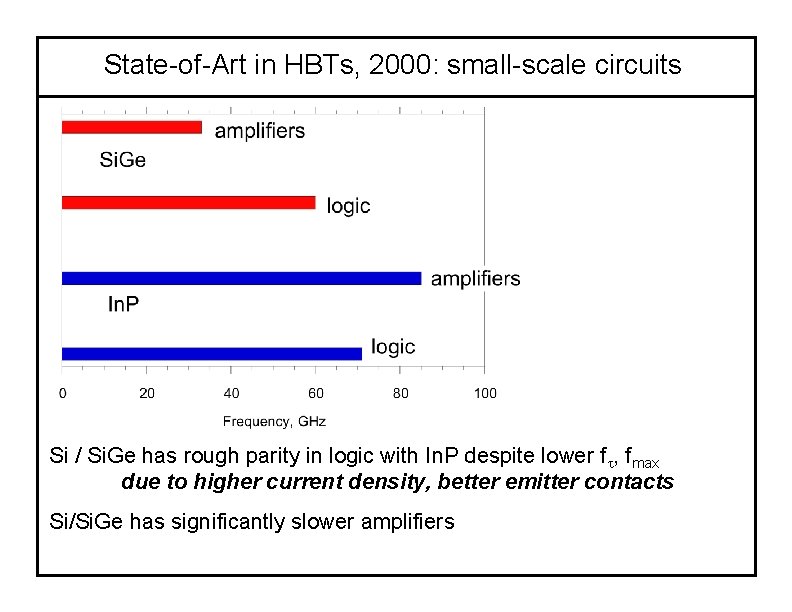

State-of-Art in HBTs, 2000: small-scale circuits Si / Si. Ge has rough parity in logic with In. P despite lower ft, fmax due to higher current density, better emitter contacts Si/Si. Ge has significantly slower amplifiers

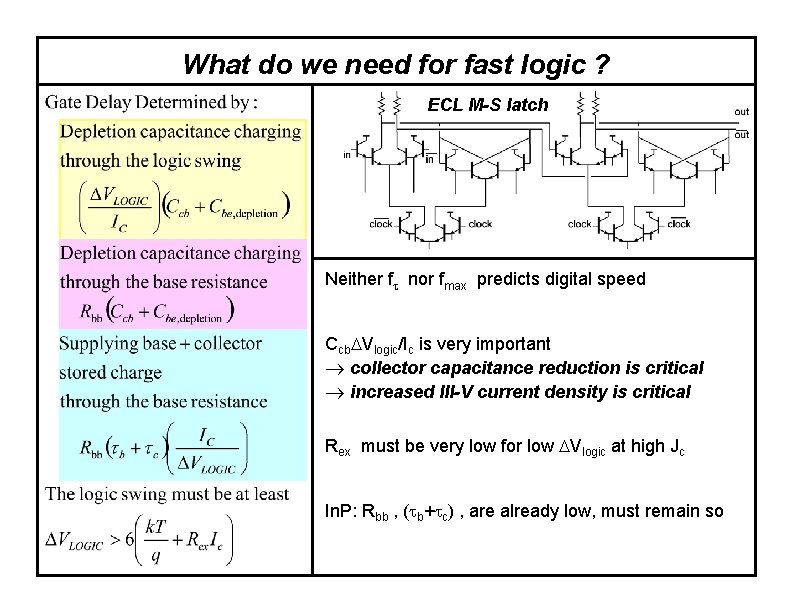

What do we need for fast logic ? ECL M-S latch Neither ft nor fmax predicts digital speed Ccb. DVlogic/Ic is very important ® collector capacitance reduction is critical ® increased III-V current density is critical Rex must be very low for low DVlogic at high Jc In. P: Rbb , (tb+tc) , are already low, must remain so

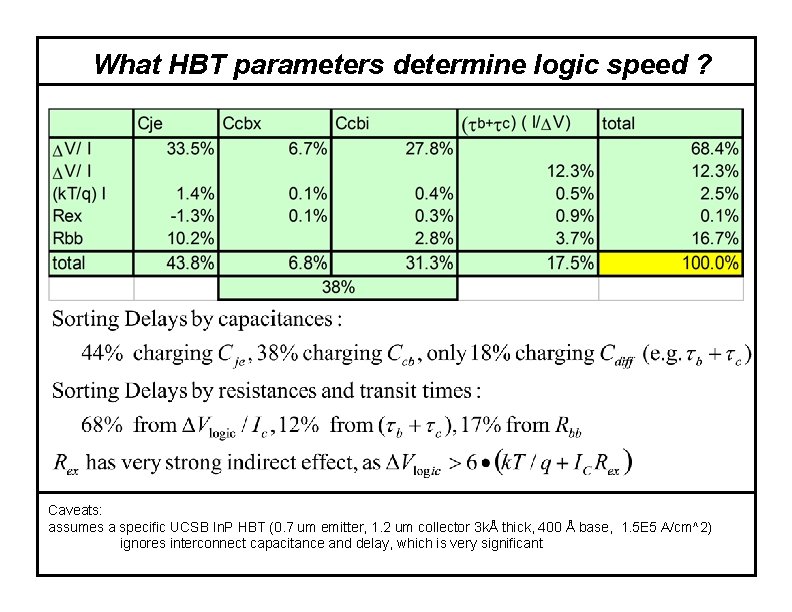

What HBT parameters determine logic speed ? Caveats: assumes a specific UCSB In. P HBT (0. 7 um emitter, 1. 2 um collector 3 kÅ thick, 400 Å base, 1. 5 E 5 A/cm^2) ignores interconnect capacitance and delay, which is very significant

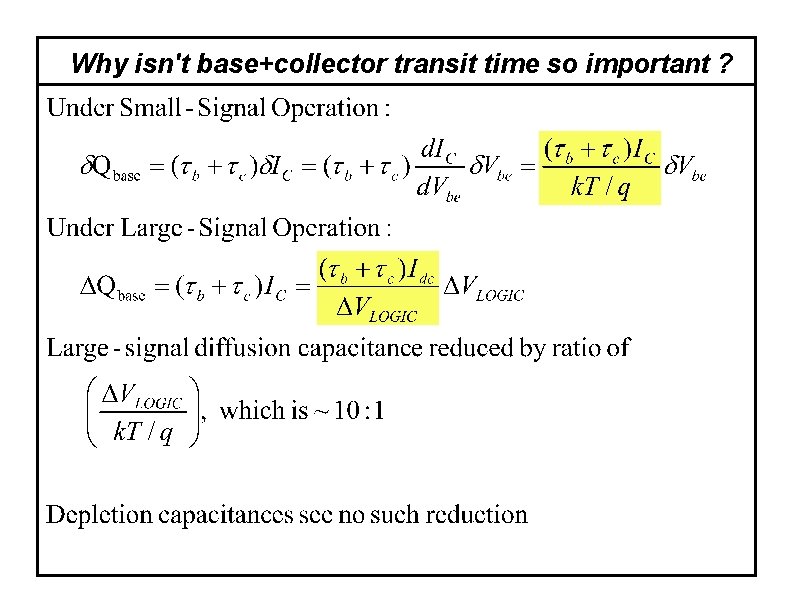

Why isn't base+collector transit time so important ?

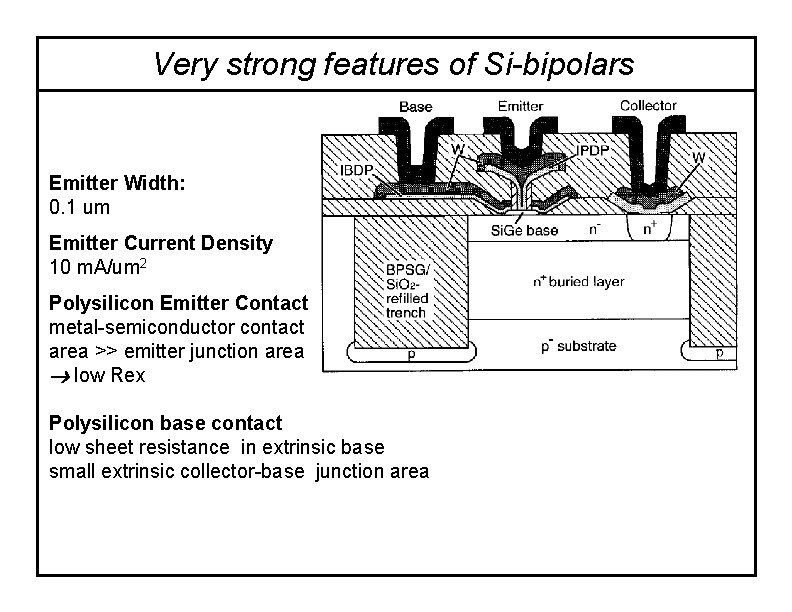

Very strong features of Si-bipolars Emitter Width: 0. 1 um Emitter Current Density 10 m. A/um 2 Polysilicon Emitter Contact metal-semiconductor contact area >> emitter junction area ® low Rex Polysilicon base contact low sheet resistance in extrinsic base small extrinsic collector-base junction area

In. P HBT limits to yield: non-planar process Emitter contact Failure modes Etch to base Liftoff base metal Emitter planarization, interconnects Yield degrades as emitters are scaled to submicron dimensions

Submicron HBT scaling: Scaling HBTs for 2 x increased speed: 2 x thinner layers, 4 x narrower junctions 4 x higher current density, 4 x improved vertical contacts Results with submicron III-V HBT scaling: 300 GHz ft , high (unmeasurable) fmax 6 -d. B 175 GHz amplifiers, 75 GHz true digital ICs Challenges with HBT scaling for fast digital : collector width scaling, current density, emitter resistivity high-yield submicron emitter & collector processes

In Case of Questions

Scaling Laws, Collector Current Density, Ccb charging time Base Push-Out (Kirk Effect) Collector Depletion Layer Collapse Collector capacitance charging time is reduced by thinning the collector while increasing current

- Slides: 37