2 GSs DataAcquisition System ZEUS GANNON Data Acquisition

![References [1] Datalogger. jpg, https: //commons. wikimedia. org/wiki/File: Datalogger. jpgt, Avisaro AG [CC BY References [1] Datalogger. jpg, https: //commons. wikimedia. org/wiki/File: Datalogger. jpgt, Avisaro AG [CC BY](https://slidetodoc.com/presentation_image_h/0f506ac035127c6bf6d7fb0eb2eb3c11/image-14.jpg)

- Slides: 14

2 GS/s Data-Acquisition System ZEUS GANNON

Data Acquisition Background Why do we collect data? • Capture trends • Let computers see the world What type of data do we collect? • Atmospheric • Industrial sensors • EM returns

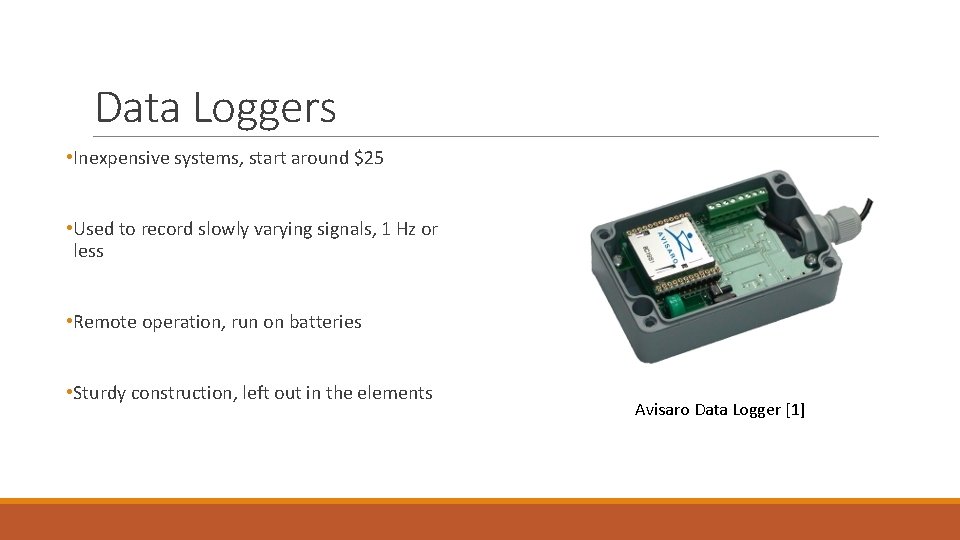

Data Loggers • Inexpensive systems, start around $25 • Used to record slowly varying signals, 1 Hz or less • Remote operation, run on batteries • Sturdy construction, left out in the elements Avisaro Data Logger [1]

Data Acquisition Systems • Expensive systems, start around $500 • Used to record high speed signals, up to 5 GS/s • Front end of oscilloscopes • Usually require a computer interface to analyze collected data 3000 Series Pico. Scope [2]

Discrete DAS • Use discrete components for clock management and address generation • Usually require Demuxing down to manageable speeds outside of the ADC • Not widely used Discrete DAS [3]

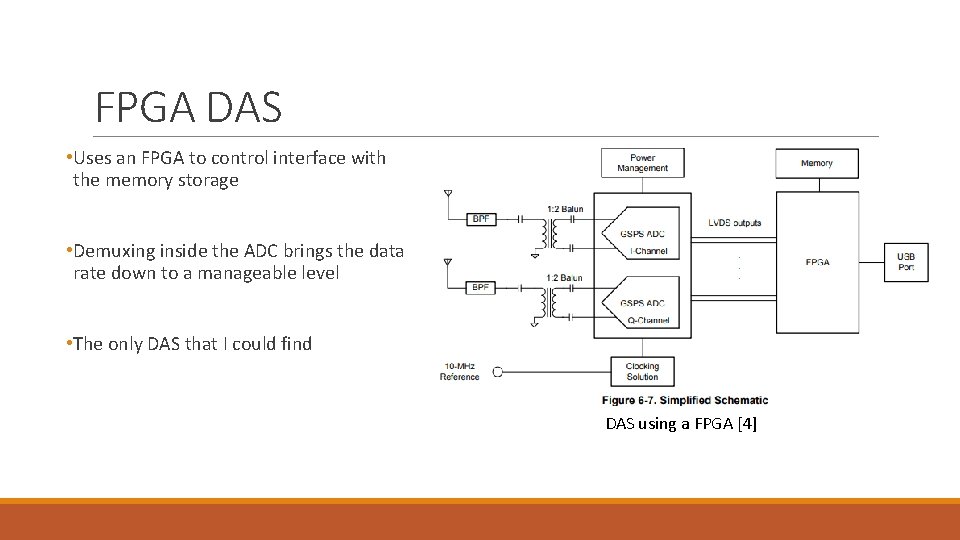

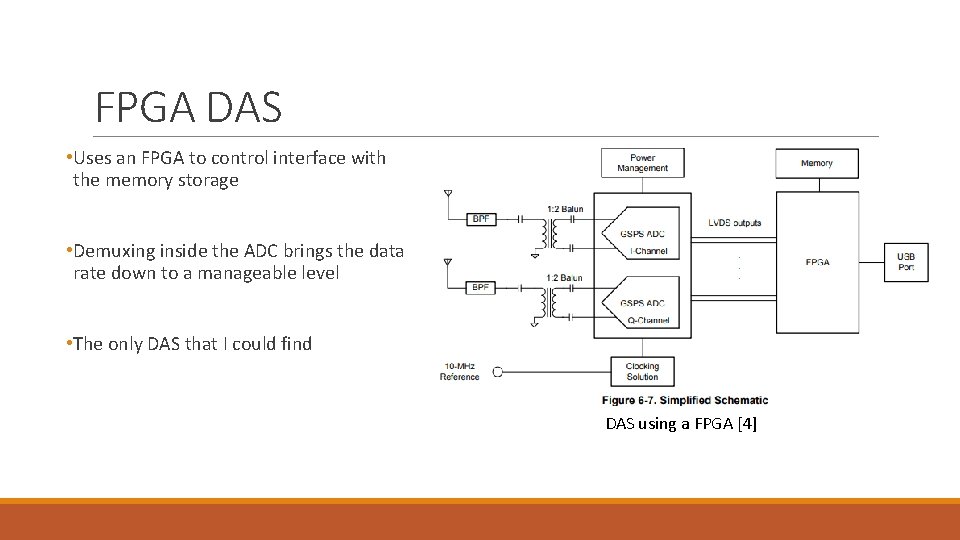

FPGA DAS • Uses an FPGA to control interface with the memory storage • Demuxing inside the ADC brings the data rate down to a manageable level • The only DAS that I could find DAS using a FPGA [4]

Motivation • Inherited a radar system • Current DAS is an oscilloscope • Rework the system to have a longer collection time • Don’t plan on building one myself • Intend on familiarizing myself with how they work

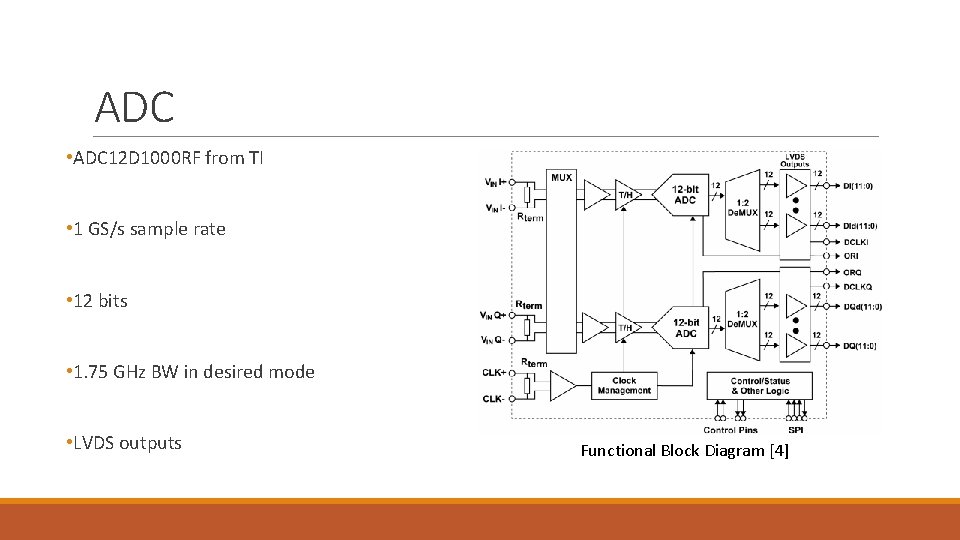

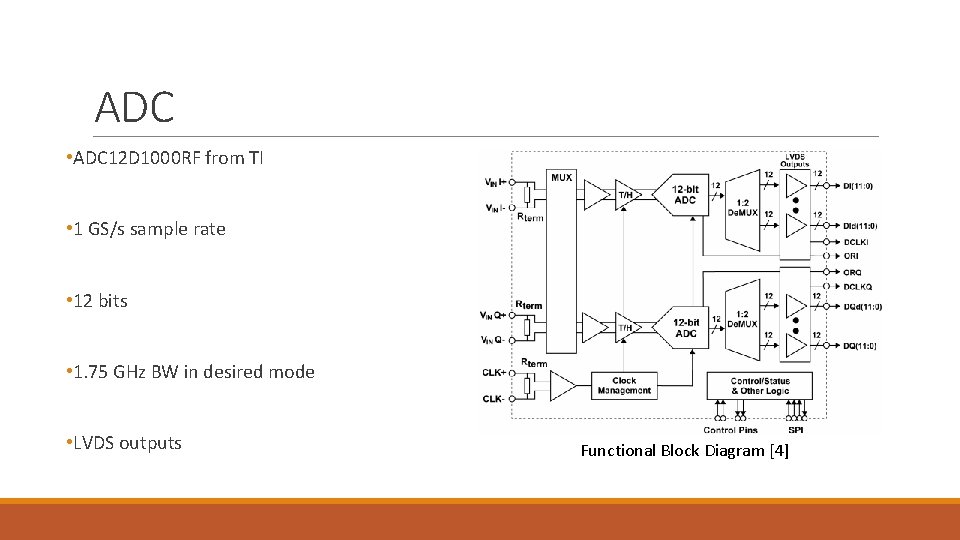

ADC • ADC 12 D 1000 RF from TI • 1 GS/s sample rate • 12 bits • 1. 75 GHz BW in desired mode • LVDS outputs Functional Block Diagram [4]

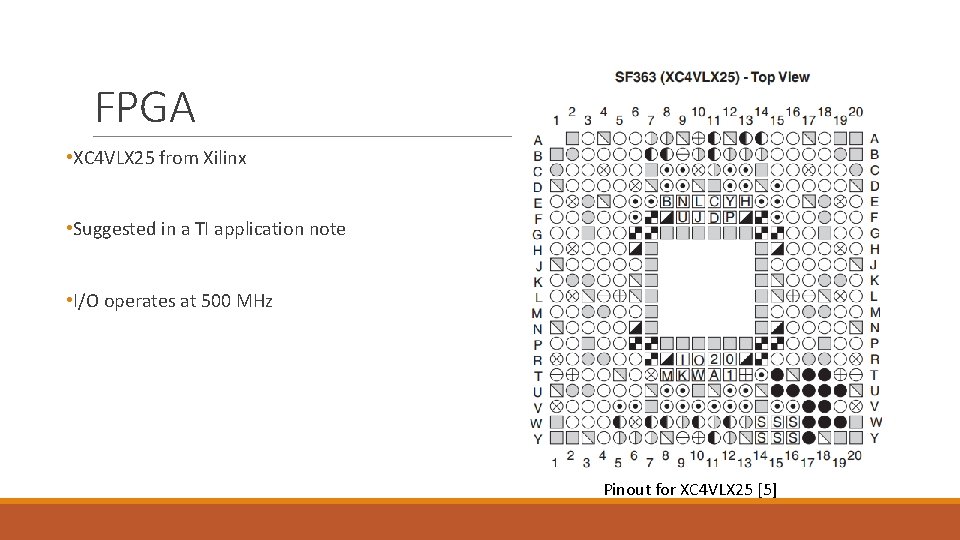

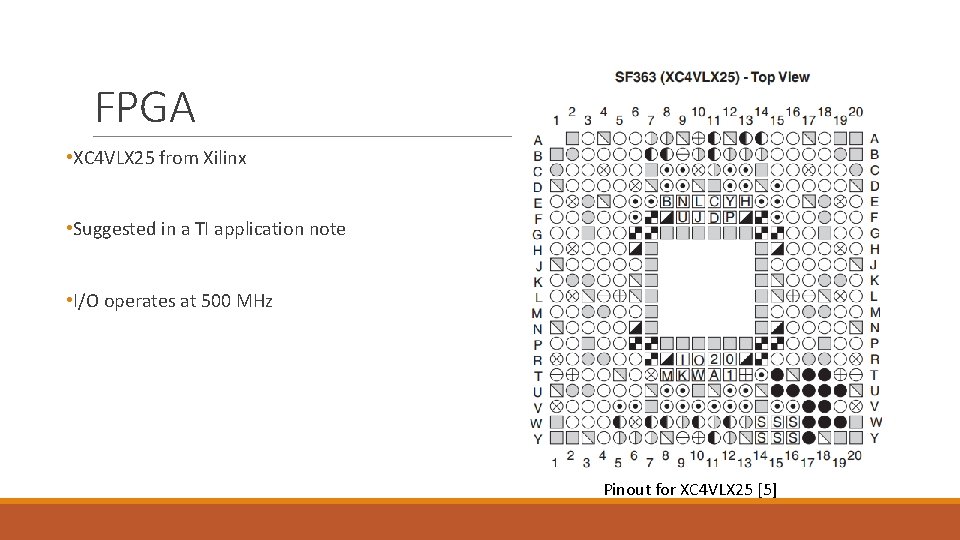

FPGA • XC 4 VLX 25 from Xilinx • Suggested in a TI application note • I/O operates at 500 MHz Pinout for XC 4 VLX 25 [5]

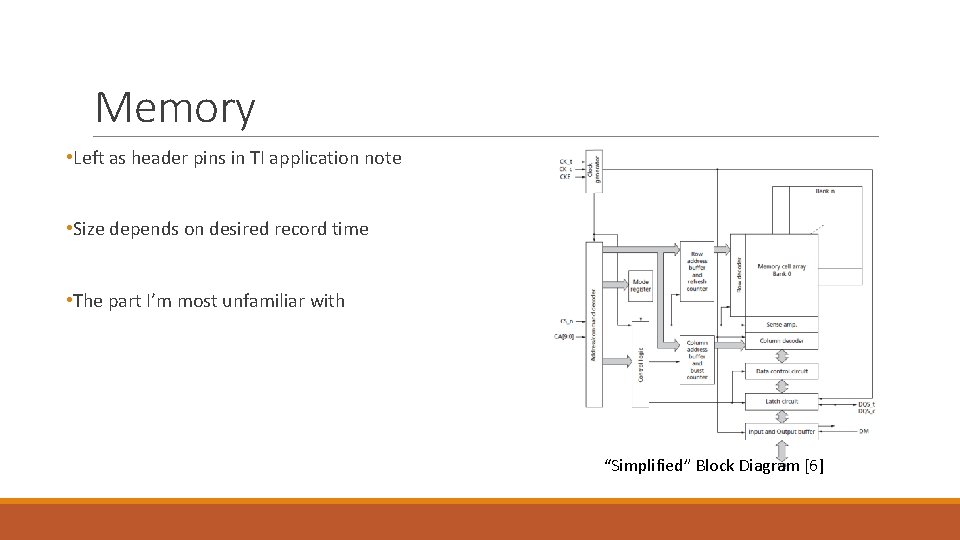

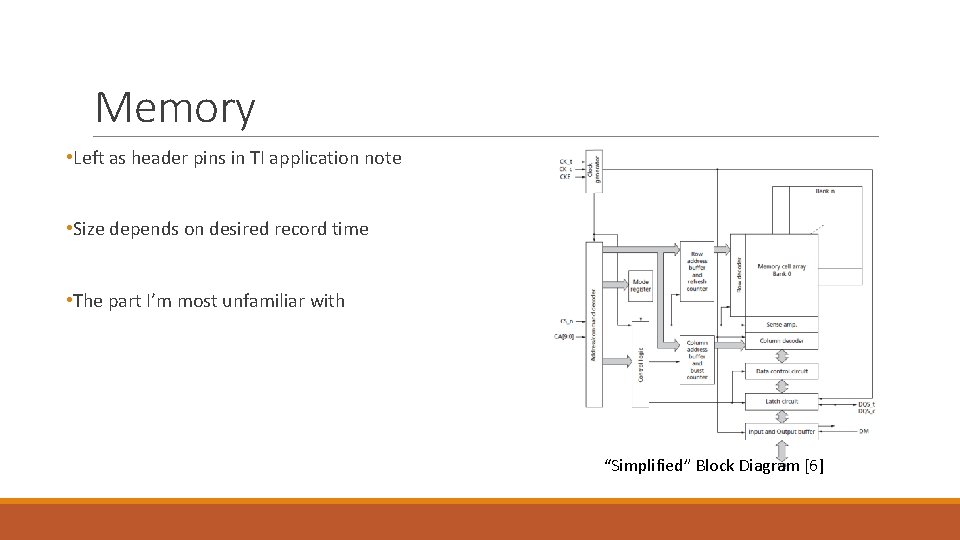

Memory • Left as header pins in TI application note • Size depends on desired record time • The part I’m most unfamiliar with “Simplified” Block Diagram [6]

Next Steps • Firmly decide on the memory chip • Read 100’s more pages of datasheets • Program every chip correctly in a schematic • Write a report

Lessons Learned • Everyone uses FPGAs for everything • What the word “interleaved” means • Chip manufactures will tell you how to use their products in the hope you will buy them • Browsing for parts is a pain

Questions?

![References 1 Datalogger jpg https commons wikimedia orgwikiFile Datalogger jpgt Avisaro AG CC BY References [1] Datalogger. jpg, https: //commons. wikimedia. org/wiki/File: Datalogger. jpgt, Avisaro AG [CC BY](https://slidetodoc.com/presentation_image_h/0f506ac035127c6bf6d7fb0eb2eb3c11/image-14.jpg)

References [1] Datalogger. jpg, https: //commons. wikimedia. org/wiki/File: Datalogger. jpgt, Avisaro AG [CC BY 3. 0 (https: //creativecommons. org/licenses/by/3. 0)] [2] PICO-3406 D-KIT-2, https: //www. picotech. com/products/oscilloscope, Pico. Tech [3] C. Allen, 713_HSD_Architectures-F 19, https: //people. eecs. ku. edu/~callen 58/713/EECS 713. htm [4] Texas Instruments, ADC 12 D 1000 RF Datasheet, http: //www. ti. com/lit/ds/symlink/adc 12 d 1000 rf. pdf [5] Xilinx, Virtex-4 FPGA Packaging and Pinout Specification, https: //www. xilinx. com/support/documentation/user_guides/ug 075. pdf [6] Micron, 216 -Ball and 220 -Ball, Dual-Channel LPDDR 2 SDRAM Features, 216 b_220 b_2 ch_2 e 0 e_embedded_lpddr 2. pdf