16 bit RISC processor for JPEG decoding Team

16 -bit RISC processor for JPEG decoding Team: DARTS Deepesh John, Smitha Shyam, Sujay Phadke, Tejasvi Kachru

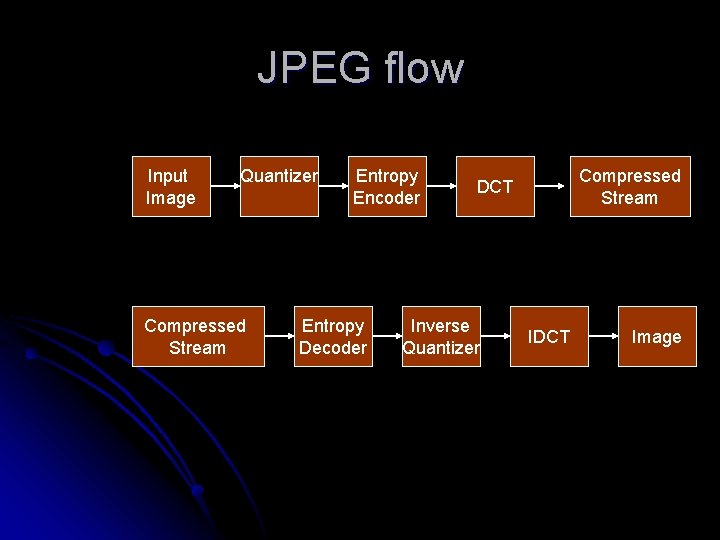

JPEG flow Input Image Quantizer Compressed Stream Entropy Encoder Entropy Decoder Compressed Stream DCT Inverse Quantizer IDCT Image

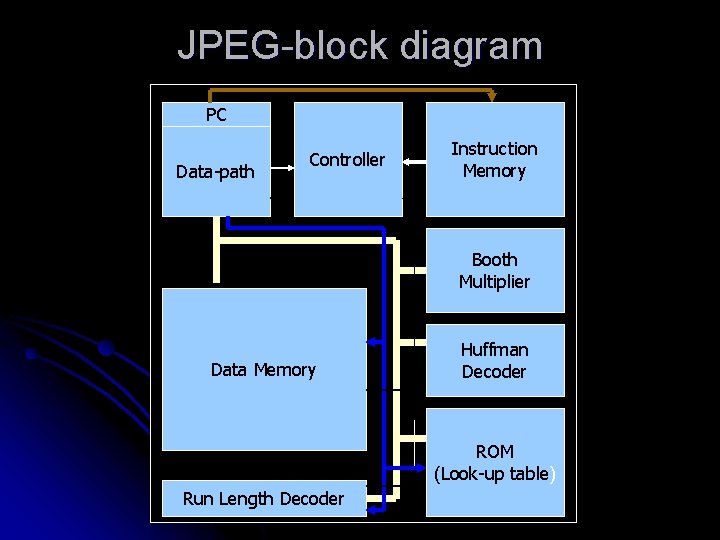

JPEG-block diagram PC Data-path Controller Instruction Memory Booth Multiplier Data Memory Huffman Decoder ROM (Look-up table) Run Length Decoder

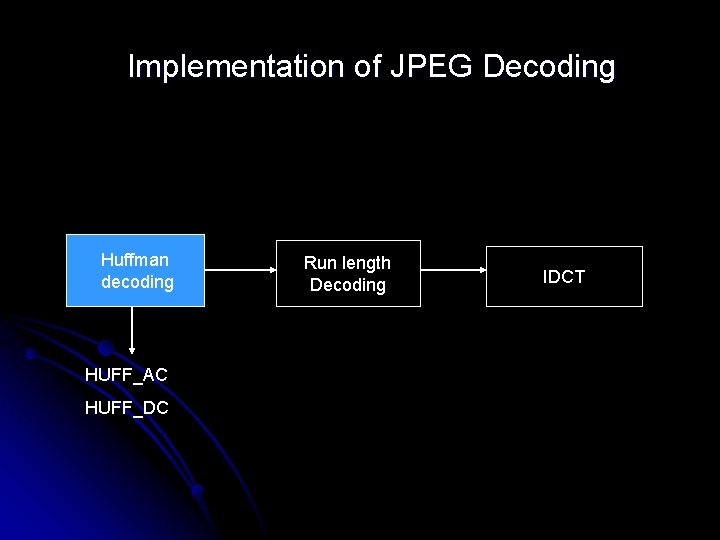

Implementation of JPEG Decoding Huffman decoding HUFF_AC HUFF_DC Run length Decoding IDCT

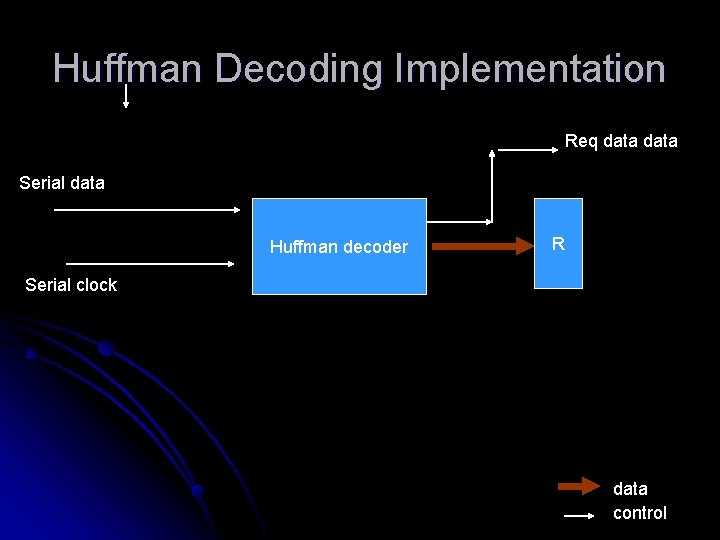

Huffman Decoding Implementation Req data Serial data Huffman decoder R Serial clock data control

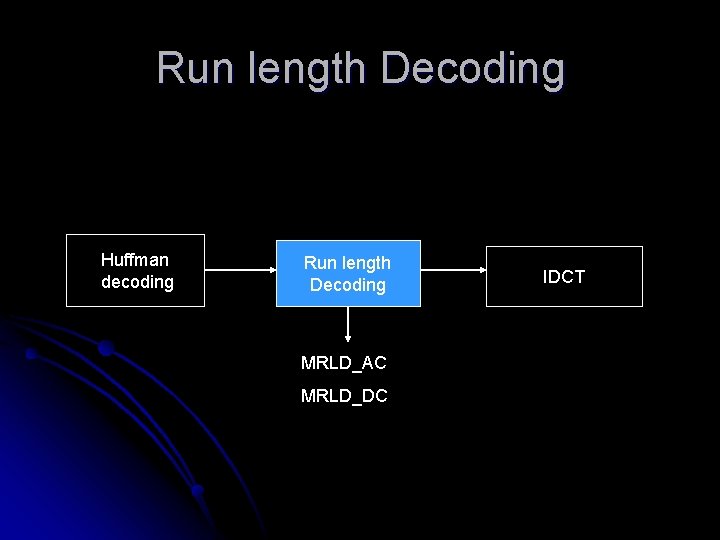

Run length Decoding Huffman decoding Run length Decoding MRLD_AC MRLD_DC IDCT

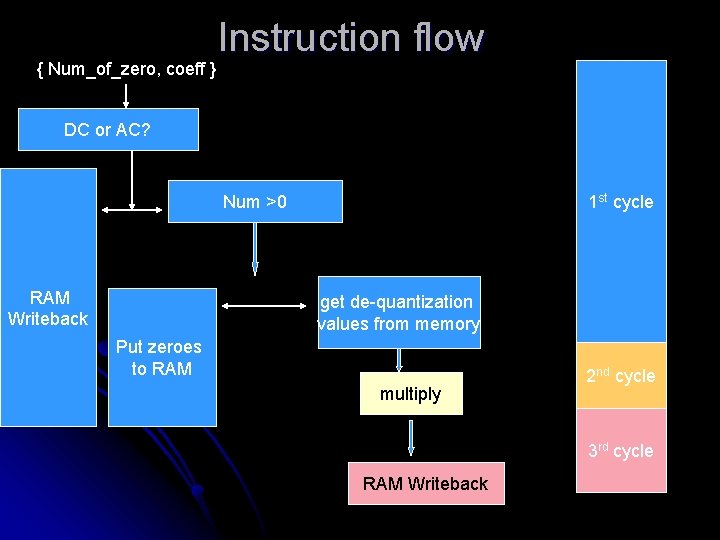

{ Num_of_zero, coeff } Instruction flow DC or AC? 1 st cycle Num >0 RAM Writeback get de-quantization values from memory Put zeroes to RAM multiply 2 nd cycle 3 rd cycle RAM Writeback

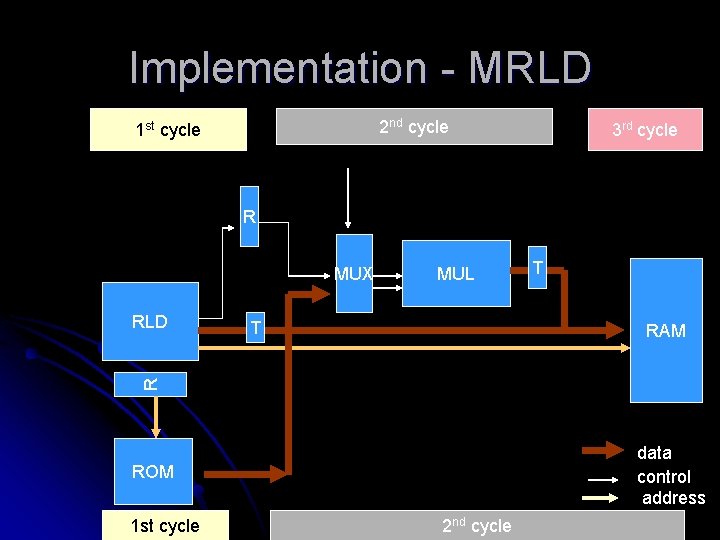

Implementation - MRLD 2 nd cycle 1 st cycle 3 rd cycle R MUX T T RAM R RLD MUL data control address ROM 1 st cycle 2 nd cycle

JPEG decoding Huffman decoding Run length Decoding IDCT MUL Rsrc, Rdest SHIFT ADD

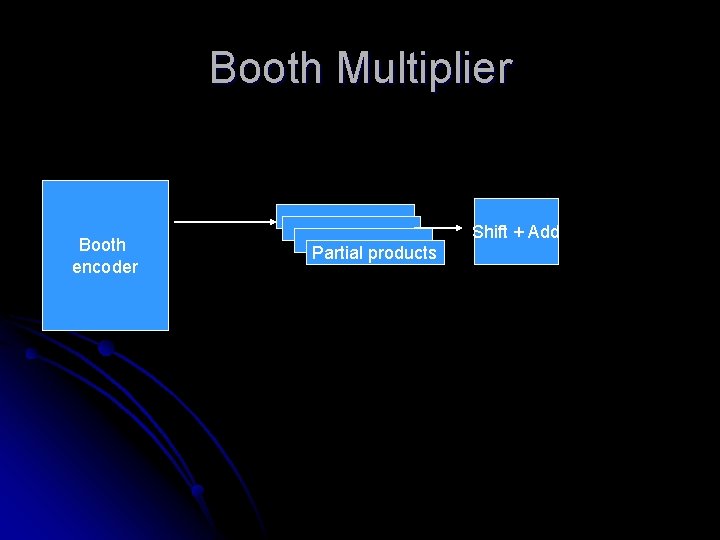

Booth Multiplier Booth encoder Shift + Add Partial products

Adder & shifter Adder l 16 -bit Carry Bypass l Carry Chain: Inversion property, Transmission gate XOR for Propagate l Reduction in area achieved by using Wang XNOR Shifter l Logarithmic shifter

Simulation Scripts for all eldo testing l Baseline instructions tested exhaustively l New instructions tested with partial reproduction of jpeg algorithm l

Critical Path l Serial clock – 5 cycles Huffman block -5. 7 ns l ROM read + MUL(MRLD) =2+6 = 8 ns

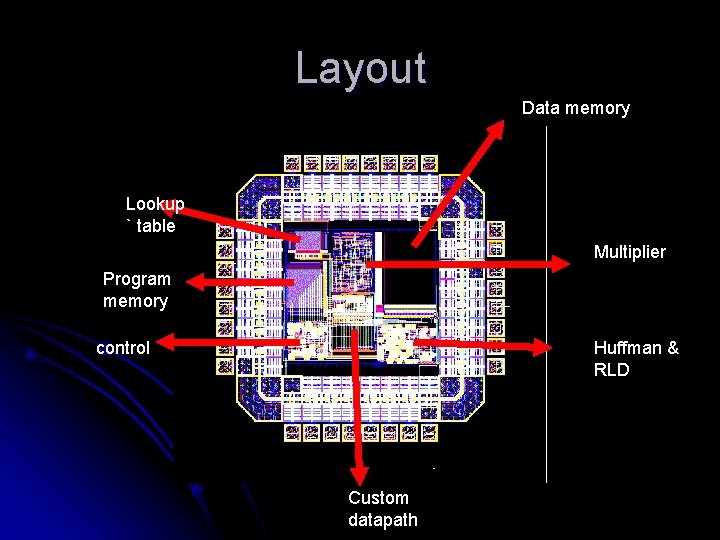

Layout Data memory Lookup ` table Multiplier Program memory control Huffman & RLD Custom datapath

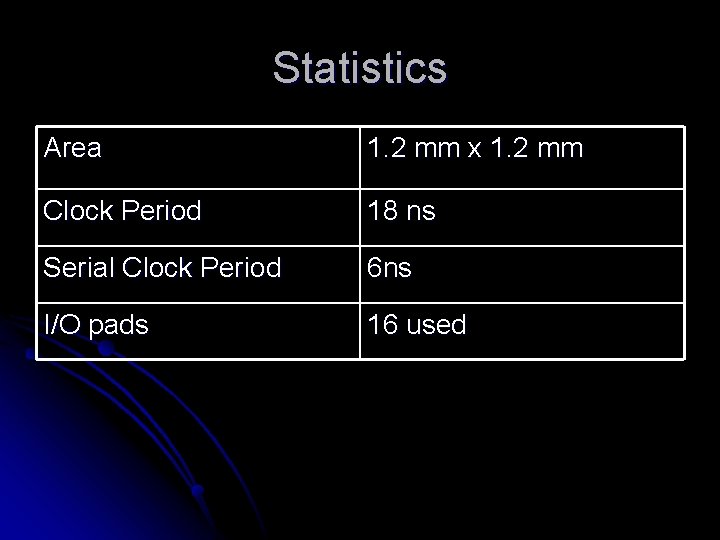

Statistics Area 1. 2 mm x 1. 2 mm Clock Period 18 ns Serial Clock Period 6 ns I/O pads 16 used

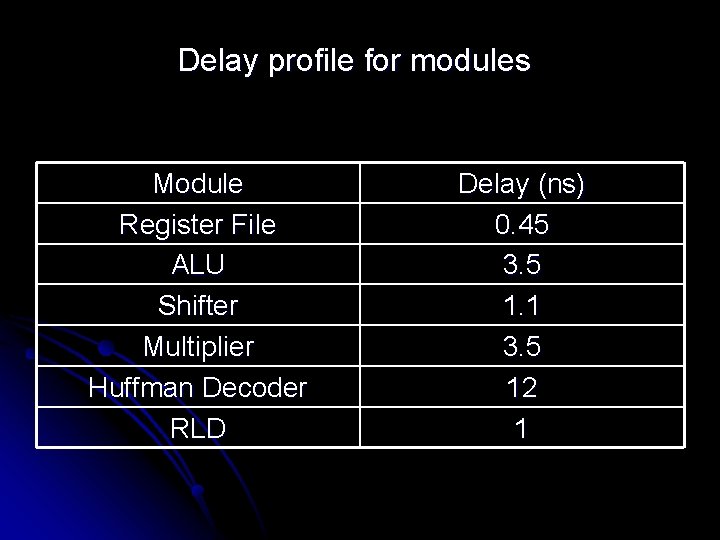

Delay profile for modules Module Register File ALU Shifter Multiplier Huffman Decoder RLD Delay (ns) 0. 45 3. 5 1. 1 3. 5 12 1

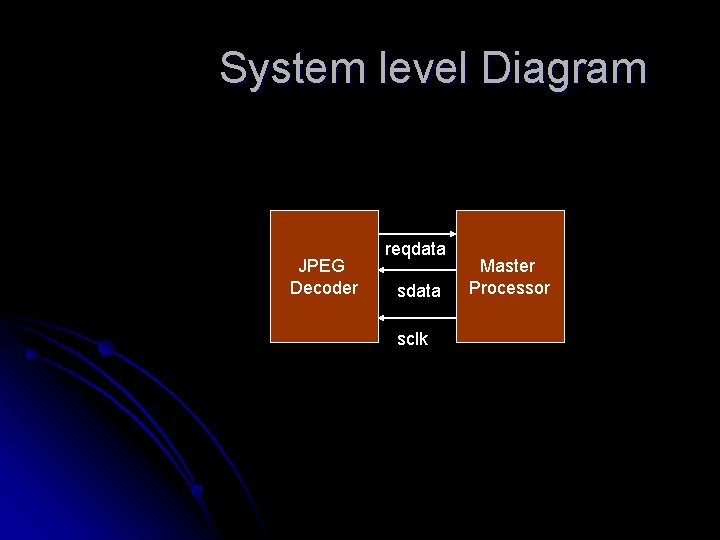

System level Diagram JPEG Decoder reqdata sclk Master Processor

Highlights Parallelism of multiply and rom read l Multiply bypass write back to ram for zero values l Adder- wang xnor l Huffman decoding l Scan chain through PC, IREG, PSR l

Improvements DMA port l Interrupts l Peripheral interface l Dynamic changing of Huffman tables l

- Slides: 19